# HIMICS: A VIRTUAL MEMORY ENVIRONMENT FOR MINI-COMPUTERS AND A DESCRIPTION OF ITS LEVEL 2 PROCESSOR

by

# ARLAN E. BENTZ

B.S., Kansas State University, 1968

A MASTER'S REPORT

submitted in partial fulfillment of the

requirements for the degree

MASTER OF SCIENCE

Department of Computer Science

KANSAS STATE UNIVERSITY

Manhattan, Kansas

1975

Approved by:

Major Professor

THIS BOOK CONTAINS NUMEROUS PAGES WITH THE ORIGINAL PRINTING BEING SKEWED DIFFERANTLY FROM THE TOP OF THE PAGE TO THE BOTTOM.

THIS IS AS RECEIVED FROM THE CUSTOMER.

LD

2668

R4

1975

B45 TABLE OF CONTENTS

C.2

Document

|      | SECTION NAME CHAPTER ONE                                                                                                                                                                                                                                                        | PAGE                                               |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 1.1  | INTRODUCTION                                                                                                                                                                                                                                                                    | 1                                                  |

| 1.2  | TECHNIQUES FOR RECURRENT USE OF MEMORY  1.2.1 OVERLAY STRUCTURES  1.2.2 VIRTUAL MEMORY  1.2.2.1 VIRTUAL MEMORY TECHNIQUES  1.2.2.2 ADVANTAGES OF VIRTUAL MEMORY                                                                                                                 | 1<br>1<br>2<br>4<br>7                              |

| 1.3  | SUPPORT FOR EMULATORS                                                                                                                                                                                                                                                           | 7                                                  |

| 1.4  | INTER-EMULATOR COMMUNICATION                                                                                                                                                                                                                                                    | 8                                                  |

| 1.5  | MANAGEABLE SOFTWARE                                                                                                                                                                                                                                                             | 8                                                  |

| 1.6  | INSTRUMENTATION  1.6.1 RECORDED COUNTS  1.6.2 WORKING SET OPTIONS                                                                                                                                                                                                               | 9<br>9<br>10                                       |

| 1.7  | OVERVIEW OF THE SYSTEM  1.7.1 ADVANTAGES OF THE SYSTEM  1.7.2 EXPLANATION OF LEVELS                                                                                                                                                                                             | 11<br>13<br>15                                     |

| 1.8  | IMPLEMENTATION  1.8.1 HARDWARE ALLOCATION  1.8.2 MEMORY LEVELS  1.8.3 LOCATION OF SOFTWARE                                                                                                                                                                                      | 16<br>17<br>17<br>22                               |

| 1.9  | SUMMARY                                                                                                                                                                                                                                                                         | 23                                                 |

| 1.10 | INTRODUCTORY DESCRIPTION OF REMAINING CHAPTERS                                                                                                                                                                                                                                  | 24                                                 |

|      | CHAPTER TWO                                                                                                                                                                                                                                                                     |                                                    |

| 2.1  | INTRODUCTION                                                                                                                                                                                                                                                                    | 26                                                 |

| 2,2  | PAGE MANAGEMENT  2.2.1 THRASHING IN PAGED MEMORY SYSTEMS  2.2.2 PAGING OPTIONS  2.2.3 WORKING SET SIZE  2.2.4 PAGING TRANSFER FLOW PATTERNS  2.2.4.1 TRANSFER FLOW PATTERN 1  2.2.4.2 TRANSFER FLOW PATTERN 2  2.2.4.3 TRANSFER FLOW PATTERN 3  2.2.4.4 TRANSFER FLOW PATTERN 4 | 26<br>26<br>27<br>30<br>30<br>34<br>34<br>35<br>36 |

|            | SECTION NAME                                 | PAGE           |

|------------|----------------------------------------------|----------------|

| <b>8</b> 6 | 2.2.5 PAGING ALCCRITHMS USED IN SYSTEM       | 37<br>39       |

|            | 2.2.5.2 PAGING ALGORITHM DISCUSSION          | <u>-</u> 2     |

|            | FOR OPTION 2                                 | 42             |

| 18         | FOR OPTION 3                                 | 44<br>45       |

| 2,3        | I/O FOR SYSTEM                               | 46<br>46<br>46 |

| 2,4        | FILE MANAGEMENT                              | 47<br>48       |

|            | CHAPTER THREE                                |                |

| 3,1        | INTRODUCTION                                 | 55             |

| 3,2        | ALGORITHM 1: MAIN DRIVER FOR NOVA ROUTINES   | 55             |

| 3,3        | ALGORITHM 2: GENERATES THE SYSTEM            | 61             |

| 3,4        | ALGORITHM 3: MAIN INPUT/OUTPUT DRIVER        | 61             |

| 3,5        | ALGORITHM 4: INPUT DRIVER                    | 68             |

| 3.6        | ALGORITHM 5: OUTPUT DRIVER                   | 70             |

| 3,7        | ALGORITHM 6: TRANSFERS DATA TO INPUT ADDRESS | 71             |

| 3.8        | ALGORITHM 7: TRANSFERS DATA TO OUTPUT FILE   | 74             |

| 3,9        | ALGORITHM 8: TRANSLATES NOVA I/O ERROR CODE  | 74             |

| 3,10       | ALGORITHM 9: PAGE OPTION 1 MAIN ROUTINE      | 76             |

| 3,11       | ALGORITHM 10: PAGE OPTION 1 INITIAL ROUTINE  | 84             |

| 3.12       | ALGORITHM 11: PAGE OPTION 2 MAIN ROUTINE     | 85             |

| 3,13       | ALGORITHM 12: PAGE OPTION 2 INITIAL ROUTINE  | 88             |

| 3,14       | ALGORITHM 13: PAGE OPTION 3 MAIN ROUTINE     | 90             |

| 3.15       | ALGORITHM 14: PAGE OPTION 3 INITIAL ROUTINE  | 90             |

| S    | ECTION NAME                                                                  |                                                              | PAGE                            |

|------|------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------|

| 3,16 | ALGORITHM 15:                                                                | RETRIEVE PAGE                                                | 91                              |

| 3.17 | ALGORITHM 16:                                                                | END OF JOB                                                   | 92                              |

| 3,18 | ALGORITHM 17:                                                                | LEVEL 3 MEMORY TO LEVEL 2 MEMORY                             | 92                              |

| 3,19 | ALGORITHM 18:                                                                | LEVEL 3 MEMORY TO LEVEL 1 MEMORY                             | 93                              |

| 3,20 | ALGORITHM 19:                                                                | LEVEL 2 MEMORY TO LEVEL 3 MEMORY                             | 93                              |

| 3,21 | ALGORITHM 20:                                                                | LEVEL 1 MEMORY TO LEVEL 2 MEMORY UNDER OPTIONS 1 AND 2       | 93                              |

| 3,22 | ALGORITHM 21:                                                                | LEVEL 1 MEMORY TO LEVEL 2 MEMORY UNDER OPTION 3              | 94                              |

| 3,23 | ALGORITHM 22:                                                                | LEVEL 1 MEMORY TO LEVEL 3 MEMORY                             | 94                              |

| 3,24 | ALGORITHM 23:                                                                | LEVEL 2 MEMORY TO LEVEL 1 MEMORY                             | 95                              |

| 3,25 | ALGORITHM 24:                                                                | INPUT SPOOLING                                               | 95                              |

| 3,26 | ALGORITHM 25:                                                                | JOB QUEUE SEARCH                                             | 98                              |

| 3.27 | ALGORITHM 26:                                                                | OBJECT DECK FILE NAME                                        | 98                              |

| 3,28 | ALGORITHM 27:                                                                | RETRIEVE OBJECT DECK FILE NAME                               | 98                              |

| 3,29 | ALGORITHM 28:                                                                | CREATE OUTPUT FILE NAME                                      | 99                              |

| 3,30 | ALGORITHM 29:                                                                | LIST STACK DEPTH COUNTS FOR PAGE OPTIONS 1 OR 3              | 99                              |

| 3,31 | ALGORITHM 30:                                                                | LIST STACK DEPTH COUNTS FOR PAGE OPTION 2                    | 100                             |

|      |                                                                              | CHAPTER FOUR                                                 |                                 |

| 4.1  | INTRODUCTION                                                                 |                                                              | 101                             |

| 4.2  | 4.2.1 I/O FI<br>4.2.2 ROLLII<br>4.2.3 MULTI-<br>4.2.4 PRIORI<br>4.2.5 PARAMI | ATION ILES N AND ROLLOUT TASKING ETER PASSING FOR SUBROUTINE | 101<br>101<br>103<br>104<br>104 |

|      | 1 N1                                                                         | DEPENDENCY                                                   | 104                             |

| SECTION NAM   | E .                                                          | PAGE |

|---------------|--------------------------------------------------------------|------|

| 4.3 TESTING O | F ALGORITHMS                                                 | 105  |

| 4.4.1         | N THEORETIC TIME ADVANTAGE SUGGESTED SYSTEM LOADS FOR SYSTEM |      |

|               | PERFORMANCE EVALUATION                                       |      |

|               | X.                                                           |      |

|               | APPENDICES                                                   |      |

| APPENDIX A: A | LGORITHMS                                                    | 117  |

| APPENDIX B: S | YSTEM CONFIGURATION FOR PAGE OPTION 1                        | 160  |

| APPENDIX C: S | YSTEM CONFIGURATION FOR PAGE OPTION 2                        | 161  |

| APPENDIX D: S | YSTEM CONFIGURATION FOR PAGE OPTION 3                        | 162  |

| APPENDIX E: S | UBROUTINE CALLING ORDER                                      | 163  |

# ILLUSTRATIONS

|               |                  |                                                           | PAGE |

|---------------|------------------|-----------------------------------------------------------|------|

| FIGURE        | 1-1              | OVERLAY STRUCTURE                                         | 3    |

| FIGURE        | 1777 1371        | VIRTUAL MEMORY STRUCTURE                                  | 5    |

| FIGURE        |                  | FIXED WORKING SET OPTIONS                                 | 12   |

| FIGURE        |                  | HIERARCHICAL STRUCTURE                                    | 14   |

| FIGURE        | Octob            | HARDWARE VIEW OF HIERARCHICAL STRUCTURE                   | 18   |

| FIGURE        | 1000             | ALTERNATE VIEW OF SYSTEM LEVELS                           | 19   |

| FIGURE        |                  | LEVELS OF MEMORY IN THE SYSTEM                            | 21   |

| FIGURE        |                  | LEVEL 2 MEMORY LAYOUT FOR VARIOUS                         | 21   |

| FIGURE        | 2-1              | PAGE OPTIONS                                              | 29   |

| FIGURE        | 2_2              | WORKING SET SIZE                                          | 31   |

| FIGURE        |                  | TRANSFER FLOW PATTERN 1                                   | 32   |

| FIGURE        |                  | TRANSFER FLOW FATTERN 2                                   | 32   |

| FIGURE        | 550              | TRANSFER FLOW PATTERN 3                                   | 33   |

| FIGURE        |                  | TRANSFER FLOW PATIENT 3 ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 33   |

| FIGURE        |                  | TRANSFER FLOW PATTERN 4                                   | 23   |

| FIGURE        | 2-1              | VARIABLE WORKING SET SIZE OPTION                          | 43   |

| FIGURE        | 2 0              |                                                           | 2.00 |

| FIGURE        |                  | SPOOL TABLE                                               | 49   |

| FIGURE        | 50,500 WPAN      | DISK USAGE SECTOR TABLE (DUST)                            | 49   |

| FIGURE        | 11.              | FILE MANAGEMENT TABLES                                    | 51   |

| FIGURE        | 2-11             | LOCATING REQUESTED PAGES IN THE                           |      |

| PTCIME        | 2 1              | LEVEL 2 PROCESSOR                                         | 53   |

| FIGURE        |                  | JOB PAGE CONTROL BLOCK                                    | 57   |

| FIGURE FIGURE |                  | USER PARAMETER BLOCK                                      | 63   |

| FIGURE        | 200000           | SYSTEM GENERATED PARAMETER BLOCK                          | 63   |

|               |                  | INTERDATA FUNCTION CODES FOR I/O                          | 64   |

| FIGURE        |                  | INTERDATA I/O ERROR CODES                                 | 65   |

| FIGURE        |                  | EXAMPLE OF I/O SPLIT ACROSS PAGE BOUNDARIES               | 69   |

| FIGURE        | 3-6              | EXAMPLE OF PAGE MAPPING                                   |      |

| BTAIRS        | ^ =              | (512 BYTES VS 256 WORDS)                                  | 73   |

| FIGURE        | 100 B            | CONTIGUOUSLY ORGANIZED FILES                              | 75   |

| FIGURE        | 1000 T 1000      | NOVA I/O ERROR CODES                                      | 77   |

| FIGURE        | VICTOR 1-12-71/7 | STACK DEPTH COUNTS                                        | 81   |

| FIGURE        |                  | EXTENDED PAGE FAULT TABLE                                 | 89   |

| FIGURE        |                  | SEQUENTIALLY ORGANIZED FILES                              | 97   |

| FIGURE        | 4-1              | EXAMPLE OF ALGORITHM TESTING                              | 107  |

|               |                  |                                                           | 108  |

|               |                  |                                                           | 109  |

| <b>D-0:</b>   |                  |                                                           | 111  |

| FIGURE        | 4-2              | MINIMUM PAGE FAULT TIME FOR SINGLE CPU                    | 114  |

The HIMICS system is a hierarchical virtual memory system for a hierarchy of interconnected mini-computers. This paper describes the design of the software system. The software system design in this paper is a hierarchical design with two major processor levels. An overall description of both processors is given and then a detailed description of its level 2 processor is presented. The detailed description includes the algorithms, written in a dialect of PL/1, along with a written description of them. The HIMICS system will provide a virtual memory system for a network of mini-computers and also allow the emulation of high level languages. The implementation of this system should result in an increase of processor efficiency and system throughput for the mini-computers involved in the network. The paper is concluded with a dialectic comparison of a single processor system versus a multi-processor system.

#### CHAPTER ONE

### 1.1 INTRODUCTION

In this paper we propose a design for a hierarchical minicomputer system called HIMICS (Hierarchical multI-tasking MinIcomputer Computer System). The system is designed with five major

objectives in mind. These objectives are:

- To provide virtual memory capability.

- (2) To provide support for emulators.

- (3) To provide inter-emulator communication.

- (4) To provide manageable software.

- (5) To provide sufficient instrumentation and monitor capabilities in order to encourage meaningful system evaluations and comparisons.

A general discussion of each of these objectives will be given before we present the actual design of the system.

# 1.2 TECHNIQUES FOR RECURRENT USE OF MEMORY

There are several techniques that are commonly used in modern day computers to execute programs which have a larger address space than the primary memory available to them. Two of the more commonly used techniques are overlay structures (1,6,12) and virtual memory (2,12).

### 1.2.1 OVERLAY STRUCTURES

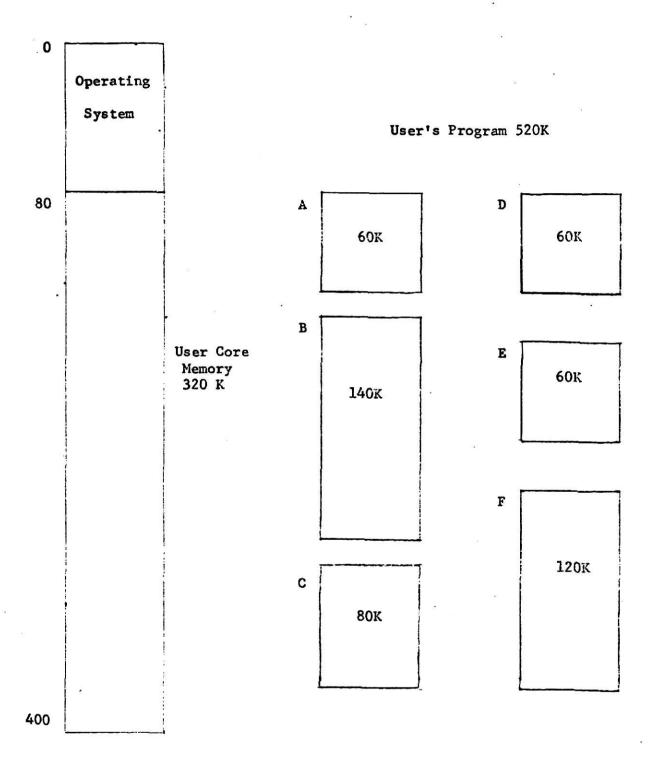

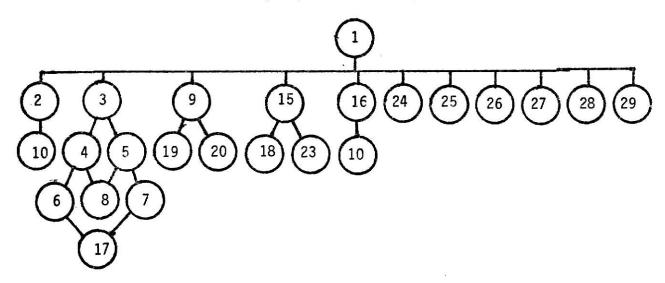

With overlay structures, segments of the program are kept on secondary storage and brought into main memory in an hierarchical sequence as they are needed. Pre-specified segments may be overwritten by incoming segments. This is illustrated in Figure 1-1. Here the user has a 520K program to be run in a 320K address space. Segments A, B and C are first loaded and execution begins. As soon as segment B is no longer needed, segments D and E can be overwritten in B's address space. The same process happens when C and E are no longer needed. They can be overwritten by F.

From this illustration it is apparent that the user must have a knowledge as to what segments are to be overwritten. It is the user's responsibility to issue orders for the overlay to occur. This is the major disadvantage of the overlay technique. The second technique, virtual memory, does not require the user to have this additional knowledge.

### 1.2.2 VIRTUAL MEMORY

The key to virtual memory relies on the fact that, for an instruction in a program to be executed, only the instruction and the data that it operates on need be in primary memory. From the instruction's point of view the rest of the program may be located on any level of memory. This removes the requirement that the job's entire address space be in physical memory at once. Because this physical restraint is removed, the operating program has the illusion that it has an extremely large memory, thus the term "virtual memory". Since a job's entire address space need not all be in primary memory at once,

THIS BOOK CONTAINS NUMEROUS PAGES WITH DIAGRAMS THAT ARE CROOKED COMPARED TO THE REST OF THE INFORMATION ON THE PAGE. THIS IS AS RECEIVED FROM CUSTOMER.

# Overlay Structure

Figure 1-1

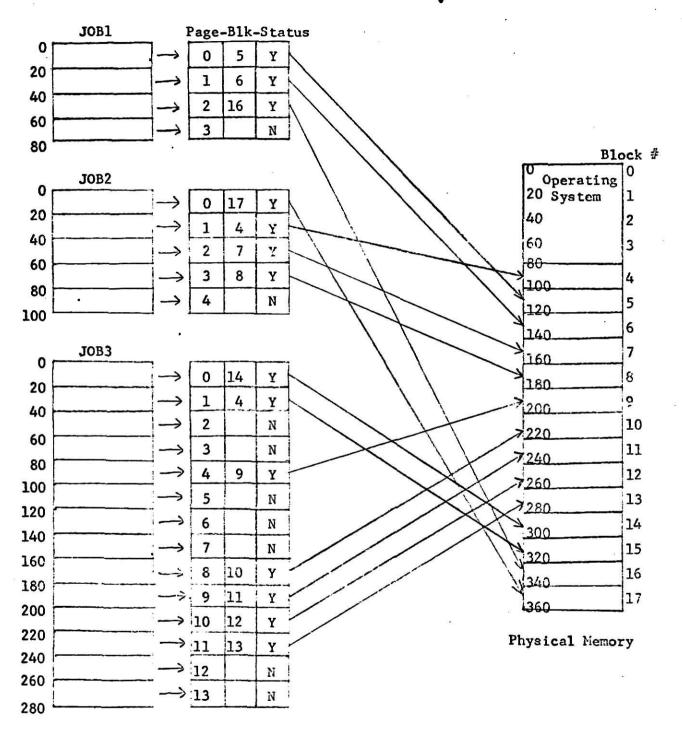

the sum of the address spaces of the jobs being multiprogrammed is permitted to exceed the physical size of main memory. This is illustrated in Figure 1-2. All three jobs are being executed in a physical memory space of 280K. The total sum of all three jobs is 460K.

The major constraint as to the size of the virtual space is limited by the hardware configuration. The hardware limits the number of addressable cells. The limiting factor is the number of bits used for an address. For example, if the hardware allows 8 bits for an address, then there are 256 addressable cells. The addresses would range from 0 to 255. This limits the virtual memory to this same size of space. The virtual space is usually considerably larger than the available primary memory of the machine.

### 1.2.2.1 VIRTUAL MEMORY TECHNIQUES

Two major virtual memory techniques are, demand-paged memory management (1,7) and segmented memory management (1). As was stated previously, virtual memory requires that the instruction and data to be operated on be located in primary memory. If this were to be done one instruction at a time it would be too time consuming. Instead they are retrieved in sections upon demand. If the sections are all equally divided into the same length, they are individually referred to as a page. This is the orgin of the term "demand-paged" memory.

### Virtual Memory Structure

Virtual Address Space Page Map Tables

Figure 1-2

If the sections are unequal in length they are called segments, hence "segmented" memory. This paper will only be concerned with the former, demand-paged memory.

At the start of execution of a user's program, the first page is brought into primary memory. This is done by the virtual memory module, which will be explained in sextion 1.7.2. As each instruction is executed, the virtual memory module checks to make sure that all the address space referenced is in primary memory. If the address space is not in primary memory an interrupt, called a page fault (2), is generated. The operating system then processes this interrupt. This is done by loading the required page into primary memory. The process is then restarted from the point of the interrupt. Each additional required page is brought into primary memory upon request.

This can obviously lead to the point where primary memory is full when a new page is being requested by the virtual memory module to be brought into primary memory. To alleviate this situation page replacement (1) is necessary. This consists of removing from primary memory a page that does not have a high probability of being referenced in the near future. This page is then placed in secondary memory while the newly requested page is moved into primary memory.

### 1.2.2.2 ADVANTAGE OF VIRTUAL MEMORY

Virtual memory is commonly used today by many large computers.

There are many advantages to be gained by using virtual memory.

Some of these advantages include:

- (1) Increase in the number of programs that can be multiprogrammed in a system.

- (2) Capability of running a program whose address space exceeds the primary memory space currently available, if less than the maximum addressable memory.

- (3) Makes programs more portable from large machines to small machines.

- (4) Helps eliminate fragmentation of dynamic storage allocation.

These are especially appealing to mini-computers since mini-computers by nature have a smaller primary memory space.

## 1.3 SUPPORT FOR EMULATORS

For use in this paper, we will define an emulator to be a firmware interpreter. This interpreter will convert a user program from the original language, instruction by instruction, into the desired computer actions. An emulator written for this system must be aware of the manner in which to access the virtual addressing system of the host processor. An emulator will not create a machine language program. Instead, it will in effect execute a small microprogram for each instruction of the original language. The result of this activity will be the execution of the original instruction.

The host machine's user assembler language itself will be emulated by HIMICS to allow virtual memory capabilities. HIMICS will

also allow "high-level" Languages to be emulated. Languages such as PL/1, APL, and COBOL are likely candidates for emulation. These languages will require a large amount of space for their emulators, but due to the virtual storage capabilities of the system, this space requirement does not present a problem.

### 1.4 INTER-EMULATOR COMMUNICATION

In many programming situations, it is desirable to use different languages for different modules of the program. For example, one might want the processing portion of his algorithm to be coded in an assembler language, and the input/output sections written in a high-level language. Such process linkage will be allowed in this system. Interprocess communication will also be allowed in this system due to the capabilities of the host machine's operating system. A task or emulated process can start another task executing. After starting another task, the calling task may wait until the named task terminates. The calling task on the other hand may also continue processing and test for the called task's completion when necessary. A task can also cancel another task which is executing. This kind of communication is solely dependent upon the functions of the host operating system.

### 1.5 MANAGEABLE SOFTWARE

The key to manageable software is to keep it simple. This can be accomplished by using a structured design (3). In this

approach a complex system is divided into small independent modules. This allows one to comprehend each module without keeping the details of the entire system in mind. Furthermore, modifications to the system are simplified since a module can be changed or added without affecting other modules.

A part of this structured design is provided by the operating systems of the host processors. Even if the operating systems have to be modified to run in a virtual memory paging environment, it is worth the trade-off. These modules are not only structured, they will be almost error free from the start, and thus more manageable. Obviously it would require a great deal of time to produce the equivalent modules from scratch.

### 1.6 INSTRUMENTATION

#### 1.6.1 RECORDED COUNTS

In order to evaluate a system's efficiency it is necessary to employ techniques to record the specific actions taken by the system. An obvious method of instrumentation is to keep a count of how many times a pre-specified event occurs. By knowing the system input, and the actions caused, it is possible to evaluate the system.

There are two counts which must be taken for every instruction.

The first is a count for each unique operation code. When evaluating the system, the frequency of execution of each kind of instruction is essential. The second count records the number of times each

page is referenced. This will be used to evaluate the performance of the system under different paging options.

### 1.6.2 WORKING SET OPTIONS

Built into the system at system generation time is the ability to perform paging under one of three options. These three options have been choosen to yield different working set (1,8,9) sizes in order to evaluate the system under various work loads for maximum efficiency. In this paper, working set size refers to the number of pages contained in Level 1 and Level 2 memory. This composes a collection of the program's most recently used pages (11). The terms Level 1 memory and Level 2 memory will be explained in detail in section 1.8.2 of this chapter. The first option operates under a non-competitive fixed partitioned working set size. The second option will allow the system to operate with a competitive variable working set size based on a local paging rate. The third option, which operates on a competitive variable working set size also, is based on a global scale and allocates secondary memory using the LRU stack (1,10) principle.

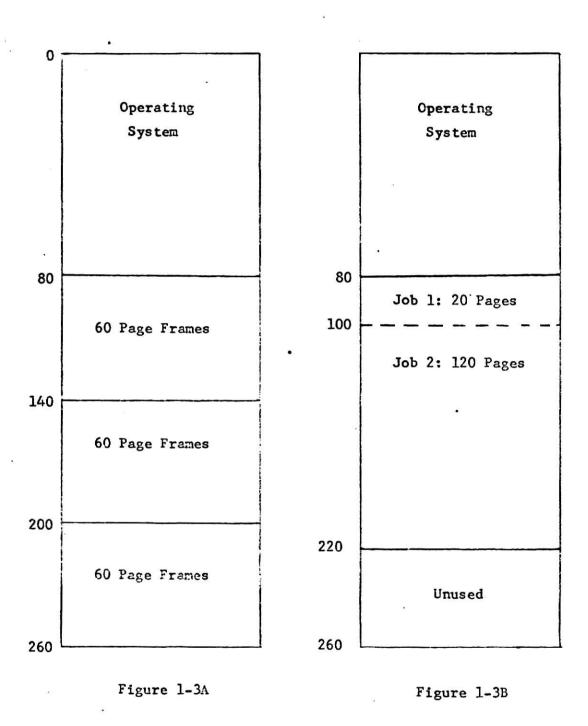

Under option one, the total amount of secondary memory will be divided by the total number of jobs allowed to be multi-programmed. This will be set at system generation time. Each job will then have a fixed working set the same size as any

other job. For example, if there are 180 page frames and 3 jobs, each job will have 60 page frames for its use. (See Figure 1-3A). Under option two the size of the working set for a job will be adjusted to approach maximum efficiency as best as can be determined. This will be based on a competitive paging ratio computed on a per-job paging rate over a given time period. Jobs having high paging rates tend to increase their working set size while low paging jobs decrease their working set size.

Option three will take the entire working set available and let all jobs have the space needed on a first come first use basis. This treats the Level 2 memory on a global basis, whereas under option one it was treated on a per-job basis or local level. This will allow, for example, two jobs, job 1 needing 20 page frames and job 2 needing 120 page frames, to be completely contained in Level 2 memory at once. (See Figure 1-3B). Under option one above, the fixed size per job, job 2 could only have 60 of its 120 pages in Level 2 memory at once.

Obviously in order to tell which of the above three methods is the best, monitoring of the different options is necessary. This will include a count of the number of page faults occurring out of each memory level for each job under the given option. There will also be an option to turn monitoring on or off.

# 1.7 OVERVIEW OF THE SYSTEM

The HIMICS system may be viewed as a hierarchical structure (4,11). A structure of this nature consists of modules located

Figure 1-3

on different hierarchical levels (See Figure 1-4). This type of structure is called "layered insensitivity" (4,11). The levels are insensitive because each level is allowed to call upon the services of levels immediately above or below it in the structure, but not those levels farther than one level away. This means that each level is not concerned about how or where things are done in the levels above it or subordinate to it, and treats them all as one level. Each level may be referenced by the level above or below it in the hierarchy, but no level maybe dependent on a level which is not a logically sequential level in the hierarchy structure. For example, level 4 of the HIMICS system will interface with the file management system level 5, and virtual storage management level 3, but level 4 may not call upon levels 1, 2, or 6.

### 1.7.1 ADVANTAGES OF SYSTEM DESIGN

There are several advantages to this type of design.

- (1) The system is easier to understand.

- (2) Each module is easier to implement.

- (3) The verification of the entire system is accomplished by verifying each individual level in a bottom-up fashion.

- (4) Modification of the system is simplified.

- (5) The software system is relatively portable (i.e. interfacing with different hardware requires only the lowest level of the system to be compatible, and the upper levels do not require modification).

# Rierarchical Structure

|                                                                                      | _       |

|--------------------------------------------------------------------------------------|---------|

| User Process                                                                         | Level 1 |

| Virtual Processors                                                                   | Level 2 |

| Virtual Storage Management                                                           | Level 3 |

| Processor Resource Allocation and Synchronization and Message Handler - Multiplexing | Level 4 |

| File Management System                                                               | Level 5 |

| Peripheral Management                                                                | Level 6 |

Figure 1-4

#### 1.7.2 EXPLANATION OF LEVELS

A short explanation of what is contained in each module follows.

Level 1 contains the user processes which are interpreted and

executed in the primary memory of the host machine. These user

programs may be written in any language supported by an emulator

on the HIMICS system.

contained in Level 2 are the virtual processors. This is the system of emulators which execute one instruction of the user's program at a time. Before each instruction is executed the current real address of the virtually addressed operands must be retrieved. Therefore all memory references must be detected and sent to level 3 to be converted before the emulation of the instruction may occur.

Level 3 contains the virtual storage management system. This system must detect any page faults which are generated from the virtual addresses of the instruction's operands. The virtual addresses of the operands must be converted to real machine addresses. This of course requires the page to be located in primary memory. This management system must interact with the file management system through the message handler in level 4 to retrieve pages to primary memory.

The message handler and resource allocation systems in level 4 are intermeshed deeply with the operating system of its host machine. The message handler is responsible for the generation

and control of all information transfer from the file management system. This communication will consist of I/O messages to and from level 6, page requests from secondary memory in level 5, and the current state of the system (i.e. "request page", "page being transferred"). This message exchange coordinates the activities of levels 5 and 6 with the upper 4 levels of the system.

The file management system will reside at level 5. It will handle all page requests between secondary and primary storage.

All input and output messages will be processed by the file management system upon request. Included in the file management module will be tables which contain the current location of each job's pages. These tables are initialized when the job is started, and are updated as pages are moved from one level of memory to another. Level 4 will send page requests and I/O messages through the message handler requesting pages to satisfy page faults and I/O requests when needed.

Level 6 is the peripheral management module. This module will handle the interface with all peripheral devices connected to the system. This may include printers, card readers, teletypes, display terminals, or whatever hardware is available to interface with the system.

### 1.8 IMPLEMENTATION

We have just presented a machine independent description of the virtual addressing system for a mini-computer system. Now a more detailed description of the implementation of the system at Kansas State University will be presented.

### 1.8.1 HARDWARE ALLOCATION

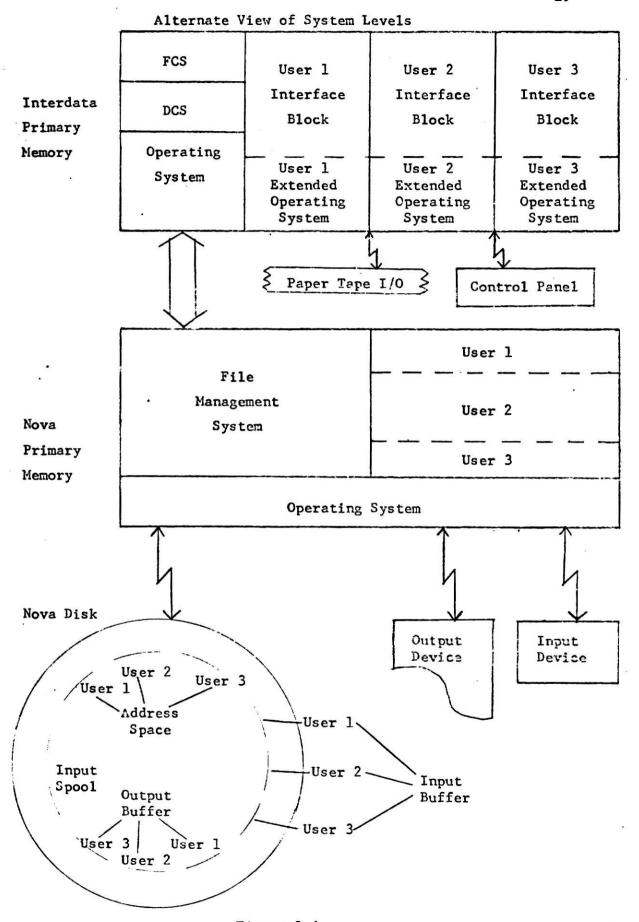

The layered insensitivity graph in Figure 1-5 makes the allocation of duties to actual hardware transparent. As can be seen, the upper four modules will be located in an Interdata 85 computer. The lower two levels will be located in a Nova computer.

The upper four levels are located in the Interdata machine because of its greater processing speeds. The extensive software required by the HIMICS system for each user instruction requires a fast processor. The Interdata cycle time of 270 nanoseconds meets these general speed requirements. The Nova machine is used as a peripheral processor. This processor will have more time to perform its duties, and yet removes a great processing overhead from the Interdata. This setup lets each machine do what it does best, and allows a more efficient and faster system. Using two CPU's in effect allows parallel processing. Real I/O may be supervised by the Nova while the Interdata is processing a user's program. Another view of the system design is given in Figure 1-6. The system shown is based on a multiprogramming environment of three users.

#### 1.8.2 MEMORY LEVELS

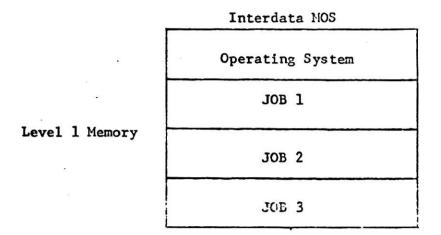

It is apparent from Figure 1-6 that the use of two separate CPU's primary memory, and disk memory creates three levels of

# Hardware View of Hierarchical Structure

Figure 1-5

Figure 1-6

memory. These three levels will be referred to as Level 1,

Level 2 and Level 3 memory in the remainder of this paper (see

Figure 1-7). The Nova disk is the lowest level of memory or

Level 3 memory. Each user's program upon entry to the system

is spooled to an input file in this third level of memory by

the Nova. When the user's job is set to running, the program is

put into his address space, also located on Nova disk, Level 3

memory. The data input is stored in his input file. Any out

put generated by his program will be spooled onto his cutput

file for printing when his job terminates.

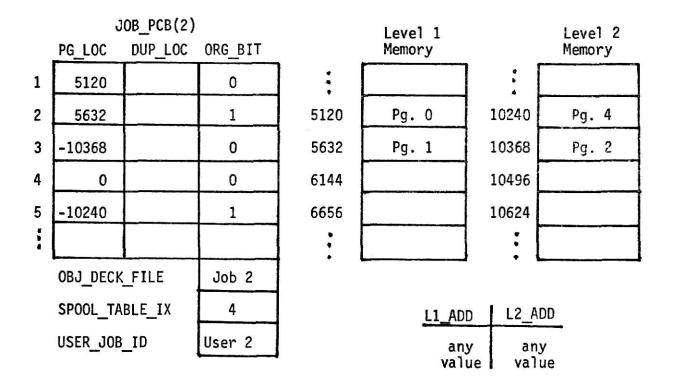

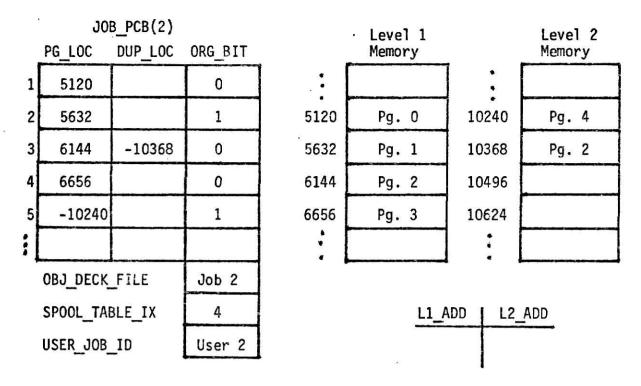

Nova primary is the second level of memory for this system. The management system which controls all page traffic in the Nova is located here. This file system receives page traffic from the Interdata, and using its own paging algorithm, rearranges the user's pages in the extended page space in the Nova's Level 2 memory. If a page is being transferred to Level 3 memory (i.e. paged out of Level 2 memory), it is copied back to the address space only if it is an original page. If a page in Level 2 memory is requested by the Interdata to satisfy a page fault, a bit is kept to record whether or not this page is original to the address space in Level 3 memory. If it is, then the page must be copied back to the user's address space before being overwritten when paged out of the Nova's Level 2 memory.

Operating System

JOB 1

Level 2 Memory

JOB 2

JOB 3

Figure 1-7

This file management system must have tables which keep track of the pages located in its Level 2 memory and Interdata Level 1 memory and all of the user's files located in Level 3 memory. This management system must also interact with the Interdata. All I/O communication and messages must be received and handled by this system.

The first level of memory is located in the Interdata.

Located in Level 1 memory will be the user's PCB (Process

Control Block). Each user will have space for a fixed number

of pages of his program, along with a page table containing

information necessary to handle page faults and address mapping.

### 1.8.3 LOCATION OF SOFTWARE

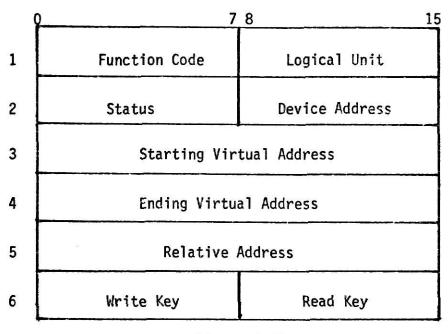

I/O SVC parameter blocks are created in the user's extended operating system in Level 1 memory. These parameter blocks are needed to inform the peripheral processor of the type of I/O which is to be done. Also the task identification, virtual page number, interval timer and starting and ending location must be included in the parameter block. These parameter blocks are built and then passed to the Nova system.

The FCS (fixed control store) is read only memory which contains the Interdata machine language instruction interpreter.

The I/O instructions will not be interpreted by an emulator as are other instructions, but will be interpreted by the program located

in the FCS. The dynamic control store (DCS) will contain the language emulator. The address translator, which recognizes and handles page faults and virtual to real address translations, will also be stored in the DCS portion of the Interdata Level 1 memory. The proposed design may be likened to that of a single system. Level 1 Interdata memory corresponds to primary memory. Level 2 Nova core memory, and Level 3 Nova disk memory corresponds to secondary memory.

### 1.9 SUMMARY

In order to bring the overall picture of the HIMICS system into focus a short summary of the system will be given. This system will be in a multiprogramming environment. Each user will initially have 64K of virtual address space at his disposal. All real I/O will occur in the Nova. A user's source program will be spooled into an input buffer on the Nova's disk. The source program will then be copied onto the user's virtual address space also located on the Nova disk. The user's data will be put in his input file on the Nova disk. The user's source program will be divided into fixed length pages. Each user's program will be given a starting virtual address of zero. As soon as the user's job is set to running by the Interdata operating system, a PCB is created in the Interdata memory. The page table will be located in this PCB.

This table will be empty when the job becomes running. A page table is also set up in the Nova Level 2 memory.

Immediately after a job is started, a page fault will be generated in the Interdata. Page zero will be requested, and paged in from Level 3 memory to Level 1 memory. The system is now ready to begin execution of the program.

The emulator is given the current instruction to process.

All operands must be converted to real addresses. When the page needed is not located in the Interdata, a page fault is generated and processed. When all operands are mapped, the instruction may be interpreted. The instruction counter is incremented, and the next instruction is executed (unless the previous instruction was a jump of some kind).

A special case is encountered when the end of a job is reached.

An I/O SVC must be generated to the Nova to empty the output

buffer to the output device. Then a job termination message will

cause the address space, buffers, and Nova core page space to be

released. The Interdata extended operating system then terminates

the job in the Interdata, and a new user's job is initiated.

# 1.10 INTRODUCTORY DESCRIPTION OF REMAINING CHAPTERS

The remainder of this paper will be concerned with levels five and six, which are the levels contained in the Nova. (See Figure 1-5.) Levels one through four are included in a report by Smith (5).

Chapter two will include a general discussion of the paging algorithms, and page migration patterns. Chapter three will dwell on the implementation of the system. This will include algorithms and data structures for implementation. Chapter four will be a short summary of the HIMICS system and a concluding survey of future work which could be done on the system.

### 2.1 INTRODUCTION

The three main functions the Nova performs in the system are, page management, file management and Input/Output for the system. In this chapter page management will be analyzed in detail. Different page flow patterns will be traced through the system. Three different paging options will be discussed and high level algorithms will be given for their implementation. File management and I/O for a general system will be discussed, but not in detail, since the operating system being used in this implementation will handle most of this for the system. I/O for this system will be discussed in detail in Chapter Three.

### 2.2 PAGE MANAGEMENT

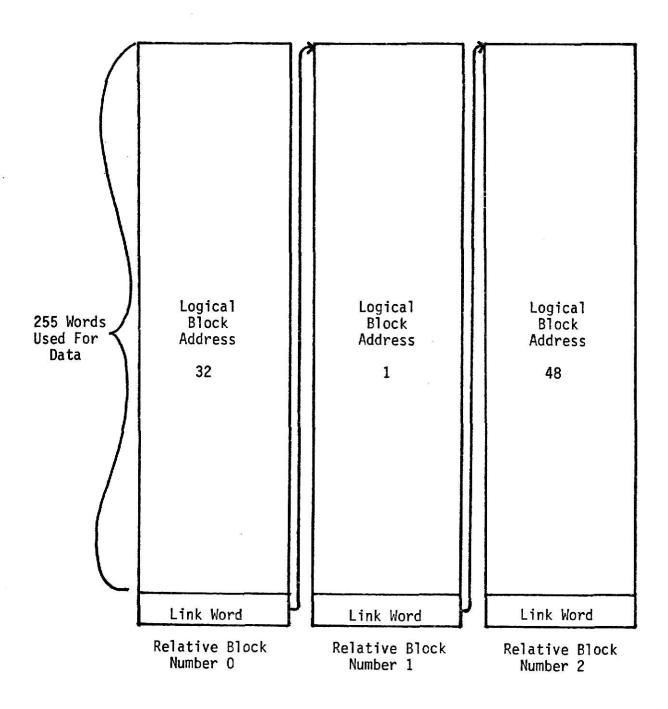

Programs executing in a virtual memory environment, using demand-paging, are brought into main memory in fixed length blocks called pages. Most systems use page sizes ranging from 256 to 1024 words. For the system being implemented in this paper a natural choice for the page size is 256 words. This is because the particular disk drive being used in this implementation reads and writes in blocks of 256 words, with each word being 16 bits long.

### 2.2.1 THRASHING IN PAGED MEMORY SYSTEMS

Thrashing (8, 13) is a troublesome phenomenon which may seriously interfere with the performance of paged memory systems.

It is characterized by too much paging. This causes the processor to be idle a high percentage of the time while performing the actual page transfers. This excessive overhead can cause severe performance

degradation or even collapse of the system. The prime cause of paging's performance degradation is the large time required to access a page stored in auxiliary memory. This is due to the rotation and head positioning times associated with most secondary memory devices.

In the implementation proposed in this paper the secondary memory access time will be minimal or transparent to the overall efficiency of the system. This is due to two main stratigies in the design of the system. The first is in the use of three levels of memory, see Figure 1-7, as opposed to the normal two levels of memory. In this proposed system the second level of memory will be directly addressable core located in a Nova mini-computer. Thus the page transfers between Level 1 memory and Level 2 memory will be much faster since they are a core to core type transfer as opposed to a rotational device to core transfer. The second reason is the fact that this proposed system has a dedicated minicomputer to handle the paging. This achieves parallel processing. Thus when one task goes blocked because of a page fault, the host machine can continue processing other tasks while the requested page is being paged in by the second processor. Even if the requested page is in the third level of storage, in effect we have eliminated the wait time in the system since it continues to do parallel processing.

### 2.2.2 PAGING OPTIONS

The Nova will handle paging for the system under one of three options. The option the system will run under will be set at

system generation time. These options will include the ability to run the system under:

- (1) A competitive variable working set size based on local paging rate.

- (2) A competitive variable working set size based on a global scale.

- (3) A non-competitive fixed partitioned working set size.

The system is being designed with these three options so that statistical data of the system can be recorded and performance evaluation analysis made of the system under the various options.

The layout of Level 2 memory for these options are shown in Figures 2-1A thru 2-1C.

Under Option 1, the competitive variable working set size based on local paging rate, each job has a portion of Level 2 memory. See Figure 2-1A. This portion of memory is variable as represented by the wavy lines. The portion each job has depends upon that job's paging rate and the availability of Level 2 memory. A job having a high paging rate tends to increase its working set size while a job with a low frequency paging rate will decrease its working set size.

In Figure 2-18, Option 2, the competitive variable working set size based on a global scale, a job is given the next available page frame when a page fault is encountered if one is available. If all the page frames are in use, then the page that has been unused the longest is paged out (LRU) (1). The job then uses this vacated page frame. The LRU algorithm is applied globally to determine which page is to be removed if all page frames in Level 2 memory are

| Page Option 1    | Page Option 2                                                   | Page Option 3    |  |

|------------------|-----------------------------------------------------------------|------------------|--|

| Operating System | Operating System                                                | Operating System |  |

| Job 1            | Job 3 Pg. 0  Job 1 Pg. 1  Job 2 Pg. 0  Job 1 Pg. 0  Job 3 Pg. 1 | Job 1            |  |

| Job 2            | Job 3 Pg. 2  Job 3 Pg. 3  Job 3 Pg. 4  Job 3 Pg. 5  Job 3 Pg. 6 | Job 2            |  |

| Job 3            |                                                                 | Job 3            |  |

| Local            | Global                                                          | Fixed            |  |

| Figure 2-1A      | Figure 2-1B                                                     | Figure 2-1C      |  |

Figure 2-1

in use. Thus under this option a single job may use all of Level 2 memory. This will be explained in detail in section 2.2.5.2.

Under Option 3, the non-competitive fixed partitioned working set size, the amount of Level 2 memory is partitioned into areas of equal size. See Figure 2-1C. The size of each area is determined by dividing the total size of Level 2 memory by the number of partitions. Any remainder of page frames will be distributed by adding to each job one page frame, starting with Job 1, until all remaining page frames have been distributed. For example, if 5 jobs are to be multiprogrammed and there are 19 page frames (19/5=3 remainder 4), the five partitions would have 4, 4, 4, 4 and 3 page frames respectively. These calculations and allocations of Level 2 memory are set at system generation time and are static.

## 2.2.3 WORKING SET SIZE

Working set size used above refers to the number of pages a program has in Level 1 memory, plus the number of pages it has in Level 2 memory at a given time. The working set size will therefore be a variable with respect to time. For example, Job 1 may have 30 pages in Level 1 memory and 20 in Level 2 memory giving it a working set size of 50 pages at some time (T<sub>i</sub>). At T<sub>i+10</sub> it may have 30 pages in Level 1 memory and 25 in Level 2 memory, giving it a working set of 55 pages. See Figure 2-2.

## 2.2.4 PAGING TRANSFER FLOW PATTERNS

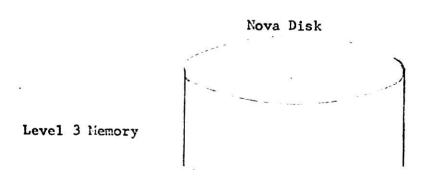

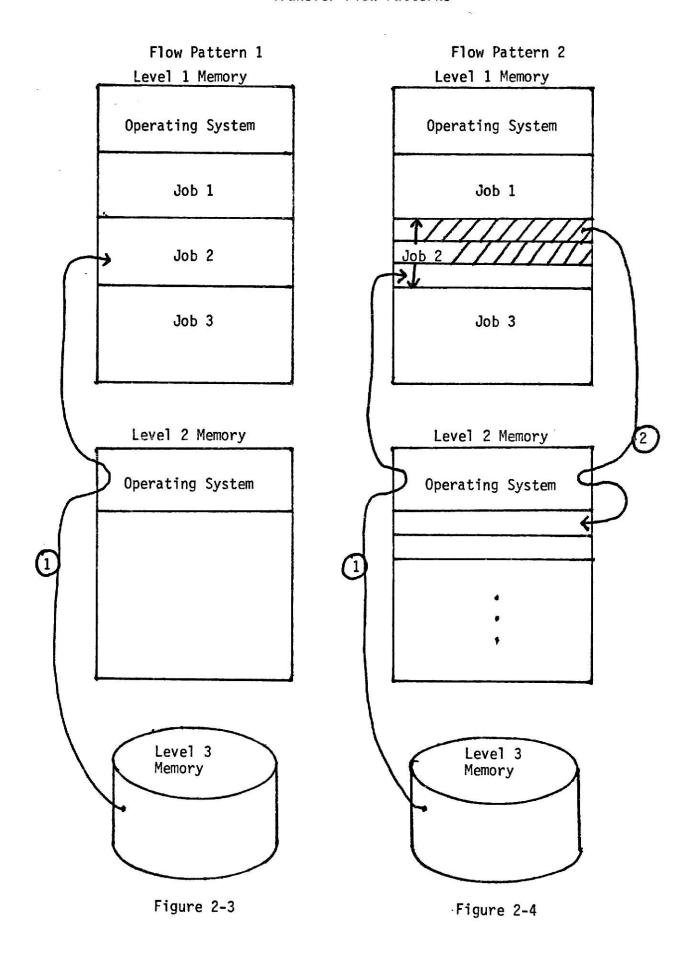

Paging in the system can follow one of four transfer flow patterns. These patterns, or sequences of page transfers are given in Figures 2-3 thru 2-6.

# Working Set Size

| Interdata        |                | Interdata        |

|------------------|----------------|------------------|

| Operating System | eta.           | Operating System |

| Job 1 30 pg.     |                | Job 1 30 pg.     |

| Job 2 25 pg.     | Level 1 Memory | Job 2 30 pg.     |

| Job 3 30 pg.     | zeve. z namovy | Job 3 30 pg.     |

| Job 4 5 pg.      |                | Job 4 15 pg.     |

| Nova             |                | Nova             |

|------------------|----------------|------------------|

| Operating System |                | Operating System |

| Job 1 20 pg.     | -              | Job 1 25 pg.     |

| Job 2 0 pg.      | N.             | Job 2 5 pg.      |

| Job 3 10 pg.     | Level 2 Memory | Job 3 O pg.      |

| Job 4 0 pg.      |                | Job 4 0 pg.      |

| Job | Working Set Size<br>(Level 1 + Level 2 Memory) |      |  |

|-----|------------------------------------------------|------|--|

| 000 | Time T <sub>i</sub> Time T <sub>i+10</sub>     |      |  |

| 1   | 50                                             | 55   |  |

| 2   | 25                                             | 35   |  |

| 3   | 40                                             | 30   |  |

| 4   | 5                                              | . 15 |  |

Figure 2-2

## Transfer Flow Patterns

#### 2.2.4.1 TRANSFER FLOW PATTERN 1

The simplest transfer is shown in Figure 2-3. This transfer is from Level 3 memory to Level 1 memory. All jobs will initially start with this type of transfer. This is because all jobs are initially spooled to Level 3 memory and before execution can begin the first page has to be transferred into the Interdata's Level 1 memory. The Interdata will issue a request to start this transfer. This type of transfer, Level 3 memory to Interdata Level 1 memory, will continue for each page fault request by a job until that job's Level 1 memory space partition in the Interdata is filled. This partition size will be set at system generation time and will vary depending on how many jobs are set to be multiprogrammed.

#### 2.2.4.2 TRANSFER FLOW PATTERN 2

This type of transfer is shown in Figure 2-4. It occurs when a page fault is requested by a job and there are no page frames available in that job's working set in the Interdata's Level 1 memory. There is always one page frame available for the transfer, but it is not counted in the job's working set. In this transfer a page is transferred from Level 3 memory, to Level 1 memory. Since this takes away the transfer page frame in Level 1 memory, a page has to be paged out of Level 1 memory. This is to allow future page faults an empty page frame into which they can be transferred. This is used for efficiency. If the extra page frame was not available, a page would first have to be transferred out of Level 1 memory before the new page could be transferred in. With the extra page frame, the page to be transferred out can be transferred after

the new page has been transferred in. This allows the process, that caused the page fault, to continue executing in the Interdata while the outgoing page is being transferred to a lower level of memory by the Nova. This flow pattern will continue until the job's Level 2 memory in the Nova is filled, or a page is requested that resides in Level 2 memory. Then flow pattern 3 or 4 will preside.

#### 2.2.4.3 TRANSFER FLOW PATTERN 3

This type of transfer is shown in Figure 2-5. It occurs when a page fault is encountered by the Interdata and the page requested is in the Nova's Level 2 memory. The transfer into the Interdata's Level 1 memory is the same as under transfer flow pattern 2, except the page is copied from the Nova's Level 2 memory instead of from Level 3 memory. This core to core transfer is much faster than the disk to core transfer. This is because the disk to core time has to include a disk seek time for the Read/Write heads on disk to be positioned in order to read a page from disk. This seek time runs on the average of 50-100 milliseconds and is very time consuming compared to the core to core transfer time of approximately 250 microseconds. This is the main reason for the extended page memory system being extended into the Nova's Level 2 memory.

The second part of the transfer, the paging out of Interdata

Level 1 memory into Nova Level 2 memory introduces two new

possibilities. One is the possibility that the page to be paged

out already has an identical copy existing in Level 2 memory. The

other is that there is not an identical copy of it. This includes

the case where there was an identical copy of the page to begin with, but the page while in the Interdata was changed, hence two identical copies do not exist. If the page has been changed in the Interdata it is flagged as an original by the Interdata. If the page to be paged out is an original it needs to be recopied. If it is not an original it need not be recopied. If it does not need to be recopied it saves the transfer time. These two possibilities will always exist whenever a page fault is encountered and a previous copy of the page existed in the lower of the two levels of memory prior to the page fault. In this case lower level memory being a higher level number (i.e. Level 1 memory is the highest and Level 3 the lowest).

#### 2.2.4.4 TRANSFER FLOW PATTERN 4

This is the most complex page flow pattern in the system.

It is shown in Figure 2-6. Before this type of flow can occur four conditions must exist. First, the job creating the page fault must have all its page frames in Level 1 memory in use. Second, all the page frames available for that job in Level 2 memory must be in use. Third, the page being paged out of Level 1 memory must not have an identical copy residing in Level 2 memory. And fourth, the page causing the page fault must reside in Level 3 memory.

As can be seen in Figure 2-6, the requested page is copied from Level 3 memory into Interdata Level 1 memory. This takes the transfer page from Level 1 memory in the Interdata. A page thus has to be released to recreate the transfer page frame. A page is selected by the Interdata to be paged out to the Nova Level 2 memory.

This frees up a page frame in the Interdata for the next transfer, but in turn takes away the Nova's transfer page frame in Level 2 memory. It therefore has to select a page for removal. This page is then moved to Level 3 memory. This releases a page frame from the Nova's Level 2 memory to be used for the next page fault to Level 1 memory. This completes the cycle.

The goal of this hierarchal memory system is to maximize the number of times pages are in the faster memory levels when being referrenced. This implies that flow pattern 3, Figure 2-5, is the desired page flow pattern we wish to achieve in this system. This is because the core to core transfer is much faster than the disk to core transfer as noted previously.

## 2.2.5 PAGING ALGORITHMS USED IN SYSTEM

In this implementation, using two mini-computers and 3 levels of memory, two paging systems will be used. One to handle the paging between Level 1 and Level 2 memory and the other to handle paging between Level 2 and Level 3 memory. Paging between Level 1 and Level 2 memory will be handled by a Least Recently Used (LRU) (1) approximation algorithm called a Not Used Recently (NUR) (1). The algorithm will be implemented in the host machine. Its implementation is dealt with in detail in a paper by Smith (5). We will look briefly at its logic in order to better understand the paging algorithm necessary between Level 2 and Level 3 memory. Also the reason why the NUR was preferred over the LRU in the host machine is discussed.

The LRU selects for removal the page that has not been referenced for the longest period of time. It is based on the theory that if a page is referenced, it is likely to be referenced again soon. Conversely, if it has not been referenced for a long time, it is unlikely to be needed in the near future. The LRU implies that a time has to be recorded each time a page is referenced. Then when a page is to be removed all these times have to be compared to find which one has been present the longest. This is too time consuming to be done using software and is the reason the NUR is preferred for this implementation.

The NUR approximates an LRU by setting a reference bit associated with the referenced page to 1 everytime the page is referenced. Periodically the reference bits are reset to 0. Thus anytime a page has a 0 reference bit it is known the page has not been referenced since the last time the bit was reset to 0. This means the page has not been used recently and is a candidate for removal. This in turn implies that at any given time, Level 1 will contain the most recently used pages for that period of time, which is the LRU approximation.

The pages that are removed from Level 1 memory are moved into Level 2 memory. Thus Level 2 memory is an extension of Level 1 memory, and will at a given time still contain the most recently used pages.

The paging algorithm being implemented between Level 2 and Level 3 memory will be a true LRU and not an approximation. The reason this can be done at this level and not above is that Level

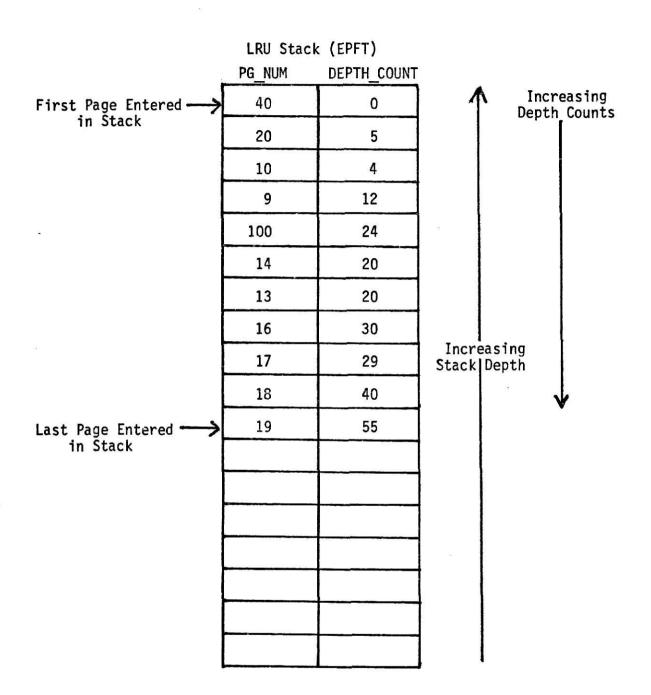

2 memory is not directly addressable by the user's program. Thus if a page in Level 2 memory is accessed, it is through the operating system. Each time a page is accessed it is moved out of Level 2 memory and this eliminates the need to keep the access times associated with the page, as was described above. Instead a First-in/First-Out (FIFO) stack (1) is kept of all the pages in Level 2 memory. This then is the LRU stack (10). Thus the first page paged into Level 2 memory is the least recently used and will be paged out first when Level 2 memory is full and a new page is to be moved from Level 1 memory to Level 2 memory.

## 2.2.5.1 PAGING ALGORITHM DISCUSSION FOR OPTION 1

Under Option One, paging in the system will be based on a competitive variable working set size. This means that a job's working set size is allowed to expand or contract. This size change will occur in Level 2 memory. This is because Level 1 memory is a fixed size for each job and is set at system generation time. The determining factor as to whether a job's working set size is changed is based upon its current paging rate compared to its past paging rate. If its current paging rate is significantly slower, then one page is paged out of its working set and the page frame put on a free list for use by other programs. If its current rate is faster, and there is a free page frame available, then its working set size is increased by one page frame. Note, this implies one job may never pre-empt a page frame from another job. It only gets a page if there is one available. In other words the algorithm is applied on a "LOCAL" basis. This means a job's working set stays intact despite the other programs paging activity with which it shares

memory. There is also the case where the past paging rate and the current paging rate are about the same. In this case the working set size is not changed. In this initial design, if the current paging rate is within plus or minus 10% of the previous page rate, the working set size will not change. This will be implemented so that it can be changed as the paging behavior will have to be monitored in the system before an optimum range can be determined.

Before presenting the high level algorithm we will look again at the hierarchy structure of the memory levels and make a few notes. In Figure 1-7 we displayed the three levels of memory in the system. Also it should be remembered that the working set size was defined as the total sum of pages a job has in Level 1 memory plus Level 2 memory, Figure 2-2. As noted above, Level 1 memory is a fixed size. Thus looking back at the 4 transfer flow patterns (Figures 2-3 thru 2-6) it can be seen that increasing a job's working set size will only be effective in reducing the paging rate in flow pattern 4, Figure 2-6. This is because in flow pattern 1 and 2, Level 2 memory for the job is not yet saturated and in flow pattern 3 increasing the size of Level 2 memory for a job will not reduce paging as the paging being done is already within the job's working set. This leaves us to only be concerned with flow pattern 4.

The page fault rate is based on a time variable. This time variable being the length of CPU time that has elapsed for the given task between page faults. When a page fault occurs, this interval time is saved to be compared against when the next page fault occurs.

Initially it will be set to zero. When a page fault occurs, the current fault rate time is compared against 90% of the previous fault rate time to see if the rate of paging has increased by a factor of at least 10%. This indicates a faster rate of paging. If so a check is made to see if there is an available page frame for use. If there is, then this task's working set size is increased by one page. If the above tests fail, then a check is made to see if the rate of paging has decreased by a factor of 10%. This is done by comparing the current fault rate against 110% of the previous fault rate. If the current fault rate is greater than 110% of the previous fault rate, indicating a slower paging rate, then the working set size for the task is decreased by one. page. If the fault rate has neither increased or decreased by 10%, then the task's working set size remains the same. current fault rate is then stored as the previous fault rate to be used when the next page fault occurs.

The algorithm given below will be entered each time a page migration between Level 2 and Level 3 occurs with the exception of a page migration for I/O. I/O will be discussed in section 2.3.2. It has no bearing on working set size but can cause page migrations between memory levels.

High Level Algorithm For Option 1

ENTER PG\_OPTION\_1(JOB\_ACC\_TIME)

- 1. CURRENT\_FAULT\_RATE=JOB\_ACC\_TIME-PREVIOUS FAULT RATE

- 2. IF CURRENT\_FAULT\_RATE<PREVIOUS\_FAULT\_RATE\*90% AND

THERE IS AN AVAILABLE PAGE FRAME THEN

- 2.1 INCREASE WORKING SET SIZE BY 1

- 3. ELSE IF CURRENT\_FAULT\_RATE>PREVIOUS\_FAULT\_RATE\*

110% THEN

- 3.1 DECREASE WORKING SET SIZE BY 1

- 4. PREVIOUS FAULT RATE=CURRENT FAULT RATE

- 5. RETURN

- 6. END

## 2.2.5.2 PAGING ALGORITHM DISCUSSION FOR OPTION 2

Under this option, the competitive variable working set size,

Level 2 memory is treated on a "GLOBAL" scale. The algorithm is

implemented by using an LRU stack. When a page migration occurs

between Level 1 and Level 2 memory the job is given the next available

page frame if one exists. If Level 2 memory is saturated, then the

LRU stack is checked to see which page in Level 2 memory has been

unreferrenced the longest. This page is then paged out to Level 3

memory, regardless of which job it belongs to, and its vacated page

frame used by the requesting job.

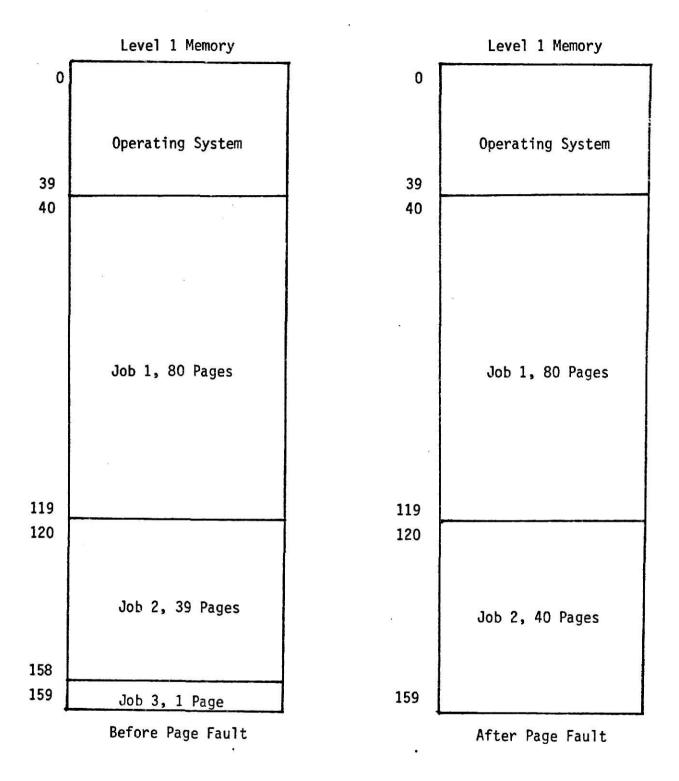

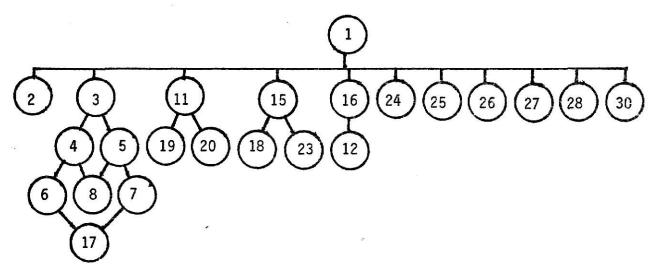

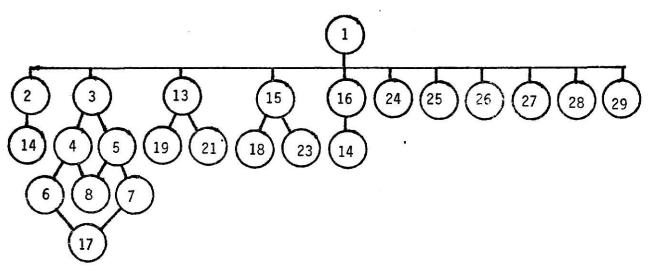

For example, take 3 jobs. Job 1 has 80 pages in Level 2 memory, Job 2 has 39 and Job 3 has 1. See Figure 2-7. Let the number of page frames available be set to 120. Let the order of request be such that Job 3's page is the oldest page. Let the next page fault be issued by Job 2. This will cause Job 3 to lose its only page in Level 2 memory and Job 2's new page to be put on top of the LRU stack.

This is shown to illustrate that 1 or 2 jobs may dominate the Nova's Level 2 memory. This may be advantageous as some small jobs, or jobs which display a high degree of locality (8,9) may

## Memory Domination Under The Competitive Variable Working Set Size Option

Figure 2-7

never need secondary storage, or at least not a large amount of it.

The high level algorithm for page Option 2 is presented next.

High Level Algorithm For Option 2

ENTER PG ALG OPTION2(JOB#)

- 1. CHECK FOR EMPTY PAGE FRAME

- 2. IF ONE EXISTS THEN

- 2.1 USE AVAILABLE PAGE FRAME

- 3. ELSE CHECK LRU STACK AND TRANSFER TO LEVEL 3 MEMORY

THE PAGE THAT HAS BEEN RESIDENT THE LONGEST IN

LEVEL 2 MEMORY AND USE THIS NEWLY RELEASED PAGE

FRAME

- 4. RETURN

#### 2,2,5,3 PAGING ALGORITHM DISCUSSION FOR OPTION 3

Under this fixed size working set option, the total number of page frames available will be divided by the number of jobs being multiprogrammed. Each job will then have a fixed maximum number of pages that it may use. For example, if there are 90 page frames of Level 2 memory and 3 jobs are running, each job may have a maximum of 30 pages of Level 2 memory (90/3=30). Each job will then use its 30 pages as an LRU stack for paging operations. The logic of the algorithm is the same as in option two. The difference is that option two has a global pool of page frames and option three has a local pool of page frames. The high level algorithm for option 3 is given below.

High Level Algorithm For Option 3

ENTER PG ALG OPTION3(JOB#)

- 1. IF PG FRAMES IN USE(JOB#) <= TOTAL AVAILABLE THEN

- 1.1 USE AVAILABLE PAGE FRAME

- 2. ELSE OBTAIN THE LEAST RECENTLY USED PAGE FROM LRU

STACK, MOVE THE LRU PAGE TO LEVEL 3 MEMORY AND

USE GIVEN PAGE FRAME

- RETURN

#### 2.2.6 THRASHING AS RELATED TO PAGING OPTIONS

The least amount of thrashing should be exhibited by option one. This is because of two things. First, the algorithm is applied on a local basis. This means excessive paging by jobs in the system will not influence the other job's paging rate. Second, the working set size for a job is allowed to expand or contract if its local paging rate indicates it to be desirable. This will tend to reduce thrashing caused by a fixed partition size as in option three. This is because the critical region causing thrashing may be only 1 or 2 pages. Under the fixed option, the extra 1 or 2 pages can never be included in the job's working set, whereas under option 3 the working set for the job will have the opportunity to increase its size the extra several pages it needs.

The most amount of thrashing should occur under option two, the global competitive working set option. This is due to the global nature of the algorithm, which means jobs will be pre-empting pages from each other. In order for a job to pre-empt a page from

another job, flow pattern 4 (Figure 2-6) must be the pattern followed. This could cause severe CPU wait time in the host machine due to the high speed page transfer between Level 1 and Level 2 memory and the slow speed between Level 2 and Level 3 memory. See Figure 2-6.

## 2.3 I/O FOR SYSTEM

There will be two basic types of I/O processing handled by the Nova for the system. The first will be the I/O which will take care of the spooling of jobs in the system. The second type will handle program requested data transfers during program execution.

#### 2.3.1 SPOOLING OF I/O

A user's program and unit record input data are initially spooled to disk in the user's virtual address space, starting at virtual address 0. The source program will be divided into fixed length page segments of 256 words each as it is being spooled. Upon completion of a job, all output for the job has been spooled to disk. The Nova then dumps this output to the printer or other output device as requested by the job.

## 2.3.2 PROGRAM REQUESTED I/O

Program requested input will be handled similar to a page fault. When the user program request input, a message is sent to the Nova by the Interdata. This message will include the starting and ending virtual addresses of the area that the data is to be read into. The Interdata will then lock the page or pages of the I/O data area in, in Level 1 memory if they are currently residing

in Level 1 memory. This is done so that the associated page(s) do not become candidates for removal during I/O. Next the page that contains the beginning virtual address of the I/O area is located. If it is in Level 1 or Level 2 memory, then the I/O is performed to its corresponding real addresses. Next its page map table entries are updated. If the page is located in Level 3 memory, it first has to be copied to an I/O work buffer located in Level 2 memory. Then the I/O is performed to the work buffer and the page transferred back to its Level 3 address. If the virtual addresses span more than one page, then each succeeding page is treated in the same manner as described above until all the I/O has been completed.

## 2.4 FILE MANAGEMENT

File management in this implementation will only be concerned with that which is necessary to do the paging and the I/O spooling. The main reason for this restriction is hardware. The present system only has one disk and it is being dedicated to I/O spooling and Level 3 memory usage in the system.

The following file management system is described for a system which allows dynamic allocation of core. Since the system being used for the actual implementation of this system does not allow dynamic allocation, the implementation version given in chapter three will vary from the following description. This version is included here as it is a more general version.

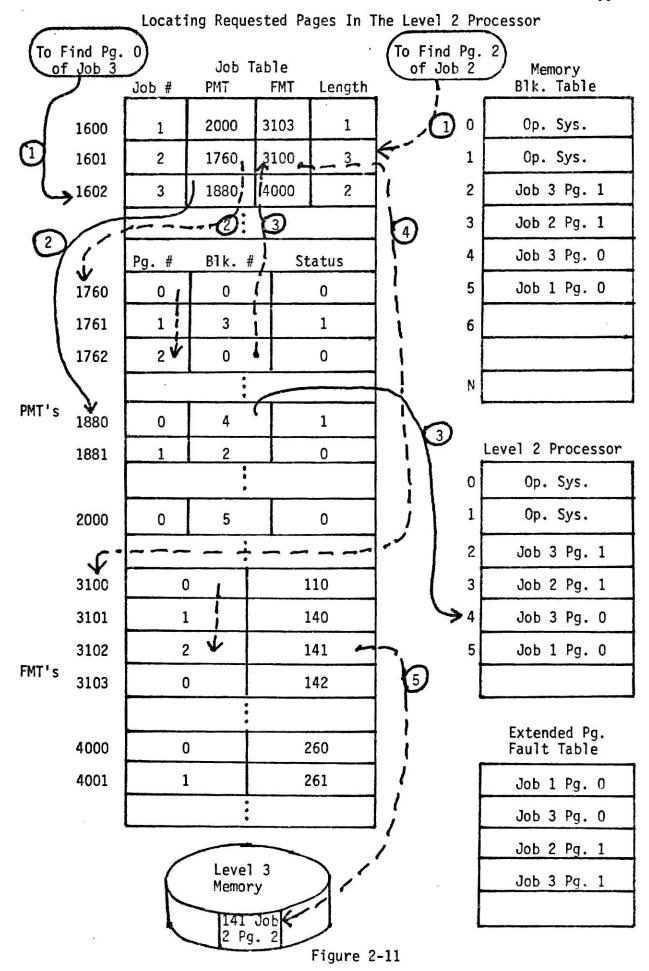

### 2.4.1 DATA BASES FOR FILE MANAGEMENT

This system will use seven types of tables to handle the file management and paging. They are:

- (1) Spool Table (ST).

- (2) Disk Usage Sector Table (DUST).

- (3) Memory Block Table (MBT).

- (4) Job Table (JT).

- (5) Page Map Table (PMT).

- (6) File Map Table (FMT).

- (7) Extended Page Fault Table (EPFT).

The spool table (Figure 2-8), keeps track of the files associated to a unique job. For initial implementation this table will remain in Level 2 memory. In an actual production environment it could become necessary to move it to Level 3 memory due to its potential size, as every job entered in the system will have an entry in the spool table. Entry one in the spool table contains a unique job identification number for each job entering the system. Entry two contains that job's source deck file name. Entry three contains the file name of the job's data input, if any exist. Entry four contains the file name of the job's object deck. Entry five contains the job's output file name. This output file will be dumped to the designated output device at the close of a job.

The Disk Usage Sector Table (DUST), Figure 2-9, is used to store the status of each sector of the disk. Each sector on disk will have a corresponding bit in the DUST table to represent whether the sector is in use or not. A 0 in the table means the sector is not in use. A 1 indicates the sector is in use. A bit map (1)

Spcol Table

|     | Job ID | Source Deck<br>File ID | Data Deck<br>File ID | Obj. Deck<br>File ID | Output<br>File ID |

|-----|--------|------------------------|----------------------|----------------------|-------------------|

| 1   | J100   | J101                   | J200                 | J98                  | J112              |

| 2   | J71    | J72                    | J73                  | J74                  | J75               |

| 3   |        |                        |                      | 500 000              |                   |

| 4   |        |                        | 6                    |                      |                   |

| 5   |        |                        |                      |                      |                   |

| :   |        |                        |                      |                      |                   |

| 100 |        |                        |                      |                      |                   |

|     | 1      | 2                      | 3                    | 4                    | 5                 |

|     |        |                        | Figure 2-8           |                      |                   |

<u>D</u>isk <u>U</u>sage <u>S</u>ector <u>T</u>able (DUST)

Figure 2-9

is used because it takes up less storage in the system.

The Memory Block Table (MBT), Figure 2-10A, will consist of two parts. A block number, one for each 256 words of storage in Level 2 memory, and the status of the block that is associated with it. The status will tell if a given block is in use, and if so who has it. There will be one MBT located in the system. It is used for dynamic allocation of storage by the operating system for the various tables.

The Job Table (JT), Figure 2-10B, will consist of four parts. The first entry will contain a job number for each job running in the system. The second entry will contain that job's starting address of its page map table. The third entry will contain the job's file map table starting address. The last entry will be the job's length in number of pages. There will be one JT for the system. The JT's main use is to save core. If it were not used each PMT and FMT for each job would have to be given a specific location in core. Furthermore, they would each have to be allocated to hold the maximum number of pages. With the job table, core for the PMT and FMT can be allocated according to the length of the job running.

There will be one Page Map Table (PMT), Figure 2-10C, per job. It will consist of two entries. Entry one will be the address where the page is located in memory. Entry two will be the status of the page. This will indicate if the page is an original. An original page is a page that has been changed in a higher level of memory but not changed in its virtual address space in Level 3

| Memory Block Table |             |  |  |  |

|--------------------|-------------|--|--|--|

| B1k. #             | Status      |  |  |  |

| 0                  | Op. Sys.    |  |  |  |

| 1                  | Op. Sys.    |  |  |  |

| 2                  | Job 3 Pg. 1 |  |  |  |

| 3                  | Job 2 Pg. 1 |  |  |  |

| 4                  | Job 3 Pg. 0 |  |  |  |

| 5                  | Job 1 Pg. 0 |  |  |  |

| 6                  | Free        |  |  |  |

| •                  | 387         |  |  |  |

| N                  |             |  |  |  |

| Figure 2-10A       |             |  |  |  |

|                    |             |  |  |  |

|                    |             |  |  |  |

| <u>File Map Table</u> |

|-----------------------|

| 110                   |

| 140                   |

| 141                   |

| 142                   |

|                       |

|                       |

| 260                   |

| 261                   |

|                       |

Figure 2-10D

|       | Length   |          |        |

|-------|----------|----------|--------|

| Job # | Loc. PMT | Loc. FMT | (pgs.) |

| 1     | 2000     | 3103     | 1      |

| 2     | 1760     | 3100     | 3      |

| 3     | 1880     | 4000     | 2      |

|       |          |          |        |

Figure 2-10B

| (ACTION A) ATT | Map <u>T</u> able<br># Status |

|----------------|-------------------------------|

| 0              | 0                             |

| 3              | 1                             |

| 0              | ,0                            |

|                |                               |

|                |                               |

| 4              | 1                             |

| 2              | 0                             |

|                |                               |

|                |                               |

| 5              | 0                             |

|                |                               |

|                |                               |

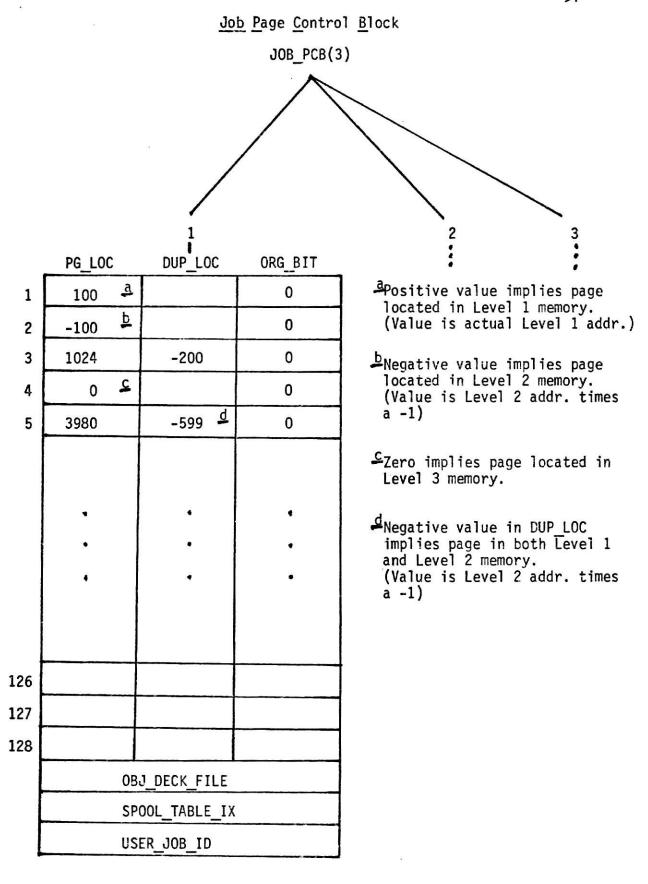

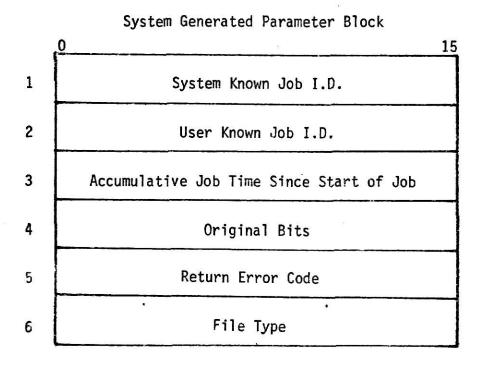

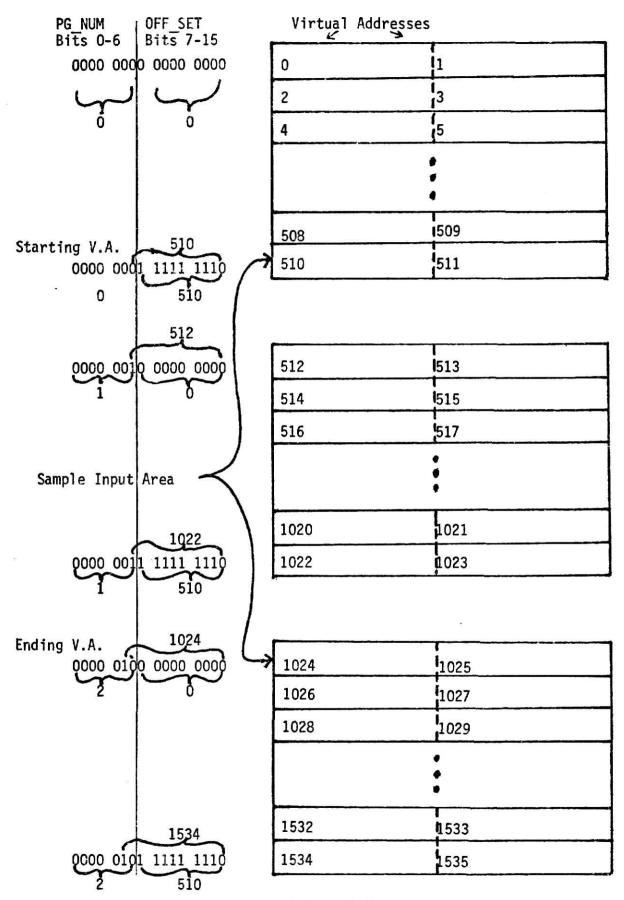

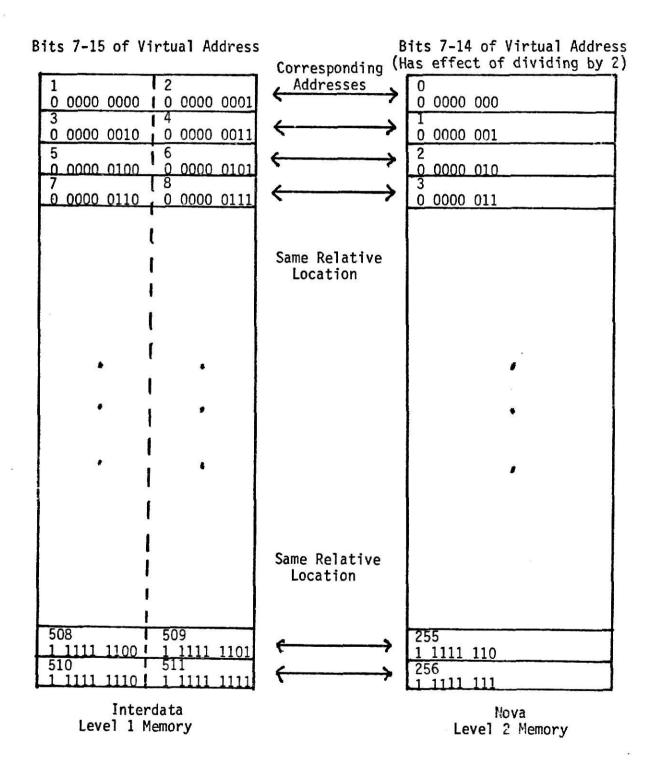

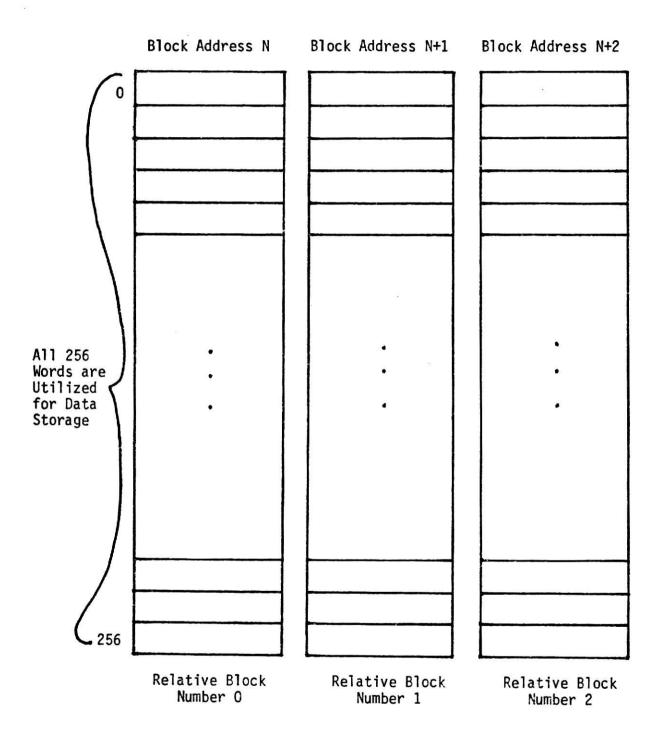

|                |                               |