#### MITIGATING OSCILLATOR PULLING DUE TO MAGNETIC COUPLING IN MONOLITHIC MIXED-SIGNAL RADIO-FREQUENCY INTEGRATED CIRCUITS

by

#### IAN DAVID SOBERING

B.S., Kansas State University, 2012

#### A THESIS

submitted in partial fulfillment of the requirements for the degree

#### MASTER OF SCIENCE

Department of Electrical and Computer Engineering College of Engineering

> Kansas State University Manhattan, Kansas

> > 2014

Approved by:

Major Professor Dr. W. B. Kuhn Copyright © 2014 Ian David Sobering All rights reserved

#### Abstract

An analysis of frequency pulling in a varactor-tuned LC VCO under coupling from an on-chip PA is presented. The large-signal behavior of the VCO's inversion-mode MOS varactors is outlined, and the susceptibility of the VCO to frequency pulling from PA aggressor signals with various modulation schemes is discussed. We show that if the aggressor signal is aperiodic, band-limited, or amplitude-modulated, the varactor-tuned LC VCO will experience frequency pulling due to time-modulation of the varactor capacitance. However, if the aggressor signal has constant-envelope phase modulation, VCO pulling can be eliminated, even in the presence of coupling, through careful choice of VCO frequency and divider ratio. Additional mitigation strategies, including new inductor topologies and system-level architectural choices, are also examined.

The analysis is then applied to improve a fully-integrated half-duplex UHF microtransceiver in which signal coupling between the LO and PA caused frequency pulling that prevented the use of QPSK signaling at certain data rates. We determine that a VCO operating at  $4 \times$  transmit frequency will be naturally insensitive to pulling from QPSK signals. To validate the proposed solution, a prototype IC containing a pair of QPSK transmitters with integrated 100 mW Class-C PAs was designed and fabricated in 0.18 um SOI. The transmitters—one utilizing a  $2 \times$  VCO, one utilizing a  $4 \times$  VCO were designed to closely match the performance of the original microtransceiver when transmitting QPSK data. The transmitter with the  $2 \times$  VCO experienced frequency pulling from the PA while transmitting QPSK data, but the transmitter with the  $4 \times$ VCO did not, thereby confirming the analysis in this work.

A revision of the microtransceiver was designed in  $0.5 \,\mu\text{m}$  SOS utilizing an offchip PA inductor to reduce signal coupling with the VCO. A second revision of the microtransceiver with two prototype transmitters was designed in  $0.25 \,\mu\text{m}$  SOS utilizing  $4 \times$  VCOs and figure-8 VCO inductors for maximum insensitivity to pulling from QPSK and band-limited modulation, as well as other design improvements that leverage the higher  $f_t$  of the smaller process. Both revisions also include a hardware FSK modulator, a new charge pump, and a redesigned fractional-N synthesizer to attenuate a divided-reference spur in the IF output. These revisions of the radio will enable future researchers to focus on system-level applications where highly-integrated medium-power transceivers with fully-functioning IQ modulation are needed.

# Contents

| Li       | st of | Figures                                                                 | vii |

|----------|-------|-------------------------------------------------------------------------|-----|

| Li       | st of | Tables                                                                  | x   |

| A        | ckno  | wledgments                                                              | x   |

| 1        | Intr  | roduction                                                               | 1   |

|          | 1.1   | Problem Overview                                                        | 1   |

|          | 1.2   | Literature Review                                                       | 3   |

|          | 1.3   | Thesis Outline                                                          | 4   |

| <b>2</b> | Cou   | pling Mechanisms in Integrated Circuits                                 | 7   |

|          | 2.1   | Substrate Coupling in Bulk CMOS                                         | 7   |

|          | 2.2   | Substrate Coupling in SOI                                               | 8   |

|          |       | 2.2.1 Thin-Film SOI                                                     | 9   |

|          |       | 2.2.2 Thick-Film SOI                                                    | 9   |

|          | 2.3   | Electric Field Coupling Between Interconnects                           | 10  |

|          |       | 2.3.1 Metal Fill                                                        | 12  |

|          |       | 2.3.2 Electric Field Coupling Mitigation Strategies                     | 13  |

|          | 2.4   | Magnetic Field Coupling                                                 | 13  |

|          |       | 2.4.1 Magnetic Coupling Mitigation Strategies                           | 15  |

|          | 2.5   | System-Level Coupling                                                   | 15  |

|          | 2.6   | Summary                                                                 | 16  |

| 3        | Free  | quency Pulling in the K-State Microtransceiver                          | 18  |

|          | 3.1   | Identification of the LO Pulling Mechanism                              | 18  |

|          | 3.2   | Magnetic Coupling                                                       | 20  |

|          |       | 3.2.1 Coupling Between the 100 mW PA and the VCO $\ldots \ldots \ldots$ | 23  |

|          |       | 3.2.2 Coupling Between the T/R Switch and the VCO $\ldots \ldots$       | 26  |

|          |                | 3.2.3 Simulation of the PA-VCO Magnetic Coupling Path 27                                                                                                             |

|----------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 3.3            | Capacitive Coupling                                                                                                                                                  |

|          | 3.4            | Additional Coupling Paths                                                                                                                                            |

|          | 3.5            | Summary                                                                                                                                                              |

| 4        | The            | e Differential Cross-Coupled LC VCO 36                                                                                                                               |

|          | 4.1            | The K-State Microtransceiver VCO                                                                                                                                     |

|          |                | 4.1.1 LC Tank Properties                                                                                                                                             |

|          |                | 4.1.2 Frequency of Oscillation                                                                                                                                       |

|          | 4.2            | Inversion-Mode MOS Varactors                                                                                                                                         |

|          |                | 4.2.1 Large-Signal Varactor Capacitance                                                                                                                              |

| <b>5</b> | Free           | quency Pulling in an LC VCO Under Magnetic Coupling 43                                                                                                               |

|          | 5.1            | Analysis of a VCO Under Magnetic Coupling                                                                                                                            |

|          | 5.2            | Frequency Pulling due to Modulation                                                                                                                                  |

|          |                | 5.2.1 Amplitude Modulation                                                                                                                                           |

|          |                | 5.2.2 Constant-Envelope Phase Modulation                                                                                                                             |

|          |                | 5.2.3 Band-Limited Modulation                                                                                                                                        |

|          | 5.3            | Additional Coupling Paths    48                                                                                                                                      |

| 6        | Pul            | ling Mitigation Strategies in Integrated Transceivers 50                                                                                                             |

|          | 6.1            | Operating Frequency                                                                                                                                                  |

|          |                | 6.1.1 Frequency Upconversion                                                                                                                                         |

|          | 6.2            | Inductor Counterwinding                                                                                                                                              |

|          | 6.3            | Figure-8 Inductors                                                                                                                                                   |

|          | 6.4            | PA Topology                                                                                                                                                          |

|          | 6.5            | Summary                                                                                                                                                              |

| 7        | $\mathbf{Des}$ | ign of a Prototype $2 \times /4 \times$ VCO QPSK Transmitter IC 62                                                                                                   |

|          | 7.1            | Transmitter Architecture                                                                                                                                             |

|          |                | 7.1.1 $2 \times \text{ and } 4 \times \text{VCOs} \dots \dots$ |

|          |                | 7.1.2 Frequency Synthesizer                                                                                                                                          |

|          |                | 7.1.3 $I/Q$ Modulator                                                                                                                                                |

|          |                | 7.1.4 Exponential-Horn Pad Driver                                                                                                                                    |

|          |                | 7.1.5 Class-C Power Amplifier                                                                                                                                        |

|          | 7.2            | Performance                                                                                                                                                          |

|          | 7.3            | Summary                                                                                                                                                              |

| 8  | Revisions to the K-State Microtransceiver |                                                                                             |    |  |

|----|-------------------------------------------|---------------------------------------------------------------------------------------------|----|--|

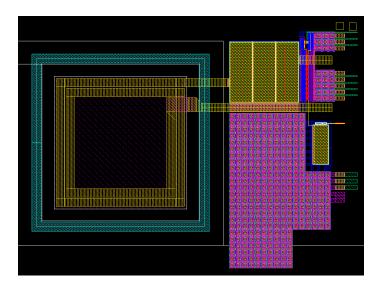

|    | 8.1                                       | K-State Microtransceiver Revision 6a                                                        | 76 |  |

|    |                                           | 8.1.1 External 100 mW PA Inductor $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 76 |  |

|    |                                           | 8.1.2 Attenuating the 4.8 MHz Divided-Reference Spur                                        | 78 |  |

|    |                                           | 8.1.3 Direct-Modulation FSK                                                                 | 78 |  |

|    |                                           | 8.1.4 Additional Improvements                                                               | 81 |  |

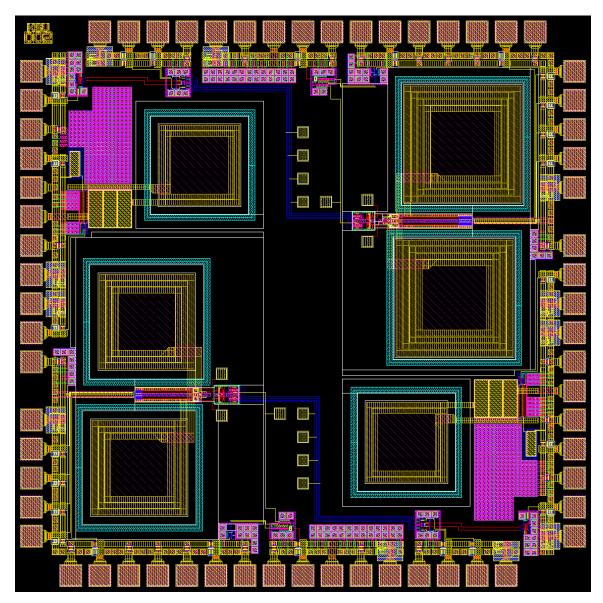

|    | 8.2                                       | K-State Microtransceiver Revision 6b                                                        | 81 |  |

| 9  | Con                                       | nclusion                                                                                    | 85 |  |

|    | 9.1                                       | Future Work                                                                                 | 87 |  |

| Bi | bliog                                     | graphy                                                                                      | 89 |  |

# List of Figures

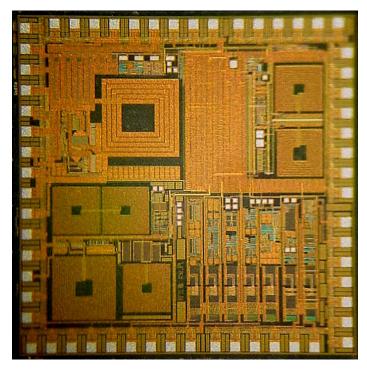

| 1.1  | Photograph of the K-State Microtransceiver                                       | 2  |

|------|----------------------------------------------------------------------------------|----|

| 2.1  | Cross-section of a typical bulk CMOS substrate                                   | 8  |

| 2.2  | Substrate coupling paths in thin-film SOI.                                       | 9  |

| 2.3  | Substrate coupling paths in thick-film SOI                                       | 10 |

| 2.4  | Capacitive coupling paths in SOI                                                 | 11 |

| 2.5  | Example of floating fill metal patterns in a six-metal 0.18 $\mu m$ SOI process. | 13 |

| 2.6  | Mutual inductance and the dot convention                                         | 14 |

| 3.1  | Block diagram of the K-State Microtransceiver.                                   | 19 |

| 3.2  | Fab 5 BPSK and RC-BPSK performance at 10 kbps                                    | 21 |

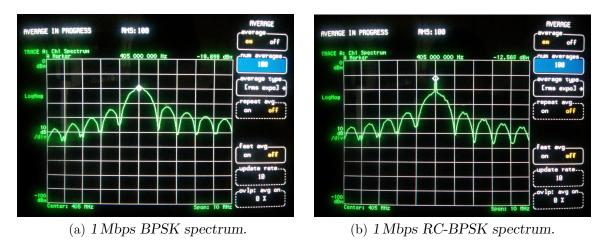

| 3.3  | Fab 5 BPSK and RC-BPSK performance above 1 Mbps                                  | 21 |

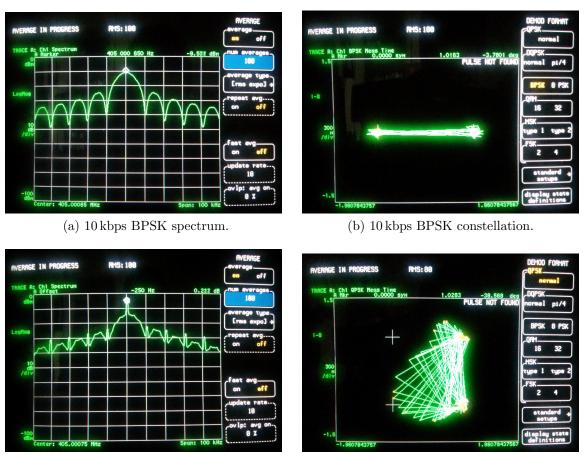

| 3.4  | Fab 5 10 kbps BPSK and QPSK performance using the $100\mathrm{mW}$ PA            | 22 |

| 3.5  | Inductor locations in the K-State Microtransceiver.                              | 24 |

| 3.6  | ADS Momentum simulation of Fab 5 inductors                                       | 24 |

| 3.7  | Extracted $S_{21}$ , $M$ , and $k$ between Fab 5 PA and VCO inductors            | 25 |

| 3.8  | Voltage induced in the VCO inductors by the 100 mWPA. $\ldots$ .                 | 26 |

| 3.9  | Schematic of the Fab 5 resonant T/R switch                                       | 27 |

| 3.10 | Extracted $M$ and $k$ between the T/R switch and VCO inductors                   | 28 |

| 3.11 | Voltage induced in the VCO inductors by the PA and by the ${\rm T/R}$ switch.    | 29 |

| 3.12 | Simulated open-loop BPSK and RC-BPSK output frequency                            | 30 |

| 3.13 | Location of the top-metal synthesizer ground shield                              | 32 |

| 3.14 | ADS Momentum simulation of Fab 5 inductors with ground shield. $\ .$             | 32 |

| 3.15 | Voltage induced in the VCO inductors by the PA, with and without                 |    |

|      | the top-metal synthesizer ground shield.                                         | 33 |

| 4.1  | Schematic of the K-State Microtransceiver VCO                                    | 37 |

| 4.2  | Fab 5 coarse-tune capacitors and MOS varactors                                   | 38 |

| 4.3  | Fab 5 VCO series half-circuit.                                                   | 38 |

| 4.4        | Fab 5 VCO parallel half-circuit.                                                                                                          | 39      |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 4.5        | Fab 5 VCO full circuit.    .                                                                                                              | 39      |

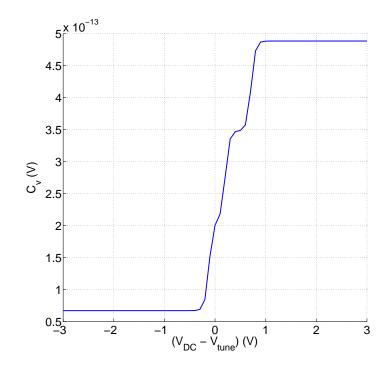

| 4.6        | Fab 5 MOS varactor DC/small-signal C-V curve                                                                                              | 40      |

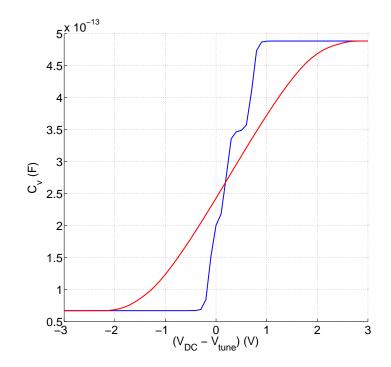

| 4.7        | Fab 5 DC/small-signal and large-signal MOS varactor C-V curves                                                                            | 42      |

| 5.1        | Schematic of the Fab 5 VCO magnetically coupled to an aggressor inductor                                                                  | 44      |

| 5.2        | Parallel half-circuit of the Fab 5 VCO magnetically coupled to an ag-                                                                     | 44      |

| 5.3        |                                                                                                                                           | 49      |

| 6.1<br>6.2 | Illustration of counterwound and non-counterwound VCO inductors<br>Change in Fab 5 output frequency for counterwound and non-counterwound | 53<br>ł |

| 6.3        | VCO inductors                                                                                                                             | 55      |

| 0.0        |                                                                                                                                           | 56      |

| 6.4        |                                                                                                                                           | 57      |

| 6.5        |                                                                                                                                           | 58      |

| 6.6        | Comparison of voltages induced by the PA in counterwound and figure-                                                                      |         |

|            |                                                                                                                                           | 59      |

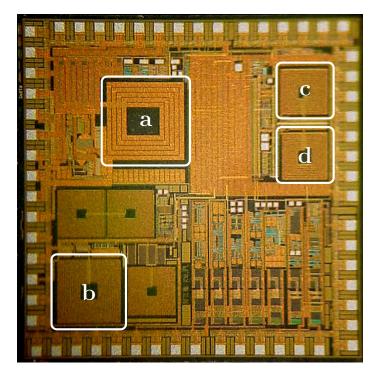

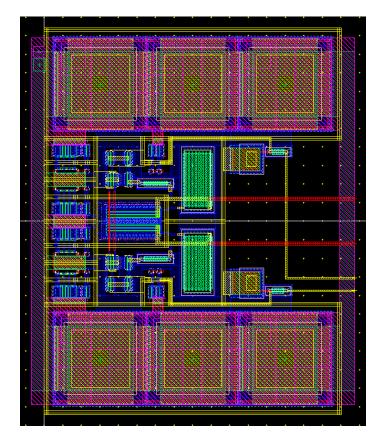

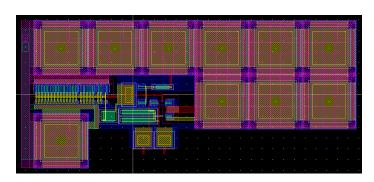

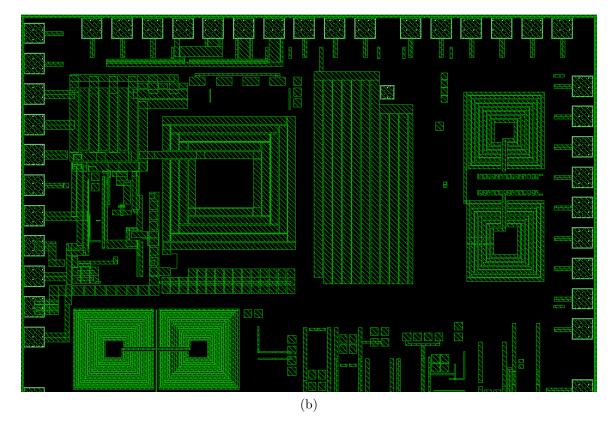

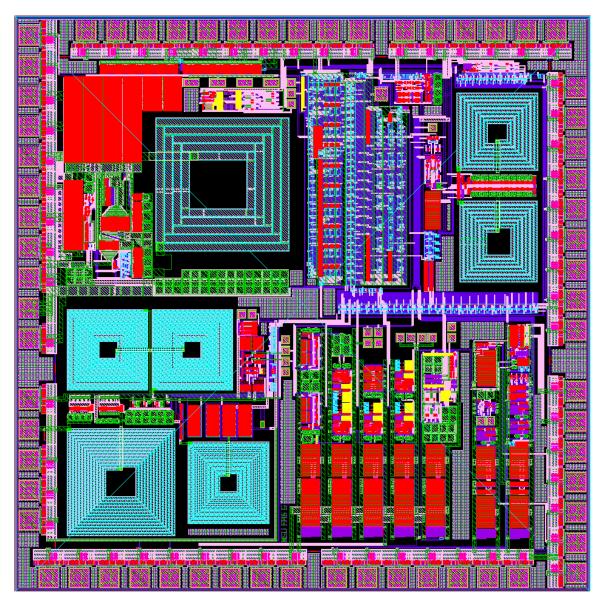

| 7.1        | $2 \times / 4 \times$ VCO QPSK transmitter IC die photograph                                                                              | 63      |

| 7.2        | Block diagram of the $2 \times / 4 \times$ QPSK transmitter test chip                                                                     | 64      |

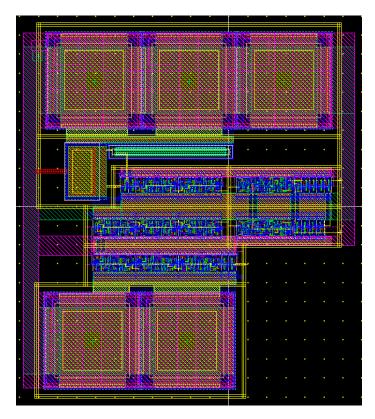

| 7.3        | Integer- $N$ frequency synthesizer layout                                                                                                 | 65      |

| 7.4        | $200\mu\text{A}$ charge pump layout                                                                                                       | 66      |

| 7.5        | $\rm I/Q$ modulator layout. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                | 67      |

| 7.6        | $10 \mathrm{mW}$ PA layout                                                                                                                | 67      |

| 7.7        | $100 \mathrm{mW}$ PA block diagram.                                                                                                       | 68      |

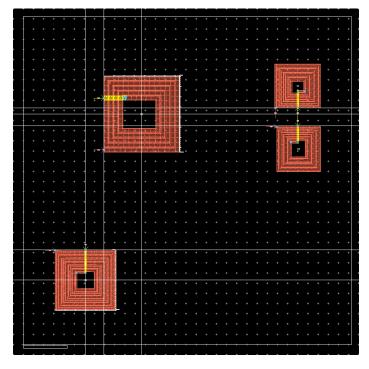

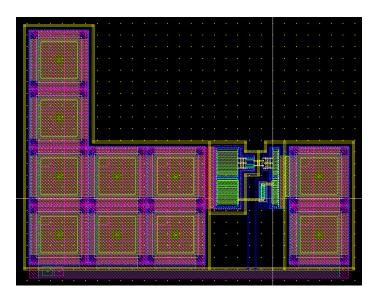

| 7.8        | $2 \times / 4 \times$ VCO QPSK transmitter IC top-level layout                                                                            | 69      |

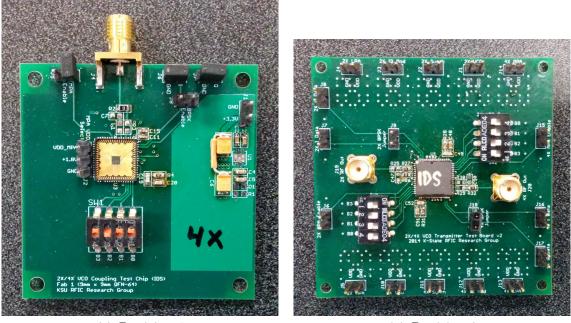

| 7.9        | $2 \times / 4 \times$ VCO transmitter IC test boards                                                                                      | 70      |

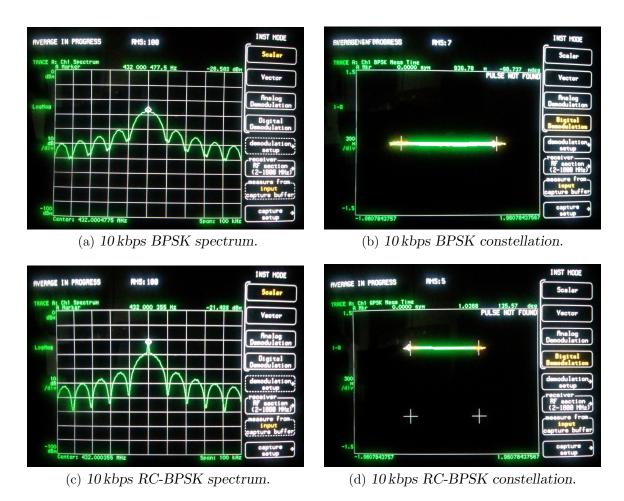

| 7.10       | $2 \times$ VCO BPSK and RC-BPSK performance at 10 kbps                                                                                    | 71      |

| 7.11       | $4 \times$ VCO BPSK and RC-BPSK performance at 10 kbps                                                                                    | 72      |

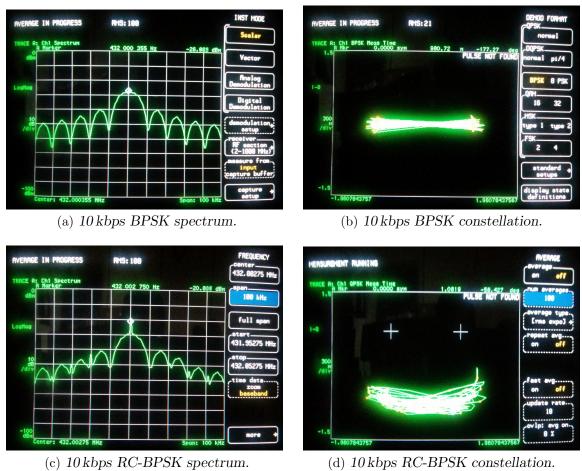

| 7.12       | $2 \times$ VCO BPSK and RC-BPSK performance at 10 kbps                                                                                    | 73      |

| 7.13       | $4 \times$ VCO BPSK and RC-BPSK performance at 10 kbps                                                                                    | 74      |

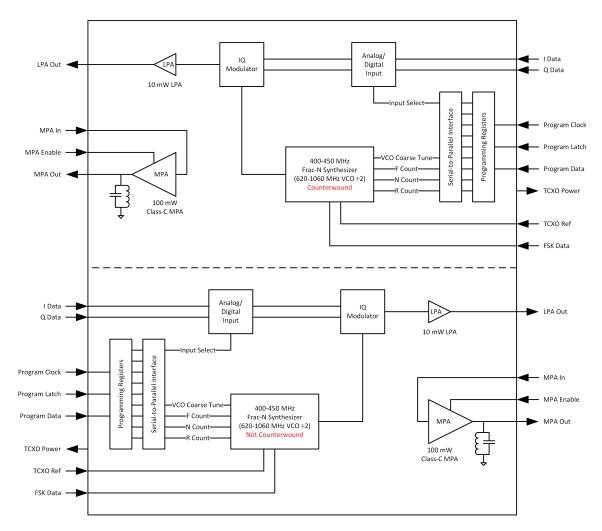

| 8.1        | K-State Microtransceiver Rev 6a block diagram                                                                                             | 77      |

| 8.2        |                                                                                                                                           | 79      |

| 8.3        | Comparison of Rev 5 and Rev 6a top-metal synthesizer ground shields.                                                                      | 80      |

| 8.4 | K-State Microtransceiver Rev 6a top-level layout. | 82 |

|-----|---------------------------------------------------|----|

| 8.5 | K-State Microtransceiver Rev 6b block diagram     | 83 |

# List of Tables

# Acknowledgments

This work was supported in part by NASA EPSCoR grant NNX11AM05A.

The author wishes to recognize David Wiegandt and Dahlon Chu of Sandia National Laboratories, who arranged for the author to attend graduate school under Sandia's Critical Skills Masters Program, and Garth Kraus, also of Sandia National Laboratories, for fabrication of the ICs designed in the course of this research. The author also wishes to acknowledge committee members Dr. Ruth Douglas Miller, Dr. Andrew Rys, and Dr. Don Gruenbacher, for their time and attention, and offers his sincerest thanks to major professor Dr. William B. Kuhn, a practical engineer who instilled in the author a passion for microwave design.

# Chapter 1

# Introduction

This thesis investigates a problem where signal coupling in a fully-integrated ultrahigh-frequency (UHF) microtransceiver caused pulling of its local oscillator (LO), preventing the use of quadrature phase-shift-keying (QPSK) signaling at certain data rates. To identify the source of this problem, all major on-chip coupling mechanisms substrate, electric field, and magnetic coupling—were considered, as well as ground bounce and power supply ripple caused by bondwire inductance.

Substrate and electric field (capacitive) coupling can be easily mitigated using techniques and features available in most modern IC processes. These mechanisms, although present in the microtransceiver to some degree, were found to be well-addressed in the original design. Magnetic coupling, however, is difficult to mitigate because magnetic shielding techniques consume valuable layout area and significantly reduce the Q of integrated inductors. While magnetic coupling was also considered during the original design, it was ultimately found to be the cause of frequency pulling. A system-level architectural solution, rather than a shielding strategy, became the primary focus of this research.

## 1.1 **Problem Overview**

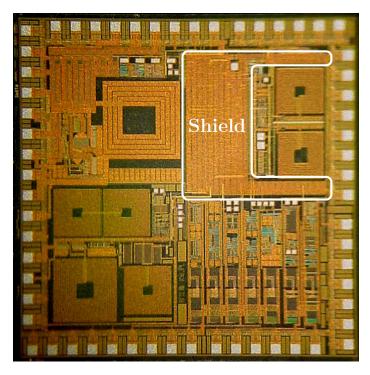

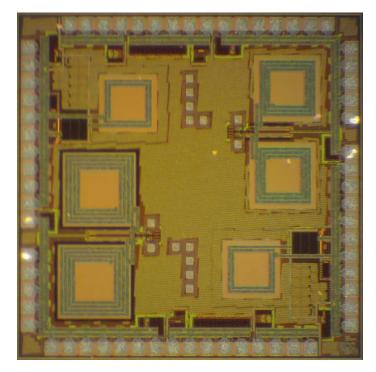

The microtransceiver IC which formed the focus of this research is part of a fullyintegrated half-duplex radio prototyped in 2006 [1]. The K-State Microtransceiver radio-frequency integrated circuit (RFIC), shown in Figure 1.1, operates in the 390– 450 MHz range and is intended to transmit data with binary phase-shift keying (BPSK),  $\pi/2$  residual-carrier BPSK (RC-BPSK), QPSK, and frequency-shift keying (FSK) modulation, with a total power consumption of 50 mW on receive and 100 mW or 300 mW on transmit for 10 mW or 100 mW output power settings. The micro-

Figure 1.1: Photograph of the K-State Microtransceiver.

transceiver was designed to be used in a two-chip or three-chip system consisting of the transceiver RFIC, an FPGA operating as a digital modem, and an optional 1 W CMOS power amplifier [2] for higher-power applications. Both the Microtransceiver and the 1 W PA were fabricated in the  $0.5 \,\mu$ m version of Peregrine Semiconductor's silicon-on-sapphire (SOS) UltraCMOS process. The high substrate resistivity and high  $f_t$  of SOS enables integration of the oscillator, transmitter, receiver, and embedded LC passives on a single  $3.2 \times 3.2 \,\mathrm{mm}$  die. The only external components required are a temperature-compensated crystal oscillator (TCXO), a 10.7 MHz ceramic filter, and surface-mount passives for power supply decoupling.

The K-State Microtransceiver has been used as a radio link in many applications, including UHF propagation studies [3], energy-harvesting research [4], and a prototype body-area network for space suit biomedical sensing [5]. While this radio has been used with both BPSK and FSK modulation in these applications, it was found to experience frequency pulling and constellation smearing when transmitting QPSK with the 100 mW PA active. At data rates greater than 1 kbps, pulling is so severe that the transmitted data could not be demodulated. Previous attempts to identify the cause of the QPSK pulling problem were unsuccessful, and the transceiver was constrained to BPSK and FSK operation. This research began in response to renewed interest in restoring the Microtransceiver's QPSK and related RC-BPSK capabilities as part of a NASA/EPSCoR-funded technology-development effort.

### 1.2 Literature Review

The phenomenon of local oscillator (LO) pulling by feedback from a PA in directconversion and superheterodyne transceiver architectures is widely recognized, as are the dominant coupling mechanisms in integrated circuits [6]. However, the literature contains little information on the precise mechanisms involved in the pulling problem. Bronckers et. al. [7] conducted an investigation of coupling mechanisms between a VCO and a PA in 0.13  $\mu$ m CMOS, but LO pulling is only briefly mentioned, and modulated PA output signals are not considered. While [7] successfully identifies substrate and magnetic coupling as the dominant PA-VCO coupling mechanisms in bulk CMOS, they fail to draw conclusions beyond those already addressed in previous K-State research [1, 8] regarding effective isolation strategies. Physical separation of the LO and PA is consistently cited as the most effective coupling mitigation strategy. However, the maximum achievable separation of the LO and PA in fullyintegrated transceivers is fundamentally limited by the available die area and the size of integrated passives.

The relationship between VCO operating frequency and PA output transmit frequency is also considered in the literature. Many published integrated transceiver designs use LO signals at half the desired frequency [9, 10], twice the desired frequency [11], or fractional thirds [12] to reduce LO pulling by the PA driver and other in-band interferers. Transceiver designs with LO frequencies higher than the transmit frequency are more prevalent because generating I and Q signals through frequency division also provides high I/Q phase accuracy [13]. This method is applied in the existing K-State Microtransceiver for both reasons. Other transceivers employ a direct-upconversion architecture, again for the stated reasons of preventing VCO pulling and reducing in-band spurs [14, 15, 16].

Operating the LO outside the band of interest prevents direct injection-locking of the LO by the PA. However, a frequency and phase relationship still exists between the LO and PA output frequencies in transceivers where I and Q are generated through frequency multiplication or division. The choice of LO frequency and divider ratio appears to be dictated by the preferred method of generating I and Q, not by efforts to mitigate pulling. Direct-upconversion transceiver architectures often provide high levels of integration with low power consumption [15], but require additional filtering to attenuate unwanted sidebands. There is no discussion in this prior art as to the *effectiveness* of frequency multiplication, division, or up-conversion at mitigating LO pulling from the PA.

Another widely-published LO pulling mitigation strategy targeted at non-constant envelope modulation schemes (QAM, CDMA, etc.) advocates the use of digital predistortion (DPD) networks to reject LO pulling while simultaneously linearizing the PA [17, 18, 19]. These methods are effective at mitigating LO self-injection and spectral regrowth in the transmitted signal, but do not address LO pulling due to PA output modulation. Additionally, this strategy is targeted at transceivers that already employ a pre-distortion network to linearize the PA. Constant-envelope modulation schemes, such as unfiltered BPSK, QPSK, and FSK, do not require linear power amplifiers. Hence, due to its complexity, implementing a pre-distortion network in transceivers with constant-envelope modulation schemes solely to mitigate LO pulling is not a desirable solution.

Review of this prior art showed no publications making a clear connection between LO pulling, LO operating frequency, PA output frequency, and modulation in fully-integrated transceivers. This thesis demonstrates that it is possible to design a robust fully-integrated transceiver, even in the presence of unavoidable coupling, by identifying potential on-chip coupling mechanisms and tailoring the transceiver architecture to be naturally insensitive to them.

### 1.3 Thesis Outline

Chapter 2 presents a brief overview of coupling mechanisms and mitigation strategies in modern IC processes. The fundamental limits on the performance of integrated passives—substrate resistivity and metal resistance—are also discussed, as well as issues surrounding on-chip magnetic shielding. We show how magnetic shielding techniques, if attempted, are generally undesirable because they can significantly degrade the Q of integrated inductors. Finally, system-level issues such as power supply crosstalk and ground bounce are briefly addressed.

Chapter 3 identifies two magnetic coupling paths between the 100 mW PA and the VCO in the K-State Microtransceiver. When the 100 mW PA is operating, the PA output is magnetically coupled into the VCO inductors from both the 100 mWPA inductor and the inductor in an integrated resonant T/R switch. Simulations of the microtransceiver transmitting QPSK under coupling from both aggressors closely match the transceiver's measured performance. A potential capacitive coupling path between the PA and VCO through a top-metal ground shield is also investigated and found not to be a strong contributor to the pulling problem.

Chapter 4 reviews the theory and operation of the varactor-tuned LC VCO in the K-State Microtransceiver, and presents a detailed analysis of the large-signal operation of inversion-mode MOS varactors used for analog frequency tuning. MOS varactors have steep C-V curves and high on/off capacitance ratios, suggesting a similar VCO frequency tuning characteristic. However, due to the large-signal output swing of the VCO, the effective capacitance seen by the LC tank is a time-averaged function of the varactor C-V curve. This averaging produces a smooth, linear VCO tuning characteristic. Chapter 4 shows that the relationship between varactor capacitance and LC tank voltage implies that signals coupled into the LC tank will time-modulate this varactor capacitance and pull the VCO.

Having established a foundation for the discussion of chip-level coupling in Chapters 2 and 4, Chapter 5 presents a time-domain analysis of frequency pulling in a varactor-tuned LC VCO from an on-chip PA, focusing on the susceptibility of the VCO to pulling from aggressor signals with different modulation schemes. If the aggressor signal is band-limited and/or amplitude-modulated, a varactor-tuned LC VCO will experience frequency pulling due to time-modulation of the varactor capacitance by the aggressor signal. However, if the aggressor signal has constant-envelope phase modulation, VCO pulling can be eliminated, even in the presence of coupling, through careful choice of the VCO frequency and VCO divider ratio.

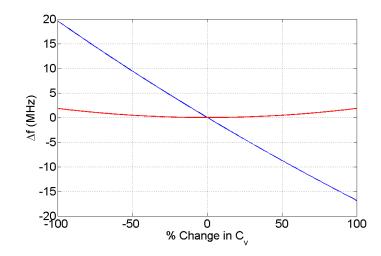

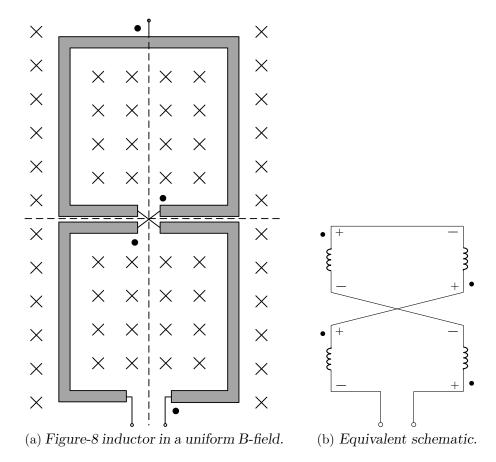

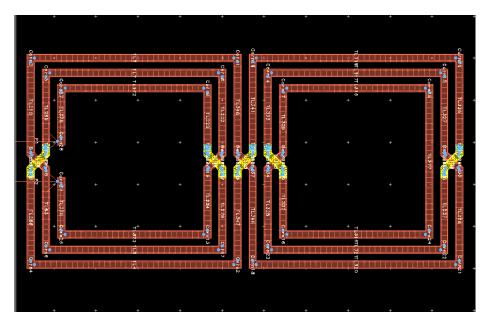

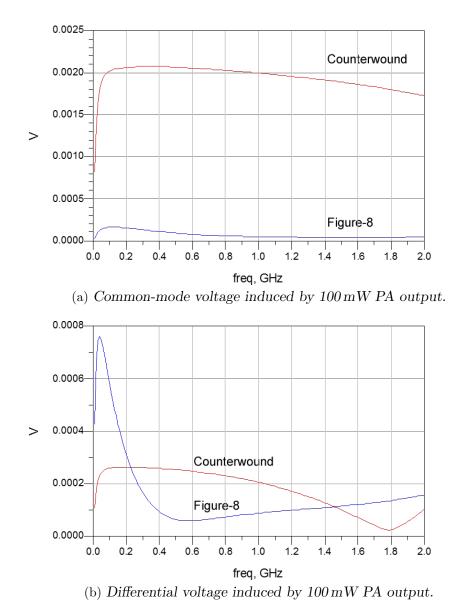

Chapter 6 presents pulling mitigation strategies for integrated transceivers based on the results in Chapter 5. These strategies are targeted at transceiver designers in the first stages of system architecture planning. In particular, Chapter 6 showcases a new figure-8 inductor topology [20] that is immune to coupling from external Bfields. Simulations of the inductor in the K-State Microtransceiver demonstrate that the figure-8 topology can provide greater than 40 dB of additional isolation between the PA and VCO compared to traditional inductor topologies. Because it is not always possible to fabricate custom inductors, Chapter 6 discusses other mitigation strategies, such as choice of VCO frequency, VCO divider ratio, modulation scheme, and PA topology to design a fully-integrated transceiver that is naturally insensitive to pulling.

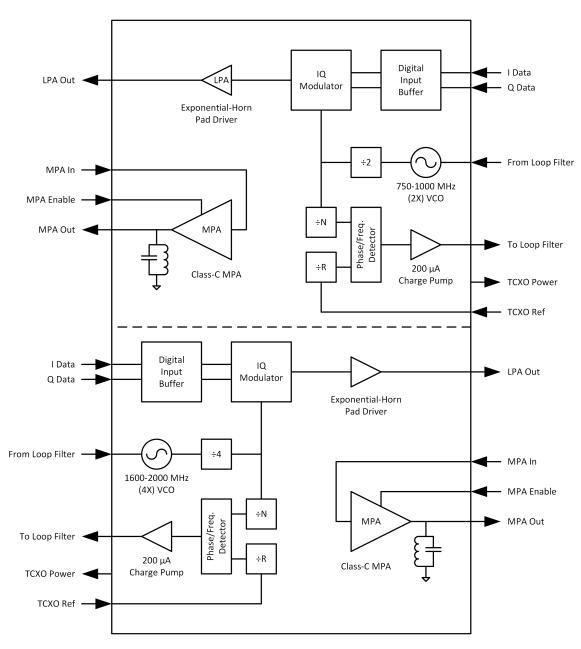

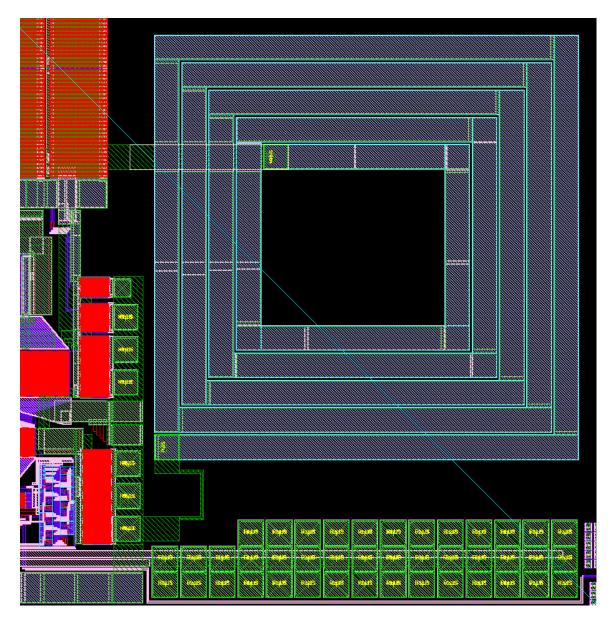

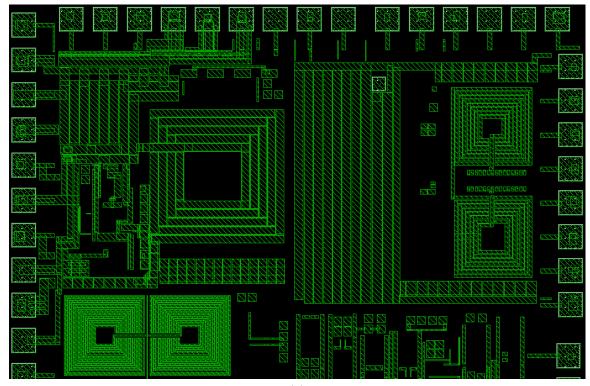

Chapter 7 describes the design and performance of a pair of QPSK transmitters fabricated in  $0.18 \,\mu\text{m}$  SOI to test a potential pulling mitigation strategy for the K-State Microtransceiver. Based on the analysis in Chapter 2, it was concluded that a VCO operating at  $4\times$  the transmit frequency would be naturally insensitive to pulling from BPSK and QPSK-modulated carrier waves. The pair of transmitters designed in this research—one utilizing a  $2 \times \text{VCO}$ , one utilizing a  $4 \times \text{VCO}$ —consisted of a differential LC VCO, an integer-N synthesizer, an IQ modulator, and 10 mW and 100 mW power amplifiers, and were designed to closely match the performance of the K-State Microtransceiver when transmitting QPSK data. Testing confirmed that the transmitter with the  $2 \times \text{VCO}$  experienced frequency pulling when transmitting QPSK, but the transmitter with the  $4 \times \text{VCO}$  did not, thereby confirming the assessment in Chapter 3.

Having confirmed the effectiveness of pulling mitigation strategies presented in Chapter 7 and having proposed a solution to enable even non-constant envelope modulation in Chapter 6, Chapter 8 describes two revisions of the K-State Microtransceiver that were designed as part of an independent study by the author. One revision of the microtransceiver was designed utilizing an off-chip PA inductor to reduce signal coupling with the VCO. In addition, a second revision containing two prototype microtransceiver transmitters with  $4 \times$  VCOs and figure-8 inductors is being designed in  $0.25\,\mu\mathrm{m}$  SOS to validate the effectiveness of the figure-8 inductor topology at eliminating frequency pulling from band-limited modulation. Other critical circuits, such as frequency dividers, are being redesigned to take advantage of the higher  $f_t$  of the smaller process. The prototype transmitters are targeted for fabrication in early 2015. Both revisions of the microtransceiver also include an improved charge pump, a hardware FSK modulator with a dedicated FSK data pin, and six years' worth of miscellaneous bug fixes and improvements. The microtransceiver's fractional-N synthesizer was also redesigned to mitigate a capacitive coupling path between the synthesizer ground shield and the receiver responsible for the appearance of a 4.8 MHz divided reference spur in the IF output. Finally, Chapter 9 concludes the thesis with a summary of results and future work.

# Chapter 2

# Coupling Mechanisms in Integrated Circuits

In this chapter, the three dominant coupling mechanisms in modern IC processes substrate, electric field, and magnetic coupling—are examined, and mitigation strategies for each mechanism are discussed. Two process technologies in particular are singled out for examination. The K-State Microtransceiver is designed in a  $0.5 \,\mu\text{m}$ silicon-on-sapphire (SOS) IC process, while another IC fabricated in the course of this research is fabricated in a  $0.18 \,\mu\text{m}$  thick-film silicon-on-insulator (SOI) process. This chapter presents research that demonstrates that both processes can provide comparable substrate and electric field coupling isolation at high frequencies. However, both processes are equally susceptible to magnetic coupling, a direct result of the flux linkage between integrated inductors. This allows magnetic coupling mitigation strategies to be investigated in either process technology and applied to both with identical results. System-level coupling mechanisms, such as crosstalk, power supply ripple, and ground bounce, are also identified and discussed.

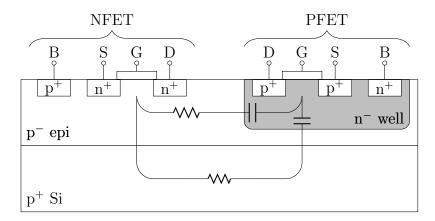

# 2.1 Substrate Coupling in Bulk CMOS

Before discussing substrate coupling in SOI, it is beneficial to briefly consider substrate coupling in bulk CMOS. A typical bulk CMOS process, shown in Figure 2.1, consists of a highly-doped silicon substrate between 600 um and 900 um thick, with a moderately to lightly-doped epitaxial layer (epi layer) between 0.5 um and 4 um thick to provide latch-up immunity [21]. Bulk CMOS processes have been extensively studied and modeled, and are favored for their high availability and low cost. However, bulk CMOS provides poor inductor performance and poor circuit isolation, both at

Figure 2.1: Cross-section of a typical bulk CMOS process showing substrate coupling paths.

DC and at high frequencies, because devices have direct DC coupling paths through both the substrate and the low-resistivity epi layer.

In bulk CMOS, selective oxide growth methods such as local oxidation of silicon (LOCOS) and shallow-trench isolation (STI) are utilized to block the DC epi layer coupling path between devices [21] and provide additional latch-up immunity [22]. Other techniques, such as surrounding sensitive circuits with grounded substrate contacts and deep-well guard rings [23] and following line-of-diffusion and standardcell layout conventions [21], help capture and shunt stray epi-layer noise to ground, providing an additional measure of isolation. However, while these techniques are effective at mitigating coupling through the epi layer, they are ineffective at mitigating coupling through the heavily-doped Si substrate. Signals which reach the low-resistivity substrate can travel long distances, allowing them to couple into circuits far away from the source.

### 2.2 Substrate Coupling in SOI

Silicon-on-insulator IC technologies were developed to address the poor isolation, low speed, and high power consumption of bulk CMOS. These processes also allow highperformance inductors to be constructed, and are therefore generally preferred for RF work. In SOI, an epitaxial film of single-crystalline Si is separated from the substrate by an insulating layer of SiO<sub>2</sub>. Compared to bulk CMOS, SOI technology allows for the fabrication of smaller devices with simpler, more effective isolation structures [24], lower parasitic substrate capacitance, higher  $f_t$ , and reduced short-channel effects [25], and provides a 30-40% reduction in power consumption [26]. Some forms of SOI technology are also inherently immune to latch-up, and high-resistivity substrates, if

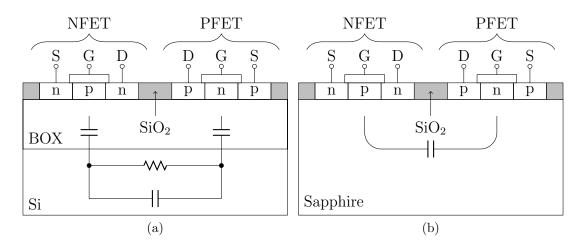

Figure 2.2: Substrate coupling paths in thin-film SOI processes. (a) SOI on buried oxide. (b) Silicon-on-sapphire.

used, eliminate the need for wells and buried doped layers. SOI technologies can be grouped into two categories—thin-film or thick-film—based on the thickness of the epi layer.

#### 2.2.1 Thin-Film SOI

In thin-film SOI, a thin layer of epitaxial silicon—between 10 nm and 1000 nm thick is grown on an insulating substrate, such as  $SiO_2$  or sapphire. Both process technologies are illustrated in Figure 2.2. Thin-film SOI is also referred to as fully-depleted SOI (FD-SOI) to emphasize that the channel region of a thin-film MOSFET extends from the gate oxide to the insulating layer. As a result, devices fabricated in thin-film SOI suffer from floating-body and kink effects [27].

Because the epi layer is so thin, it can be oxidized or etched away. This restricts substrate coupling in thin-film SOI to capacitive mechanisms through the high-resistivity substrate. The high-resistivity substrate also allows IC designers to fabricate high-Q integrated passives. Q values greater than 30 have been reported for integrated inductors fabricated in SOS, compared to typical achievable Q values of 3-12 in bulk CMOS [28]. The K-State Microtransceiver was originally designed in  $0.5 \,\mu$ m SOS for this reason.

#### 2.2.2 Thick-Film SOI

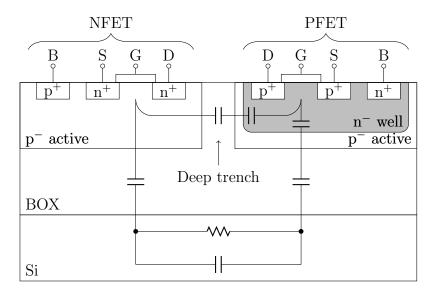

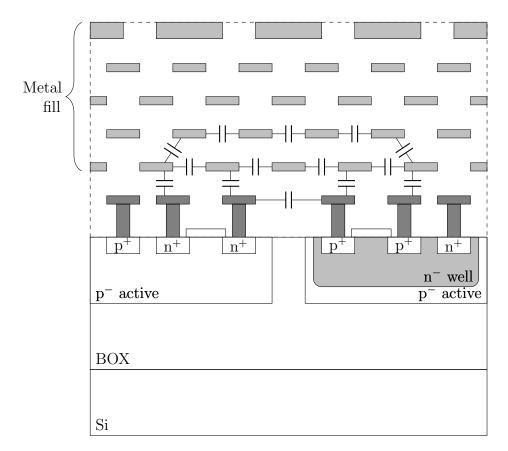

In thick-film SOI, shown in Figure 2.3, a thicker layer of epitaxial silicon—approximately  $1 \,\mu m$  thick—is separated from a Si substrate by a layer of buried oxide. Unlike thin-

Figure 2.3: Substrate coupling paths in a typical thick-film SOI process.

film SOI, the height of the silicon film in which thick-film devices are fabricated is larger than the height of the devices' depletion regions. As a result, thick-film SOI technology is referred to as partially-depleted SOI (PD-SOI), and necessitates the use of body contacts to prevent the floating-body effect.

Previous K-State research [8] characterized substrate coupling in a commercial  $0.18 \,\mu\text{m}$  thick-film SOI process used to fabricate an IC designed in the course of this research and measured the effectiveness of different substrate coupling mitigation techniques, including increasing the physical separation between active devices, isolating circuits with deep-trenches, blocking channel-stopper implant used to prevent surface inversion to increase the resistivity of the epi layer, and isolating circuits with grounded NTAP guard rings to absorb substrate currents. Of these strategies, a combination of deep-trench wells and substrate-contact guard rings was found to produce the best isolation, resulting in a 40 dB-per-decade increase in isolation at high frequencies [8].

## 2.3 Electric Field Coupling Between Interconnects

Another dominant on-chip coupling mechanism is capacitive coupling caused by fringing electric fields between metal interconnects. Capacitive coupling paths can form between metal device interconnects, adjacent traces on routing layers, and through floating fill metal, as illustrated in Figure 2.4, and between adjacent bondwire pads.

Metal-to-metal coupling was extensively studied and simulated in [8]. To a first

Figure 2.4: Capacitive coupling paths in a six-metal-layer thick-film SOI process.

order, the capacitance between two overlapping metals in a uniform dielectric can be approximated as a parallel-plate capacitor

$$C = \frac{A\epsilon_0\epsilon_r}{h} \tag{2.1}$$

where A is the overlapping area,  $\epsilon_r$  is relative the dielectric constant of the oxide, and d is the inter-metal dielectric (IMD) thickness. The fringing-field capacitance between two adjacent metal interconnects, such as device contacts or parallel traces, may be approximated by modeling the adjacent metals as parallel coplanar strips in a multilayer dielectric and applying the closed-form formulas presented in [8] and [29]. It is left to an exercises to the reader to solve for the fringing-field capacitance between two parallel metals. However, both Equation 2.1 and [29] show that fringingfield capacitance decreases as the separation between metal objects increases. It is important to note that the capacitance between two parallel metal interconnects is largely dependent on the separation between the two traces, not the trace width, because the primary fringing field interaction occurs between the near edges of the traces [8].

#### 2.3.1 Metal Fill

Another potential metal-to-metal coupling path in ICs is through metal fill. Dummy metal fill patterns, shown in Figure 2.5, are generated in empty areas of the die to reduce variations in interlayer dielectric thickness and prevent the accidental partial removal of metal layers during chemical-mechanical polishing (CMP), which is used to planarize inter-metal dielectric (IMD) oxide layers.

As illustrated in Figure 2.4, capacitive coupling between floating metal fill shapes could allow high-frequency signals to couple between metal interconnects and active devices. However, research has shown that there is no significant change in coupling between active devices when fill metal is blocked because the high-frequency capacitive coupling path through the insulating substrate has a much lower impedance than the series-connected fringing-field capacitances of a chain of metal fill shapes [8]. Blocking fill metal above metal interconnects was only found to provide a 1 dB increase in metal-to-metal isolation.

Figure 2.5: Example of floating fill metal patterns in a six-metal  $0.18 \,\mu m$  SOI process.

#### 2.3.2 Electric Field Coupling Mitigation Strategies

To a first order, capacitive coupling between metal interconnects in ICs can be modeled using well-known capacitance equations. Since interconnects to active devices are generated by the process toolkit, metal-to-metal coupling between the drain, gate and source interconnects of a MOSFET is unavoidable to some degree. Such parasitic capacitances become part of the model of the active device. In general, however, capacitive coupling can be mitigated in both thick-film and thin-film SOI by increasing the vertical and horizontal separation between adjacent metal interconnects leading to the device, and by avoiding closely-spaced parallel metal runs.

Coupling between bondwire pads on an IC should also be addressed. In thickfilm SOI, a combination of substrate and capacitive coupling mitigation techniques can be used to increase pad-to-pad isolation, including increasing the pad pitch, surrounding the pads with grounded substrate-contact guard rings to trap stray epi-layer noise currents, and inserting deep-trench grids beneath the pads to reduce pad-to-pad coupling through the substrate [8].

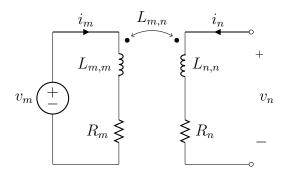

## 2.4 Magnetic Field Coupling

Before discussing magnetic coupling, it is important to review mutual inductance. Figure 2.6 is a schematic diagram of two coupled inductors with reference dots denoting the polarity of the mutual inductance. The subscripts  $L_{m,m}$  and  $L_{n,n}$  are used

Figure 2.6: Mutual inductance and the dot convention.

to denote the self-inductance of each coil. To a first order, the planar spiral inductors fabricated in ICs can be treated as wire loops. The flux linkage between two coupled coils m and n is given by

$$L_{m,n} = \frac{N_n \Phi_{n,m}}{i_m} \tag{2.2}$$

where N is the number of turns in the inductor,  $\Phi$  is the magnetic flux through inductor n generated by inductor m, and  $L_{m,n}$  is the mutual inductance between the two inductors. It is important to note that the forward and reverse mutual inductances of two coupled coils are equal, and are given by

$$L_{m,n} = L_{n,m} = M = k \sqrt{L_{m,m} L_{n,n}}$$

(2.3)

where the coupling coefficient  $0 \le k \le 1$  is the ratio of the total magnetic flux linking  $L_m$  and  $L_n$  to the total flux through both coils. A coupling coefficient of 1 therefore implies complete flux linkage between the two inductors. By Faraday's law of induction, the voltage induced in coil n due to flux from coil m is given by

$$v_{n,m}(t) = N_n \frac{d\Phi_n}{dt} = M \frac{di_m}{dt}$$

(2.4)

therefore, the total voltage across coil n, as shown in 2.6, can be expressed as

$$v_n(t) = L_{n,n} \frac{di_n}{dt} + i_n(t)R_n + M \frac{di_m}{dt}$$

$$\tag{2.5}$$

where  $R_n$  is the equivalent series resistance of the lumped-element inductor model.

#### 2.4.1 Magnetic Coupling Mitigation Strategies

Equations 2.2 and 2.4 suggest that magnetic coupling can be mitigated in two ways. First, the flux linkage between two inductors can be reduced by decreasing the number of turns in the inductor, or by physically shrinking the size of the inductor to decrease the amount of flux passing through it. Unfortunately, this is not always possible. Inductor dimensions and number of turns are usually set by the desired inductance, self-resonant frequency, and Q in a particular process. The flux linkage between two inductors can also be reduced by employing solid metal shields above or below sensitive inductors. The time-varying magnetic field creates eddy currents in the shield which flow in accordance with Lenz's law, creating magnetic fields that oppose the flux through the inductor. The net flux through the inductor is therefore decreased. Unfortunately, so too is the self-inductance, and hence the inductor Q. Simulations of a  $300 \times 300 \,\mu\text{m}$ , 0.5 nH single-turn spiral inductor in 0.25  $\mu\text{m}$  SOS [8] show that, in order to achieve a 20 dB reduction in magnetic coupling, a solid metal ground shield must be located  $1-2\,\mu\text{m}$  above the inductor and produces a 90% decrease in effective inductance. The parasitic capacitance between the ground shield and inductor windings also significantly reduces the inductor's self resonant frequency. Ground shields are therefore undesirable for use in circuits requiring high-Q inductors.

If the designer is unable to change the dimensions of the inductors, magnetic coupling may be mitigated by reducing the mutual inductance M and coupling coefficient k using physical separation. As the two coupled inductors are separated, the amount of flux linking the two inductors decreases, and k converges to zero. In the far field, the value of the coupling coefficient is largely dependent on the separation of the inductors and not on the size or number of turns [8]. Increasing the physical separation between inductors is the most straightforward magnetic coupling mitigation strategy [30]. However, the maximum achievable inductor separation is limited both by the size of the inductors and the size of the die.

## 2.5 System-Level Coupling

Designers of integrated circuits occasionally forget that the devices they build are part of a larger system. While an in-depth study of system-level coupling mechanisms is outside the scope of this thesis, common-mode noise sources such as power supply ripple and ground bounce caused by bondwire inductance will be considered in Chapter 3 as potential LO pulling mechanisms. The use of differential circuits and signaling is critical for power-supply and common-mode noise immunity, especially in RF circuits. The K-State Microtransceiver is almost entirely differential to provide high common-mode rejection in addition to simplified circuit layout and higher voltage swings. Active supply filters are also implemented in sensitive circuits, such as high-gain IF amplifiers, to prevent unwanted feedback and oscillation [1]. In addition to employing differential circuit topologies, power supply ripple and ground bounce can be mitigated by designing low-power circuits with small switching currents, operating at lower supply voltages, and reducing bondwire and package lead inductance by choosing smaller packages. Additional techniques commonly used include the separation of analog and digital power and ground pins and employing ground down-bonds to shorten the length of the bondwire, and allocating multiple power and ground pins for a single domain.

Many of these techniques were utilized to mitigate power supply ripple and ground bounce in the in the K-State Microtransceiver's 100 mW Class-C PA, which draws a peak switching current of 90 mA during normal operation. To reduce bondwire and package-lead inductance, the microtransceiver was packaged in a QFN with an exposed ground paddle, and the PA was allocated three power pins and four ground pins. Ground down-bonds to the exposed paddle reduce the inductance of each ground bondwire by half. In addition to 600 pF of on-chip decoupling, each PA power pin is decoupled at the board level by multiple ceramic and low-ESR tantalum capacitors.

## 2.6 Summary

Substrate and electric field (capacitive) coupling are present to some degree in all modern IC technologies. While thin-film SOI and SOS are much less susceptible to substrate coupling than thick-film SOI, [8] demonstrated that thick-film SOI can provide as much high-frequency substrate isolation as SOS through proper use of deep-trench surrounds, PTAP and NTAP guard rings, and selective blocking of any channel-stopper implant. Additionally, all ICs, regardless of process technology, are susceptible to capacitive coupling between metal interconnects, and to system-level coupling mechanisms such as power supply ripple and ground bounce. These can be easily mitigated through board-level and on-chip supply decoupling, on-chip supply filtering, reducing bondwire and lead inductance through the use of down-bonds and multiple power and ground pins, and by employing separate power and ground connections for separate subsystems and differential signaling on chip to reject commonmode disturbances when crossing power and ground domains. Unfortunately, while substrate, electric field, and system-level coupling can be mitigated without dramatically impacting circuit performance, magnetic shielding techniques such as ground shields reduce magnetic flux and increase inductor parasitic capacitance, thereby reducing inductor Q. This is extremely undesirable in RF circuits. Increasing the physical separation between inductors decreases magnetic coupling without impacting Q, however, the maximum separation—and therefore the upper bound on achievable magnetic isolation—is set by the inductor dimensions and the available die size. In the case of the K-State Microtransceiver, which has seven integrated inductors on a  $3.2 \times 3.2$  mm die, magnetic interaction is inevitable and must be mitigated in other ways.

# Chapter 3

# Frequency Pulling in the K-State Microtransceiver

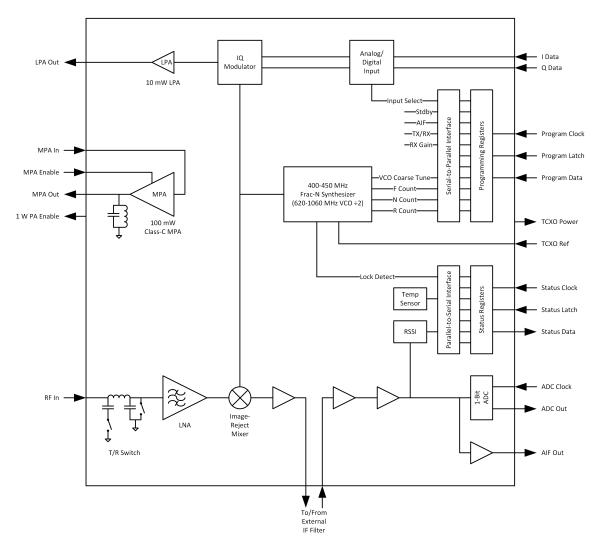

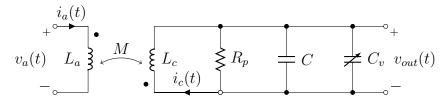

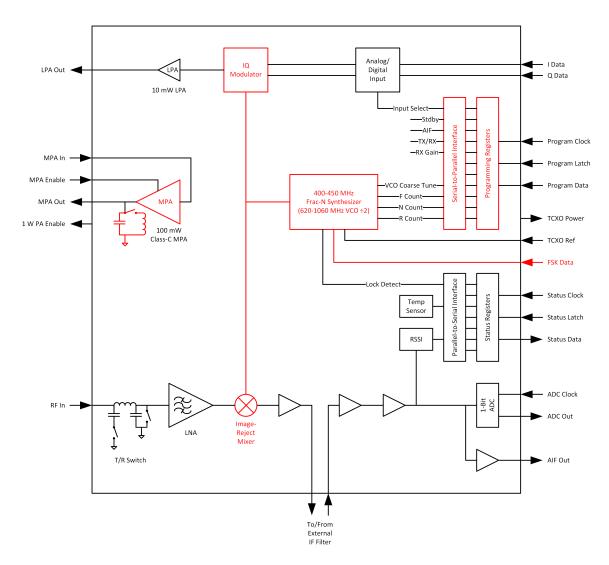

A top-level block diagram of the K-State Microtransceiver is shown in Figure 3.1. The upper half consists of a direct-modulation transmitter capable of transmitting BPSK,  $\pi/2$  RC-BPSK, QPSK, and FSK with externally-generated IQ waveforms. The VCO operates at twice the modulated output frequency and is divided down to generate differential quadrature outputs for IQ modulation. A 10-bit fractional-N synthesizer with 3rd-order  $\Sigma$ - $\Delta$  modulator operating from a 19.2 MHz off-chip reference oscillator allows the transmitter to achieve a tuning step size of 4.7 kHz. The microtransceiver can transmit using either a 10 mW exponential-horn pad driver or an integrated 100 mW class-C PA. The lower half is a classic superheterodyne receiver with an off-chip 10.7 MHz IF filter and a 1-bit oversampling ADC. An integrated T/R switch designed into the LNA allows the LNA to be directly connected to the PA output as shown in Figure 3.1. The combination of 10.7 MHz IF and oversampled ADC was selected over a direct-conversion architecture due to the requirement for the radio to process extremely low data rate BPSK and QPSK at sensitivities  $\leq$  -120 dBm in an IC process where 1/f noise can extend into the MHz range [1].

### 3.1 Identification of the LO Pulling Mechanism

The microtransceiver's LO pulling problem had been investigated by various graduate researchers in the past; however, the results of their investigations were largely unsuccessful, and the specific LO pulling mechanism remained unidentified. The first step in identifying the LO pulling mechanism in this thesis was to extensively test the microtransceiver and attempt to replicate the problem. The microtransceiver

Figure 3.1: Block diagram of the K-State Microtransceiver.

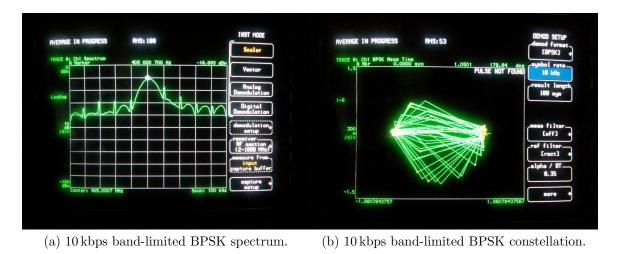

was operated in BPSK and QPSK mode at various data rates at 10 mW and 100 mW output power settings, and the radio's output spectrum and symbol constellation were examined on an HP89410A Vector Signal Analyzer in an attempt to determine which factors let to frequency pulling. An Agilent 33220A Function/Arbitrary Waveform Generator programmed with a 2<sup>64</sup>-symbol PRBS sequence was used to generate pseudo-random I or Q data. Because an arbitrary waveform generator capable of synthesizing phase-coherent I and Q data waveforms was not accessible,  $\pi/2$  residual-carrier BPSK (RC-BPSK) modulation was used to test the microtransceiver's QPSK performance. RC-BPSK is generated by fixing the value of either the in-phase or quadrature channel and transmitting data on the other, thereby using only two adjacent QPSK symbols, producing a QPSK spectrum with a large residual-carrier peak. Transmitting RC-BPSK is a simple way of exercising an IQ modulator in QPSK mode in the absence of a dual-data-stream PRBS generator.

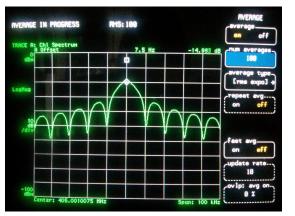

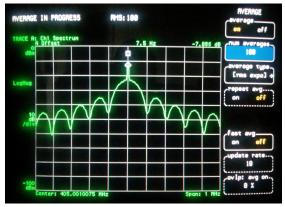

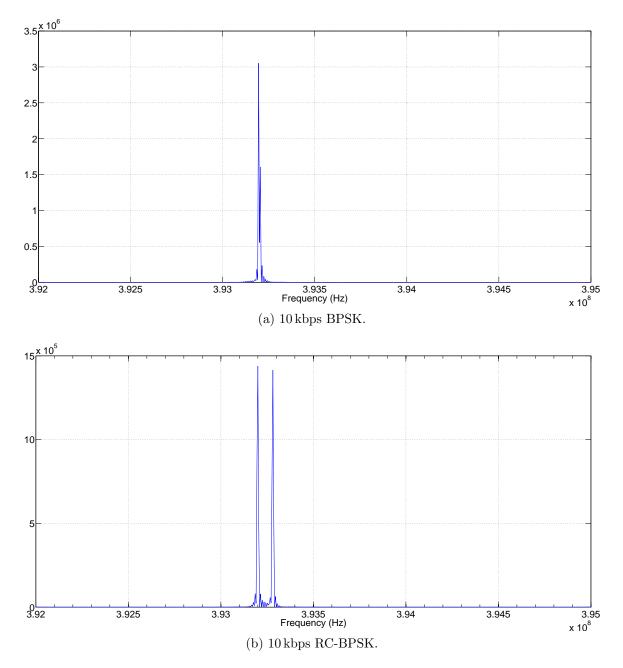

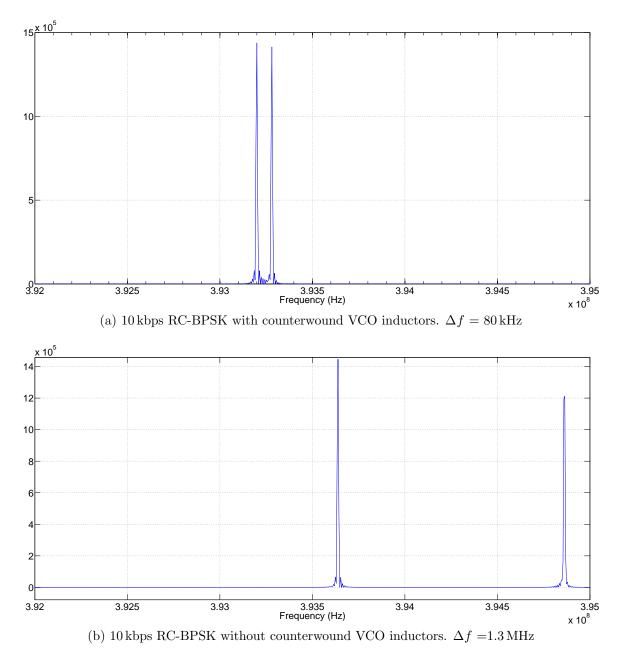

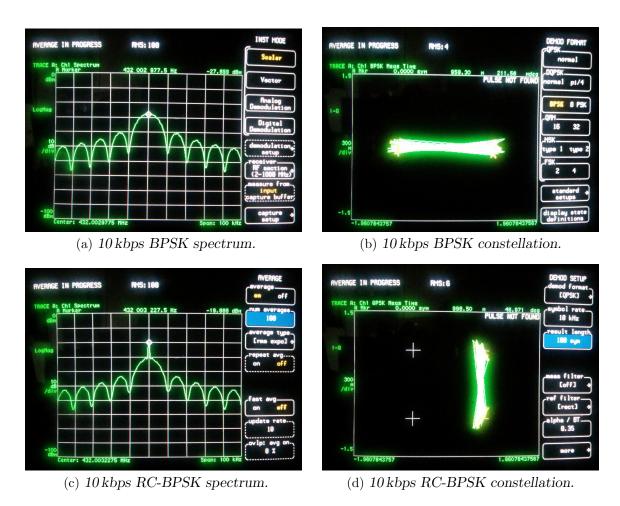

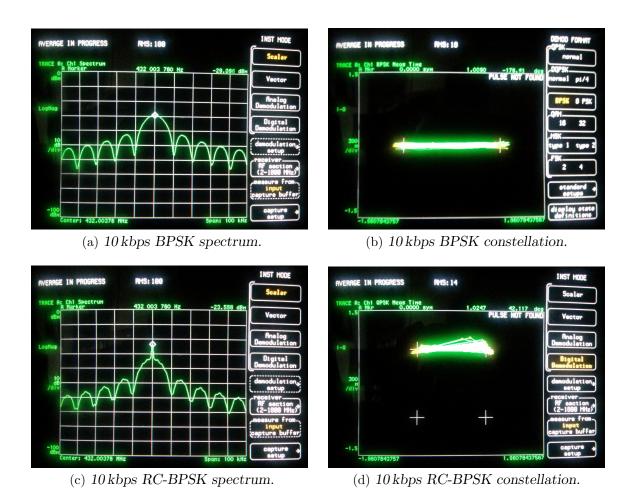

Figure 3.2 compares the microtransceiver's BPSK and RC-BPSK (QPSK) performance transmitting 10 kbps data with the 10 mW low-power amplifier, an inductorless exponential-horn inverter pad driver. Similar tests revealed that the microtransceiver is able to transmit both BPSK and RC-BPSK (QPSK) successfully at data rates up to 1 Mbps. At data rates above 1 Mbps, both the BPSK and RC-BPSK output spectrums become lopsided, shown in Figure 3.3, due to asymmetrical prefiltering on the microtransceiver's data inputs.

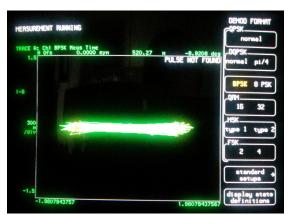

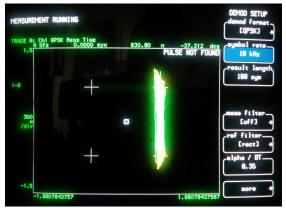

Figure 3.4 compares the BPSK and QPSK performance transmitting 10 kbps data with the 100 mW PA active. The radio's BPSK performance is not affected by the 100 mW PA. However, the QPSK spectrum (Figure 3.4c) was severely degraded, and symbols in the QPSK constellation (Figure 3.4d) are indicative of severe LO pulling. At 10 kbps, each QPSK symbol accumulated between  $\pi/4$  and  $\pi/2$  radians of phase error within one bit period, and at data rates greater than 10 kbps, pulling is so severe that the signal constellation cannot be demodulated. This strongly indicates that the 100 mW PA is the source of the LO pulling.

## **3.2** Magnetic Coupling

Having discovered that 100 mW PA was the apparent aggressor responsible for LO pulling, magnetic coupling between the PA and VCO inductors was suspected to be the dominant coupling mechanism. A design review identified two potential magnetic coupling paths between the PA and VCO. The 100 mW PA output can potentially couple directly into the VCO inductors from the inductor in the 100 mW PA, or from

(a) 10 kbps BPSK spectrum.

(b) 10 kbps BPSK constellation.

(c) 10 kbps RC-BPSK spectrum.

(d)  $10\,kbps$  RC-BPSK constellation.

Figure 3.2: Fab 5 BPSK and RC-BPSK performance at 10 kbps using the microtransceiver's inductorless 10 mW exponential-horn pad driver.

Figure 3.3: Fab 5 BPSK and RC-BPSK spectrums at 1 Mbps. The lopsided spectrums are caused by asymmetrical prefiltering on the I and Q data inputs.

(c)  $10 \,\mathrm{kbps}$  QPSK spectrum.

(d)  $10\,\rm kbps$  QPSK constellation.

Figure 3.4: Comparison of Fab 5 BPSK and QPSK performance transmitting 10 kbps data with the  $100\,\mathrm{mW}$  PA active.

| Inductor     | Designation | Design Value      | Extracted Value   |

|--------------|-------------|-------------------|-------------------|

| 100 mW PA    | a           | $16\mathrm{nH}$   | 14.8 nH           |

| T/R switch   | b           | $80\mathrm{nH}$   | $77.6\mathrm{nH}$ |

| VCO (top)    | с           | $17.5\mathrm{nH}$ | $17.2\mathrm{nH}$ |

| VCO (bottom) | d           | $17.5\mathrm{nH}$ | 18.1 nH           |

Table 3.1: Table of Fab 5 inductor design values and extracted values.

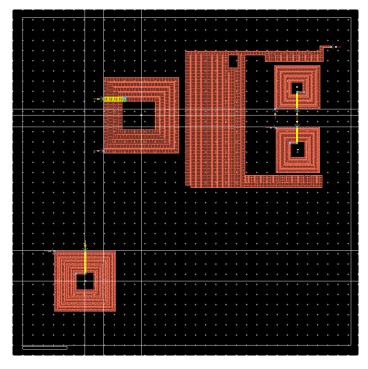

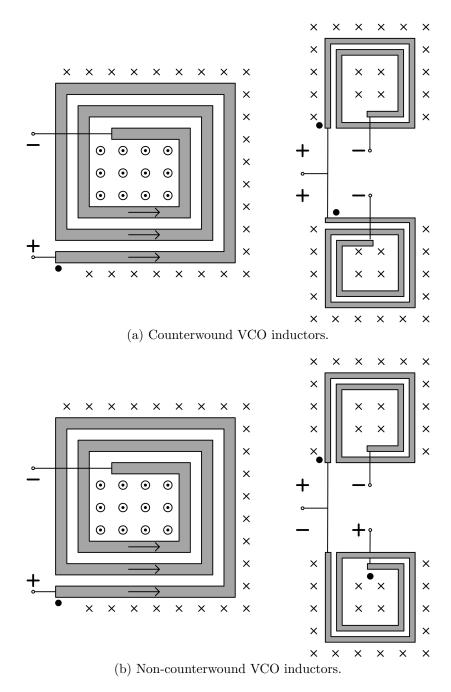

an inductor in the resonant T/R switch used to protect the LNA input. Figure 3.5 indicates the position of both inductors. Note that the VCO employs two inductors in a counterwound arrangement in an attempt to reduce coupling. This attempt is shown to be less than totally effective in Chapter 6, where we investigate the detailed origin of the pulling problem. To quantify the coupling between each set of inductors, the VCO, 100 mW PA, and T/R switch inductors were drawn and simulated together in ADS Momentum, as shown in Figure 3.6. An 8-port S-parameter network was extracted to model the interactions between inductors. The mutual inductance M and coupling coefficient k for each pair of inductors can be calculated from the extracted S-parameters using

$$M = \sqrt{\mathrm{Im}(Z_{12})\,\mathrm{Im}(Z_{21})} \tag{3.1a}$$

$$k = \sqrt{\frac{\operatorname{Im}(Z_{12}) \operatorname{Im}(Z_{21})}{\operatorname{Im}(Z_{11}) \operatorname{Im}(Z_{22})}}$$

(3.1b)

Table 3.1 compares the design values of the inductors in Figure 3.5 with their extracted inductances. Following the inductor labeling in Figure 3.5,  $k_{a,c}$  and  $k_{a,d}$  will be used to denote the coupling coefficients between the 100 mW PA inductor and the top and bottom VCO inductors, respectively. Likewise,  $k_{b,c}$  and  $k_{b,d}$  denote the coupling coefficients between the resonant T/R switch.

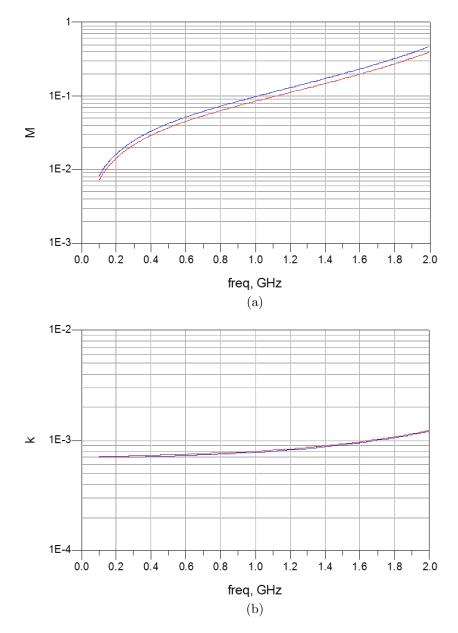

#### 3.2.1 Coupling Between the 100 mW PA and the VCO

Figure 3.7 plots the simulated mutual inductance and coupling coefficient between the VCO inductors and the 100 mW PA inductor. Although the differential VCO was laid out symmetrically, it was positioned slightly off the centerline of the 100 mW PA inductor. This resulting in slightly different flux linkage between the upper and lower VCO inductors. In the extracted model,  $k_{ac} = 0.00073$  and  $k_{ad} = 0.00071$ .

The 100 mW PA delivers a measured +18 dBm into  $50 \Omega$ , corresponding to a peak voltage of 2.51 V. To determine the voltage induced across the VCO inductors by

Figure 3.5: Inductor locations in the K-State Microtransceiver. (a) 100 mW PA inductor. (b) Resonant T/R switch. VCO inductors (c) and (d).

Figure 3.6: ADS Momentum simulation of Fab 5 inductor S-parameters.

Figure 3.7: Extracted M and k between the 100 mW PA and the top (red) and bottom (blue) VCO inductors. At midband (420 MHz),  $k_{a,c} = 0.00073$  and  $k_{a,d} = 0.00071$ .

Figure 3.8: Voltage induced in the VCO inductors (c and d) by the 100 mW PA.

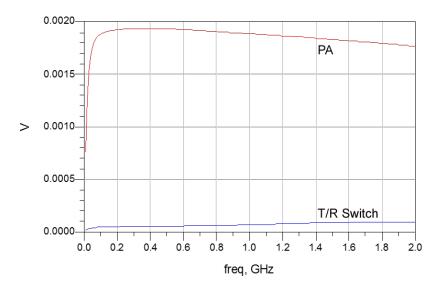

the 100 mW PA, a frequency-domain simulation was performed on the extracted Sparameter network. The PA inductor was driven with a 2.51 V source, and the induced voltage across the other extracted inductors was simulated over the microtransceiver's operating band. Figure 3.8 is a plot of the voltage induced in the VCO inductors by the 100 mW PA. At 420 MHz, the PA induced a 1.9 mV voltage across the terminals of the VCO inductor.

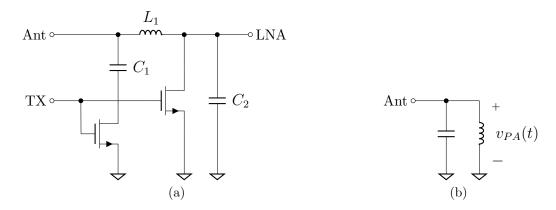

#### 3.2.2 Coupling Between the T/R Switch and the VCO

The second potential magnetic coupling path is through the microtransceiver's resonant T/R switch. The radio operates in half-duplex mode and uses one antenna, so the output of the 100 mW PA can be connected directly to the LNA input, as shown in Figure 3.1. A resonant T/R switch developed at K-State, shown in Figure 3.9a, is used to protect the sensitive LNA input during transmit and provide input matching for the LNA in receive mode [2]. When the microtransceiver is receive mode, the TX line in Figure 3.9a is pulled low, and  $L_1$  and  $C_2$  form a highpass matching network between the antenna and the LNA. When the microtransceiver is transmitting, TX is pulled high, and  $L_1$  resonates with  $C_1$  to present a high impedance to the PA output while simultaneously shorting the LNA input to ground. As shown in Figure 3.9b, the entire PA output voltage is developed across the resonating inductor when the radio is transmitting, potentially creating another magnetic coupling path between the PA and VCO.

Figure 3.10 plots the extracted M and k between the inductor in the resonant

Figure 3.9: (a) Schematic of the resonant T/R switch in the K-State Microtransceiver and (b) Equivalent circuit in transmit mode.

T/R switch and both VCO inductors. The extracted coupling coefficients between the T/R switch inductor and the upper and lower VCO inductors were calculated to be  $6.3 \times 10^{-6}$  and  $6.1 \times 10^{-6}$ , respectively, at 420 MHz, over two orders of magnitude less than the coupling coefficients between the PA and VCO inductors.

Figure 3.11 compares the simulated voltages induced in the VCO inductors by the PA and by the T/R switch. At 420 MHz, the T/R switch induces a 53  $\mu$ V voltage across the VCO inductors, compared to a 1.9 mV induced voltage from the PA. This implies that, although a small degree of magnetic coupling exists between the resonant T/R switch and the VCO, it is not as significant a contributor to the QPSK pulling problem as the main PA inductor aggressor.

#### 3.2.3 Simulation of the PA-VCO Magnetic Coupling Path

To confirm that magnetic coupling between the PA and VCO inductors was responsible for frequency pulling, the transmit half of the K-State Microtransceiver (minus the fractional-N frequency synthesizer) was imported into Agilent ADS. A transient simulation was performed of the microtransceiver running open-loop while transmitting 10 kbps BPSK and QPSK. To model the interaction between inductors, the inductors in the VCO, 100 mW PA, and resonant T/R switch were replaced with the 8-port S-parameter model extracted from ADS Momentum.

Figure 3.12 compares the simulated open-loop output transmit frequency of the microtransceiver for different BPSK and QPSK symbols. The microtransceiver's output frequency remained constant for all BPSK symbols, indicating no LO pulling. However, changing between adjacent QPSK symbols (from an output phase of  $\phi = 0$  or  $\pi$  to an output phase of  $\phi = \frac{\pi}{2}$  or  $\frac{3\pi}{2}$ ) produced an 80 kHz change in open-loop

Figure 3.10: Extracted M and k between the resonant T/R switch and the upper (blue) and lower (red) VCO inductors.

Figure 3.11: Voltage induced in the VCO inductors by the PA and by the T/R switch.

output frequency. Since the microtransceiver was simulated transmitting constantenvelope phase modulation, the total accumulated phase error over one symbol period  $T_s$  produced by a change in frequency  $\Delta f$  is given by

$$\Delta \phi = \int_0^{T_s} 2\pi \cdot \Delta f dt = 2\pi \cdot T_s \cdot \Delta f \tag{3.2}$$

where  $T_s$  is the symbol period. Since the microtransceiver operates with a 100 kHz loop bandwidth, however,  $T_s = 1 \times 10^{-5}$  for data rates less than 100 kHz. Applying Equation 3.2, the accumulated phase error created by the simulated 80 kHz jump in output frequency would be

$$\Delta \phi = 2\pi \cdot T_s \cdot \Delta f = 2\pi \cdot \frac{80 \,\mathrm{kHz}}{100 \,\mathrm{kHz}} = 5.02 \,\mathrm{rad} \tag{3.3}$$

In Figure 3.4d, the observed accumulated phase error while transmitting 10 kbps RC-BPSK was between  $\frac{\pi}{2}$  (1.571) and  $\pi$  (3.142) radians. Therefore, the simulation closely matches the measured performance of the microtransceiver and strongly indicated that magnetic coupling between the 100 mW PA and VCO is the dominant LO pulling mechanism.

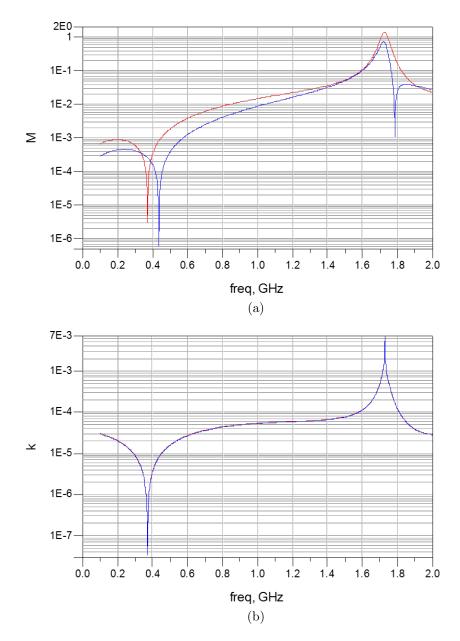

# 3.3 Capacitive Coupling

When the K-State Microtransceiver was designed, a top-metal ground shield, shown in Figure 3.13, was implemented over the fractional-N synthesizer and digital pro-

Figure 3.12: Simulated open-loop output frequency when transmitting BPSK and RC-BPSK. Transitioning between RC-BPSK symbols produced a  $\Delta f$  of 80 kHz.

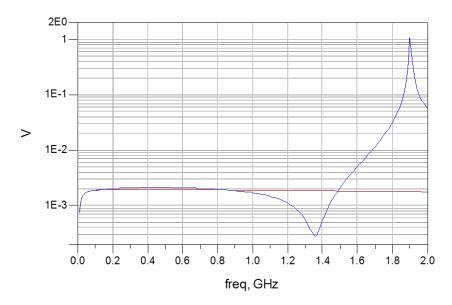

gramming registers to prevent digital noise from capacitively or inductively coupling into the LNA and high-gain IF chain while the radio was operating in receive mode [1]. The close proximity of the  $\Sigma$ - $\Delta$  modulator to the PA required the shield to come within 60  $\mu$ m of the PA inductor and 30  $\mu$ m of the VCO inductors. Because of its close proximity to both the VCO and 100 mW PA inductors, it was speculated that fringing-field capacitance between the inductors and the non-zero impedance of the bondwire to ground allowed the PA output signal to capacitively couple from the outer windings of the PA inductor to the outer windings of the VCO inductors.

To determine its contribution to the QPSK pulling problem, the ground shield was added to the inductor layout in ADS Momentum, shown in Figure 3.13, and a 9port S-parameter network was extracted to model the interaction between the VCO and 100 mW PA. The voltage induced in the VCO inductors by the PA was then simulated with a 10 nH bondwire inductance between the shield and ground. Figure 3.15 compares the voltage induced in the VCO inductors by the PA with and without the ground shield. Between 390 and 450 MHz, the shield contributes less than 200  $\mu$ V of additional induced voltage across the VCO inductors, an increase of roughly 10%.

It was therefore concluded that, while some capacitive coupling exists between the PA and the VCO through the top-metal ground shield, it was likely not a significant contributor to the pulling problem. However, electric field coupling between the synthesizer ground shield and top-metal features in the receiver—including the outer windings of the LNA inductor—is responsible for the appearance of a 4.8 MHz divided-reference spur in the IF output. In Chapter 8, the synthesizer ground shield is redesigned to reduce metal-to-metal coupling between the shield and the receiver while still providing adequate shielding for the synthesizer. Additionally, the bondwire inductance between the synthesizer shield and ground resonates with the fringing-field capacitance of the shield and creates a resonant peak at 1.9 GHz, as seen in Figure 3.15. Care must be taken in such designs to insure that the shield-bondwire resonance remains outside the operating band of both the PA (390-450 MHz) and the VCO (620-1060 MHz).

## **3.4 Additional Coupling Paths**

While the 100 mW PA was clearly the cause of LO pulling in the K-State Microtransceiver, and magnetic coupling a clear contributor, the system-level coupling mechanisms identified in 2.5 were also considered. Due to the high current draw

Figure 3.13: Location of the top-metal synthesizer ground shield.

Figure 3.14: ADS Momentum simulation of Fab 5 inductor S-parameters with top-metal synthesizer ground shield.

Figure 3.15: Voltage induced in the VCO inductors by the PA, with (blue) and without (red) the top-metal synthesizer ground shield. Note the presence of the resonant peak at 1.9 GHz.

of the 100 mW PA, power supply ripple and ground bounce were identified as possible coupling paths for the aggressor signal from the PA to couple back into the VCO. To assess the contribution of system-level coupling issues to the pulling problem, the microtransceiver was extensively tested, including

- testing on three different boards with different layouts,

- testing with different decoupling capacitance configurations, including removing all board-level decoupling on the VCO and PA,

- comparing the performance of the radio in TQFP and QFN packages to observe the effect of increased bondwire and lead inductance,

- comparing the performance of the radio in packages with and without ground down-bonds, and

- attempting to induce LO pulling by magnetically coupling the 10 mW output back into the loop filter.

Surprisingly, however, none of these tests produced any discernible change in the microtransceiver's BPSK or QPSK performance, nor were they able to produce LO pulling when the 100 mW PA was off. In general, the radio was found to be very robust. This indicated that the system-level and non-inductive coupling mechanisms

discussed in Section 2.5 had been well-addressed in the original design, and were not significant contributors to the QPSK pulling problem.

### 3.5 Summary

The BPSK and QPSK performance of the K-State Microtransceiver was tested in various operating modes to determine the cause of LO pulling. It was discovered that the microtransceiver could transmit both BPSK and QPSK without pulling using the 10 mW low-power amplifier, an exponential-horn pad driver. When the 100 mW class-C medium-power amplifier was activated, the microtransceiver experienced severe LO pulling when transmitting QPSK. At data rates faster than 10 kbps, LO pulling is so severe that the signal constellation cannot be demodulated. The radio's BPSK performance, however, is unaffected by the 100 mW PA.

The correlation between LO pulling and the 100 mW PA strongly suggested that an inductive coupling mechanism between the PA and VCO inductors was somehow responsible for the LO pulling. A series of design reviews identified two potential magnetic coupling paths between the PA and VCO. When the 100 mW PA is operating, the PA output is magnetically coupled into the VCO inductors from both the 100 mW PA inductor and the inductor in an integrated resonant T/R switch. The VCO, PA, and T/R switch inductors were simulated together in ADS Momentum, and an 8-port network of S-parameters was extracted to model the interaction between inductors. The PA and VCO inductors were found to be the dominant magnetic coupling path with an extracted coupling coefficient of 0.00036 at 420 MHz, implying that the 100 mW PA output would induce a 2 mV peak voltage in the VCO inductors. A potential capacitive coupling path between the PA and VCO inductors through a top-metal ground shield was also simulated and found not to be a strong contributor to the interaction between the PA and VCO.

To verify that magnetic coupling between the PA and VCO is the primary LO pulling mechanism, the transmit half of the microtransceiver was imported into Agilent ADS. The microtransceiver was simulated transmitting both BPSK and QPSK at 10 kbps, using the extracted 8-port S-parameter network to model the interaction between integrated inductors. As expected, the microtransceiver's output frequency remained constant for all BPSK symbols, indicating no LO pulling. However, changing between adjacent QPSK symbols (from an output phase of 0 or  $\pi$  to an output phase of  $\frac{\pi}{2}$  or  $\frac{3\pi}{2}$ ) produced an 80 kHz change in output frequency, corresponding to an accumulated phase error of 5 radians over one symbol period. This closely agrees with the microtransceiver's observed QPSK performance. It was therefore concluded that magnetic coupling between the PA and VCO inductors is the primary LO pulling mechanism. The mechanisms of this pulling, together with the reason the micro-transceiver's BPSK performance is unaffected by magnetic coupling between the PA and VCO, are studied in the following chapters.

# Chapter 4

# The Differential Cross-Coupled LC VCO

Having identified magnetic coupling between the 100 mW PA and VCO as the primary LO pulling mechanism in the K-State Microtransceiver, the operation of the VCO was closely scrutinized. This chapter presents a circuit-level analysis the microtransceiver's differential LC VCO in preparation for the analysis of a VCO under magnetic coupling in Chapter 5. Since the constellation smearing observed in QPSK mode is caused by frequency pulling, this chapter focuses on the frequency tuning mechanisms in the microtransceiver, specifically the small-signal and large-signal operation of the VCO's MOS varactors.

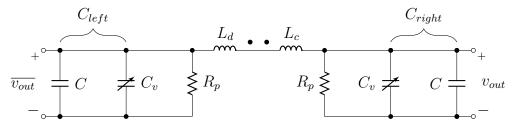

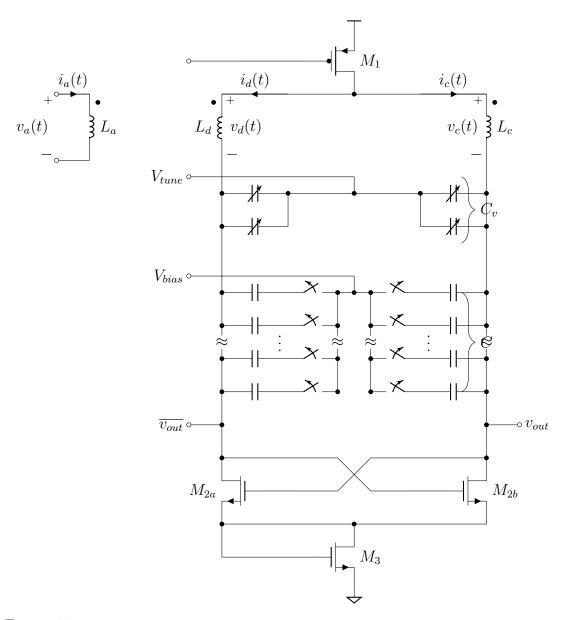

#### 4.1 The K-State Microtransceiver VCO

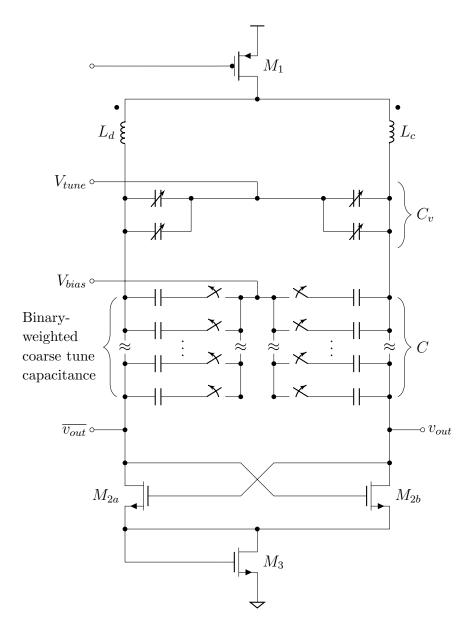

The K-State Microtransceiver employs the differential cross-coupled LC VCO topology shown in Figure 4.1. Inductors  $L_c$  and  $L_d$  are named in accordance with the labeling in Figure 3.5. The polarities of both inductors are oriented to minimize coupling onto the differential-mode VCO outputs. Transistor  $M_1$  is a standard PMOS current source, and cross-coupled FETs  $M_{2a}$  and  $M_{2b}$  form the negative-resistance compensating the losses in the LC tank. Transistor  $M_3$  is sized to bias the VCO outputs at half the supply voltage for maximum output voltage swing.

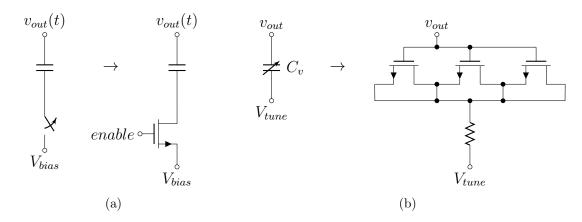

Coarse frequency tuning is accomplished using a binary-weighted bank of switched MIM capacitors, shown in Figure 4.2a, and analog frequency tuning is accomplished using inversion-mode MOS (I-MOS) varactors, shown in Figure 4.2b. In order to span the 390-450 MHz band, the VCO tunes from 620-1060 MHz and a quadrature divide-by-two is used to generate differential I and Q signals.

Figure 4.1: Schematic of the K-State Microtransceiver VCO.

Figure 4.2: Detail of the Fab 5. (a) Switched MIM capacitors for coarse frequency tuning. (b) MOS varactors for analog frequency tuning.

Figure 4.3: Series-resistance half-circuit representation of the Fab 5 VCO LC tank.

#### 4.1.1 LC Tank Properties

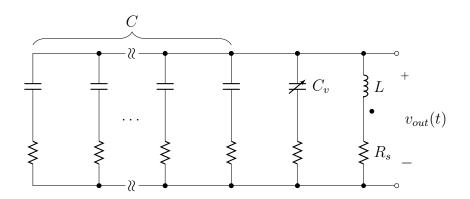

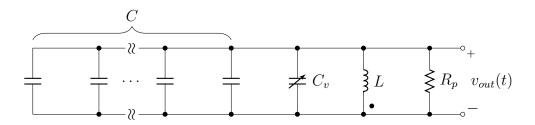

Figure 4.3 illustrates the half-circuit representation of the LC tank with losses modeled by series resistance. To a first order, the single-ended output voltage is a sinusoid

$$v_{out}(t) = V_0 \sin\left(\omega_c t + \theta\right) + V_{DC} \tag{4.1}$$

with peak amplitude  $V_0$ , angular frequency  $\omega_c$ , phase offset  $\theta$ , and DC bias  $V_{DC}$ . The series-resistance representation more closely represents the physical losses in integrated inductors and capacitors. For convenience, however, Figure 4.3 can be transformed into the parallel-resistance representation in Figure 4.4 and collect the parallel resistance terms of all components into  $R_p$ .

Figure 4.4: Parallel-resistance half-circuit representation of the Fab 5 VCO LC tank.

Figure 4.5: Full resonant circuit representation of the Fab 5 VCO LC tank.

#### 4.1.2 Frequency of Oscillation

If the left and right tank capacitances in a differential LC VCO are equal, the LC tank reduces to the half-circuit shown in Figure 4.4, and the frequency of oscillation is given by

$$\omega_c^2 = \frac{1}{L\left(C + C_v\right)} \tag{4.2}$$

However, if the left and right tank capacitances are unequal, the LC tank can be treated as the full resonant circuit shown in Figure 4.5. The frequency of oscillation is then given by

$$\omega_c^2 = \frac{1}{2L} \left( \frac{1}{C_{left}} + \frac{1}{C_{right}} \right) \tag{4.3}$$