# FLEXIBLE ENCODER AND DECODER DESIGNS FOR LOW-DENSITY PARITY-CHECK CODES

by

#### SUNITHA KOPPARTHI

B.E., Andhra University, 2000 M.S., Louisiana State University, 2003

#### AN ABSTRACT OF A DISSERTATION

submitted in partial fulfillment of the requirements for the degree

#### DOCTOR OF PHILOSOPHY

Department of Electrical and Computer Engineering College of Engineering

> KANSAS STATE UNIVERSITY Manhattan, Kansas

> > 2010

#### Abstract

Future technologies such as cognitive radio require flexible and reliable hardware architectures that can be easily configured and adapted to varying coding parameters. The objective of this work is to develop a flexible hardware encoder and decoder for low-density parity-check (LDPC) codes. The design methodologies used for the implementation of a LDPC encoder and decoder are flexible in terms of parity-check matrix, code rate and code length. All these designs are implemented on a programmable chip and tested.

Encoder implementations of LDPC codes are optimized for area due to their high complexity. Such designs usually have relatively low data rate. Two new encoder designs are developed that achieve much higher data rates of up to 844 Mbps while requiring more area for implementation. Using structured LDPC codes decreases the encoding complexity and provides design flexibility. The architecture for an encoder is presented that adheres to the structured LDPC codes defined in the IEEE 802.16e standard.

A single encoder design is also developed that accommodates different code lengths and code rates and does not require re-synthesis of the design in order to change the encoding parameters. The flexible encoder design for structured LDPC codes is also implemented on a custom chip. The maximum coded data rate of the structured encoder is up to 844 Mbps and for a given code rate its value is independent of the code length.

An LDPC decoder is designed and its design methodology is generic. It is applicable to both structured and any randomly generated LDPC codes. The coded data rate of the decoder increases with the increase in the code length. The number of decoding iterations used for the decoding process plays an important role in determining the decoder performance and latency. This design validates the estimated codeword after every iteration and stops the decoding process when the correct codeword is estimated which saves power consumption. For a given parity-check matrix and signal-to-noise ratio, a procedure to find an optimum value of the maximum number of decoding iterations is presented that considers the affects of power, delay, and error performance.

# FLEXIBLE ENCODER AND DECODER DESIGNS FOR LOW-DENSITY PARITY-CHECK CODES

by

#### SUNITHA KOPPARTHI

B.E., Andhra University, 2000 M.S., Louisiana State University, 2003

#### A DISSERTATION

submitted in partial fulfillment of the requirements for the degree

#### DOCTOR OF PHILOSOPHY

Department of Electrical and Computer Engineering College of Engineering

> KANSAS STATE UNIVERSITY Manhattan, Kansas

> > 2010

Approved by:

Major Professor Don M. Gruenbacher

# Copyright

### SUNITHA KOPPARTHI

2010

#### **Abstract**

Future technologies such as cognitive radio require flexible and reliable hardware architectures that can be easily configured and adapted to varying coding parameters. The objective of this work is to develop a flexible hardware encoder and decoder for low-density parity-check (LDPC) codes. The design methodologies used for the implementation of a LDPC encoder and decoder are flexible in terms of parity-check matrix, code rate and code length. All these designs are implemented on a programmable chip and tested.

Encoder implementations of LDPC codes are optimized for area due to their high complexity. Such designs usually have relatively low data rate. Two new encoder designs are developed that achieve much higher data rates of up to 844 Mbps while requiring more area for implementation. Using structured LDPC codes decreases the encoding complexity and provides design flexibility. The architecture for an encoder is presented that adheres to the structured LDPC codes defined in the IEEE 802.16e standard.

A single encoder design is also developed that accommodates different code lengths and code rates and does not require re-synthesis of the design in order to change the encoding parameters. The flexible encoder design for structured LDPC codes is also implemented on a custom chip. The maximum coded data rate of the structured encoder is up to 844 Mbps and for a given code rate its value is independent of the code length.

An LDPC decoder is designed and its design methodology is generic. It is applicable to both structured and any randomly generated LDPC codes. The coded data rate of the decoder increases with the increase in the code length. The number of decoding iterations used for the decoding process plays an important role in determining the decoder performance and latency. This design validates the estimated codeword after every iteration and stops the decoding process when the correct codeword is estimated which saves power consumption. For a given parity-check matrix and signal-to-noise ratio, a procedure to find an optimum value of the maximum number of decoding iterations is presented that considers the affects of power, delay, and error performance.

# **Table of Contents**

| List of Figures                                           | X    |

|-----------------------------------------------------------|------|

| List of Tables                                            | xiv  |

| Acknowledgements                                          | xvi  |

| Dedication                                                | xvii |

| CHAPTER 1 - Introduction                                  | 1    |

| 1.1 Motivation                                            | 2    |

| 1.2 Literature Review                                     | 4    |

| 1.2.1 Encoder Implementation                              | 4    |

| 1.2.2 Decoder Implementation                              | 6    |

| 1.3 Accomplishments                                       | 8    |

| 1.4 Organization of Dissertation                          | 9    |

| CHAPTER 2 - Low-Density Parity-Check Codes                | 10   |

| 2.1 Encoding                                              | 10   |

| 2.1.1 Generic Encoding                                    | 11   |

| 2.1.2 Efficient Encoding                                  | 12   |

| 2.2 Decoding                                              | 14   |

| 2.2.1 Logarithmic Message Passing Algorithm               | 15   |

| 2.2.2 Minimum Sum Algorithm                               | 17   |

| 2.2.3 Modified Minimum Sum Algorithm                      | 18   |

| 2.2.4 Other Decoding Algorithms                           | 18   |

| CHAPTER 3 - Design Tools for FPGA and ASIC Implementation | 19   |

| 3.1 Altera Quartus                                        | 19   |

| 3.1.1 Compilation                                         | 21   |

| 3.1.2 Simulations                                         | 21   |

| 3.1.3 Power Analysis                                      | 22   |

| 3.2 Cadence                                               | 23   |

| 3.2.1 RTL Compiler                                        | 25   |

| 3.2.2 Encounter                                           | 26   |

| 3.3 Matlab                                                                        | 27     |

|-----------------------------------------------------------------------------------|--------|

| CHAPTER 4 - Encoder Design for Randomly Generated Low-Density Parity-Check Code   | s 30   |

| 4.1 Encoder Design                                                                | 30     |

| 4.1.1 Preprocessing                                                               | 31     |

| 4.1.2 Hardware Implementation                                                     | 34     |

| 4.1.2.1 Multi Clocked Inner Product                                               | 35     |

| 4.1.2.2 Single Clock Inner Product                                                | 36     |

| 4.2 Results                                                                       | 36     |

| CHAPTER 5 - Encoder Design for Structured Low-Density Parity-Check Codes          | 41     |

| 5.1 Structured LDPC Codes                                                         | 41     |

| 5.2 Design Methodology                                                            | 43     |

| 5.3 Hardware Implementation                                                       | 44     |

| 5.3.1 Computation of <i>V</i>                                                     | 44     |

| 5.3.1.1 Vector-Vector Multiplication                                              | 45     |

| 5.3.1.2 Computation of $e_p$                                                      | 45     |

| 5.3.2 Computation of Parity Bits                                                  | 46     |

| 5.4 Results                                                                       | 46     |

| CHAPTER 6 - Flexible Multi-Code Rate and Multi-Code Length Encoder for Structured | d Low- |

| Density Parity-Check Codes                                                        | 51     |

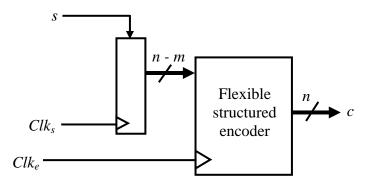

| 6.1 Design Methodology                                                            | 51     |

| 6.2 Hardware Implementation                                                       | 52     |

| 6.2.1 Storing Base Parity-Check Matrices for Different Rates of LDPC Codes        | 52     |

| 6.2.2. Parity-Check Matrix                                                        | 55     |

| 6.2.2.1 Multiplication                                                            | 57     |

| 6.2.2.2 Division                                                                  | 59     |

| 6.2.2.3 Computation of $H_1$                                                      | 61     |

| 6.2.2.4 Latency for the Computation of <i>H</i>                                   | 62     |

| 6.2.3 Computation of $e_p$                                                        | 64     |

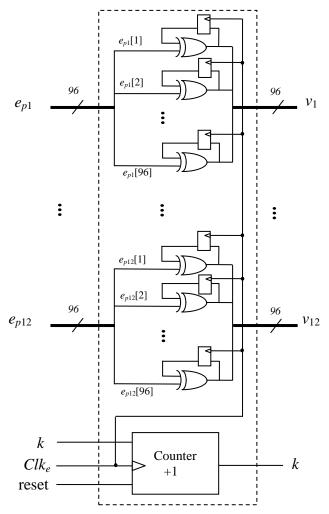

| 6.2.4 Computation of <i>V</i>                                                     | 66     |

| 6.2.5 Computation of Parity Bits                                                  | 67     |

| 6.3 Results of the Flexible Structured Encoder Implemented on an FPGA             | 67     |

| 6.4 Implementation of a Flexible Multi-Code Rate and Multi-Code Length Structured | d Encoder |

|-----------------------------------------------------------------------------------|-----------|

| on an ASIC                                                                        | 70        |

| CHAPTER 7 - Decoder for Low-Density Parity-Check Codes                            | 73        |

| 7.1 Study of LDPC Decoder Parameters                                              | 74        |

| 7.1.1 Decoding Algorithm                                                          | 74        |

| 7.1.2 Decoder Architecture                                                        | 75        |

| 7.1.3 Quantization                                                                | 75        |

| 7.1.3.1 Quantization of $\varphi$                                                 | 75        |

| 7.1.3.2 Quantization of Log-Likelihood Ratios                                     | 76        |

| 7.1.4 Maximum Number of Decoding Iterations                                       | 77        |

| 7.2 Design and Implementation of LDPC Decoder on FPGA                             | 78        |

| 7.2.1 Quantization                                                                | 78        |

| 7.2.1.1 Quantization of $\varphi$                                                 | 78        |

| 7.2.1.2 Quantization of Log-Likelihood Ratios                                     | 79        |

| 7.2.1.3 Conversion of Log-Likelihood Ratios from One Form to Another              | Form of   |

| Representation                                                                    | 80        |

| 7.2.2 Initialization of Decoder Process                                           | 81        |

| 7.2.3 Check Node Processing                                                       | 82        |

| 7.2.4 Variable Node Processing                                                    | 85        |

| 7.2.5 End of Decoding Process                                                     | 86        |

| 7.2.6 Decoder                                                                     | 87        |

| 7.3 Results                                                                       | 88        |

| 7.4 Optimization of Decoder Parameters                                            | 90        |

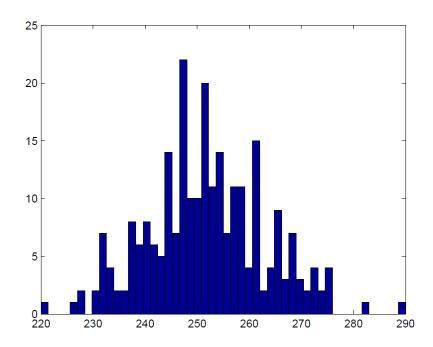

| 7.4.1 Erroneous Codewords                                                         | 90        |

| 7.4.2 Decoder Delay                                                               | 92        |

| 7.4.3 Decoder Energy                                                              | 92        |

| 7.4.4 Optimization                                                                | 95        |

| CHAPTER 8 - Conclusion                                                            | 101       |

| 8.1 Future Work                                                                   | 103       |

| CHAPTER 9 - References                                                            | 104       |

| Appendix A - Design of a Convolutional Encoder in Verilog HDL                     | 110       |

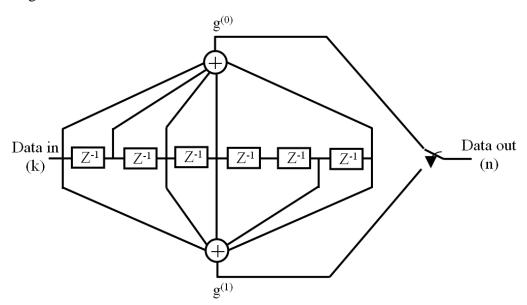

| A.1 Convolutional Encoder                                                    | 110 |

|------------------------------------------------------------------------------|-----|

| Appendix B - FPGA Implementation using Quartus                               | 112 |

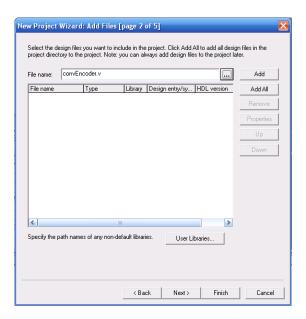

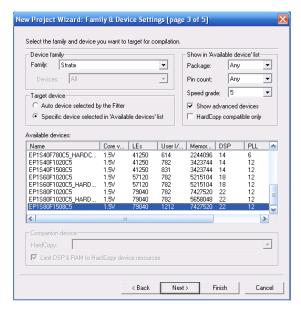

| B.1 Creating a Project                                                       | 112 |

| B.2 Compilation of the Project                                               | 114 |

| B.3 Timing Simulation                                                        | 115 |

| B.4 Power Analysis                                                           | 119 |

| Appendix C - ASIC Implementation using Cadence                               | 122 |

| C.1 Initial Setup                                                            | 122 |

| C.2 Synthesis of Verilog HDL Modules in RTL Compiler                         | 123 |

| C.3 Place and Route using Cadence Encounter                                  | 125 |

| C.4 Verification of the Design                                               | 136 |

| Appendix D - Quantization of Log-Likelihood Ratios in Decoder Implementation | 141 |

# **List of Figures**

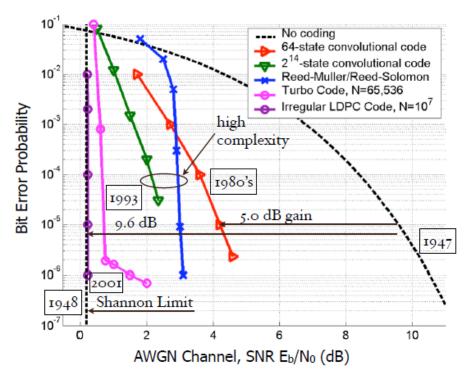

| Figure 1.1: Comparison of bit error probability of error correcting codes                             |

|-------------------------------------------------------------------------------------------------------|

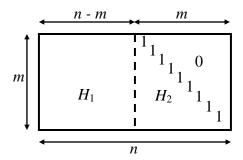

| Figure 2.1: Parity-check matrix                                                                       |

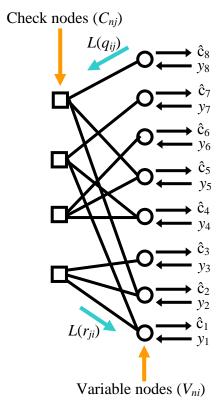

| Figure 2.2: Tanner graph representation of parity-check matrix                                        |

| Figure 2.3: A parity-check matrix in equivalent lower triangular form                                 |

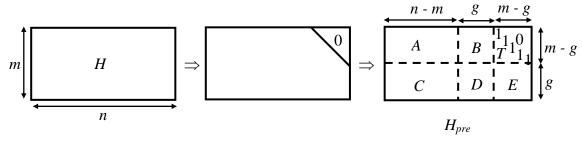

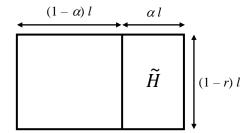

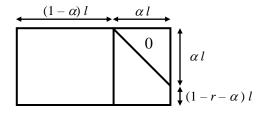

| Figure 2.4: Parity-check matrix in approximate lower triangular form, $H_{pre}$ , and its division of |

| sub-matrices                                                                                          |

| Figure 2.5: Subgraph of Tanner graph showing message passing from variable node to check              |

| node14                                                                                                |

| Figure 2.6: Subgraph of Tanner graph showing message passing from check node to variable              |

| node14                                                                                                |

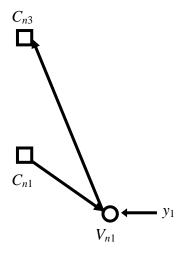

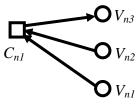

| Figure 3.1: Logic element architecture on the Stratix FPGA.                                           |

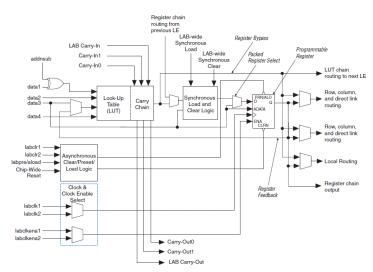

| Figure 3.2: Design flow in Quartus                                                                    |

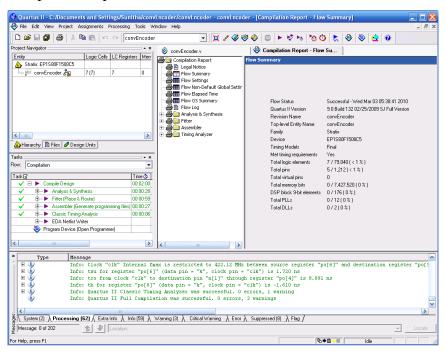

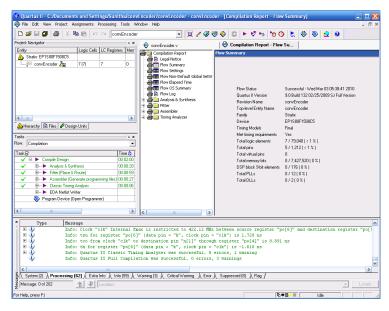

| Figure 3.3: Compilation report                                                                        |

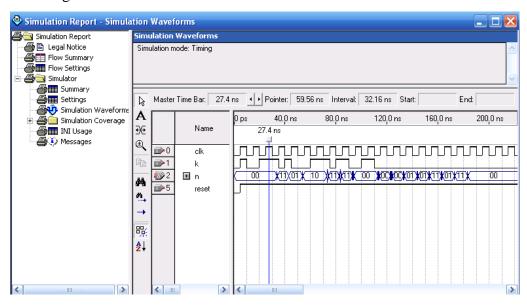

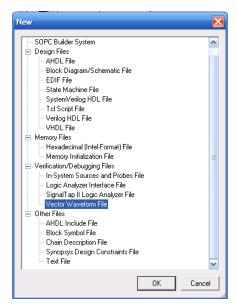

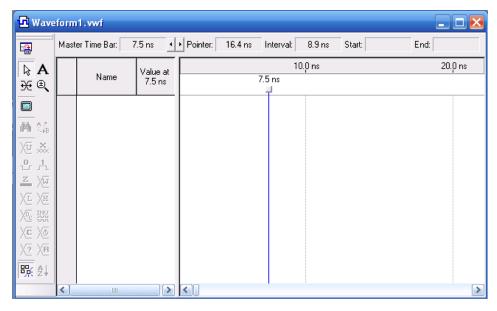

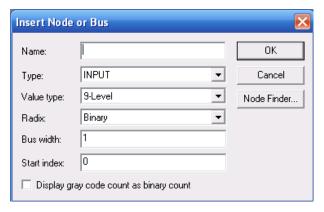

| Figure 3.4: Timing simulations                                                                        |

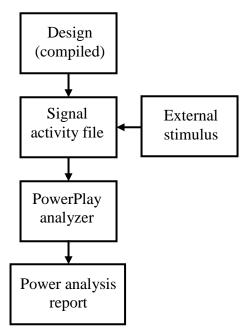

| Figure 3.5: PowerPlay power analyzer design flow                                                      |

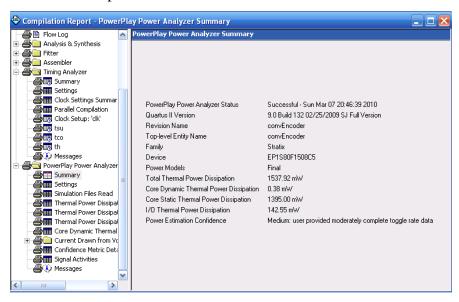

| Figure 3.6: PowerPlay power analyzer summary                                                          |

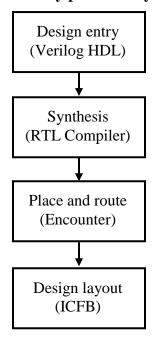

| Figure 3.7: ASIC design flow.                                                                         |

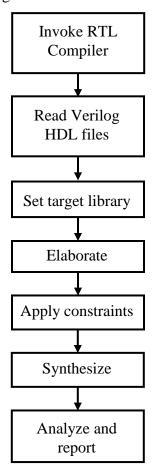

| Figure 3.8: Design flow in RTL Compiler                                                               |

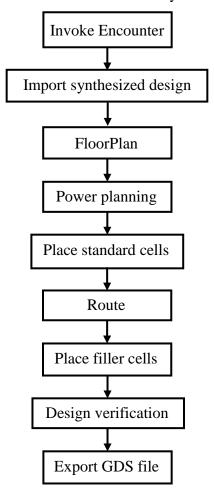

| Figure 3.9: Design flow in Encounter                                                                  |

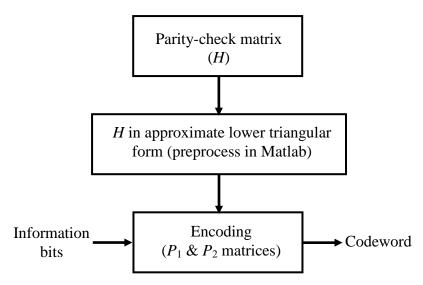

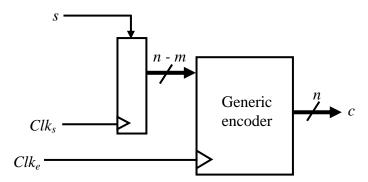

| Figure 4.1: Overview of the LDPC encoder                                                              |

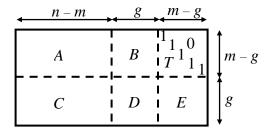

| Figure 4.2: Application of greedy algorithm A on <i>H</i>                                             |

| Figure 4.3: Distribution of number of one's in each row of $P_2$ matrix for an irregular $H$ of size  |

| 504 × 1008                                                                                            |

| Figure 4.4: Complete system of the generic encoder                                                    |

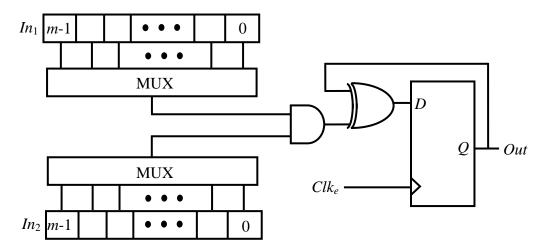

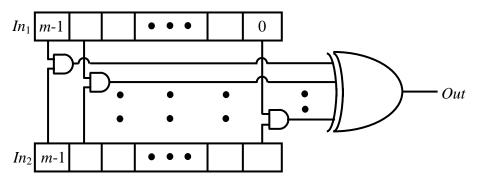

| Figure 4.5: Circuit for multi clocked inner product (MCIP)                                            |

| Figure 4.6: Circuit for single clocked inner product (SCIP)                                           |

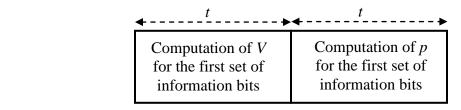

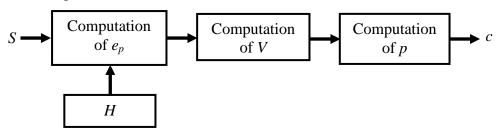

| Figure 5.1: Encoding process                                                                          |

| Figure 5.2: Overview of encoding process                                                              |

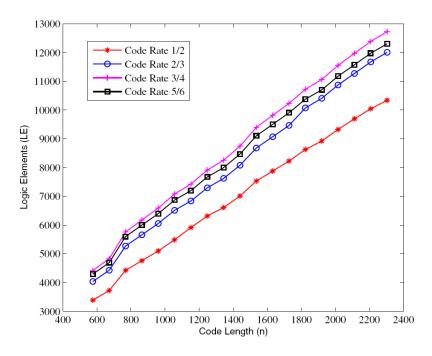

| Figure 5.3: Logic elements vs. code lengths for different code rates.                                       | 48           |

|-------------------------------------------------------------------------------------------------------------|--------------|

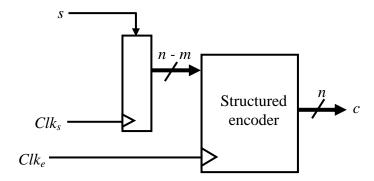

| Figure 5.4: Complete structured encoder system                                                              | 48           |

| Figure 6.1: Overview of the encoding process.                                                               | 52           |

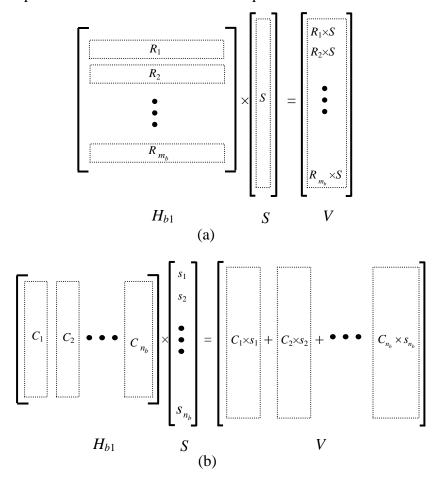

| Figure 6.2: Computation of $V$ using (a) row parallelization method and (b) column para                     | ıllelizatior |

| method                                                                                                      | 53           |

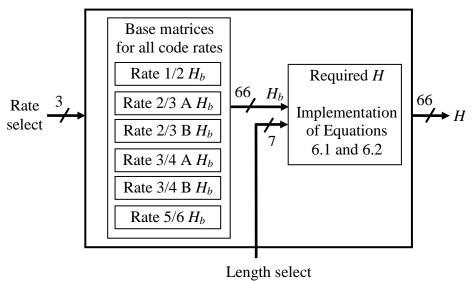

| Figure 6.3: Storing base parity-check matrices, $H_b$ , for different code rates                            | 55           |

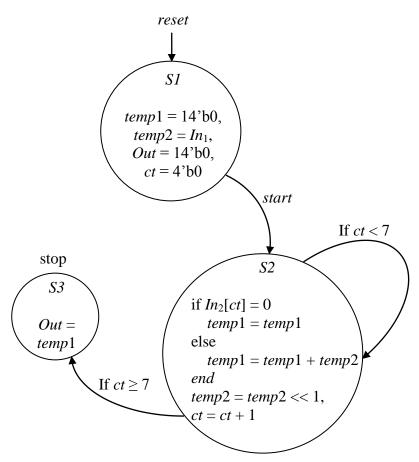

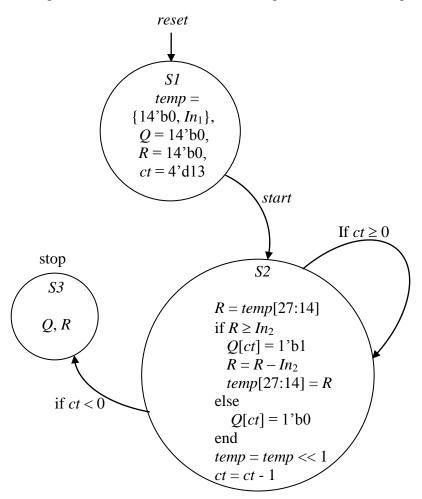

| Figure 6.4: Finite state machine for the multiplication module                                              | 57           |

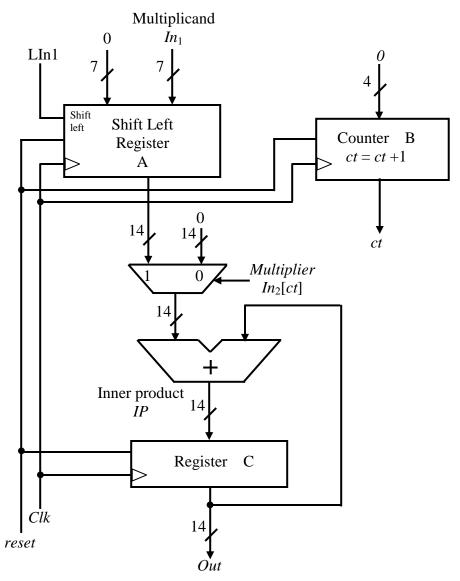

| Figure 6.5: Hardware block diagram for the multiplication module.                                           | 58           |

| Figure 6.6: Finite state machine for the division module.                                                   | 59           |

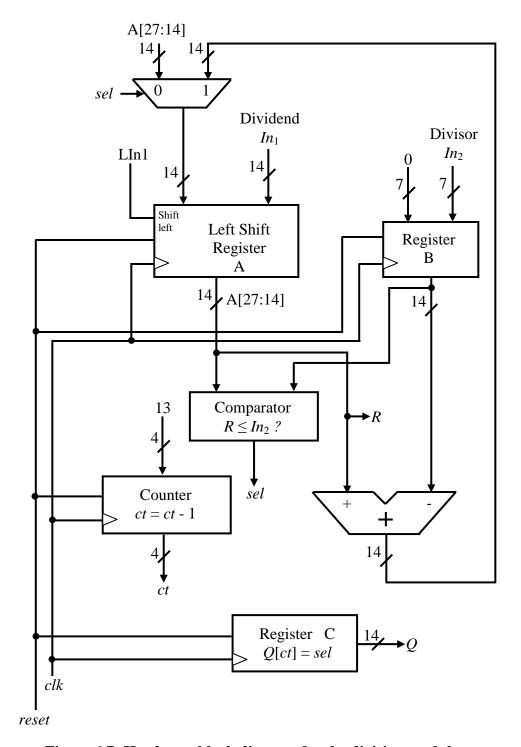

| Figure 6.7: Hardware block diagram for the division module                                                  | 60           |

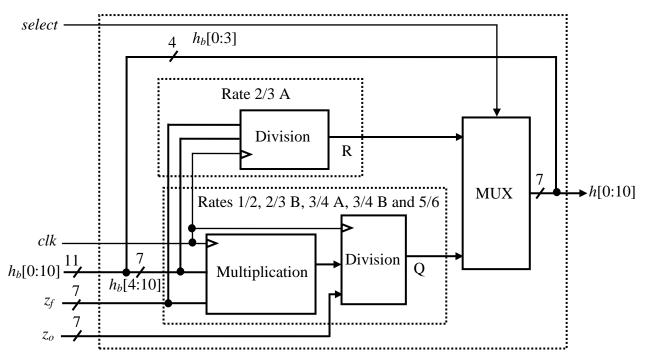

| Figure 6.8: Computation of an element of $H_1$ , $h_{1(i,j)}$ , from an element of $H_{b1}$ , $h_{b1(i,j)}$ | 62           |

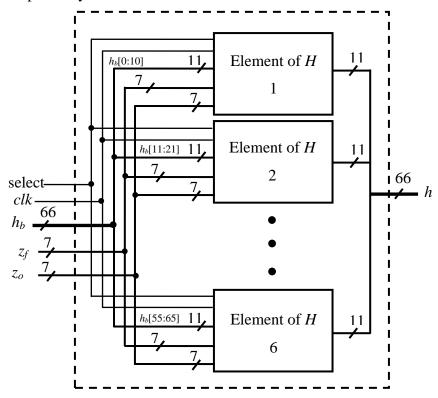

| Figure 6.9: Computation of a column of $H_1$ from a column of $H_{b1}$                                      | 63           |

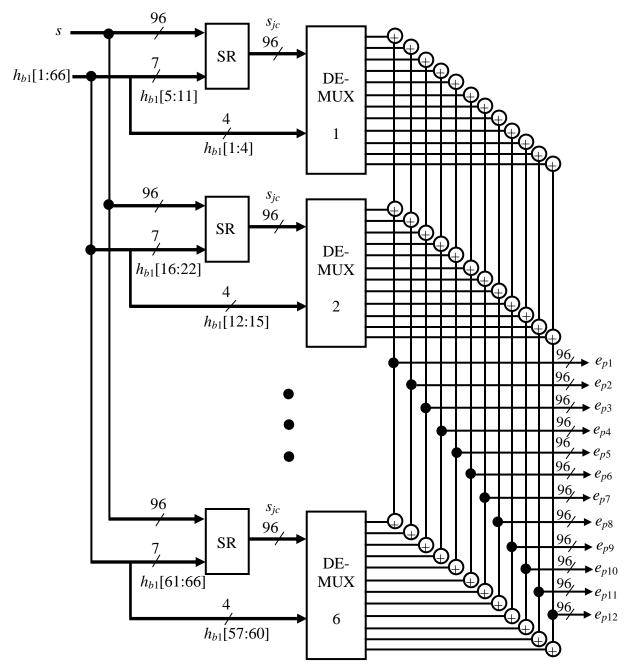

| Figure 6.10: Computation of $e_p$                                                                           | 65           |

| Figure 6.11: Computation of <i>V</i> .                                                                      | 66           |

| Figure 6.12: Complete system of the flexible multi-code rate and multi-code length                          | structured   |

| LDPC encoder.                                                                                               | 69           |

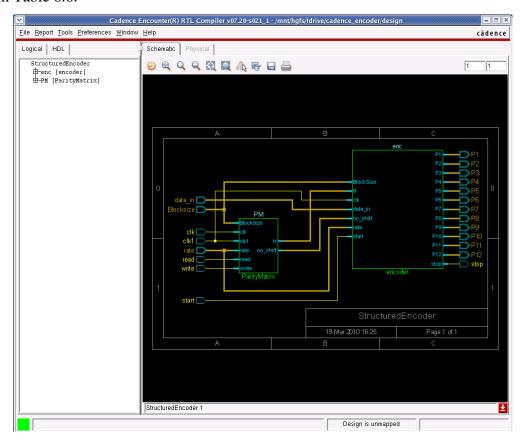

| Figure 6.13: Synthesized flexible multi-code rate and multi-code length LDPC                                | structured   |

| encoder in Cadence RTL Compiler.                                                                            | 70           |

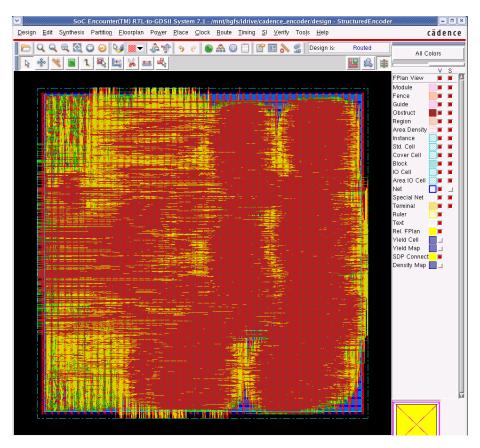

| Figure 6.14: Layout view of the flexible multi-code rate and multi-code length LDPC                         | structured   |

| encoder in Cadence Encounter                                                                                | 71           |

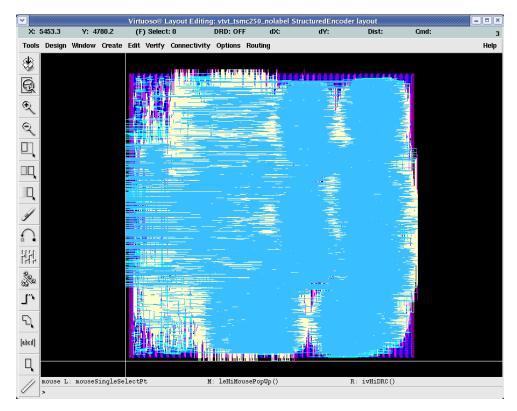

| Figure 6.15: Layout view of the flexible multi-code rate and multi-code length LDPC                         | structured   |

| encoder in Cadence ICFB.                                                                                    | 72           |

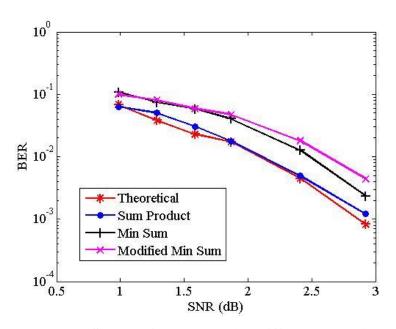

| Figure 7.1: BER vs. SNR performance using different decoding algorithms                                     | 74           |

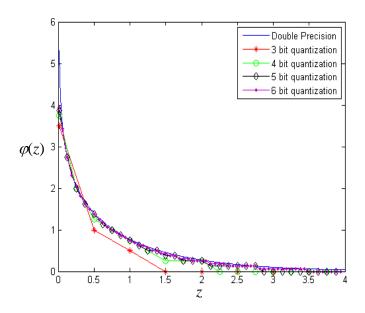

| Figure 7.2: Quantization of $\varphi$                                                                       | 7 <i>6</i>   |

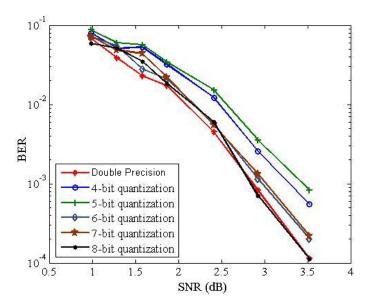

| Figure 7.3: BER vs. SNR performance for different quantization levels of log-likelihous                     | ood ratios   |

|                                                                                                             | 77           |

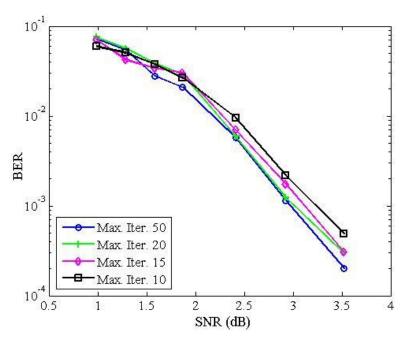

| Figure 7.4: BER vs. SNR for different values of maximum number of decoding iteratio                         | ns 78        |

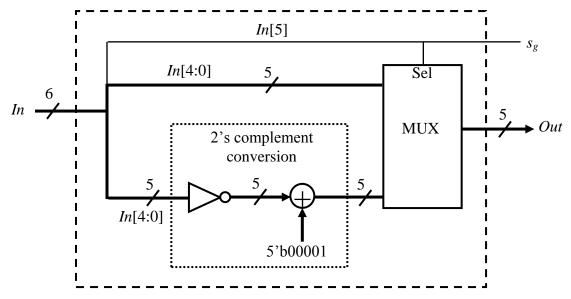

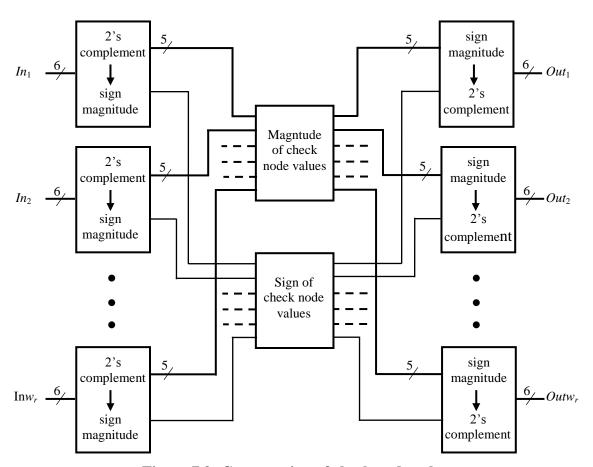

| Figure 7.5: Conversion of 2's complement to sign magnitude representation                                   | 81           |

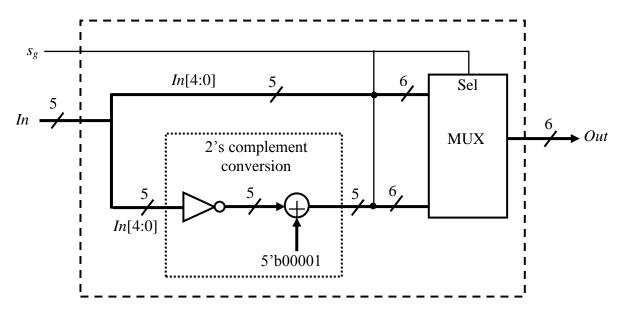

| Figure 7.6: Conversion of sign magnitude to 2's complement representation                                   | 81           |

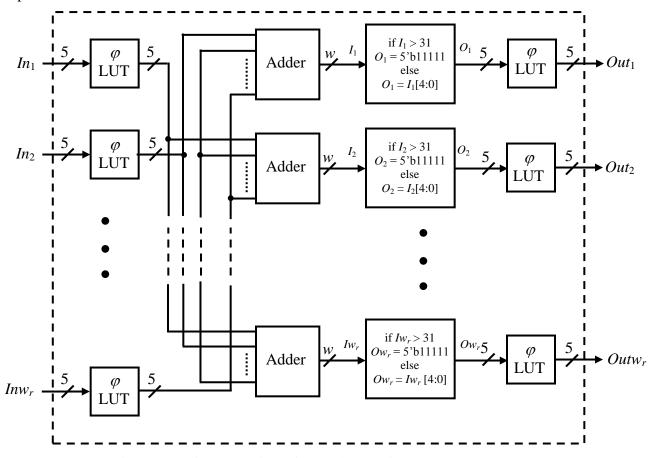

| Figure 7.7: Computation of magnitude of check node values.                                                  |              |

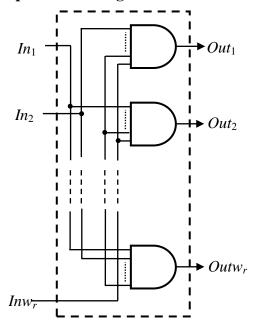

| Figure 7.8: Computation of sign of check node values                                                        | 83           |

| Figure 7.9: Computation of check node values.                                       | 84  |

|-------------------------------------------------------------------------------------|-----|

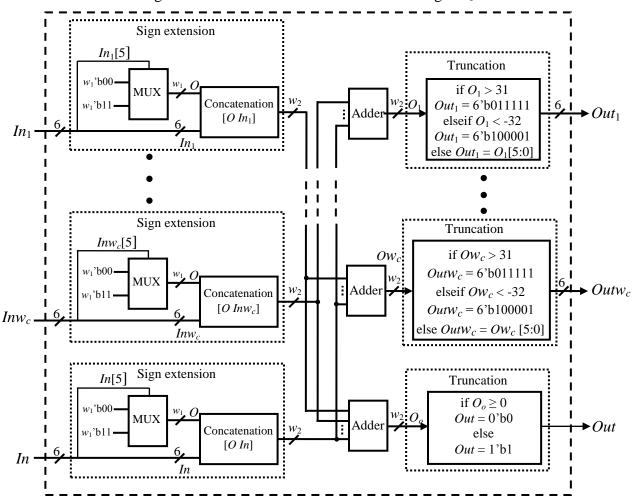

| Figure 7.10: Computation of variable node values.                                   | 85  |

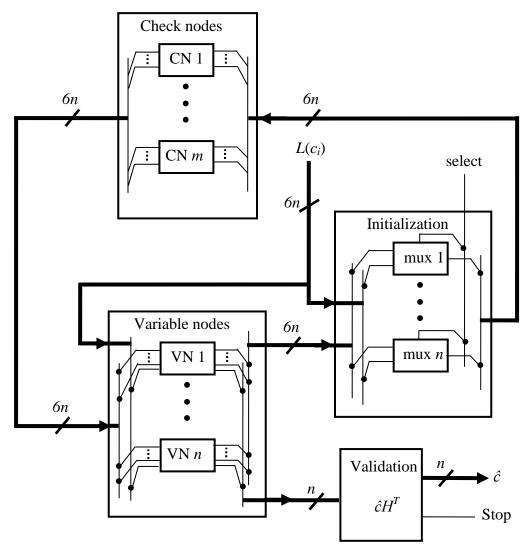

| Figure 7.11: Design of LDPC decoder.                                                | 87  |

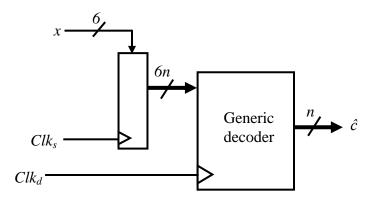

| Figure 7.12: Complete decoder system.                                               | 89  |

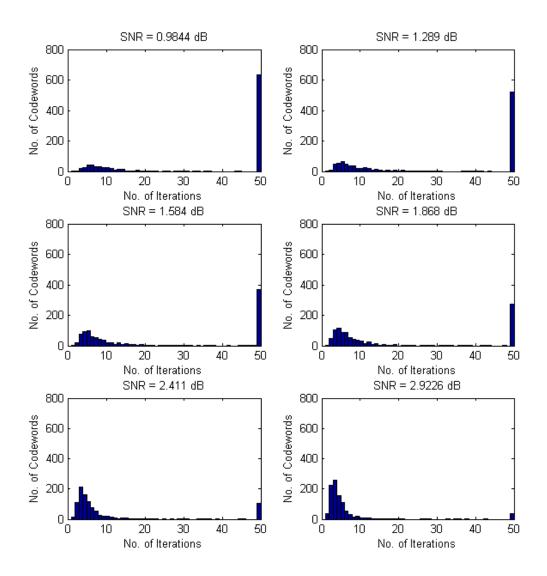

| Figure 7.13: Histogram of decoding iterations required by codewords for varying SNR | 91  |

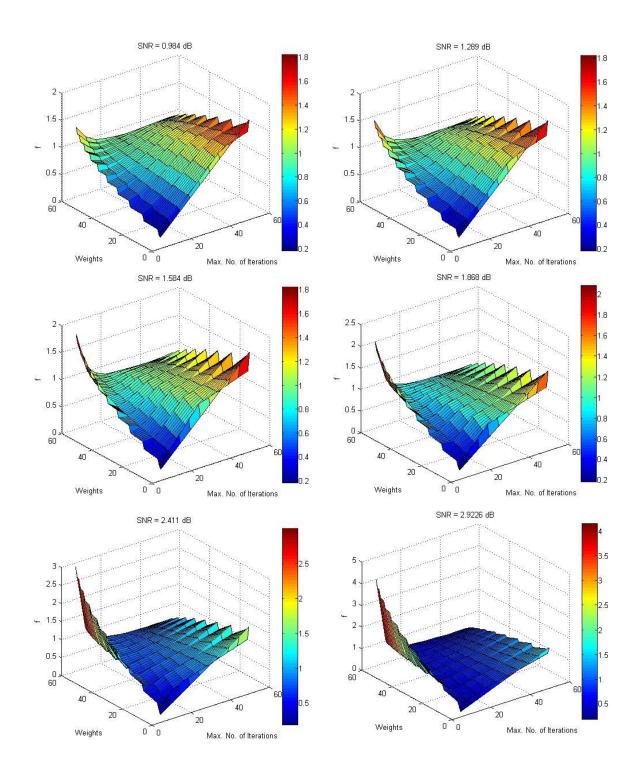

| Figure 7.14: Surface plot of $f$ for varying SNR, $Iter_{Max}$ and weights          | 98  |

| Figure A.1: A 1/2 rate convolutional encoder with constraint length 7               | 110 |

| Figure B.1: The main Quartus II display.                                            | 112 |

| Figure B.2: Creation of new project.                                                | 113 |

| Figure B.3: Adding design files.                                                    | 113 |

| Figure B.4: Choose the device family and a specific device.                         | 114 |

| Figure B.5: Other EDA tools can be specified.                                       | 114 |

| Figure B.6: Summary of the project settings.                                        | 115 |

| Figure B.7: Flow summary of the compilation report.                                 | 115 |

| Figure B.8: Creating vector waveform file.                                          | 116 |

| Figure B.9: Waveform editor window.                                                 | 116 |

| Figure B.10: Insert node or bus dialog box                                          | 117 |

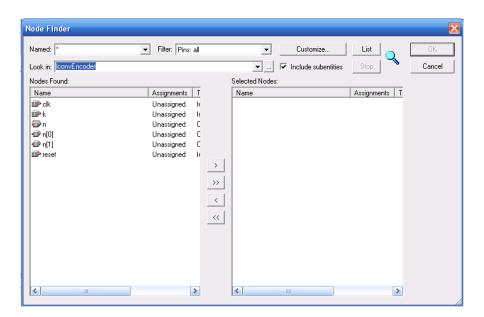

| Figure B.11: Selecting nodes to insert into the waveform editor.                    | 117 |

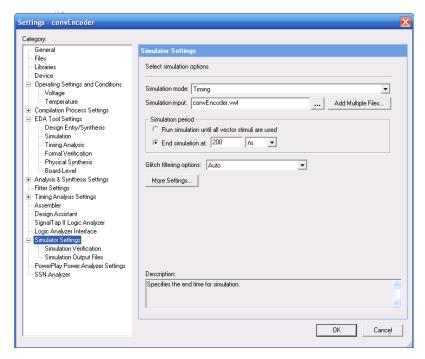

| Figure B.12: Simulator settings.                                                    | 118 |

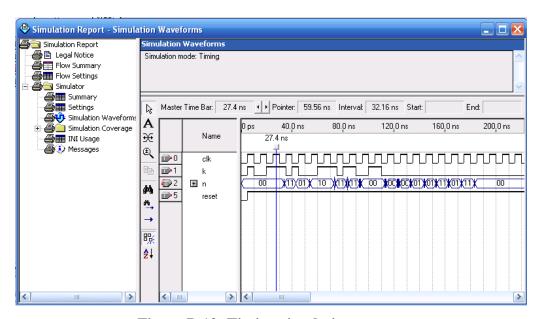

| Figure B.13: Timing simulation report.                                              | 118 |

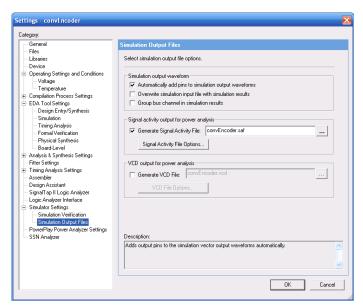

| Figure B.14: Creating .saf file.                                                    | 119 |

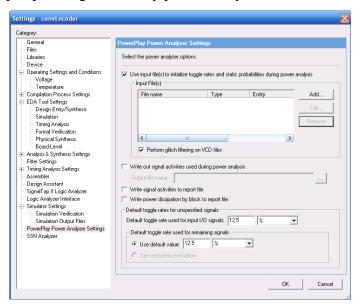

| Figure B.15: PowerPlay power analyzer tool.                                         | 119 |

| Figure B.16: Power settings.                                                        | 120 |

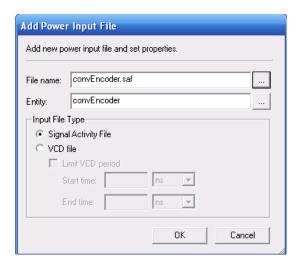

| Figure B.17: Add power input file.                                                  | 120 |

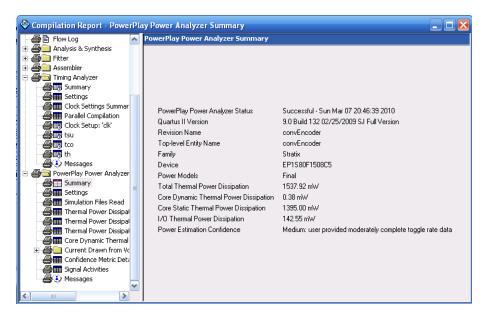

| Figure B.18: PowerPlay power analyzer summary                                       | 121 |

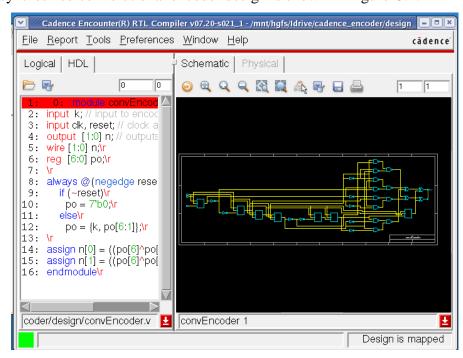

| Figure C.1: Synthesized convolutional encoder in RTL Cadence.                       | 123 |

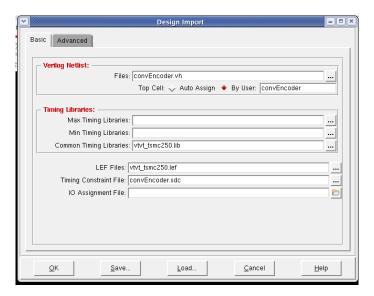

| Figure C.2: Basic design import.                                                    | 126 |

| Figure C.3: Advanced design import.                                                 | 126 |

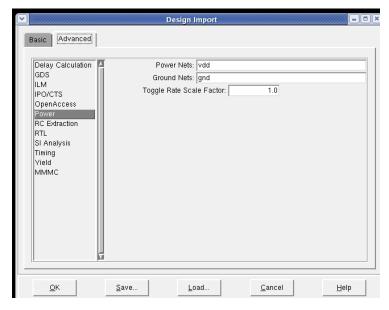

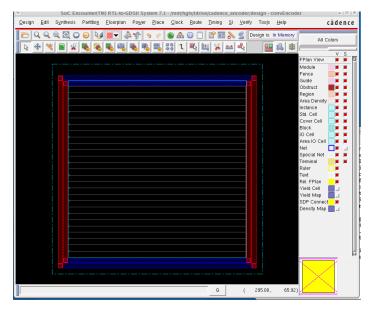

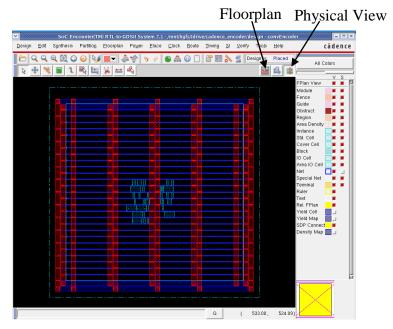

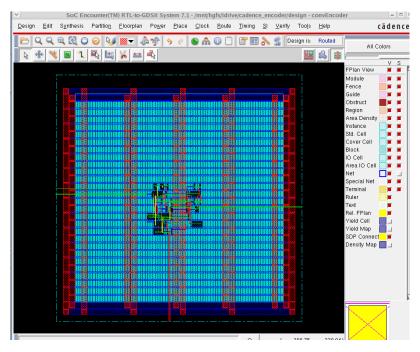

| Figure C.4: After importing the design.                                             | 127 |

| Figure C.5: Specify floorplan.                                                      | 127 |

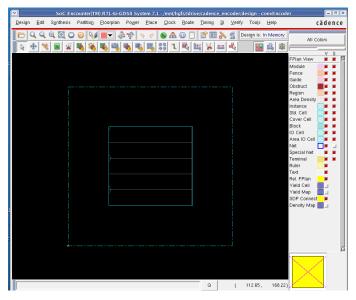

| Figure C.6: After floorPlan.                                                        | 128 |

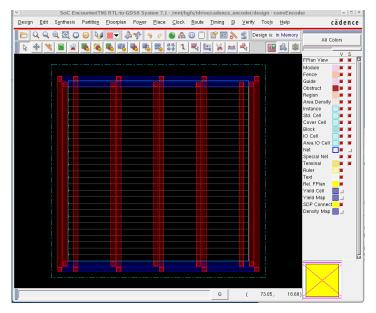

| Figure C.7: Add rings.               | 128 |

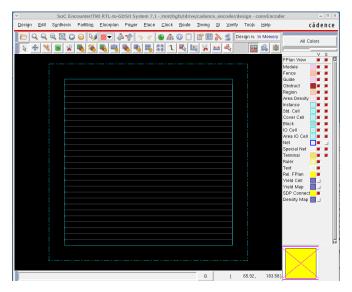

|--------------------------------------|-----|

| Figure C.8: After adding rings.      | 129 |

| Figure C.9: Add stripes.             | 129 |

| Figure C.10: After adding stripes    | 130 |

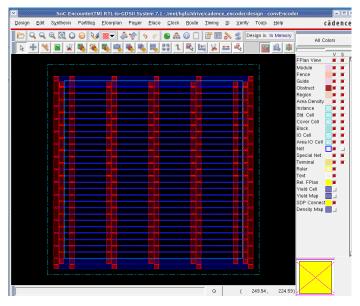

| Figure C.11: Special route.          | 130 |

| Figure C.12: After special route     | 131 |

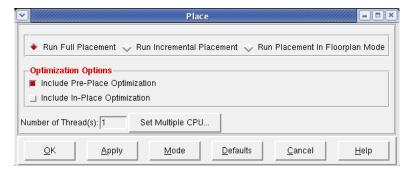

| Figure C.13: Place                   | 131 |

| Figure C.14: After placing cells.    | 132 |

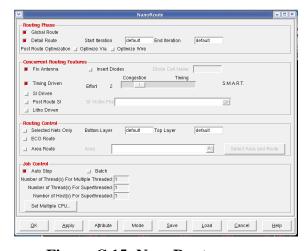

| Figure C.15: NanoRoute.              | 132 |

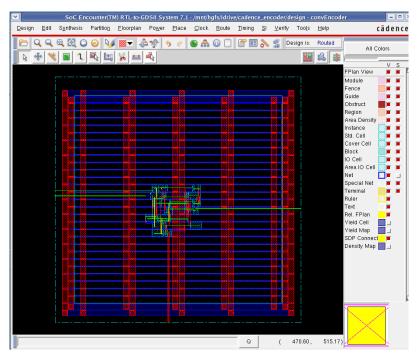

| Figure C.16: After nanoRoute.        | 133 |

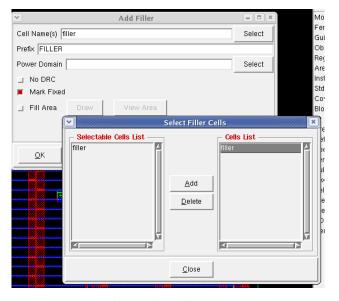

| Figure C.17: Add filler              | 133 |

| Figure C.18: After adding fillers.   | 134 |

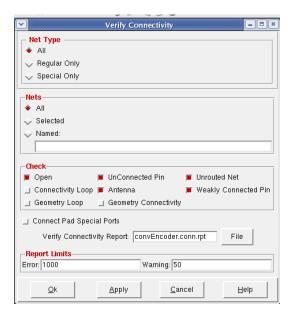

| Figure C.19: Verify connectivity.    | 134 |

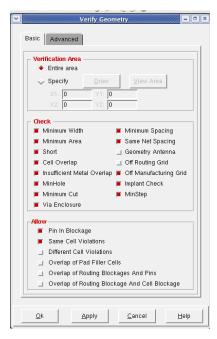

| Figure C.20: Verify geometry.        | 135 |

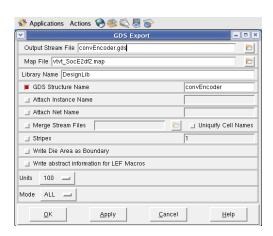

| Figure C.21: GDS export form.        | 135 |

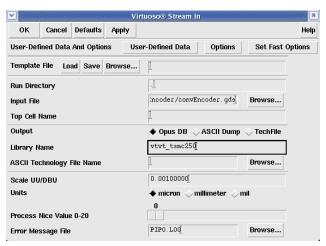

| Figure C.22: Stream in form.         | 136 |

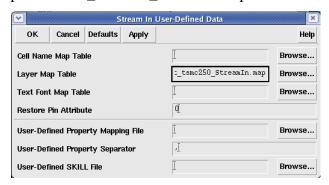

| Figure C.23: User-defined data form. | 136 |

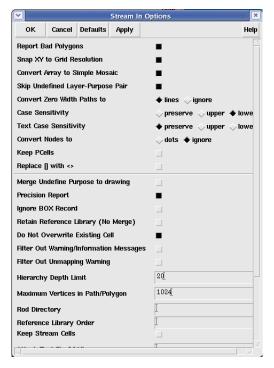

| Figure C.24: Options form.           | 137 |

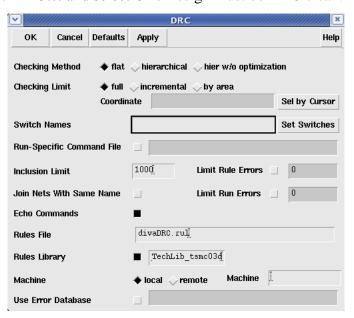

| Figure C.25: DRC form.               | 137 |

| Figure C.26: Import Verilog in.      | 138 |

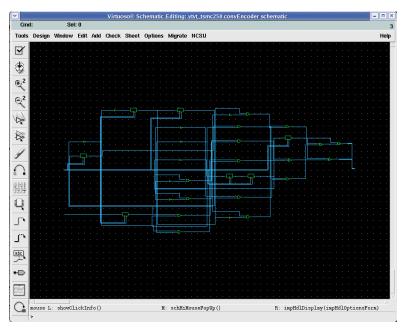

| Figure C.27: Schematic view.         | 139 |

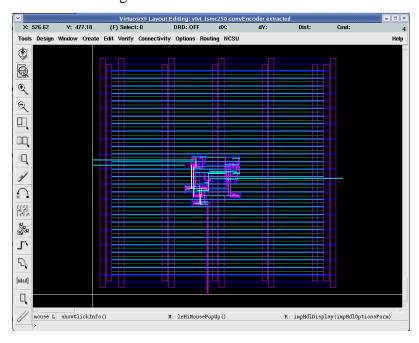

| Figure C.28: Extracted view.         | 139 |

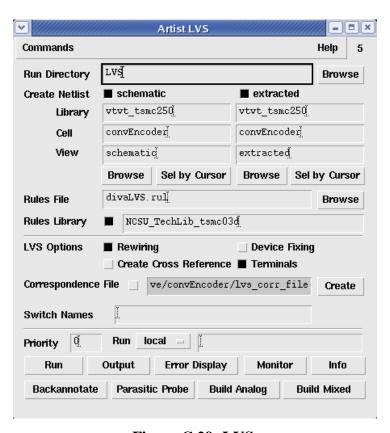

| Figure C.29: LVS.                    | 140 |

# **List of Tables**

| Table 1.1: Coding schemes for different standards.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Table 2.1: Steps for computation of parity bits $p_1$ and $p_2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13           |

| Table 4.1: Density (number of one's) of $H$ , $P_1$ and $P_2$ matrices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 33           |

| Table 4.2: Synthesis results of encoder implementation using MCIP on Stratix EP1S8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 30F1508C5.   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 37           |

| Table 4.3: Synthesis results of encoder implementation using SCIP on Startix EP1S8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 30F1508C5.   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 37           |

| Table 4.4: Synthesis results of complete encoder system using MCIP and SCIP impl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | emented on   |

| Stratix EP1S80F1508C5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 39           |

| Table 4.5: Synthesis results of LDPC encoder designed by Lee.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39           |

| Table 5.1: Synthesis results of structured encoder using LDPC codes defined in 802.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6e 47        |

| Table 5.2: Comparison of information data rate without I/O serialization of our                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | r proposed   |

| structured encoder with the encoder presented by Kim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 49           |

| Table 5.3: Comparison of coded data rate with I/O serialization of our proposed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | l structured |

| encoder with the encoder presented by Kim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 50           |

| Table 6.1: Rate select values for different code rates.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 56           |

| Table 6.2: Length select values for different code lengths.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 56           |

| Table 6.3: Number of clock cycles required for computation of $H_1$ from $H_{b1}$ for different computation of $H_1$ from $H_2$ from $H_2$ from $H_3$ from $H_3$ from $H_4$ | ferent code  |

| rates.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 63           |

| Table 6.4: Synthesis results of the flexible encoder for structured LDPC codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 68           |

| Table 6.5: Latency involved in computation of <i>H</i> for different code rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68           |

| Table 6.6: Synthesis results of flexible multi-code rate and multi-code length LDPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | encoder in   |

| Cadence RTL Compiler.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 71           |

| Table 7.1: Quantization of $\varphi$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 76           |

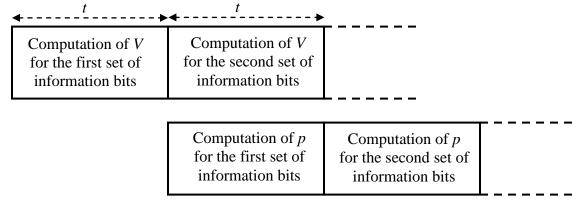

| Table 7.2: Quantization of log-likelihood ratios                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 77           |