## LOW POWER DESIGN IMPLEMENTATION OF A SIGNAL ACQUISITION MODULE

by

#### RAVI BHUSHAN THAKUR

B.Tech, Jawaharlal Nehru Technological University, INDIA 2007

#### A THESIS

submitted in partial fulfillment of the requirements for the degree

#### MASTER OF SCIENCE

Department of Electrical and Computer Engineering College of Engineering

> KANSAS STATE UNIVERSITY Manhattan, Kansas

> > 2010

Approved by:

Major Professor Dr. Don Gruenbacher

# **Abstract**

As semiconductor technologies advance, the smallest feature sizes that can be fabricated get smaller. This has led to the development of high density FPGAs capable of supporting high clock speeds, which allows for the implementation of larger more complex designs on a single chip. Over the past decade the technology market has shifted toward mobile devices with low power consumption at or near the top of design considerations. By reducing power consumption in FPGAs we can achieve greater reliability, lower cooling cost, simpler power supply and delivery, and longer battery life.

In this thesis, FPGA technology is discussed for the design and commercial implementation of low power systems as compared to ASICs or microprocessors, and a few techniques are suggested for lowering power consumption in FPGA designs. The objective of this research is to implement some of these approaches and attempt to design a low power signal acquisition module.

Designing for low power consumption without compromising performance requires a power-efficient FPGA architecture and good design practices to leverage the architectural features. With various power conservation techniques suggested for every stage of the FPGA design flow, the following approach was used in the design process implementation: the switching activity is addressed in the design entry, and synthesis level and software tools are utilized to get an initial estimate of and optimize the design's power consumption. Finally, the device choice is made based on its features that will enhance the optimization achieved in the previous stages; it is configured and real time board level power measurements are made to verify the implementation's efficacy

# **Table of Contents**

| List of I | Figure | esvii                         |

|-----------|--------|-------------------------------|

| List of T | Γable  | six                           |

| Acknow    | ledge  | ementsx                       |

| Chapter   | 1      |                               |

| Introduc  | ction. | 1                             |

| 1.1       | FPC    | GA architecture2              |

| 1.1       | .1     | Configurable Logic Blocks     |

| 1.1       | .2     | Programmable Interconnects    |

| 1.1       | .3     | Input/output Blocks           |

| 1.1       | .4     | Additional Features 6         |

| 1.2       | FPC    | GA Applications6              |

| 1.3       | Des    | ign Flow8                     |

| 1.3       | 3.1    | Design entry                  |

| 1.3       | 5.2    | Synthesis                     |

| 1.3       | 3.3    | Place and Route9              |

| 1.3       | 3.4    | Design Verification           |

| 1.3       | 5.5    | Programming and Configuration |

| 1.4       | Mot    | ivation and objectives10      |

| 1.5       | The    | sis outline11                 |

| Chapter   | 2      |                               |

| Related   | work   | in Low power FPGA design      |

| 2.1       | Dev    | ice level techniques14        |

| 2.2       |        | tem level techniques14        |

| 2.2       | 2.1    | Voltage scaling               |

| 2.2       | 2.2    | Clock gating                  |

| 2.2       | 2.3    | Clock scaling                 |

| 2.2       | 2.4    | Glitch reduction              |

| 2.3       | FPC    | GA CAD tools                  |

| Chapter   | 3      | 19                            |

| Design meth | odologies for Low power design              | . 19 |

|-------------|---------------------------------------------|------|

| 3.1 FP      | GA power components                         | . 19 |

| 3.1.1       | In-Rush power                               | . 19 |

| 3.1.2       | Configuration power                         | . 19 |

| 3.1.3       | Static power                                | . 20 |

| 3.1.4       | Dynamic power                               | . 20 |

| 3.2 FP      | GA power modes                              | . 21 |

| 3.2.1       | Power-up mode                               | . 21 |

| 3.2.2       | Configuration mode                          | . 21 |

| 3.2.3       | Standby mode                                | . 22 |

| 3.2.4       | Active mode                                 | . 22 |

| 3.2.5       | Sleep mode                                  | . 22 |

| 3.3 Lo      | w power design approaches                   | . 23 |

| 3.3.1       | Proper device selection                     | . 24 |

| 3.3.2       | Voltage and temperature control.            | . 26 |

| 3.3.3       | Supply voltage scaling and Power switching  | . 27 |

| 3.3.4       | Reducing clock activity and signal activity | . 27 |

| 3.3.5       | Clock frequency scaling                     | . 29 |

| 3.3.6       | CAD tools                                   | . 30 |

| Chapter 4   |                                             | . 31 |

| Hardware ar | nd Software                                 | . 31 |

| 4.1 De      | vice Selection                              | . 31 |

| 4.2 Cy      | clone II FPGA Architecture                  | . 32 |

| 4.2.1       | Interconnect structures                     | . 32 |

| 4.2.2       | Embedded multipliers                        | . 33 |

| 4.2.3       | Embedded memory blocks                      | . 33 |

| 4.2.4       | Cyclone II Logic Element structure          | . 35 |

| 4.3 Qu      | artus II and Power Play power analyzer      | . 36 |

| 4.3.1       | Power estimation and analysis               | . 38 |

| 4.3.2       | Compilation report                          | . 40 |

| Chapter 5   |                                             | . 42 |

| Design  | Wor   | k                                        | 42  |

|---------|-------|------------------------------------------|-----|

| 5.1     | HD    | DL design code                           | 42  |

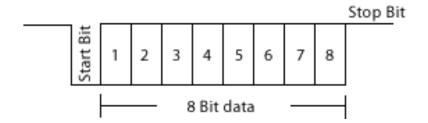

| 5.      | 1.1   | Serial Module                            | 43  |

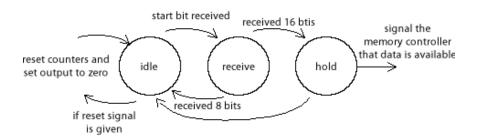

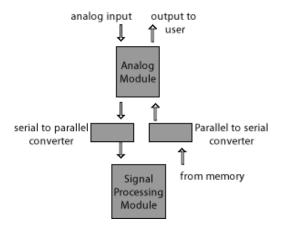

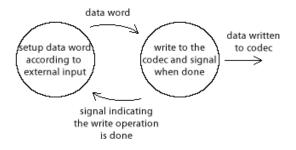

| 5.      | 1.2   | Analog module                            | 45  |

| 5.      | 1.3   | Filter Module                            | 48  |

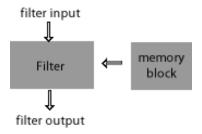

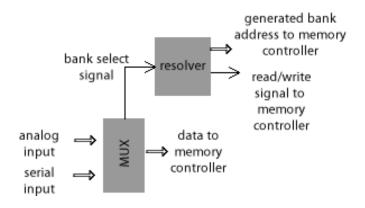

| 5.      | 1.4   | Memory module                            | 50  |

| 5.      | 1.5   | User interface                           | 52  |

| 5.2     | Tes   | st board design                          | 53  |

| 5.      | 2.1   | Design schematic                         | 54  |

| 5.      | 2.2   | Preparing for layout                     | 56  |

| 5       | 2.3   | Design layout                            | 61  |

| Chapte  | r 6   |                                          | 76  |

| Design  | powe  | er optimization and preliminary analysis | 76  |

| 6.1     | De    | sign power analysis strategy             | 76  |

| 6.2     | Pre   | eliminary device analysis                | 79  |

| 6.3     | Ind   | lividual module analysis                 | 80  |

| 6       | 3.1   | Serial module                            | 80  |

| 6.      | 3.2   | DSP module                               | 81  |

| 6.      | 3.3   | Memory module                            | 84  |

| 6       | 3.4   | Analog module                            | 85  |

| Chapte  | r 7   |                                          | 87  |

| Final d | esign | operation and analysis                   | 87  |

| 7.1     | De    | sign operation                           | 87  |

| 7.2     | De    | sign simulation and power analysis       | 91  |

| 7.      | 2.1   | Input mode                               | 91  |

| 7.      | 2.2   | Output mode                              | 92  |

| 7.      | 2.3   | Serial shutdown mode                     | 93  |

| 7.      | 2.4   | Analog shutdown mode                     | 94  |

| 7.      | 2.5   | Device power down mode                   | 95  |

| 7.3     | Rea   | al time board measurement challenges     | 96  |

| 7.4     | Me    | easurement and Test setup                | 100 |

| 7.4.1        | Establishing a baseline                                     | 100 |

|--------------|-------------------------------------------------------------|-----|

| 7.4.2        | Design test setup and measurements                          | 102 |

| 7.4.3        | Analyzing results                                           | 106 |

| Chapter 8    |                                                             | 108 |

| Conclusions. |                                                             | 108 |

| 8.1 Futi     | ure work                                                    | 109 |

| Bibliography | ·                                                           | 111 |

| Appendix A   | - Design top level HDL code                                 | 114 |

| Appendix B   | - Analog module HDL code                                    | 116 |

| Appendix C   | - DSP module HDL code                                       | 125 |

| Appendix D   | - Serial module HDL code                                    | 128 |

| Appendix E   | - Memory module HDL code                                    | 133 |

| Appendix F   | Clock distributor and device power down components HDL code | 145 |

| Appendix E   | - MATLAB code for generating the filter coefficients        | 146 |

| Appendix F   | - Analog module testbenches                                 | 148 |

| Appendix G   | - Serial module testbenches                                 | 155 |

| Appendix H   | - DSP module testbenches                                    | 158 |

| Appendix I - | Memory module testbenches                                   | 162 |

| Appendix I - | Signal acquisition module operating modes testhenches       | 170 |

# **List of Figures**

| Figure 1-1: Configurable elements of a FPGA [3]             | 3  |

|-------------------------------------------------------------|----|

| Figure 1-2: FPGA logic cell                                 | 4  |

| Figure 1-3: FPGA slice                                      | 4  |

| Figure 1-4: FPGA design flow [4]                            | 8  |

| Figure 2-1: Spartan -3 core power consumption [8]           | 15 |

| Figure 2-2: Clock gating techniques                         | 16 |

| Figure 3-1: SRAM FPGA current components                    | 21 |

| Figure 3-2 FPGA power profile [22]                          | 23 |

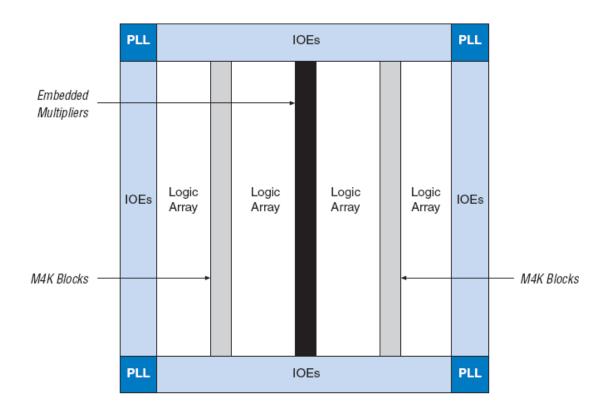

| Figure 4-1: Cyclone II FPGA architecture [3]                | 32 |

| Figure 4-2: Cyclone II FPGA Logic Element [3]               | 35 |

| Figure 4-3: Quartus II power driven synthesis flow [24]     | 38 |

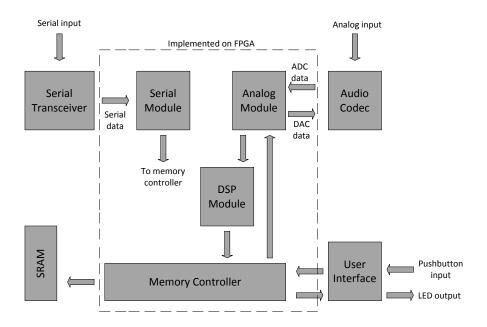

| Figure 5-1: Design block diagram                            | 43 |

| Figure 5-2: RS232 frame structure                           | 44 |

| Figure 5-3: Serial module FSM flow                          | 44 |

| Figure 5-4: Data formatting modules                         | 46 |

| Figure 5-5: Analog module operation flow                    | 48 |

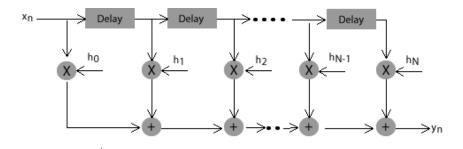

| Figure 5-6: FIR filter block diagram                        | 48 |

| Figure 5-7: Filter module block diagram                     | 49 |

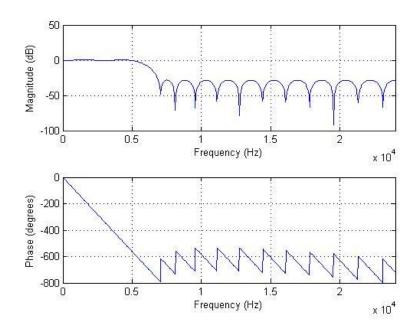

| Figure 5-8: FIR filter magnitude and phase plots            | 50 |

| Figure 5-9: Bank select module                              | 51 |

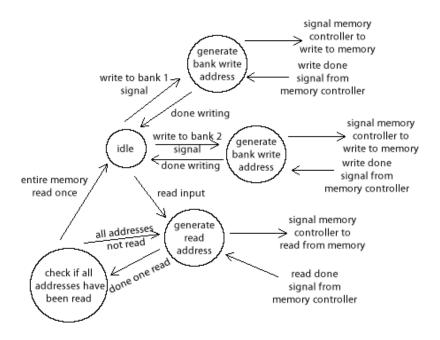

| Figure 5-10: Memory module state flow diagram               | 52 |

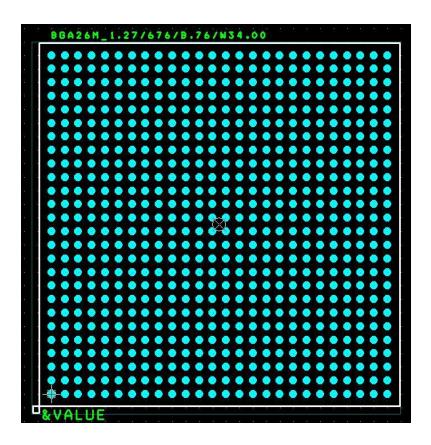

| Figure 5-11: 676 pin BGA foot print in the standard library | 58 |

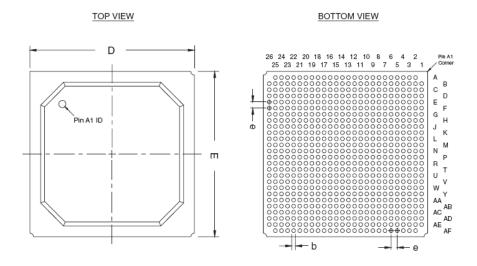

| Figure 5-12: 674 pin BGA package outline [25]               | 59 |

| Figure 5-13: Modified 674 pin BGA footprint                 | 60 |

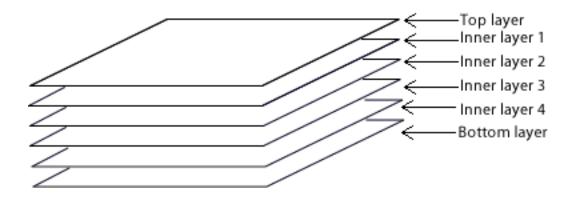

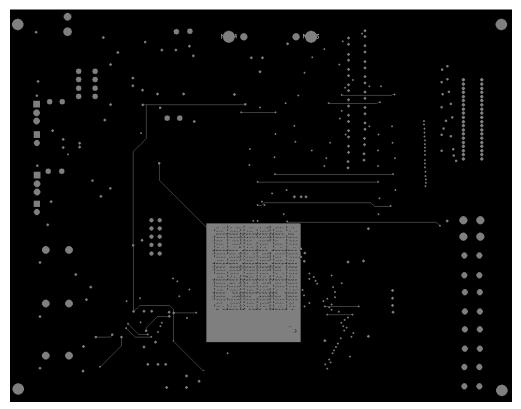

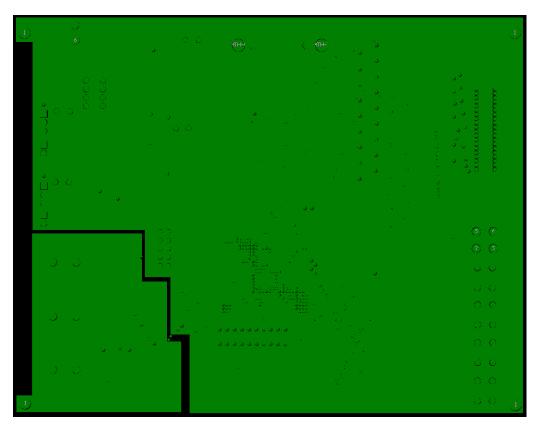

| Figure 5-14: Test board layer stack up                      | 62 |

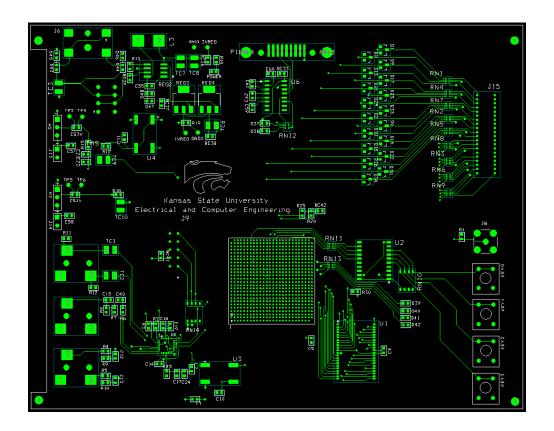

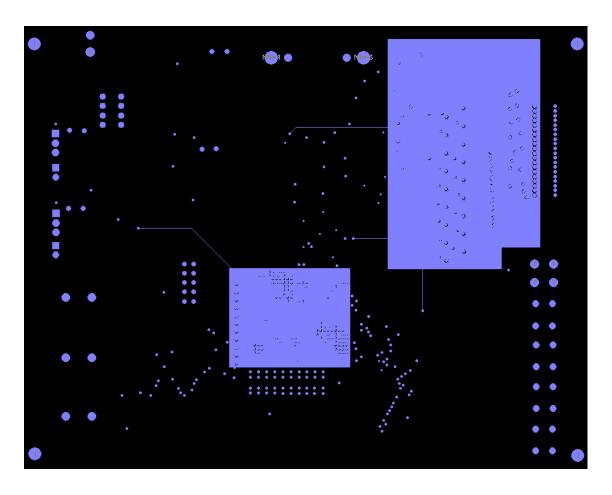

| Figure 5-15: PCB Top layer                                  | 64 |

| Figure 5-16: PCB Bottom layer component placement           | 65 |

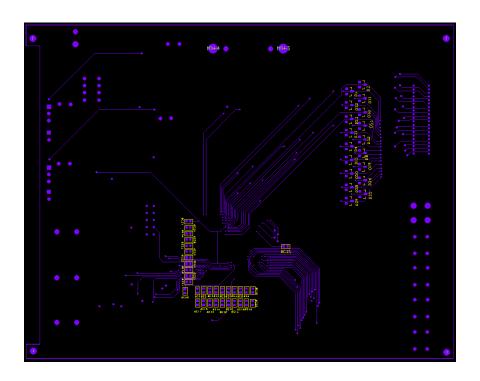

| Figure 5-17: PCB Inner layer 1                              | 66 |

| Figure 5-18: Via thermal relief and inner clearance         | 67 |

| Figure 5-19: Copper pour islands                            | 68 |

| Figure 5-20: Copper pour with proper clearance and width    | 68 |

| Figure 5-21: Via connection flooded onto the plane          | 69 |

| Figure 5-22: PCB inner layer 3                              |    |

| Figure 5-23: PCB Inner layer 2                              | 70 |

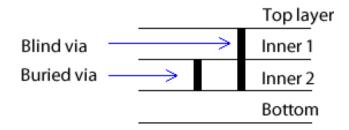

| Figure 5-24: Blind and Buried vias                          |    |

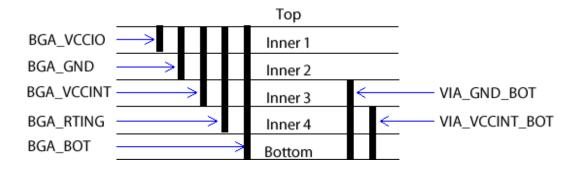

| Figure 5-25: Vias created for BGA routing                   |    |

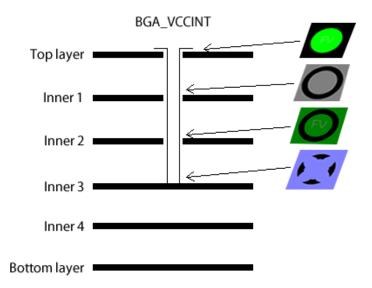

| Figure 5-26: Via BGA_VCCINT                                 |    |

| Figure 5-27: FPGA routing on Inner layer 4 and Bottom layer |    |

| Figure 5-28: Parallel trace routes on adjacent layers                            | 75  |

|----------------------------------------------------------------------------------|-----|

| Figure 6-1: Design power analysis flow implemented                               | 78  |

| Figure 6-2: Serial module clock control block diagram                            | 80  |

| Figure 6-3: DSP module clock control block diagram                               | 82  |

| Figure 6-4: Memory module clock control block diagram                            | 84  |

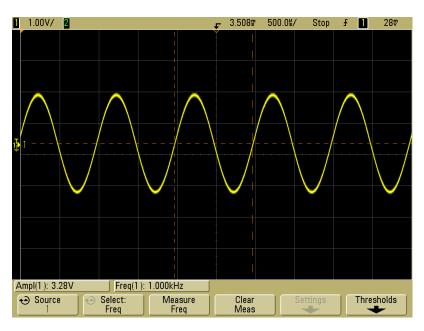

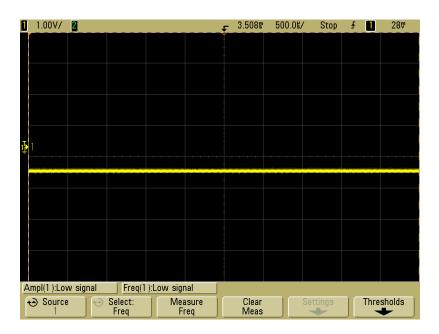

| Figure 7-1: Analog output for 1 kHz input frequency                              | 89  |

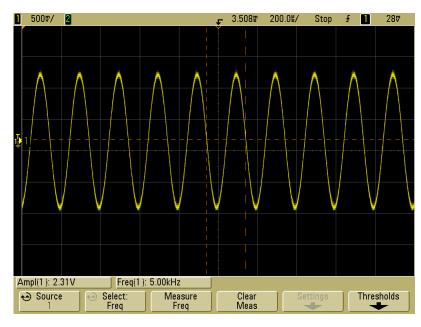

| Figure 7-2: 5 kHz sine wave data sent over serial interface                      | 89  |

| Figure 7-3: Analog output for 13 kHz input frequency                             | 90  |

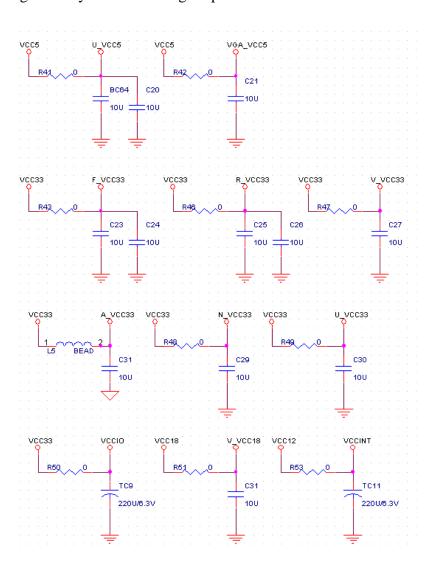

| Figure 7-4: Power supply section of the DE2 board schematic [27]                 | 98  |

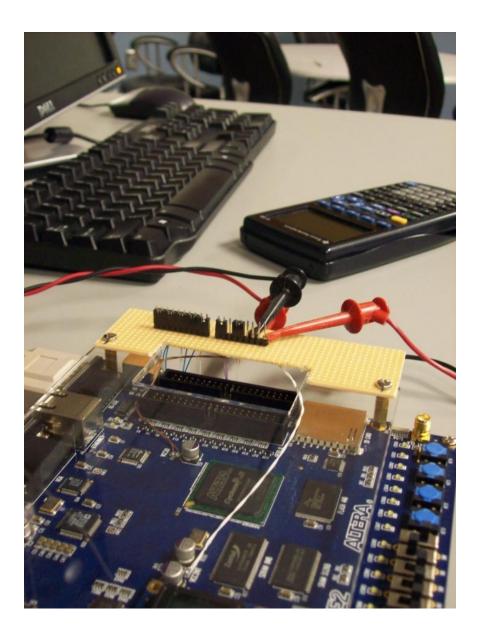

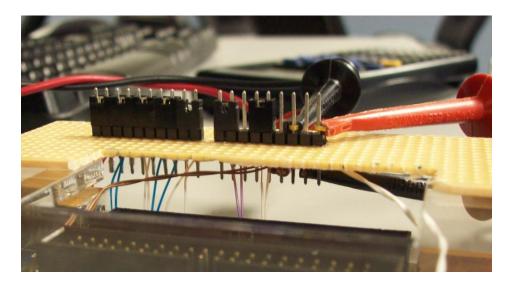

| Figure 7-5: Modified DE2 board to allow FPGA current measurements                | 99  |

| Figure 7-6: Ammeter probes connected to the header pins for current measurements | 100 |

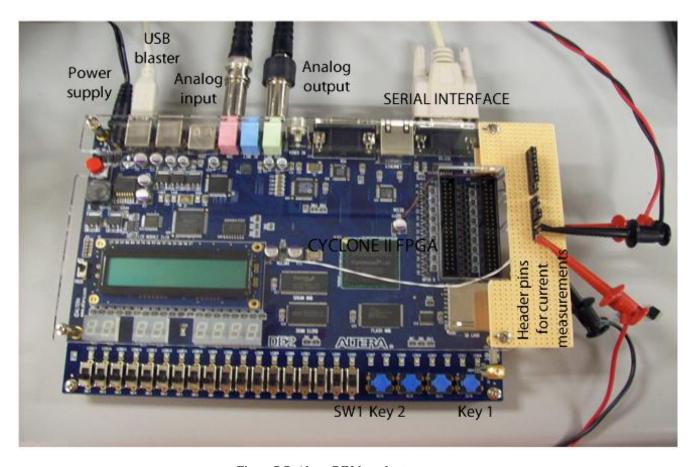

| Figure 7-7: Altera DE2 board setup                                               | 103 |

# **List of Tables**

| Table 1-1: Available technology choices [2]                                         | 2       |

|-------------------------------------------------------------------------------------|---------|

| Table 3-1: Power optimization achieved [24]                                         | 23      |

| Table 3-2: Results summary [6]                                                      | 24      |

| Table 3-3: FPGA technology summary [1]                                              | 26      |

| Table 3-4: Comparing toggle rates of binary and gray code                           | 28      |

| Table 3-5: One hot FSM encoding method                                              | 29      |

| Table 5-1: Package dimensions [25]                                                  | 59      |

| Table 5-2: Test board layer functions                                               | 63      |

| Table 6-1: Preliminary FPGA device power test results                               | 79      |

| Table 6-2 : Serial module power analysis results                                    | 81      |

| Table 6-3: Filter module device utilization test results                            | 82      |

| Table 6-4: Filter module power consumption                                          | 83      |

| Table 6-5: Effect of clock gating on filter module dynamic power consumption        | 83      |

| Table 6-6: Effect of clock gating on memory module                                  | 85      |

| Table 6-7: Analog module power analysis result                                      | 86      |

| Table 7-1: Design input mode power analysis results                                 | 92      |

| Table 7-2: Design output mode power analysis results                                | 93      |

| Table 7-3: Design normal operation power analysis results                           | 93      |

| Table 7-4: Device serial module shut down power analysis results                    | 94      |

| Table 7-5: Design codec shutdown mode power analysis results                        | 94      |

| Table 7-6: Design power down mode power analysis results                            | 95      |

| Table 7-7: Base line test power analysis result                                     | 101     |

| Table 7-8: Power analysis report on the current drawn from voltage supplies         |         |

| Table 7-9: Baseline design real time current measurements                           | 102     |

| Table 7-10: Reported voltage supply current drawn values                            | 105     |

| Table 7-11: Measured voltage supply current drawn values                            | 105     |

| Table 7-12: Change in current value from base static current for each mode          |         |

| Table 7-13: Comparing the measure and reported VCCIO supply total current drawn for | or each |

| mode                                                                                | 106     |

# Acknowledgements

I would like to take this opportunity to express my gratitude to Dr. Don Gruenbacher, Dr William Kuhn and Dr Andrew Rys for their inspiration and constant support throughout my Masters. I would like to thank Dr Gruenbacher for his patience and guidance that made the completion of this work possible. Finally, I would like to thank my family and friends for their unrelenting support and encouragement.

# **Chapter 1**

## Introduction

A Field Programmable Gate Array, FPGA, is a digital device that is hardware programmable by the user so that a specific design can be configured for a task. Depending on the device used, the design can be either burned temporarily, semi-permanently or loaded from an external memory every time during device power up. FPGAs have found immense application potential in fields of communication, computing and consumer electronics due to the design flexibility that it provides. The FPGA platform allows for the design to be modified even after the system has been manufactured. This is a highly desirable trait for applications that need to have a fast time to market and it has enabled system engineers to cope with changing market requirements.

Application Specific Integrated Circuits (ASICs), fuse programmed Custom Gate Arrays (CGAs), Programmable Array Logic (PAL), Programmable Logic Array (PLA) and Programmable Logic Devices (PLDs) [1] are the other Integrated Circuit technologies available to designers for implementing digital logic. ASICs have always been preferred by the industry for design and implementation of digital systems, but over the last decade we have seen FPGA technology come a long way from a few thousand gates to more than a million gates in recent times. It is this increase in the gate density and the capability to operate at high clock frequencies that has enabled the use of FPGAs in many applications for which ASICs were preferred earlier.

With the industry requirement of making the systems as small and portable as possible, the factors on top of every design team are the size and power considerations. These portable systems need to have high functionality and are expected to have battery lives lasting weeks or even months at a time. While ASICs have been successfully used in the past to provide such a requirement, an increased need for a fast time to market has proven the use of FPGAs to be more

beneficial. Table 1-1 below [2] summarizes the design choices available for electronic module design. The factors used to make the comparison are the cost, time to market and the flexibility offered by the platform. The platform referred to as custom processor is defined as a product designed for a particular application while the generic microprocessor refers to a general off-the-shelf microprocessor. The speed of the technology is decreasing while its design flexibility increases as you go down the table

| Technology                | Performance/<br>cost | Time until running | Time to high performance | Time to alter functionality |

|---------------------------|----------------------|--------------------|--------------------------|-----------------------------|

| ASIC                      | Very High            | Very Long          | Very Long                | Impossible                  |

| Custom processor/<br>DSP  | Medium               | Long               | Long                     | Long                        |

| FPGA                      | Low-Medium           | Short              | Short                    | Short                       |

| Generic<br>microprocessor | Low-Medium           | Short              | Not attainable           | Short                       |

Table 1-1: Available technology choices [2]

With all of the technologies available, it is up to the designers to choose the platform most suited for the application they are designing. This choice has to be made considering all the features of a particular technology that will allow the designers to meet design specifications and market requirements. Bio-medical devices are one field that has utilized these technologies. Systems have been implemented in ASICs and microprocessors, and in this thesis we explore the viability of an FPGA based system design of a module for application in this field. In this chapter, I have provided an overview of the FPGA device architecture, applications, design flow and described the objectives of this thesis work.

#### 1.1 FPGA architecture

The FPGA is made up of a large number of identical logic cells also known as logic elements (LE) [1]. The term logic cell (LC) is used by Xilinx while Altera refers to them as logic elements;

both describing the same elemental component of the FPGA architecture. The LEs or LCs are grouped to from a slice; there are two LEs in a slice. These logic elements or logic cells are the core building blocks of an FPGA. The number of logic cells/elements has increased from 64 in the Xilinx XC2064 to 200,000 in the Altera Cyclone III device family and this value is increasing with every new device family introduced.

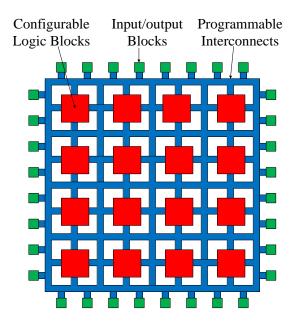

These individual cells are interconnected by a matrix of wires and programmable switches. The user defined operation is implemented by specifying each block with a simple logic function and closing the programmable switches and combining these basic blocks to get the desired functional logic block. A more complex design is implemented by interconnecting these blocks to create the desired digital logic circuit. The three configurable components of an FPGA are shown in the figure below:

Figure 1-1: Configurable elements of a FPGA [3]

- Configurable Logic Blocks (CLBs) or Logical Array Blocks (LABs)

- Programmable Interconnects

• Input/output Blocks (I/O)

## 1.1.1 Configurable Logic Blocks

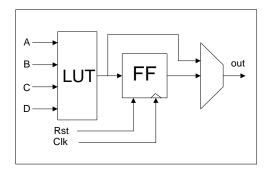

CLBs (as referred to by Xilinx) are the basic logic units of the FPGA [1]. Logic array blocks or LABs as referred to by Altera, have the same concept as the CLBs. Every CLB consists of a number of slices, each slice consisting of functional blocks called Logic Cells. These Logic Cells have in them Lookup Tables (LUTs) which are configurable switch matrices with 4 or 6 inputs, multiplexers and flip-flops.

Figure 1-2: FPGA logic cell

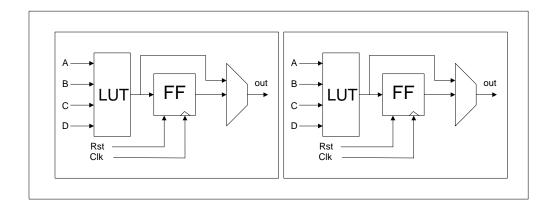

Two of these logic cells make up a slice and a CLB consists of 1, 2 or 4 slices depending on the FPGA vendor and a particular FPGA family. The basic difference between CLBs and LABs is the definition of what components constitute a logic cell.

Figure 1-3: FPGA slice

As the name suggests the LUT stores the truth table of the combinational logic function to be performed [1]. Every combination of the input signals points to a particular cell in the look up table, which contains the desired value. In certain earlier architectures, it was suggested that the use of multiplexers (MUX) instead of LUTs was more advantageous. This approach however was not adopted because the MUX-based architecture did not provide high speed carry logic chains that help speed up arithmetic processing. The LUT can be formed using SRAM cells, EEPROM cells, anti-fuses or FLASH cells. They are SRAM based in many devices which allows for the use of a 4-bit LUT as a 16x1 RAM block or a 16 bit shift register.

#### 1.1.2 Programmable Interconnects

While the CLBs perform the required logic functions, the programmable interconnects are responsible for routing the signals between CLBs or from the CLBs to and from the I/O blocks. The responsibility of performing this routing function is handled by the design software, which greatly reduces the complexity of the design procedure. These interconnects are either local interconnects available to individual CLBs or global interconnects that route signals between the CLBs. Some FPGAs are also provided with dedicated interconnects for improving device performance like a global clock network to route critical clock paths and carry chain logic between the LEs to assist in speeding up arithmetic operations.

#### 1.1.3 Input/output Blocks

I/O blocks contain circuitry that facilitates transfer of signals to and from package pins to the internal signal lines. These blocks are distributed on the periphery of the FPGA architecture and are provided with registers to achieve glitch free signal switching. Devices that are provided with high speed I/O blocks and embedded transceiver modules are a great advantage in

communication applications. Current FPGA devices support many I/O standards such as 3.3V LVTTL, 3.3V LVCMOS, 1.5V etc in the Cyclone II device family [4].

#### 1.1.4 Additional Features

In addition to the blocks described above FPGA architectures are provided with additional features like [1]:

- Embedded RAM: To provide for the memory requirements of the user applications, FPGA architectures are provided with embedded RAM block arrays. Depending on the architecture these blocks can be located on the periphery of the device, arrange into columns or scattered within the device. These blocks can be used independently or as a single block depending on the application.

- Embedded DSP blocks: Arithmetic operations like multipliers and adders are required to perform DSP applications. These operations, especially multiplication, when implemented by connecting large number of CLBs can be logic consuming and are prone to glitch errors. The embedded DSP blocks provide error free operation and also consume less power while taking up less logic area on the device.

- Embedded Microprocessors: Some FPGA architectures have microprocessor cores embedded in them, referred to as microprocessor cores. These cores can be either hard microprocessor cores where the core is a dedicated part of the IC or soft microprocessor cores where the core is implemented in the general purpose logic cells.

## 1.2 FPGA Applications

ASIC designers have always used FPGAs as a resource to test and verify their system design before the final ASIC implementation. Nowadays with the development of advanced FPGAs, they are being used for just about any application. These high-performance FPGAs contain features like embedded processors and high-speed input/output (I/O) interfaces to name a few, which enable their use in the design of many Digital Signal Processing (DSP) applications and System on Chip (SOC) designs. FPGAs are finding their way into the following Digital Logic fields [1].

- Custom Silicon: As discussed earlier, FPGAs are being used in applications that previously could only be done in either custom silicon or ASICs.

- Digital Signal Processing: Traditionally DSP has been implemented on DSP processors which are specialized microprocessors whose architecture has been optimized to quickly and efficiently perform the operations required to perform a DSP algorithm. With current FPGA technology enabling the embedding of dedicated arithmetic blocks and availability of large amounts of RAM on chip, we are seeing FPGAs being considered for many DSP applications.

- Embedded microcontrollers: Microcontrollers have been used in applications that are required to provide simple control functions at a low cost. Generally, embedded microcontrollers are application specific with memories, I/O etc packaged with the processor. FPGAs are more than capable of providing the functionality of the microcontroller and with the costs falling, the end result is a more customizable and flexible system

- Physical layer communications: In network systems FPGAs have been used to interface communication chips with the high level networking protocols layers.

- Reconfigurable computing: This concept was proposed in the 1960s in a paper by Gerald Estrin [1]. It talked about a computer built with a standard processor and an array of

reconfigurable hardware. The core processor controls the functionality of the reconfigurable hardware *i.e.* FPGA which is tailor made to perform the specific task at hands such as DSP or image processing and after the task was done the same reconfigurable hardware could be used to perform any other task.

## 1.3 Design Flow

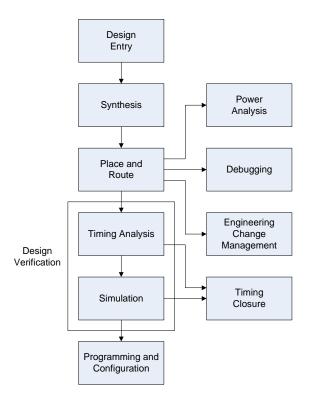

The figure here shows the standard design flow of an FPGA application design process [5]

Figure 1-4: FPGA design flow [4]

## 1.3.1 Design entry

For the implementation of any design in an FPGA the digital design can be created with either a schematic digital design editor, Hardware Description Language (HDL), or a combination of the two. Selection of the design entry method is up to the designer and the design that needs to be implemented. For a complex design, the schematic design approach is recommended, but if the designer is comfortable with an algorithmic approach, then an HDL is

the better choice. HDL entry is faster and isolates the designer from the details of the hardware implementation, but it lags in performance and if you are hardware oriented, the schematic entry method is a better choice.

## 1.3.2 Synthesis

You can synthesize your design once the design files have been created. The synthesis process converts HDL code into a device netlist format. The device netlist is the gate level circuit as described by the HDL code. The synthesis process will check code syntax and analyze the hierarchy of your design which ensures that your design is optimized for the design architecture you have selected. The device netlist file generated is used in the next step.

#### 1.3.3 Place and Route

This step of the design flow matches the logic and timing requirements of the project with the available resources of the target device. It assigns logic functions to the best logic cell location to meet routing and timing requirements, and selects appropriate interconnection paths and pin assignments. After the place and route is done, the design is tested and debugging is performed if needed. The power analysis step, after place and route, helps the designer compare block level power consumption values to the design specifications and alter the design if he wishes to. This assists in power consumption control of the final design.

#### 1.3.4 Design Verification

Simulation and Timing analysis of the design constitute design verification. These are performed using EDA simulation tools to test functional and timing validity of the design and compare the results to the original design requirements. Verifications can be either RTL simulations or post -translation simulations. In RTL or behavioral simulations the code is tested to check if it performs as intended. This simulation is very fast and any errors or concerns can be

easily traced back to the HDL code. The post translation or functional simulations are performed to check the logical operation of the circuit generated after the synthesis step. If the circuit operation is not as intended, the changes in the design are made and the design steps are performed again.

## 1.3.5 Programming and Configuration

Configuration is a process in which the designed circuit (a bitstream file) is downloaded into the FPGA. Through this method the FPGA is configured from within design software.

## 1.4 Motivation and objectives

FPGAs have been used in the development of many portable systems and the fact that the above mentioned features can be utilized to optimize and enhance the systems functioning as per the user's requirements, have made them a very popular platform for digital logic implementation. With power consumption becoming a major concern in portable wireless devices, many researchers have studied and quantified FPGA power consumption and proposed strategies to reduce it.

This thesis work was done to reduce power consumption in such an application. The following objectives were achieved in this research

- 1. Proposed low power design methodologies were studied and their effects were quantified

- 2. A wireless signal acquisition module was designed and tested to confirm proper functioning

- 3. Design features were added to reduce the power consumption in the system

- 4. Simulation and power estimation was used to observe the efficacy of the design methods used to reduce power consumption

- 5. A custom test board was designed to perform real time on-board power measurements

- 6. Power estimation results were compared to real time FPGA current measurements to gauge the accuracy of the estimator tools and the testing approach taken.

#### 1.5 Thesis outline

This thesis is organized as follows:

In chapter 2, I provide details of related work done in the field of low power FPGA designs. In this chapter, the research work done on the techniques for low power design implementation is categorized, and the work done in each of the categories is discussed.

In chapter 3, the various FPGA power components are described and the modes of operation of an FPGA device are discussed. This is followed by discussion on the standard design methodologies that are practiced to achieve low power FPGA design.

In chapter 4, the hardware and software choice i.e. the device choice and the CAD software choices made are discussed, outlining their advantages and other features that make them suitable for the purposes of this thesis work

In chapter 5, the design work done for this thesis is discussed. The HDL code written is described followed by the details about the process involved in designing a custom board for making power measurements.

In chapter 6, the details of the low power techniques used in the HDL coding process are discussed along with the strategies implemented for testing purposes. The results of power analysis done on the individual modules using the power analyzer tool are discussed.

In chapter 7, the device operation is demonstrated and the strategy implemented for the power analysis done and the work done to allow for making real time board measurements are described. The real time board measurements made are provided in this chapter.

In chapter 8, conclusions are drawn and future work is discussed.

# **Chapter 2**

# Related work in Low power FPGA design

With the development of high density FPGAs with embedded features as mentioned above, it is possible now to choose FPGAs for applications that in the past were primarily implemented using ASCIs and microprocessors. As mentioned earlier, high NRE costs associated with ASICs along with the difficulty in prototyping designs [1] has caused designers to choose FPGAs for those applications. For microprocessors, one thing that affects applications implemented on them is the fact that in a few years the processor will become obsolete [2]. The most radical and expensive solution to this problem of processor obsolescence is to design the system all over again around a new processor. This results in loss of hundreds of man hours which could be spent refining the application. Depending on the life of the application, this solution is temporary at best.

In this chapter, the research work done in the field of low power FPGA design is presented. As mentioned in a previous chapter, designing for low power consumption without compromising performance requires power-efficient FPGA architecture and good design practices to leverage the architectural features. Power conservation techniques are provided for every level of the FPGA design flow. The researchers in [6] have taken a comprehensive look at these techniques at every stage of the application design process. These techniques can be broadly classified into: device level techniques, where the manufacturing process, elemental circuitry and device architecture are the points of interest; system level techniques where the digital logic implementation and device operating conditions are targets for these techniques; and CAD tools at design software level that can assist designers in the optimization process.

## 2.1 Device level techniques

Power reduction techniques have been suggested for as low as the transistor level. The affect of transistor gate length reduction coupled with reduction in supply voltage is shown to have a substantial improvement in dynamic power consumption reduction of an FPGA [7] [8]. Methods are suggest in [9] for controlling CMOS leakage at transistor level, and reducing switching power by using low voltage swing flip flops. Models generated in [10] for leakage and timing variations in an FPGA are used to improve the device design and architecture. This results in substantial improvement in leakage reduction. Improvements in routing architecture also helps reduce power by reducing the number of routing elements needed. Other architectural changes like increasing LUT size from 4 inputs to either 6 or 7 inputs reduces power, as less routing is needed between LUTs improving dynamic power consumption. LUTs are implemented using a low leakage smaller transistor which improves device static power consumption [6].

# 2.2 System level techniques

The techniques suggested are applied on the system design to improve power efficiency while some alter the systems operating conditions to achieve optimization. Some of the techniques studied are provided in this section.

## 2.2.1 Voltage scaling

In this technique, supply voltage of the circuit is varied to reduce power consumption. This can lead to reduction in system performance due to an increase in circuit delay. The delay occurs as the gate switching speed reduces with reduction in supply voltage [11] [12]. In [12], the researchers have developed and tested a voltage controller that dynamically controls supply voltage and is responsible for ensuring that voltage is not reduced beyond a certain level which affects system operation and delay requirements.

There are two errors associated with this technique: I/O errors and delay errors [12]. In I/O errors, the supply voltage is at such a low value where a logic level high on an I/O line is lower than the threshold voltage of I/O blocks and is interpreted as logic level low. In delay errors, the voltage reduction brings about a reduction in the switching speed, which in turn reduces critical path delay. If the voltage is lowered further, this delay can become longer than the clock period, and the FPGA no longer meets timing requirements. I/O voltages are not varied to maintain the FPGAs compatibility with other components on the board level. Care should be taken in determining the optimal voltage so that it helps reduce power consumption and at the same time maintains system reliability. In [13] and [14], researchers have designed systems implementing these design techniques; measured and quantified the improvement in power consumption of the design.

## 2.2.2 Clock gating

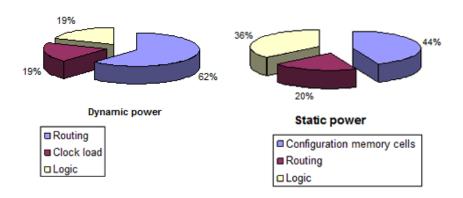

FPGA interconnects are a major portion of the static and dynamic power consumption [11] [8] [15] as shown in Figure 2-1 [8].

Figure 2-1: Spartan -3 core power consumption [8]

In order to reduce the effect of interconnect power dissipation, switching activity on them needs to be reduced. This reduction can be achieved by methods like clock gating and clock frequency scaling [16] [14] [17]. Clock gating is described in this section and clock scaling is discussed in the next.

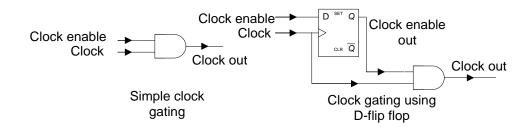

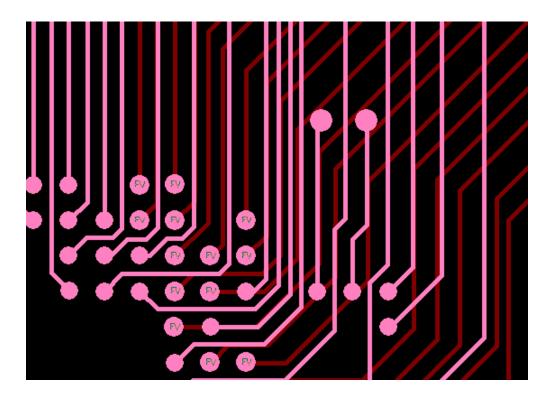

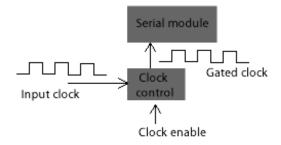

In the clock gating technique, specified synchronous components of the system are disabled by removing the clock to it during either idle or standby mode of operation. Experimental results show that clock gating technique applied to FPGAs has a higher dynamic power reduction than ASICS [16]. The simplest method of clock gating is by using a single AND gate with both the clock and enable signal as inputs. This technique, however, is not without drawbacks. This implementation will invariably lead to setup and hold time violations in the design due to improper alignment of the clock edges. Another technique is to use a flip flop to sync the enable signal with the clock and reduce clock misalignment [18]. Both approaches are shown in Figure 2-2.

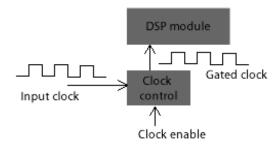

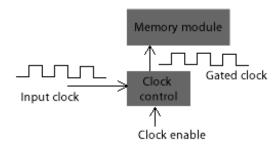

Figure 2-2: Clock gating techniques

#### 2.2.3 Clock scaling

In clock scaling, clock rates are adjusted based on the amount of computation required [17]. A reduction in frequency results in reduced signal activity and lower power consumption. Dynamic clock frequency scaling can be achieved by designing clock managers, and special care needs to be taken in the design. Improper design can affect both functioning and power consumption of the device. Two such design concerns are clock skew and clock hazards or clock glitching. Clock skew is when a single clock reaches different components in a design at

different times. This may be due to interconnect length and capacitive effects during transmission. This skew can lead to alignment difficulties and loss of functionality in applications where alignment is very important, like data communication. Glitching on signal lines can cause the system to go into a metastable state and compromise circuit operation

An approach suggested to reduce skew is by introducing a PLL and using feedback from the logic to dynamically adjust the input frequency. Glitching during dynamic clock frequency adjustment is addressed by making sure that proper alignment is achieved between the current clock and the clock the device is switching to. While reduction in clock frequency does lower power consumption, it also affects the design performance. One way to account for this is by introducing parallelism in the design. While this can lead to increase in the logic area consumed, experimental results have shown that power consumption increases disproportionately to area occupied when operating at a lower frequency [14].

#### 2.2.4 Glitch reduction

A large fraction of FPGA power consumption is caused by glitches [19] [6]. One mitigation technique studied [20] is pipelining, where registers are placed in between combinational circuit blocks to reduce occurrence of spurious signal activity that can affect the operation of the circuit. Another approach to reduce glitching, is adding configurable delay elements [21] to the input of each logic element to align their arrival times. The experimental results showed a significant improvement in power reduction in both approaches. Embedded DSP and RAM blocks are an added advantage in the device structure. Mapping components into these blocks can help improve power efficiency of the design in both FPGAs and ASICs [22].

#### 2.3 FPGA CAD tools

FPGA CAD tools are provided with techniques to further optimize the design. Power consumption in clock networks can be reduced by utilizing clock aware placement algorithms implemented in CAD tools which also optimizes the design's speed and routability. Also, dividing the design into clock domains can lead to a reduction in complexity and area of a clock network [6]. As mentioned above, both Altera and Xilinx provide designers with power estimation and analysis tools. They also provide early power estimators [5] which are spreadsheets and can be used to estimate power consumption before the design is completed. These estimates as based on estimated resource utilization details generated by the design software and signal activity and operating condition requirements of the design.

The power analysis, however, needs more detailed information to make power estimations after the design is completed. The analysis tools take into account capacitance effects, leakage and signal activity at each node to perform the estimations and hence are more accurate than early power estimates. If the simulation results are unknown, vectorless estimations can be used to supplement information needed in the power analysis. Vectorless estimation determines signal activity at a node using the estimated inputs of that node and the logic operation of the node. It is typically fast and does not require any input signal information. However, the fact that it does not take into account interactions between nodes, makes it less accurate.

The CAD software is also responsible for placement and routing of the design on the device. Low power mapping algorithms [6] are implemented during this process to minimize power. These algorithms achieve this by reducing interconnect length between logic blocks by proper mapping into the device, and in general they minimize power by absorbing as many high activity nodes when gates are packed into LUTs and minimizing node duplication.

# **Chapter 3**

# Design methodologies for Low power design

In this section, we take a look at how the power consumption in an FPGA application is characterized. The FPGA operation modes are discussed and then a few proposed design methodologies and approaches for low power consumption are described.

## 3.1 FPGA power components

Power consumption of an FPGA is classified into four basic components. They are Power Up or In-Rush power, Configuration power, Static power, and Dynamic power. These factors need to be considered in designing the power supply for the low power application

### 3.1.1 In-Rush power

During power-up of the device, supply voltages need to be ramped up to their operating values and the device voltages need to be ramped up to a stable state. To achieve this, a substantial amount of logic array current is needed for a specific duration. This high current is called the in-rush current. The amount of time it takes for the supply voltages to reach their steady state values depends on how high this current is, which could be in the order of a few amperes.

#### 3.1.2 Configuration power

In SRAM based FPGA systems where the device configuration data is stored on a non-volatile external memory like an EEPROM or Flash memory, this power is drawn while the system is configured during power up. The device draws this current to load configuration data from memory and program the logic and I/O blocks.

#### 3.1.3 Static power

Static power depends on the amount of static current that the device draws when it is not performing any operation, after the device is powered up and configured, due to inactivity in clock and data paths. It is dissipated either as transistor leakage current or bias current. As dimensions of transistors shrink, the amount of leakage current has increased. This has resulted in static power becoming a larger fraction of total power consumed.

## 3.1.4 Dynamic power

This power is a factor of switching capacitances and routing capacitances and is dissipated when signals charge the capacitive nodes present within logic blocks, routing wires in the interconnect logic, I/O pins and other board level traces driven by the FPGA outputs. This power depends on the operating frequency and signal switching activities in the devices capacitive nodes. Smaller transistor dimensions result in smaller capacitances and hence lower dynamic power dissipation. The dynamic power can be modeled as follows [17];

$$P_d = kV_{DD}^2 C_L f \tag{1}$$

Where f is clock frequency,  $V_{\rm DD}$  is supply voltage and C is the output capacitance of a gate.

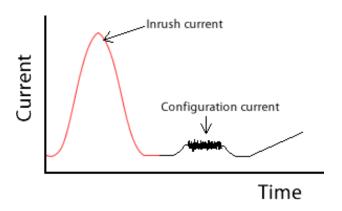

The graph in Figure 3-1 shows the inrush and configuration power consumption components described above for SRAM FPGAs [23]. These two components are important because designers must account for them when designing the power supplies. These components are an issue especially when we have multiple FPGAs drawing power from a single source. If the device undergoes frequent on and off cycles, these components have to be accounted for in calculating battery life.

Figure 3-1: SRAM FPGA current components

## 3.2 FPGA power modes

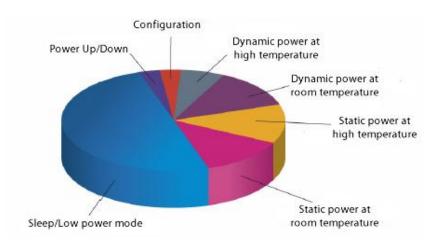

After classifying the power consumption components we need to take a closer look at the device operation for accurate total power consumption estimates. FPGA device operation can be divided into five modes: power-up, configuration, stand-by, active, and sleep. The amount of time the device spends in each of these modes can affect total power consumption.

## 3.2.1 Power-up mode

In this mode the device is powered up and brought to a state where configuration can be done. In SRAM-based FPGA systems this includes the power supplies ramping up to a steady state and the device being reset for configuration. The in-rush current is seen in this mode and as mentioned above, it can be on the order of a few amps. To moderate this surge, devices are powered up in complex sequences which add to the cost and complexity of the system.

### 3.2.2 Configuration mode

Once the device has been powered up and reset, the device is configured. The configuration is done with either data stored on an external memory or with bitstream data downloaded from an external device. This sequence is performed every time after power-up is completed as well as when prototyping boards are programmed in a development environment. The amount of current

consumed is in the range of a few hundred milliamps which is acceptable for devices that get power from the electrical grid, but for portable devices this can be a power critical mode.

### 3.2.3 Standby mode

In this mode, the device is configured but not active. In this mode, the device is either waiting for an input from the user or an interrupt form a coprocessor working in parallel. The power consumed in this mode is static power. The amount of static power consumed depends on the FPGA technology and the operating temperature. SRAM FPGA devices consume more static power than FLASH FPGA devices and this difference is higher at higher temperatures.

#### 3.2.4 Active mode

In this mode the device is performing operations described by the application bitstream. The power consumed in this mode is not just dynamic power due to switching activities but also includes static power. Just as in standby mode, SRAM FPGAs consume more power than FLASH FPGAs and this difference is more at higher temperatures.

#### 3.2.5 Sleep mode

To conserve power in portable battery powered devices, power is turned off when the system is in idle state. This mode is different from standby mode. In standby mode the device is still consuming static power even when it is idle, while in sleep mode the device maintains only minimal power required to bring it back to operational mode. This has a drawback in SRAM FPGAs because the configuration data has to be reloaded every time the device is coming out of sleep mode, thus consuming the configuration power. The graph in Figure 3-2 shows the power profile. We know that the device operates majorly in the sleep mode. So, even though the power consumption is minimal in this mode, the duration spent by the design in it results in the power consumed in this mode becoming a major part of the total power consumed

Figure 3-2 FPGA power profile [22]

## 3.3 Low power design approaches

Different low power techniques provide different percentage improvements, so used alone they might not provide the desired optimization; moreover power reduction achieved is based on the test design and test device. But these approaches used together substantially reduce overall design power consumption. Table 3-1 [24] shows the contribution of each of these approaches in a microprocessor device design's overall power reduction.

| Technique                   | Saving |

|-----------------------------|--------|

| Low power synthesis         | 15%    |

| Clock gating                | 8%     |

| Logic/architectural changes | 45%    |

| Voltage reduction           | 32%    |

**Table 3-1: Power optimization achieved** [24]

Now that we have an idea about the power consumption components and how this total power is distributed over the different modes of the device's operation, we can make design decisions from the very first step that allow us to identify problem areas and mitigate them with appropriate technology choices and design strategies. By using low power techniques to optimize the design and operation, significant reduction in power consumption can be achieved. In [13]

the designers of an audio decoder could achieve 55% power saving compared to other available decoders.

## 3.3.1 Proper device selection

First step in the design process is choosing a right FPGA to run the application on. This is an important step in the design process. By choosing the right device, the system design can be tailored to achieve optimization for that particular device. The architecture and device structure are very important factors in device selection. Static power, as mentioned earlier, is due to transistor leakage and bias currents. By choosing devices that employ transistors with low leakage current, static power consumption can be controlled. Transistors with longer channel lengths and higher thresholds are also used in the device structure to address this issue. Researchers in [10] have shown that by tuning the device a 39% improvement in the leakage yield was achieved and this coupled with architectural optimization, the leakage yield improved by 73%. In [8] the researchers designed a 90 nm FPGA core architecture that consumes 46% less active power and 99% less standby power when compared to a Spartan-3 FPGA core.

In [7], experimental results have shown that reducing gate length and operating voltage has a significant effect on the gate capacitance and dynamic power consumption. The findings are summarized in Table 3-2 below. The lower gate size has achieved a 15% reduction in gate capacitance while a reduction of supply voltage from 1.2V to 1V has reduced consumption by 17%. These two techniques resulted in a 40% overall reduction of the dynamic power

|                    | Virtex-4<br>FPGA 90 nm | Virtex-5<br>FPGA 65nm | % of change | Power<br>Ratio |

|--------------------|------------------------|-----------------------|-------------|----------------|

| V <sub>CCINT</sub> | 1.2                    | 1                     | -16.60%     | 0.69           |

| $C_{TOTAL}$        | 1                      | 0.85                  | -15%        | 0.85           |

| Power              | 1.44                   | 0.85                  | -40%        | 0.59           |

Table 3-2: Results summary [6]

From the technology point of view, there are three main types of FPGA technologies: Antifuse, SRAM and FLASH [1], In comparison, Anti-fuse technologies consumes less static power than SRAM and FLASH FPGAs because of its finer grained architecture while they also occupy less real estate. Dynamic power consumption is lower because of small switching and routing capacitances, smaller interconnect delays and hence they are faster than their counterparts. So one would think that this is the most appropriate technology for commercial use, but it has some drawbacks. Anti-fuse technology is more expensive to manufacture, which neutralizes its speed and power advantages. Moreover, anti-fuse devices are OTP (one-time programmable) devices (once the device is programmed, it cannot be programmed again). If any design changes need to be made later in the systems life cycle the entire FPGA device has to be discarded and replaced. During the testing process it is not economical to cycle test patterns through the system, which also increases the test time in a development or prototyping environment

Even though both FLASH and SRAM FPGAs are reprogrammable devices, FLASH technology is not preferred over SRAM because these devices require five additional manufacturing process steps on top of the standard CMOS technology. FLASH devices also tend to consume more static power due to their vast number of pull up resistors. So depending on the application, proper choice of device can be made. Table 3-3 summarizes the features of these technologies.

| Feature                                   | SRAM                                                             | Anti-fuse                      | E2PROM/<br>FLASH                  |

|-------------------------------------------|------------------------------------------------------------------|--------------------------------|-----------------------------------|

| Technology node                           | State of the art                                                 | One or more generations behind | One or more generations behind    |

| Reprogrammable                            | Yes<br>(in system)                                               | No                             | Yes<br>(in system or offline)     |

| Reprogramming<br>speed<br>(incl. erasing) | Fast                                                             |                                | 3x slower<br>than SRAM            |

| Volatile (must be programmed on power-up) | Yes                                                              | No                             | No<br>(but can be if<br>required) |

| Requires external configuration file      | Yes                                                              | No                             | No                                |

| Good for prototyping                      | Yes<br>(very good)                                               | No                             | Yes<br>(reasonable)               |

| Instant-on                                | No                                                               | Yes                            | Yes                               |

| IP security                               | Acceptable<br>(especially when<br>using bitstream<br>encryption) | Very good                      | Very good                         |

| Size of configuration cell                | Large<br>(six transistors)                                       | Very small                     | Medium-small (two transistors)    |

| Power consumption                         | Medium                                                           | Low                            | Medium                            |

Table 3-3: FPGA technology summary [1]

## 3.3.2 Voltage and temperature control

As mentioned above, transistor leakage current increases with an increase in temperature and lowering the supply voltage has significant effect on leakage current. In Virtex-5 devices [7] it has been shown than a  $\pm 5\%$  variation in core voltages causes an approximate  $\pm 15\%$  change in static power consumption and  $\pm 10\%$  change in dynamic power consumption. FPGAs are designed to meet performance requirements within  $\pm 5\%$  variation in the supply voltages from the nominal. In the case of junction temperature for the same family of devices, a decrease in the temperature form 100°C to 85°C causes an approximate 20% reduction in static power consumption while also increasing device reliability.

## 3.3.3 Supply voltage scaling and Power switching

As mentioned earlier, dynamic power is proportional to the square of the supply voltage. So by scaling it down the dynamic power can be reduced. But a reduction in supply voltage affects the device performance as CMOS gates run slower at a lower voltage. The design can be modified to overcome this performance degradation. Having more logic running in parallel to boost performance at a lower supply voltage does not have a big impact on the dynamic power consumption and the advantage of the scaled down power can be observed. In [12] experimental results have shown that dynamic voltage gating of the device voltage performed by a voltage controller resulted in a power consumption reduction of 4% to 54% on average. Typical reduction values were 20% to 30%.

In power switching, any unused on-chip resources are independently turned off to save power. The device can be divided into blocks based on the power consumption and each block is separately switched to conserve power. The block size can be as small as an individual CLB, controlled by the user directly or by configuring the device using an appropriate bitstream.

## 3.3.4 Reducing clock activity and signal activity

As mentioned earlier, dynamic power consumption depends on the clock frequency and amount of signal activity in the design. Signal gating can be used to reduce the activity on design interconnects, but existence of large clock distribution networks can diminish any gain achieved with signal gating alone [17]. Due to high capacitances of these global interconnects, 25% of the overall dissipation is due to clock signals and this value can go as high as 50% in highly pipelined circuits. This can be controlled by turning the clock off when the circuit is idle and turning it back on when required, which is called clock gating. The designer needs to be careful because this can lead to set-up and hold time violations in the design.

Spurious activity in interconnects, known as glitching, can also cause an increase in dynamic power consumption. In combinational circuits like adders and multipliers with multiple stages, testing has shown that glitching accounts for 80% of the signal activity [19]. Pipelining is shown to reduce the energy per operation by 40% to 90% [20] by reducing glitching. Adding configurable delay elements in the device architecture can also reduce glitching by 87% [21] and reduce the overall FPGA power consumption by 17%. Glitching in logic block interconnects can also be reduced by either gating or pipelining.

Another type of switching activity that can be controlled is the change in states of finite state machines (FSM). By encoding the FSM states, number of toggles of flip flops during state transitions can be reduced. FSMs are usually encoded in standard binary format but by using gray code the number of toggles during state transitions is reduced. In larger designs that extensively use state machines, this technique does have a valuable impact. The table below shows the differences in number of toggles between binary and gray code.

| Binary code | # of Toggles | Gray code | # of Toggles |

|-------------|--------------|-----------|--------------|

| 000         | 3            | 000       | 1            |

| 001         | 1            | 001       | 1            |

| 010         | 2            | 011       | 1            |

| 011         | 1            | 010       | 1            |

| 100         | 3            | 110       | 1            |

| 101         | 1            | 111       | 1            |

| 110         | 2            | 101       | 1            |

| 111         | 1            | 100       | 1            |

Table 3-4: Comparing toggle rates of binary and gray code

Another form of FSM encoding is called one-hot state machine encoding. In this type of encoding, each state uses one flip-flop. For example, a four state FSM will need a 4 bit register to be declared as shown in Table 3-5.

| State[0] | 4'b0001 |

|----------|---------|

| State[1] | 4'b0010 |

| State[2] | 4'b0100 |

| State[3] | 4'b1000 |

Table 3-5: One hot FSM encoding method

The advantage of one hot encoding is that they are typically faster. The speed does not depend on the number of states. A design with many encoded states can slow down. This type of encoding is easy to design and synthesize. The logic is larger when compared to either gray coding or binary, but in larger designs the logic occupied is comparable and this encoding makes it easier to debug.

# 3.3.5 Clock frequency scaling

The clock frequency has a direct effect on power, as mentioned above in the model for dynamic power consumption. A significant reduction in power consumption due to a reduction of only the signal activities is seen in asynchronous circuits. To be more effective in synchronous circuits, the clock also needs to be controlled. FPGAs, when compared to ASICS, have shown to achieve a dynamic power saving of 50% to 80% [16]. When compared to their ASIC counterparts, the total power saving ranged only from 6% to 30% due to the effect of high static power consumption in FPGAs. Though clock gating is one way to reduce the clock signal activity, clock frequency scaling is another method to control dynamic power consumption. In devices with higher capacitances in clock distribution circuits, this technique helps reduce the power lost at output capacitances of these lines. Lowering clock frequency affects the system performance, but in [14] the researchers have demonstrated the tradeoff between logic implemented and clock frequency in respect to power consumption. They have shown experimentally that at low frequencies a 5 fold increase in occupied area resulted in a 1.5 times

increase in dynamic power while the same factor of increase in area at a higher frequency resulted in a 3.8 times increase in dynamic power.

In cases where the design sub-systems are in idle state or the computational needs have reduced, the clock to these modules can be reduces without affecting the application throughput. This method is called dynamic clock scaling and has been successfully implemented in [17]. This method in conjunction with dynamic voltage scaling can be very effective in reducing the dynamic and overall power consumption. The device at lower clock speeds maintains switching speeds due to the lowered supply voltage levels [17].

### 3.3.6 CAD tools

Both Altera and Xilinx provide users with power estimation tools which can be used either during the design process or after the final design is done to get an idea about the device power consumption [5]. During the design process, early power estimators, provided as a spreadsheet, can be used to estimate power consumption of that part of the design. After the design process is done, power analyzer tools utilize detailed switching activities provided by the user. The device routing and placement information along with detailed device temperature and cooling information is also used to estimate the power consumed. Although the most accurate way to measure power consumption of the device is by hardware measurements, power estimators are a convenient way to determine the power budget. This along with power efficient routing algorithms implemented during the place and route step of the design process, help enhance the devices architectural features.

# Chapter 4

# **Hardware and Software**

This section describes the need for proper device selection for a design and the steps taken in making the choice for this thesis are discussed. The device features are presented along with some details about the Quartus II design software and PowerPlay power optimization tool.

#### 4.1 Device Selection

A wide variety of FPGA devices are available in the market today, each with one or more of the features that were discussed in Chapter 1. Using a desired design entry method with appropriate power conservation techniques is only half of the job. It is equally important to choose the right device to run the application on, and it should provide the designer with the required resources while being flexible enough to accommodate any future design and resource requirement changes.

For this thesis design, Altera's FPGA devices were chosen for implementation due to the availability and the author's familiarity with the design software. The Altera FPGA families chosen to perform the analysis on are given below:

- Stratix series: High bandwidth, high density FPGAs

- Arria series: Midrange FPGAs with transceivers, optimized for mainstream protocols

- Cyclone series: Built from ground up for low cost, low power consumption

Preliminary power analysis measurements were made using the PowerPlay power analyzer. Steps taken in performing the device power estimations and their results are provided and discussed in a later chapter. The FPGA EP2C35F672 which belongs to the Cyclone II device family of Altera was chosen based on these estimation results.

# 4.2 Cyclone II FPGA Architecture

For this thesis, HDL code implementation was done on the Cyclone II device family. The device architecture is described below [4].

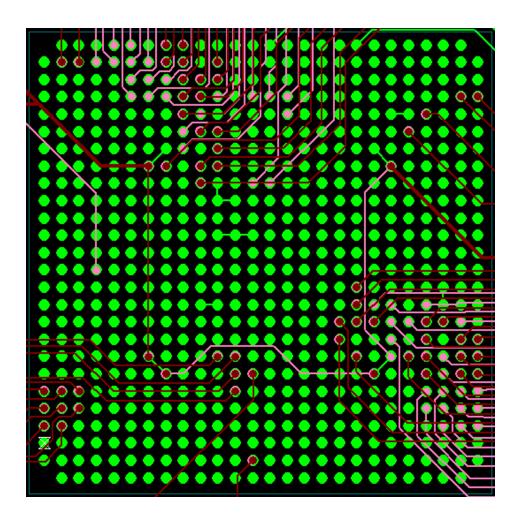

Figure 4-1: Cyclone II FPGA architecture [3]

In Figure 4-1, the area denoted as Logic Array is the array of CLBs (Altera LABs), where each LAB consists of 16 logic elements. The Interconnect structures are not shown here, but the special function blocks are shown. The Cyclone II FPGA has embedded in it multiplier blocks, RAM blocks (shown as M4K blocks), and Phase Locked Loops denoted as PLL in the figure. As labeled, the IOEs are the input/output elements or input/output blocks.

#### 4.2.1 Interconnect structures

The architecture of cyclone II is a two-dimensional row and column based architecture. The row and column interconnects provide the required connectivity between different CLBs, multipliers and RAM blocks. These interconnects are of varying speeds. Along with 4 PLLs, the

cyclone II device is also provided with a global clock network. The clock network consists of up to 16 global clocks running through the entire device, and it is used to provide clock to all device resources like multipliers, memory blocks along with the CLBs and IOEs.

The device architecture has special performance enhanced routing lines called multi-track interconnects. They consist of routing lines of different speeds, used to achieve connectivity within a design block or between design blocks. Depending on how critical a certain interconnect path is, the compiler decides if it needs to be on the faster lines or not, in order to boost the design performance.

### 4.2.2 Embedded multipliers

Each of the embedded multipliers can be used to implement either two independent 9x9 bit multipliers or one 18x18 bit multiplier. These multipliers have been optimized for multiplication intensive DSP functions like Finite Impulse Response (FIR) filters, Fast Fourier Transform (FFT) etc. The number of embedded multiplier columns depends on the device; between 1 and 3; and these columns are the same length as the LAB column. For example, in the EP2C35 device, we have 1 embedded multiplier column with 35 multipliers which can be used to implement either 70 9x9 multipliers or 35 18x18 multipliers. These multipliers operate at a maximum frequency of 250 MHz at the highest speed grade.

### 4.2.3 Embedded memory blocks

Each of the embedded memory blocks has a size of 4068 RAM bits. These blocks can be used to implement different types of memory such as true Dual port memory (dual port RAM has ability to simultaneously read and write different memory cells at different addresses), simple dual port, single port RAM, ROM and first-in-first-out (FIFO) buffers with or without parity. The M4K blocks also support the following features:

- Byte enable: The byte enable allows input data to be masked so the device can write to specific bytes.

- Parity bits: One parity bit for each byte can be used to implement parity checking for error detection

- Shift register: Using RAM based first in first out (FIFO) buffers instead of LE registers saves general logic resources, increases overall speed and reduces power consumption.

- Various clock modes: The input and output registers can be clocked in different modes

either independent of each other, one clock controlling the two ports or one clock and

clock enable to provide register control.

- Address clock enable: This allows for the address busses to hold the previous address

value for as long as the enable signal is given.

- Global clock networks and Phase locked loops

The global clock network has a clock control block that can be used to select between the PLL clock outputs, dedicated clock inputs and dual purpose clock inputs. Every device has a different number of the above resources available in them to select from. If the dedicated clock pins are not used as clock inputs, they can be used as general purpose I/O pins. As mentioned before, the global clock network provides clocks for all resources within the device, like the CLBs, IOEs, memory blocks, and embedded multipliers.

The global clock lines can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed from the external pin. Internal logic can also drive the global clock network for internally generated global clocks and asynchronous clears, clock enables, or other control signals. Cyclone II devices have up to 4 PLLs that can be used for clock

multiplication and division, phase shifting. Some of the other features supported by the PLLS are programmable phase shifting, clock outputs for differential I/O support etc.

# 4.2.4 Cyclone II Logic Element structure

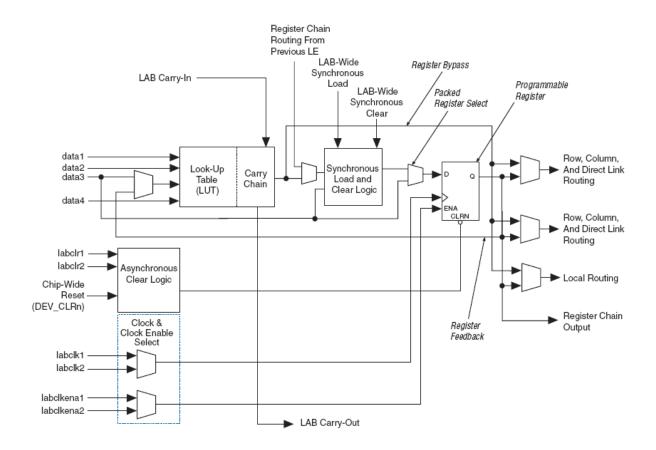

Figure shows the structure of the logic element of the FPGA device [4].

Figure 4-2: Cyclone II FPGA Logic Element [3]

Each LE in the cyclone II device consists of:

- A four-input look-up table (LUT), which is a function generator that can implement any function of four variables

- A programmable register which can be configured for D, T, JK or SR operation

- Carry chain connections for implementing fast carry logic. The Quartus II compiler creates carry chain logic during the design processing.

- A register chain connection. This feature allows the registers in a CLB to be cascaded together for shift register implementation.

- The ability to drive all types of interconnects: local, row, column, register chain, and direct link interconnect. Each LE has 3 of outputs that allow for driving these routing resources. The LUT and the register outputs can drive these interconnects independently

- Support for register packing. The high routability feature of the FPGA architecture and ability of the synthesis tool and place and route tool to utilize this feature allows the efficient use of the LEs. This allows the LUT in a CLB to be utilized independently of the registers i.e. the LUT can be used to perform one operation while the register available in that CLB can be used, either individually or in conjunction with other registers, to perform a completely different task. This reduces the size of a design and usually fits a design into a smaller device

- Support for register feedback. This is when the output of the programmable register is fed back as an input to the LUT.

# 4.3 Quartus II and Power Play power analyzer

Quartus II design software is one of the design and synthesis tools available to designers [5] [25]. These tools are designed to take advantage of device architecture and special features to map the design into logic and help achieve the designer's optimization requirements. The designer can choose to optimize for area, timing or power of the design. Area driven synthesis will reduce the amount of logic used. This also helps reduce dynamic power consumption due to optimized and reduced logic levels. Timing driven synthesis uses timing constraint information provided by the user to determine the design's routing. This is done at the cost of consuming extra logic on the FPGA device. In power driven synthesis the main objective is to reduce the

power consumption. Reduction in area and power driven synthesis go hand in hand. For example, using embedded features of the FPGA like multipliers, embedded RAM and special interconnect structures are very effective in reducing power consumption [22].

The software allows the designer to select the factor that needs to be optimized at both the analysis and synthesis step and fitter step. In the analysis and synthesis step, the design is compiled to check for syntax, logical completeness and inconsistencies. The design is synthesized and resource utilization decisions such as using embedded multipliers or memory blocks are taken. The last step of the compilation process is generating the files necessary to program the device and this process is called "fitting". Quartus II fitter places and routes the design. Using the database file created during analysis and synthesis step of the design compilation, the fitter assigns resources on the selected device to match the logic and project requirements of area, timing or power. The logic functions are assigned to optimal logic cell locations and appropriate interconnection paths are chosen. The final result of the fitting process is a bitstream file that is used to program the FPGA.

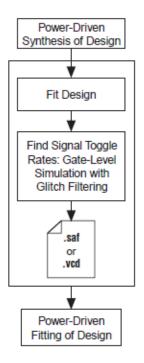

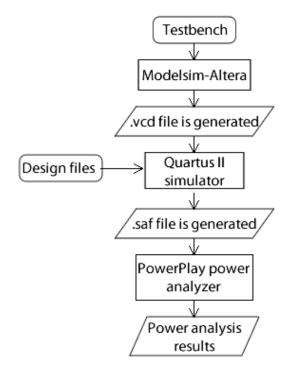

Signal activity files (.saf) or value change dump files (.vcd) help the fitter fully optimize design routing for power conservation. These files contain the signal activities of all signals in the design and are determined after a full design simulation performed on the post-fit netlist. If the input vectors used to perform simulation represent the typical behavior expected at the system inputs, the .saf file or .vcd file will reflect the actual behavior at every design node. If the user does not provide either of these files, Quartus II software uses vectorless estimation [6] [5] [25] to estimate the signal activities. This involves estimating the switching activity at each node based on the activity of its inputs and the logical function performed at that node [6]. This