# Corrective schemes for internal and external abnormalities in cascaded multilevel inverters

by

#### Jacob Lamb

B.S., Northern Arizona University, 2013 B.S.E., Northern Arizona University, 2013

#### AN ABSTRACT OF A DISSERTATION

submitted in partial fulfillment of the requirements for the degree

### DOCTOR OF PHILOSOPHY

Department of Electrical and Computer Engineering College of Engineering

KANSAS STATE UNIVERSITY

Manhattan, Kansas

### Abstract

Corrective schemes for facilitating continued operation of dc-ac converters during internal and external abnormalities are presented in this dissertation. While some of the developed techniques are suited for any dc-ac converter topology, most of the presented methodologies are designed specifically for cascaded H-bridge (CHB) multilevel converters. While CHB provide increased scalability and efficiency compared to traditional topologies, these converters are more likely to experience internal faults due to the additional components required. Realizing the full potential of CHB converters requires fault tolerant techniques, such as those demonstrated in this dissertation. Adaptive sinusoidal pulse width modulation (ASPWM) is introduced in this dissertation as a method which enables CHB to directly utilize time-variant dc sources, increasing CHB flexibility when compared to traditional pulse width modulation (PWM) methods which require dc sources with equal magnitudes or with magnitudes existing in specific ratios. Two alternative algorithms are presented to enable ASPWM implementation, providing a trade off between system performance and required sensor circuitry. This dissertation also introduces a load independent analytical approach for identifying discordant operating points, i.e. operating points where some cells in an asymmetric CHB leg regenerate power while the overall leg delivers power, or vice-versa. Identification of these points is essential due to the deleterious effects which can result from extended discordant operation, for instance overcharging of batteries leading to lifespan degradation or even catastrophic failures such as fires or explosions. Additionally, a method for rapidly identifying, isolating, and verifying internal IGBT open-circuit and gate-driver faults is presented in this dissertation to address the increased probability of switch failures occurring within CHB. The proposed approach enables converter operation to continue in the event of gate-driver or open-circuit faults, but avoids unnecessary converter reconfiguration due to gate-misfiring faults. For a CHB leg with M cells, the proposed technique identifies and isolates open-circuit switch faults in less than 2M measurement (sampling) cycles, and verification is completed in less than one full fundamental cycle. Furthermore, this dissertation introduces a real-time implementable atypical PWM technique which enables increased dc bus utilization under a wide range of non-ideal operating conditions. While this approach is suitable for a wide range of converters operating under external abnormalities, for instance maximizing dc bus utilization for converters providing auxiliary services such as negative-sequence compensation, this approach also facilitates operation of CHB with faulty cells. The proposed method can be used with any control technique and any carrier-based PWM method, enabling its implementation in both symmetric and asymmetric CHB. In addition to these fault tolerant techniques, a novel approach for analyzing the active- and reactivepower deliverable by grid-interactive converters is proposed. This method facilitates performance comparisons for various converter configurations, simplifying the process for selecting filter components, dc bus voltages, and other system parameters. This analytical approach also enables converter performance to be analyzed during internal and external fault events, allowing assessment of converter robustness. The efficacy of the developed techniques are supported by MATLAB/Simulink simulations as well as experimental data obtained using a laboratory-scale cascaded H-bridge multilevel converter.

# Corrective schemes for internal and external abnormalities in cascaded multilevel inverters

by

### Jacob Lamb

B.S., Northern Arizona University, 2013 B.S.E., Northern Arizona University, 2013

### A DISSERTATION

submitted in partial fulfillment of the requirements for the degree

### DOCTOR OF PHILOSOPHY

Department of Electrical and Computer Engineering College of Engineering

### KANSAS STATE UNIVERSITY

Manhattan, Kansas

2017

Approved by:

Major Professor Dr. Behrooz Mirafzal

# Copyright

© Jacob Lamb 2017.

### Abstract

Corrective schemes for facilitating continued operation of dc-ac converters during internal and external abnormalities are presented in this dissertation. While some of the developed techniques are suited for any dc-ac converter topology, most of the presented methodologies are designed specifically for cascaded H-bridge (CHB) multilevel converters. While CHB provide increased scalability and efficiency compared to traditional topologies, these converters are more likely to experience internal faults due to the additional components required. Realizing the full potential of CHB converters requires fault tolerant techniques, such as those demonstrated in this dissertation. Adaptive sinusoidal pulse width modulation (ASPWM) is introduced in this dissertation as a method which enables CHB to directly utilize time-variant dc sources, increasing CHB flexibility when compared to traditional pulse width modulation (PWM) methods which require dc sources with equal magnitudes or with magnitudes existing in specific ratios. Two alternative algorithms are presented to enable ASPWM implementation, providing a trade off between system performance and required sensor circuitry. This dissertation also introduces a load independent analytical approach for identifying discordant operating points, i.e. operating points where some cells in an asymmetric CHB leg regenerate power while the overall leg delivers power, or vice-versa. Identification of these points is essential due to the deleterious effects which can result from extended discordant operation, for instance overcharging of batteries leading to lifespan degradation or even catastrophic failures such as fires or explosions. Additionally, a method for rapidly identifying, isolating, and verifying internal IGBT open-circuit and gate-driver faults is presented in this dissertation to address the increased probability of switch failures occurring within CHB. The proposed approach enables converter operation to continue in the event of gate-driver or open-circuit faults, but avoids unnecessary converter reconfiguration due to gate-misfiring faults. For a CHB leg with M cells, the proposed technique identifies and isolates open-circuit switch faults in less than 2M measurement (sampling) cycles, and verification is completed in less than one full fundamental cycle. Furthermore, this dissertation introduces a real-time implementable atypical PWM technique which enables increased dc bus utilization under a wide range of non-ideal operating conditions. While this approach is suitable for a wide range of converters operating under external abnormalities, for instance maximizing dc bus utilization for converters providing auxiliary services such as negative-sequence compensation, this approach also facilitates operation of CHB with faulty cells. The proposed method can be used with any control technique and any carrier-based PWM method, enabling its implementation in both symmetric and asymmetric CHB. In addition to these fault tolerant techniques, a novel approach for analyzing the active- and reactivepower deliverable by grid-interactive converters is proposed. This method facilitates performance comparisons for various converter configurations, simplifying the process for selecting filter components, dc bus voltages, and other system parameters. This analytical approach also enables converter performance to be analyzed during internal and external fault events, allowing assessment of converter robustness. The efficacy of the developed techniques are supported by MATLAB/Simulink simulations as well as experimental data obtained using a laboratory-scale cascaded H-bridge multilevel converter.

# Table of Contents

| Li | st of        | Figure  | es                                           | xii   |

|----|--------------|---------|----------------------------------------------|-------|

| Li | ${ m st}$ of | Tables  | s                                            | xxi   |

| Ao | cknov        | wledge  | ements                                       | xxiii |

| De | edica        | tion    | 3                                            | xxiv  |

| 1  | Intr         | oducti  | ion                                          | 1     |

|    | 1.1          | Motiva  | ation and Objectives                         | 1     |

|    |              | 1.1.1   | Switch Faults                                | 4     |

|    |              | 1.1.2   | Utilization of Time-Variant DC Source Inputs | 5     |

|    |              | 1.1.3   | Unbalanced Grid-Interactive Operation        | 6     |

|    | 1.2          | Litera  | ture Review                                  | 7     |

|    |              | 1.2.1   | Switch Faults                                | 7     |

|    |              | 1.2.2   | Maintaining Balanced Input Sources           | 8     |

|    |              | 1.2.3   | Effective Utilization of DC Sources          | 10    |

|    | 1.3          | Contri  | ibution of Dissertation                      | 12    |

|    | 1.4          | Organ   | ization of Dissertation                      | 13    |

| 2  | The          | e Casca | aded H-Bridge Multilevel Converter           | 16    |

|          | 2.1                                           | .1 System Topology                                                                   |       | <br> | <br>• | 16                                                    |

|----------|-----------------------------------------------|--------------------------------------------------------------------------------------|-------|------|-------|-------------------------------------------------------|

|          | 2.2                                           | 2 PWM Methods                                                                        |       | <br> |       | 19                                                    |

|          |                                               | 2.2.1 Level-Shifted Pulse Width Modulation                                           |       | <br> |       | 19                                                    |

|          |                                               | 2.2.2 Reference Modifications                                                        |       | <br> |       | 24                                                    |

|          |                                               | 2.2.3 Hybrid Pulse Width Modulation                                                  |       | <br> |       | 26                                                    |

|          | 2.3                                           | 3 Continued Post-Fault Operation                                                     |       | <br> |       | 27                                                    |

|          | 2.4                                           | 4 Conclusion                                                                         |       | <br> |       | 32                                                    |

| 3        | PQ                                            | Q Plane Operating Analysis                                                           |       |      |       | 33                                                    |

|          | 3.1                                           | .1 Symmetric CHB Converter Operating Region                                          |       | <br> |       | 34                                                    |

|          | 3.2                                           | .2 Asymmetric CHB Converter Operational Region                                       |       | <br> |       | 42                                                    |

|          | 3.3                                           | 3 Numerical Test Cases                                                               |       | <br> |       | 47                                                    |

|          | 3.4                                           | 4 Conclusion                                                                         |       | <br> |       | 52                                                    |

|          |                                               |                                                                                      |       |      |       |                                                       |

| 4        | Aty                                           | atypical PWM for Maximizing DC Bus Utilization                                       |       |      |       | 53                                                    |

| 4        | <b>Aty</b> 4.1                                | •                                                                                    |       | <br> |       | <b>53</b>                                             |

| 4        | ·                                             | 1 PQ Plane Output Region Under Unbalanced Condition                                  | ons . |      |       |                                                       |

| 4        | 4.1                                           | 1 PQ Plane Output Region Under Unbalanced Condition                                  | ons . | <br> |       | 54                                                    |

| 4        | 4.1                                           | PQ Plane Output Region Under Unbalanced Condition Common-Mode Component Generation   | ons . | <br> |       | 54<br>56                                              |

| 4        | 4.1                                           | PQ Plane Output Region Under Unbalanced Condition.  Common-Mode Component Generation | ons . | <br> |       | 54<br>56<br>57                                        |

| 4        | 4.1 4.2                                       | PQ Plane Output Region Under Unbalanced Condition Common-Mode Component Generation   | ons . | <br> | <br>  | 54<br>56<br>57<br>59                                  |

| <b>4</b> | 4.1<br>4.2<br>4.3<br>4.4                      | PQ Plane Output Region Under Unbalanced Condition Common-Mode Component Generation   | ons . | <br> | <br>  | 54<br>56<br>57<br>59<br>62                            |

|          | 4.1<br>4.2<br>4.3<br>4.4                      | PQ Plane Output Region Under Unbalanced Condition Common-Mode Component Generation   | ons . | <br> | <br>  | 544<br>566<br>577<br>599<br>622<br>677                |

|          | 4.1<br>4.2<br>4.3<br>4.4<br><b>Dir</b>        | PQ Plane Output Region Under Unbalanced Condition Common-Mode Component Generation   | ons . | <br> | <br>  | 544<br>566<br>577<br>599<br>622<br>677                |

|          | 4.1<br>4.2<br>4.3<br>4.4<br><b>Dir</b><br>5.1 | PQ Plane Output Region Under Unbalanced Condition Common-Mode Component Generation   | ons . | <br> |       | 544<br>566<br>577<br>599<br>622<br>677<br><b>68</b> 8 |

|   | 5.5 | Exper   | imental Verification                               | . 85  |

|---|-----|---------|----------------------------------------------------|-------|

|   | 5.6 | Steady  | y-State Behavior Modifications                     | . 88  |

|   |     | 5.6.1   | Preventing Discordant Operation                    | . 89  |

|   |     | 5.6.2   | Minimizing Switching Losses in a High-Voltage Cell | . 90  |

|   | 5.7 | Concl   | usion                                              | . 92  |

| 6 | Оре | en-Ciro | cuit Switch Fault Detection and Isolation          | 93    |

|   | 6.1 | Chapt   | er Notation                                        | . 93  |

|   |     | 6.1.1   | Open-Circuit Switch Fault Effects                  | . 95  |

|   | 6.2 | Open-   | Circuit Fault Detection                            | . 96  |

|   |     | 6.2.1   | Identifying Possible Open-Circuit Fault Locations  | . 97  |

|   |     | 6.2.2   | Faulty Switch Isolation                            | . 99  |

|   |     | 6.2.3   | Faulty Switch Verification                         | . 101 |

|   | 6.3 | Simula  | ation Results                                      | . 104 |

|   |     | 6.3.1   | Open-Circuit Fault                                 | . 105 |

|   |     | 6.3.2   | Gate Misfiring Fault                               | . 106 |

|   | 6.4 | Exper   | imental Verification                               | . 107 |

|   | 6.5 | Epsilo  | on Selection                                       | . 114 |

|   |     | 6.5.1   | False Alarms                                       | . 115 |

|   |     | 6.5.2   | Missed Detection                                   | . 115 |

|   |     | 6.5.3   | Minimizing $ SW_F $                                | . 117 |

|   |     | 6.5.4   | Selecting $\epsilon$                               | . 117 |

|   | 6.6 | Concl   | usion                                              | . 118 |

| 7 | Con | clusio  | ns and Suggestions for Future Work                 | 119   |

|   | 7.1 | Summ    | nary and Conclusions                               | . 119 |

|   | 7 2 | Sugge   | stions for Future Work                             | 122   |

| Bi           | bliog | raphy                    | 124 |

|--------------|-------|--------------------------|-----|

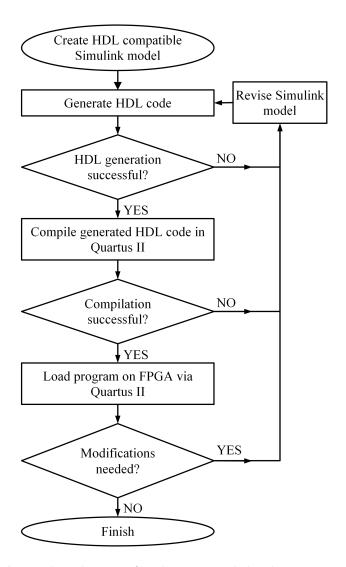

| $\mathbf{A}$ | FPC   | GA for Rapid Prototyping | 140 |

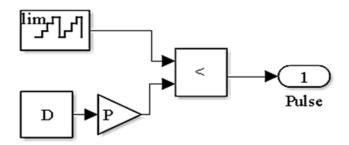

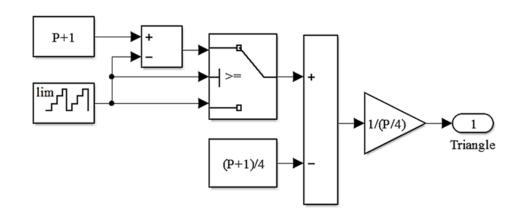

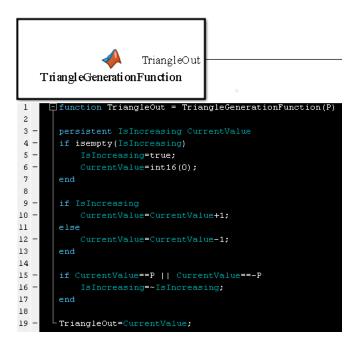

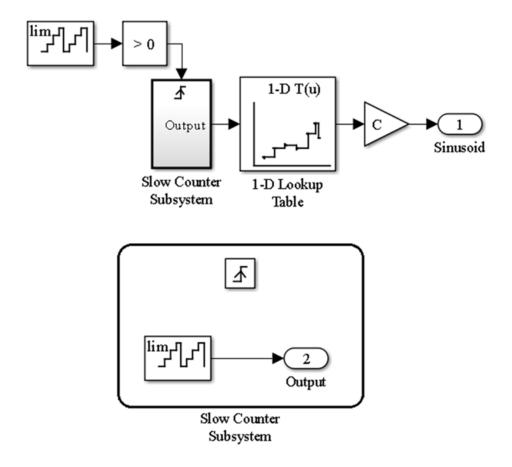

|              | A.1   | Waveform Generation      | 143 |

| В            | Dev   | reloped Hardware         | 148 |

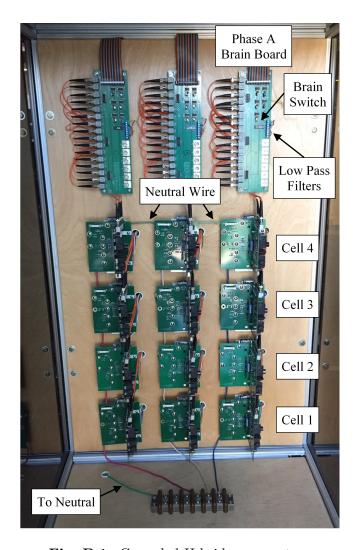

|              | B.1   | Converter Layout         | 148 |

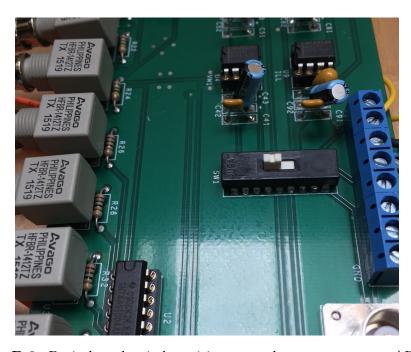

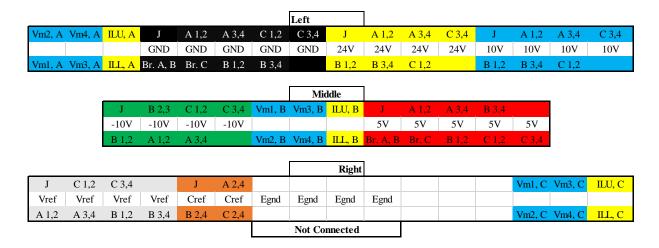

|              | B.2   | FPGA Interfacing         | 153 |

# List of Figures

| 1.1 | Conventional three-phase, two-level voltage source inverter topology      | 2  |

|-----|---------------------------------------------------------------------------|----|

| 1.2 | Three-phase cascaded H-bridge multilevel topology with $M$ cells per leg. | į  |

| 2.1 | A grid-interactive cascaded H-bridge multilevel converter                 | 17 |

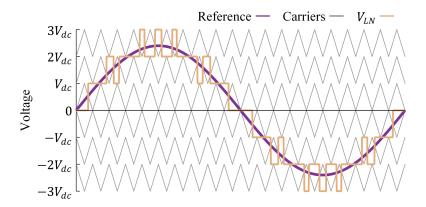

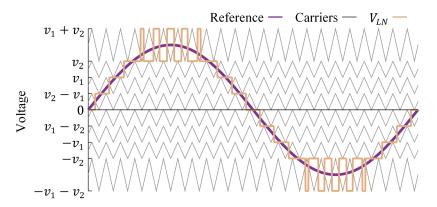

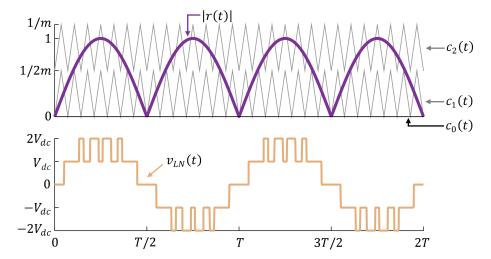

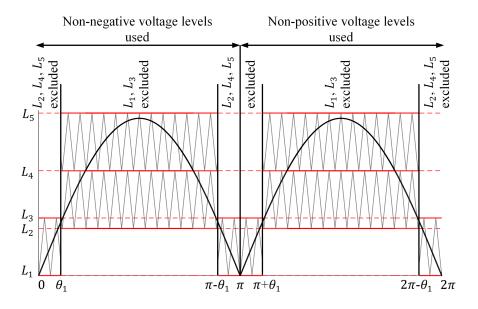

| 2.2 | Reference, carriers, and the unfiltered line-to-neutral output when using |    |

|     | level-shifted PWM to modulate a symmetric three-cell CHB. Carriers        |    |

|     | are in the phase opposition disposition configuration                     | 20 |

| 2.3 | Reference, carriers, and the unfilitered line-to-neutral output when us-  |    |

|     | ing level-shifted PWM to modulate an asymmetric two-cell asymmetric       |    |

|     | CHB with $v_2 > v_1 > v_2 - v_1$ . Carriers are in the phase disposition  |    |

|     | configuration                                                             | 21 |

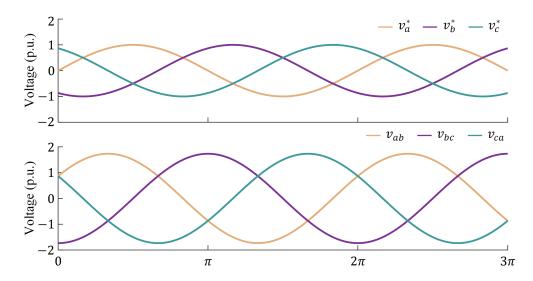

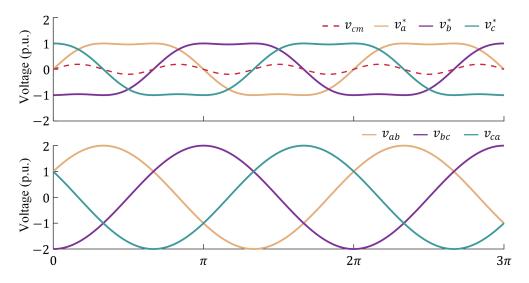

| 2.4 | Maximum references (top) and resulting ideal line-to-line voltages (bot-  |    |

|     | tom) when using purely sinusoidal references in a balanced three-phase    |    |

|     | system. Waveforms are normalized by the sum of dc bus voltages within     |    |

|     | a leg                                                                     | 21 |

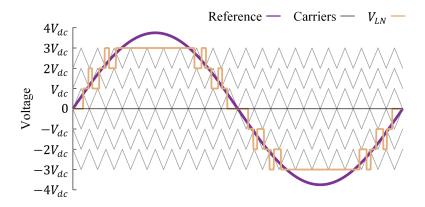

| 2.5 | Reference, carriers, and the unfilitered line-to-neutral output when us-  |    |

|     | ing level-shifted PWM to modulate a symmetric three-cell CHB. Since       |    |

|     | the reference exceeds the maximum line-to-neutral output voltage, the     |    |

|     | converter is overmodulated                                                | 23 |

| 2.6  | Overmodulated references and ideal line-to-neutral voltages (top) as well        |    |

|------|----------------------------------------------------------------------------------|----|

|      | as the resulting ideal line-to-line voltages (bottom) when using purely          |    |

|      | sinusoidal references in a balanced three-phase system. Waveforms are            |    |

|      | normalized by the sum of dc bus voltages within a leg                            | 23 |

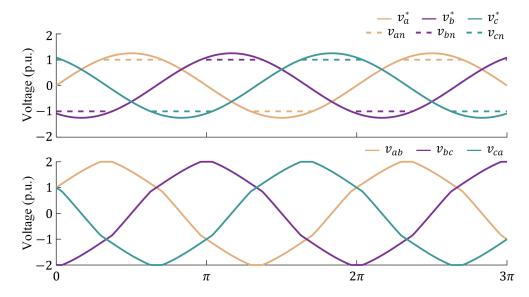

| 2.7  | References and common-mode component (top) and resulting ideal line-             |    |

|      | to-line voltages (bottom) when using third-harmonic injection in a bal-          |    |

|      | anced three-phase system. Waveforms are normalized by the sum of dc              |    |

|      | bus voltages within a leg                                                        | 24 |

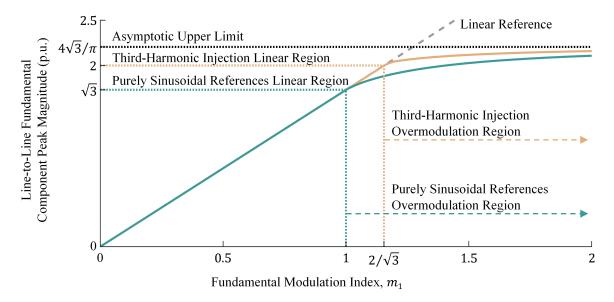

| 2.8  | Compared to purely sinusoidal references, the linear PWM range of a              |    |

|      | CHB is increased by utilizing third-harmonic injection. Regardless of            |    |

|      | the method utilized, operation in the overmodulation causes difficult to         |    |

|      | filter low order harmonics. Voltage magnitudes are normalized by the             |    |

|      | sum of dc bus voltages within a leg                                              | 25 |

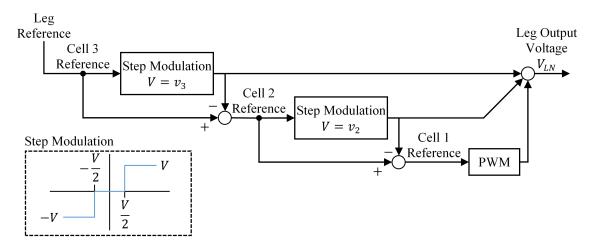

| 2.9  | Block diagram for implementing hybrid PWM in a three-cell CHB leg.               | 26 |

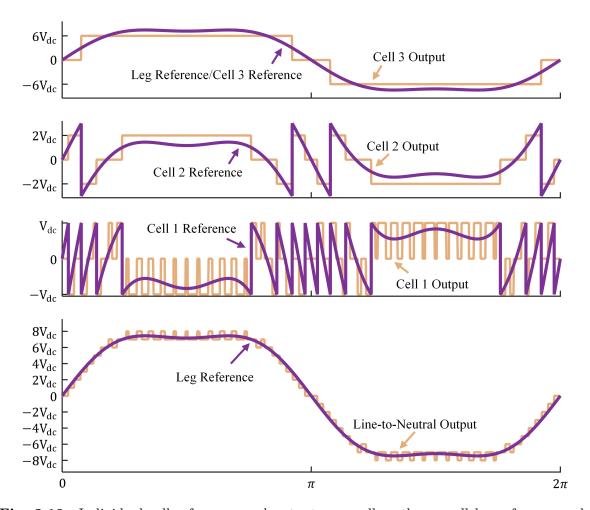

| 2.10 | Individual cell references and outputs, as well as the overall leg reference     |    |

|      | and unfilitered line-to-neutral output, when hybrid PWM is used to               |    |

|      | modulate a three-cell CHB leg with $[v_1:v_2:v_3]=[1:2:6]$ . Assuming            |    |

|      | this is one leg of a three-phase system, third-harmonic injection can be         |    |

|      | used to increase dc bus utilization since this is a carrier-based technique.     | 27 |

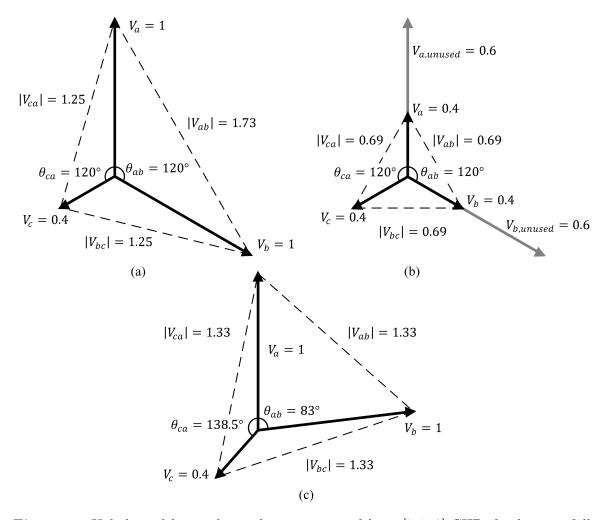

| 2.11 | Unbalanced line-to-line voltages generated by a $[5,5,2]$ CHB if references      |    |

|      | fully utilize the available leg voltages and maintain $120^{\circ}$ phase shifts |    |

|      | (a), balanced line-to-line voltages generated by utilizing only some of          |    |

|      | the cells in healthy legs (b), and balanced line-to-line voltages generated      |    |

|      | by applying FPSC to adjust phase shifts between references (c). All              |    |

|      | voltage magnitudes are normalized by $5V_{dc}$ , the sum of dc bus voltages      |    |

|      | in a healthy leg.                                                                | 29 |

|      |                                                                                  |    |

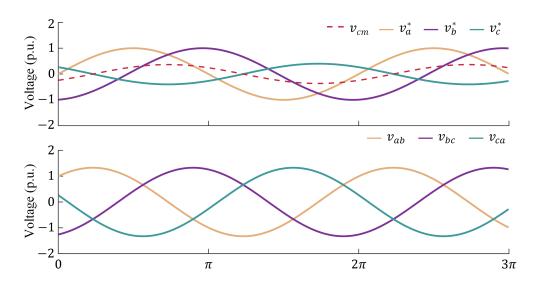

| 2.12 | FPSC generated references and their common-mode component (top)                   |    |

|------|-----------------------------------------------------------------------------------|----|

|      | and ideal resultant line-to-line voltages (bottom) for a $[5,5,2]$ CHB. All       |    |

|      | waveforms are normalized by $5V_{dc}$                                             | 30 |

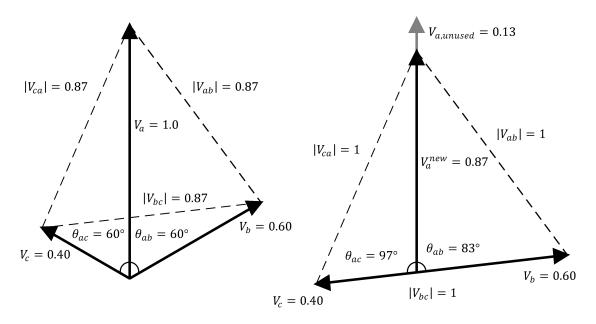

| 2.13 | Solutions to (2.1), (2.2), and (2.3) enable balanced voltages to be pro-          |    |

|      | duced for a $[5,3,2]$ CHB (left), but larger voltage magnitudes can be            |    |

|      | obtained using extended FPSC, i.e. $(2.4)$ and $(2.5)$ (right). All voltage       |    |

|      | magnitudes are normalized by $5V_{dc}$                                            | 31 |

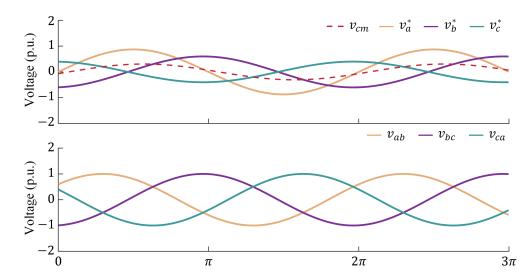

| 2.14 | FPSC references and common-mode component (top) and resulting ideal               |    |

|      | line-to-line voltages for a $[5,3,2]$ CHB. All waveforms are normalized by        |    |

|      | $5V_{dc}$                                                                         | 32 |

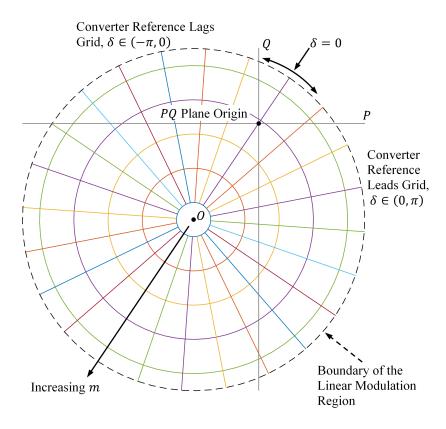

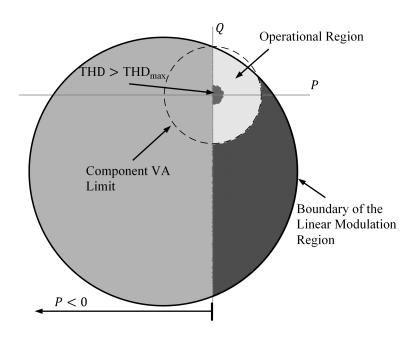

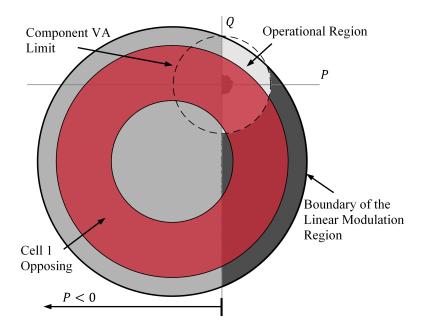

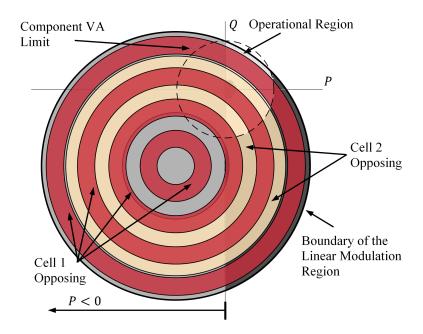

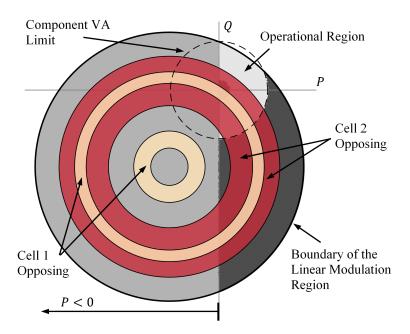

| 3.1  | The boundary of the linear modulation region defines the output region            |    |

|      | for a grid-interactive CHB. Converter output points for fixed $m$ and             |    |

|      | variable $\delta$ trace circles in the PQ plane, while output points trace radial |    |

|      | lines for fixed $\delta$ and variable $m$                                         | 36 |

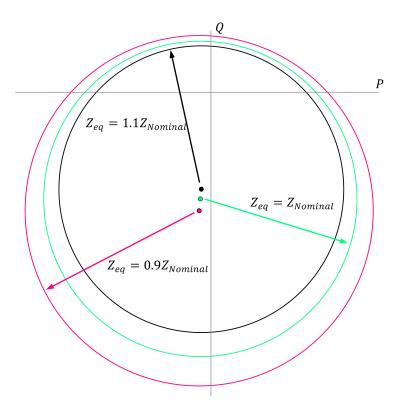

| 3.2  | Alterations of the converter's output region due to ten percent deviations        |    |

|      | of a nominal impedance used coupling the converter and grid                       | 37 |

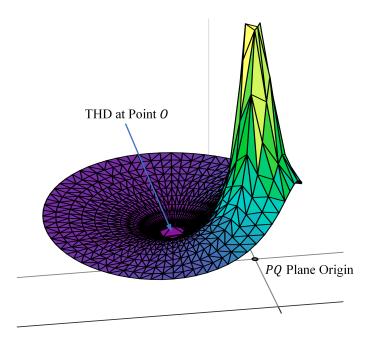

| 3.3  | Line current THD for the PQ plane output region of a grid-interactive             |    |

|      | CHB. Distortion increases dramatically near the origin of the PQ plane,           |    |

|      | and values of THD are asymmetric about the PQ plane's origin. $$                  | 39 |

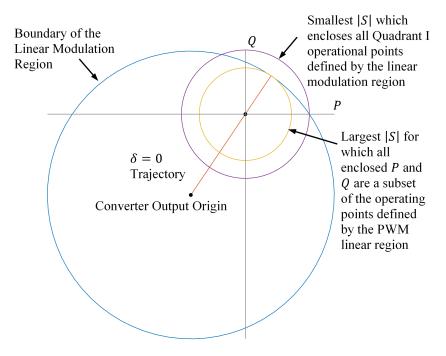

| 3.4  | Two potentially desirable $ S_{max} $ values, used for component selection,       |    |

|      | based on the disk defined by the linear modulation region                         | 41 |

| 3.5  | PQ plane operational region for a grid-tied symmetric CHB converter               |    |

|      | operating in the linear PWM region                                                | 41 |

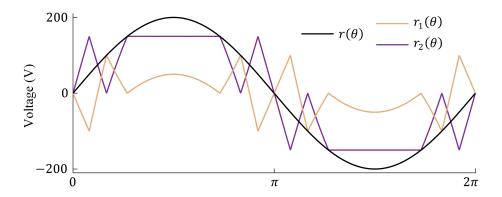

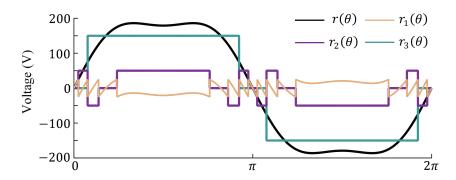

| 3.6  | LSPWM and cell references for an $M=2$ cell CHB with $v_1=100\mathrm{V},$                                                                   |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | $v_2 = 150 \mathrm{V}$ , and $r(\theta) = 200 \sin(\theta)$ . Cell references $r_1(\theta)$ and $r_2(\theta)$ are                           |    |

|      | not typically available, but are constructed for analysis                                                                                   | 44 |

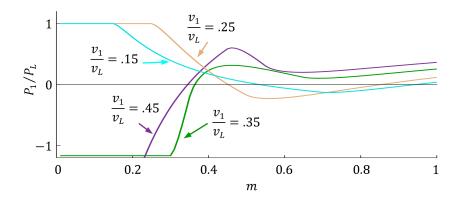

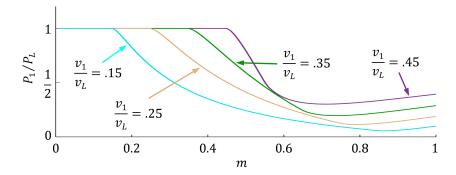

| 3.7  | Power ratio for the low voltage cell, cell 1, of a two-cell CHB for varying                                                                 |    |

|      | ratios of $v_1/(v_1+v_2)=v_1/v_L$ , assuming all available voltage outputs                                                                  |    |

|      | are used for $PWM$ generation. A given value of $m$ results in a cell 1                                                                     |    |

|      | discordant output point if $P_1/P_L < 0.$                                                                                                   | 44 |

| 3.8  | PQ plane operational region for a two-cell grid-tied asymmetric CHB                                                                         |    |

|      | converter operating in the linear region, with all available output volt-                                                                   |    |

|      | ages utilized. Voltage ratios are in the trinary configuration, $v_1:v_2=1:3.$                                                              | 45 |

| 3.9  | Power ratio $P_1/P_L$ for the low voltage cell of a two-cell CHB for varying                                                                |    |

|      | ratios of $v_1/(v_1+v_2)=v_1/v_L$ , assuming converter voltages $v_1-v_2$ and                                                               |    |

|      | $-v_1 + v_2$ are not used for PWM generation                                                                                                | 46 |

| 3.10 | PQ plane operational region for a three-cell grid-tied asymmetric CHB                                                                       |    |

|      | converter operating in the linear region, $with\ all\ available\ output\ voltages$                                                          |    |

|      | utilized. Voltage ratios are in the trinary configuration, $v_1:v_2:v_3=1:$                                                                 |    |

|      | 3:9                                                                                                                                         | 46 |

| 3.11 | PQ plane operational region for a three-cell grid-tied asymmetric CHB                                                                       |    |

|      | converter operating in the linear region, with some output voltages un-                                                                     |    |

|      | used. Voltage ratios are in the trinary configuration                                                                                       | 47 |

| 3.12 | PWM and cell references for an $M=3$ cell CHB with $v_1=25\mathrm{V},$                                                                      |    |

|      | $v_2 = 50 \text{V}, \ v_3 = 150 \text{V}, \ \text{and} \ r(\theta) = 215 \left(\sin{(\theta)} + \sin{(3\theta)} / 6\right). \ \text{Using}$ |    |

|      | hybrid PWM, only the low voltage cell switches at PWM frequency                                                                             | 48 |

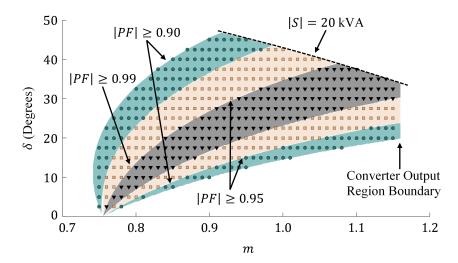

| 3.13 | Simulated data (markers) from test case 1 compared to results (shaded                                          |    |

|------|----------------------------------------------------------------------------------------------------------------|----|

|      | areas) obtained via (3.1), showing regions in the $m\delta$ plane corresponding                                |    |

|      | to power factors greater than 0.9, 0.95, and 0.99 when power is delivered                                      |    |

|      | to the grid and components have an artificially imposed VA limit of                                            |    |

|      | 20 kVA                                                                                                         | 50 |

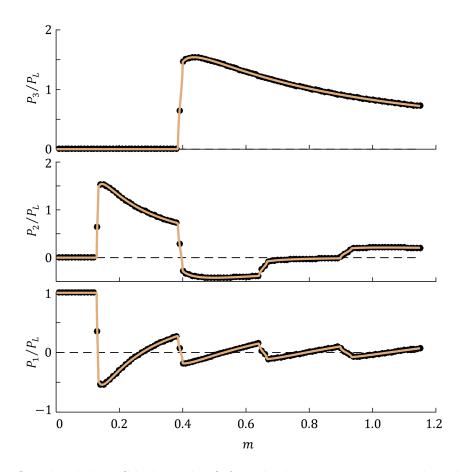

| 3.14 | Simulated data (black markers) from both test cases compared to data                                           |    |

|      | (gold) obtained via (3.5), showing the ratio $P_x/P_L$ is only dependent                                       |    |

|      | upon $m$                                                                                                       | 51 |

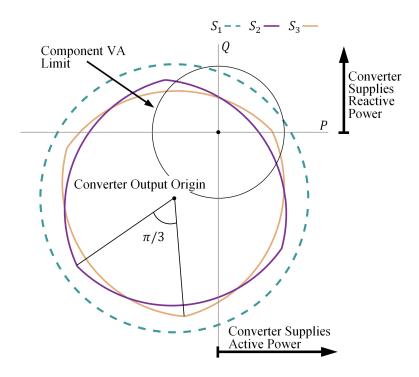

| 4.1  | PQ plane output region boundary for: no negative-sequence component                                            |    |

|      | $(S_1)$ ; negative-sequence component $V_2 \angle \theta$ $(S_2)$ ; and negative-sequence                      |    |

|      | component $V_2 \angle (\theta + \pi/3)$ (S <sub>3</sub> ). An ideal component VA limit is included             |    |

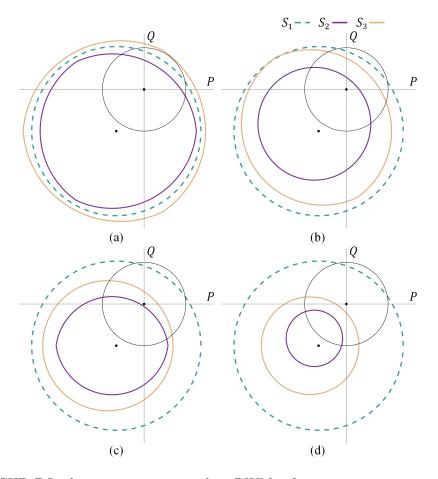

|      | as a typical, though arbitrary, reference.                                                                     | 56 |

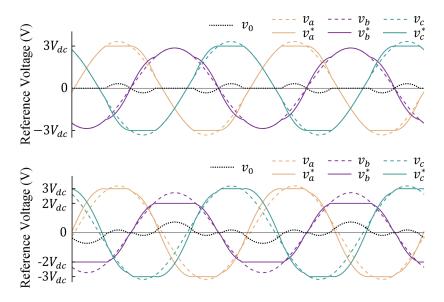

| 4.2  | Unadjusted PWM references containing a negative-sequence component,                                            |    |

|      | $v_x$ , compared to Atypical PWM references, $v_x^* = v_x - v_0$ , for a healthy                               |    |

|      | [3,3,3] CHB (top), and a [3,2,3] CHB (bottom)                                                                  | 58 |

| 4.3  | CHB PQ plane output region when PWM references contain negative-                                               |    |

|      | sequence component $V_2 \angle 0$ without any common-mode component $(S_2)$                                    |    |

|      | and using the proposed atypical PWM method $(S_3)$ for: (a) healthy                                            |    |

|      | [3,3,3] CHB, (b) $[3,3,2]$ CHB, (c) $[3,2,2]$ CHB, and (d) $[3,2,1]$ CHB.                                      |    |

|      | A circle, $S_1$ , centered at the converter's operating origin is included for                                 |    |

|      | reference.                                                                                                     | 61 |

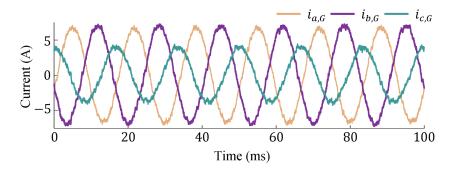

| 4.4  | Setup used for experimental verification                                                                       | 63 |

| 4.5  | Grid currents drawn by the converter and unbalanced load for $R_a =$                                           |    |

|      | $24\Omega$ , $R_b=24\Omega$ , and $R_c=31\Omega$ , when $V_{LL,rms}=208\mathrm{V}$ , $MV_{dc}=195\mathrm{V}$ , |    |

|      | and the converter does not supply negative-sequence compensation                                               | 63 |

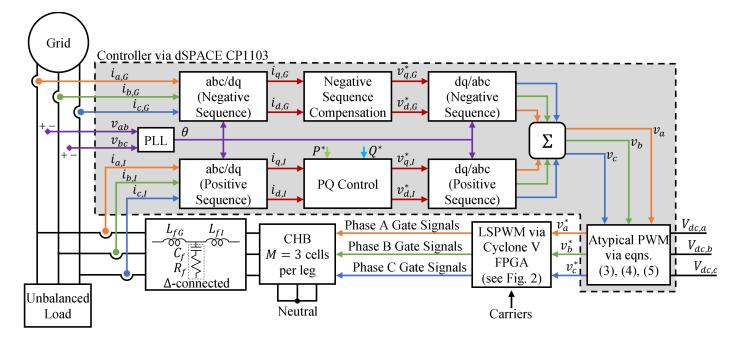

| 4.6 | Block diagram of the system used for experimental verification                  | 64 |

|-----|---------------------------------------------------------------------------------|----|

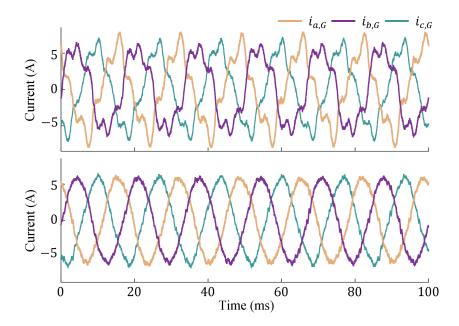

| 4.7 | Grid currents using total leg dc bus voltage $MV_{dc}=160\mathrm{V},$ obtained  |    |

|     | without (top) and with (bottom) the proposed atypical PWM scheme                | 65 |

| 4.8 | Grid current THD vs. total leg dc bus voltage, $MV_{dc}$ , with each dc         |    |

|     | bus voltage tested at three different measurement instants. For the case        |    |

|     | where a cell is faulty, $MV_{dc}$ is the total dc bus voltage of a healthy leg. | 66 |

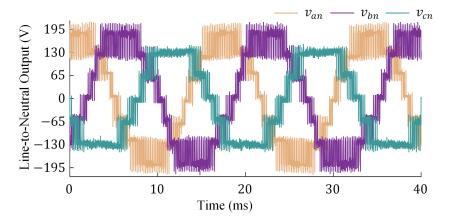

| 4.9 | Line-to-neutral PWM waveforms obtained when a leg C cell is bypassed            |    |

|     | using the proposed technique, and the total dc bus leg voltage of a             |    |

|     | healthy leg is $MV_{dc} = 195 \mathrm{V.}$                                      | 66 |

| 5.1 | A grid-interactive cascaded H-bridge multilevel converter                       | 69 |

| 5.2 | Reference and carrier waveforms (top) and converter line-to-neutral out-        |    |

|     | put (bottom) obtained using conventional SPWM, assuming $r\left(t\right)>0$     |    |

|     | for $t \in (0, T/2) \cup (T, 3T/2)$ , and $r(t) < 0$ otherwise                  | 71 |

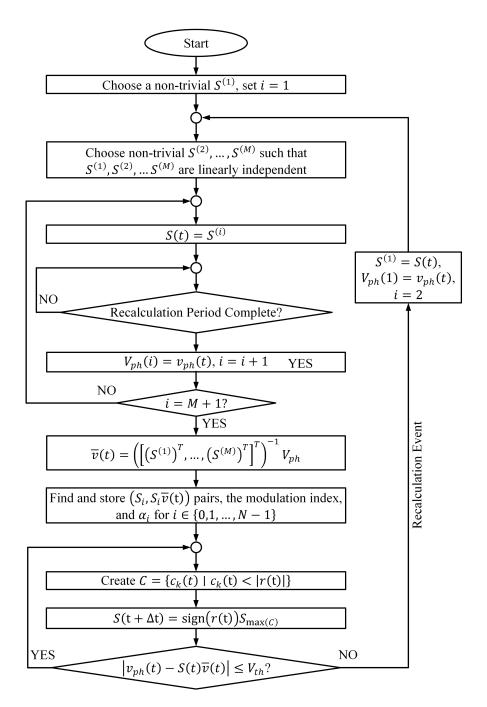

| 5.3 | Flowchart of SPS adaptive SPWM                                                  | 72 |

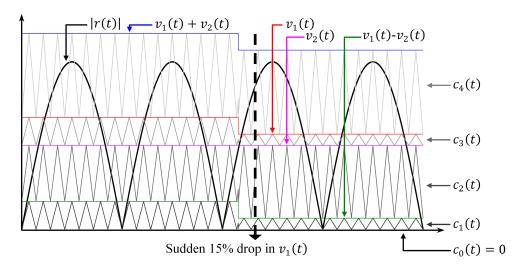

| 5.4 | Example showing SPS adaptive SPWM where a recalculation event is                |    |

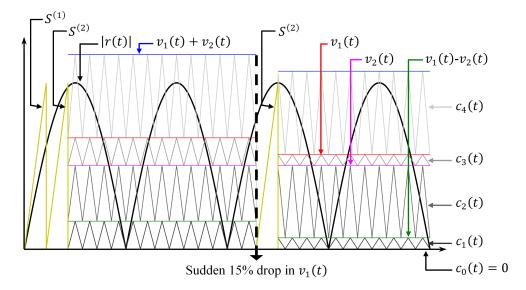

|     | triggered during the third half-cycle                                           | 74 |

| 5.5 | Flowchart of SPL adaptive SPWM                                                  | 76 |

| 5.6 | Example showing SPL adaptive SPWM with an initialization event as               |    |

|     | well as a recalculation event in the third half-cycle, with recalculation       |    |

|     | periods shown as one period of a sawtooth waveform.                             | 79 |

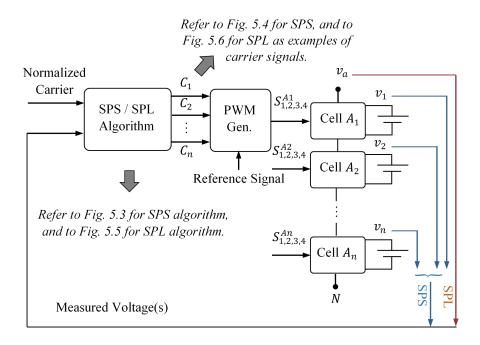

| 5.7 | Block diagram representation of the SPS and SPL algorithms, allowing            |    |

|     | a given reference signal to be more accurately followed using available         |    |

|     | sources.                                                                        | 81 |

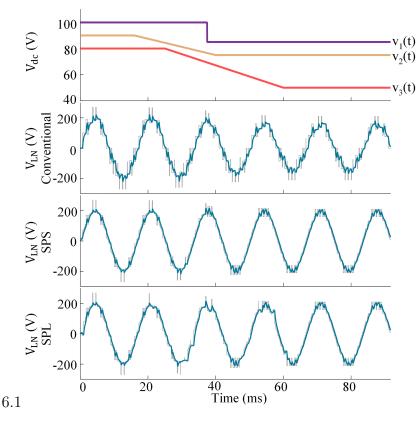

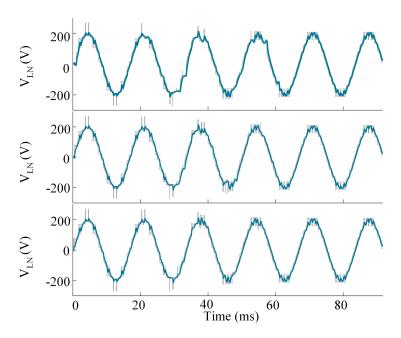

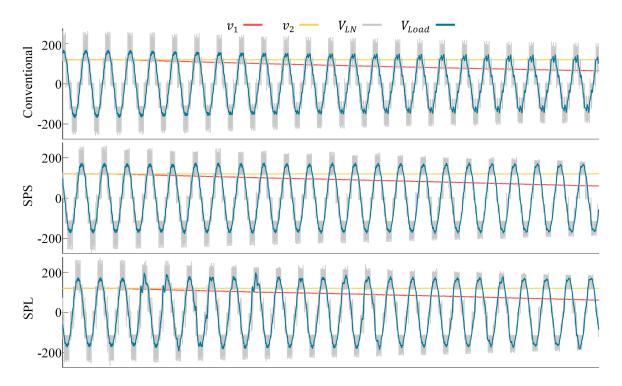

| 5.8  | Cell voltages (top) used to generate converter unfiltered output voltages                                    |    |

|------|--------------------------------------------------------------------------------------------------------------|----|

|      | (gray) and filtered load voltages (blue) for conventional SPWM, SPS                                          |    |

|      | adaptive SPWM, and SPL adaptive SPWM algorithms using simulation                                             |    |

|      | parameters shown in Table 5.2                                                                                | 83 |

| 5.9  | Comparison of unfiltered output voltages (gray) and filtered load volt-                                      |    |

|      | ages (blue) generated via SPL adaptive SPWM for $T_r = 500 \mu\mathrm{s}$ (top),                             |    |

|      | $250\mu s$ (middle), and $125\mu s$ (bottom) using simulation parameters shown                               |    |

|      | in Table 5.2                                                                                                 | 85 |

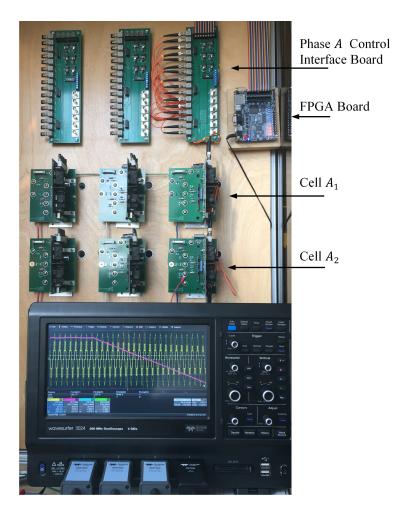

| 5.10 | One phase of this experimental setup was used to verify the proposed                                         |    |

|      | techniques, as the SPS and SPL algorithms are implemented indepen-                                           |    |

|      | dently for each CHB leg                                                                                      | 86 |

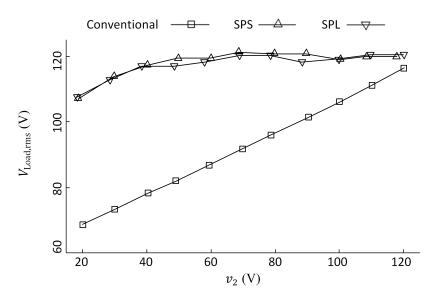

| 5.11 | Steady-state fundamental rms voltage for $v_1 = 120 \text{ V}$ and $v_2 \in [20 \text{ V}, 120 \text{ V}]$ , |    |

|      | obtained using conventional SPWM, SPS adaptive SPWM, and SPL                                                 |    |

|      | adaptive SPWM                                                                                                | 87 |

| 5.12 | Dynamic performance of the conventional first-on-first-off algorithm, the                                    |    |

|      | SPS algorithm, and the SPL algorithm for a rapidly decreasing cell voltage.                                  | 88 |

| 5.13 | Partitioning of the half-wave region $[0,\pi]$ for a two-cell asymmetric CHB                                 |    |

|      | which minimizes the number of switching transitions for the higher volt-                                     |    |

|      | age cell, where the reference in a region is generated by switching be-                                      |    |

|      | tween levels with solid lines                                                                                | 91 |

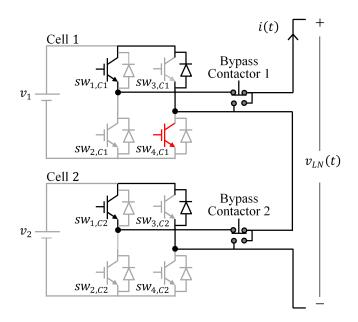

| 6.1  | One cascaded H-bridge multilevel converter leg                                                               | 94 |

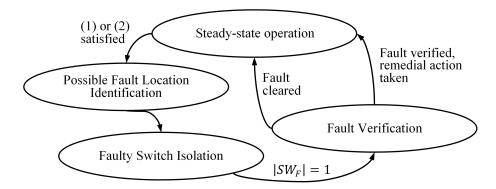

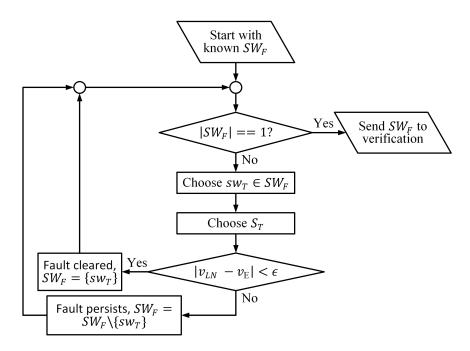

| 6.2  | Finite-state machine diagram for the proposed fault-detection method.                                        | 96 |

| 6.3  | Current path when $i\left(t\right)>0$ for a two-cell CHB leg under the $S=\left[1,0_{U}\right]$              |    |

|      | leg-state, with an open-circuit fault in $sw_{4,C1}$ . The expected voltage is                               |    |

|      | $v_E = v_1$ , but the measured voltage is $v_{LN}(t) = 0$                                                    | 98 |

| 6.4  | Procedure for fault location isolation using set of possible fault locations,          |     |

|------|----------------------------------------------------------------------------------------|-----|

|      | $SW_F$ , identified as explained in Section 6.2.1                                      | 99  |

| 6.5  | Three-step verification process for a $sw_{x,Cy}$ fault, $x \in \{1,4\}$ . For $x \in$ |     |

|      | $\{2,3\}$ the current direction for each step is reversed                              | 102 |

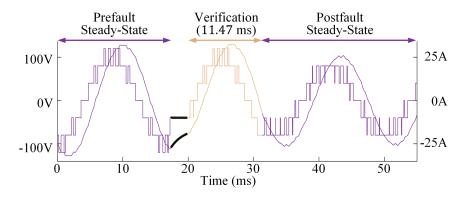

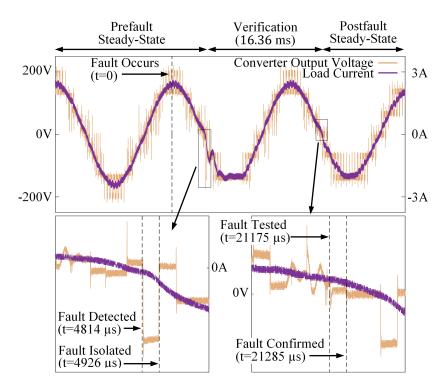

| 6.6  | CHB leg line-to-neutral voltage and load current with a $sw_{3,C3}$ open-              |     |

|      | circuit fault occurring at 17.35 ms. Fault detection and isolation, high-              |     |

|      | lighted in black, occur in the 2.5 ms between prefault steady-state and                |     |

|      | verification.                                                                          | 105 |

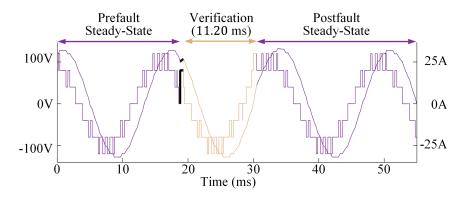

| 6.7  | CHB leg line-to-neutral voltage and load current with a $sw_{1,C1}$ gate               |     |

|      | misfiring fault occurring at 18.8 ms. Fault detection and isolation, high-             |     |

|      | lighted in black, occur in the $0.5\mathrm{ms}$ between prefault steady-state and      |     |

|      | verification.                                                                          | 106 |

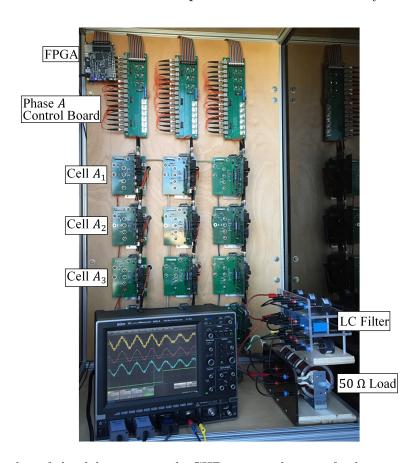

| 6.8  | One leg of this laboratory scale CHB was used to verify the proposed                   |     |

|      | technique, as it is designed to be implemented independently for each leg.             | 108 |

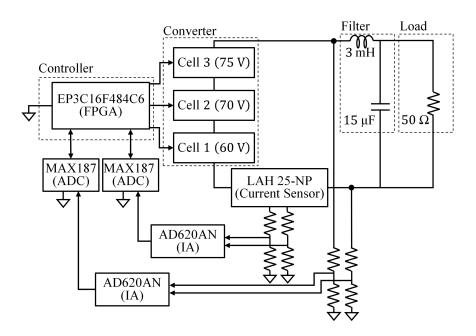

| 6.9  | Diagram of experimental setup, detailing the current and voltage sensor                |     |

|      | circuitry used                                                                         | 109 |

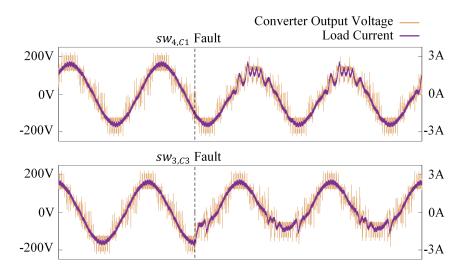

| 6.10 | Experimental data collected for an open-circuit fault in $sw_{4,C1}$ (top),            |     |

|      | and $sw_{3,C3}$ (bottom), if no corrective actions are taken                           | 109 |

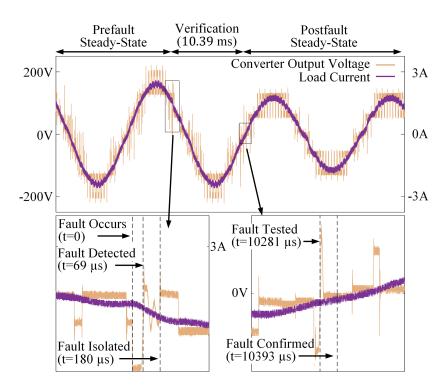

| 6.11 | Performance for an open-circuit fault in $sw_{1,C3}$ , with behavior shown in          |     |

|      | detail during detection/isolation and step three of the verification process.          | 110 |

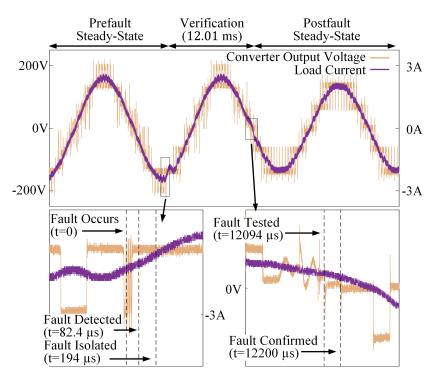

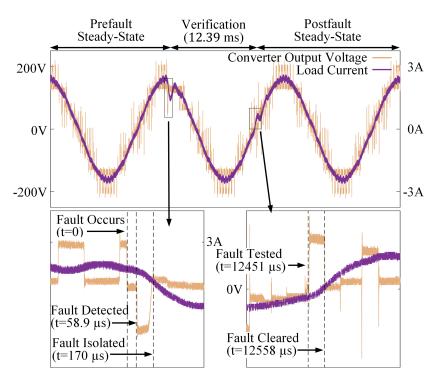

| 6.12 | Performance for an open-circuit fault in $sw_{2,C1}$ occurring mid-cycle               | 111 |

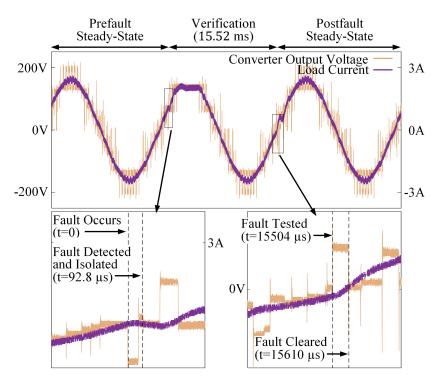

| 6.13 | Performance for an open-circuit fault in $sw_{1,C2}$ occurring during a non-           |     |

|      | affected cycle. Overmodulation is apparent due to the soft-bypass of the               |     |

|      | faulty cell during step one of the verification process                                | 112 |

| 6.14 | Performance for an open-circuit fault in $sw_{2,C1}$ occurring during a non-        |     |

|------|-------------------------------------------------------------------------------------|-----|

|      | affected cycle. Overmodulation is apparent due to the soft-bypass of the            |     |

|      | faulty cell during step one of the verification process                             | 113 |

| 6.15 | Performance for a gate misfiring fault in $sw_{4,C1}$ occurring during a non-       |     |

|      | affected cycle. Overmodulation is apparent as the faulty cell is soft-              |     |

|      | bypassed during step one of the verification process                                | 114 |

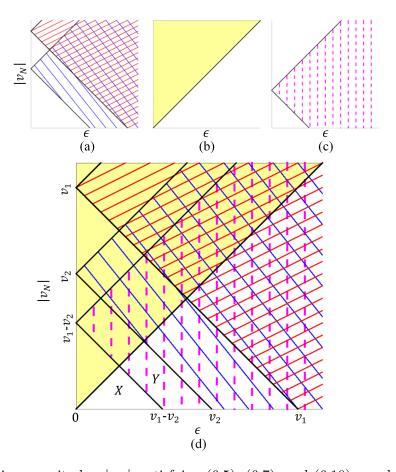

| 6.16 | Noise magnitudes, $ v_N $ , satisfying (6.5), (6.7), and (6.10) are shown for       |     |

|      | fixed $\epsilon$ in the shaded and hashed areas of (a), (b), and (c), respectively, |     |

|      | for a two-cell asymmetric CHB leg. The union of these areas is shown                |     |

|      | in (d). When a fault initially occurs $ SW_F $ is minimized if the system           |     |

|      | operates in region $X$ of (d), though operation in either region $X$ or             |     |

|      | region $Y$ ensures no false flags or missed detections will occur                   | 116 |

| A.1  | Flow diagram for the proposed development process                                   | 142 |

| A.2  | Simulink model used to generate a pulse waveform with duty ratio $D.\ .$            | 144 |

| A.3  | Simulink model used to generate a triangular waveform with unity am-                |     |

|      | plitude and zero dc offset                                                          | 145 |

| A.4  | HDL-Compatible MATLAB function used to generate a triangular wave-                  |     |

|      | form with no dc component                                                           | 145 |

| A.5  | Simulink model used to generate a sinusoidal waveform with arbitrary                |     |

|      | amplitude                                                                           | 147 |

| B.1  | Cascaded H-bridge converter                                                         | 149 |

| B.2  | Cell switch position to set IA gains for FPGA                                       | 151 |

| В.3  | Brain board switch position to send measurements to ADCs                            | 151 |

| B 4  | Layout of terminal strips on the upper backside of the CHB                          | 153 |

## List of Tables

| 2.1 | Cell $A_n$ Switch Configurations, Output Voltages, and States                           | 19  |

|-----|-----------------------------------------------------------------------------------------|-----|

| 3.1 | Numerical Test Case Results                                                             | 49  |

| 4.1 | Experimental Parameters                                                                 | 62  |

| 5.1 | Cell $A_n$ Switch Configurations, Output Voltages, and States                           | 70  |

| 5.2 | Simulation Parameters                                                                   | 82  |

| 5.3 | Analysis of Simulation Steady-State Behavior Before and After Cell In-                  |     |

|     | put Voltage Changes Shown in Fig. 5.8                                                   | 83  |

| 5.4 | Experimental Parameters                                                                 | 87  |

| 6.1 | Cell Switch Configurations, Output Voltages, and States                                 | 94  |

| 6.2 | Cell $n$ Output Voltage Deviation, $\Delta v = v_{expected} - v_{actual}$ , Under Open- |     |

|     | Circuit Fault Conditions                                                                | 95  |

| 6.3 | Simulation Parameters                                                                   | 104 |

| 6.4 | Experimental Parameters                                                                 | 107 |

| B.1 | FPGA GPIO Pin Assignments                                                               | 155 |

### Acknowledgments

First, I would like to thank my parents and my brothers for their encouragement during my studies. This dissertation would not exist without their support.

A big thanks to my advisor Dr. Behrooz Mirafzal. My experience as a graduate student would have been very different without his guidance, and the insight he provided has undoubtedly made me a better researcher. Also, I don't know how he is able to see the difference between font sizes or tell when letters appear pixelated, but my work would be much less visually appealing without his hawk-like vision.

I'd like to extend my gratitude to Dr. Dwight Day, Dr. Anil Pahwa, and Dr. Suresh Gopalakrishnan for the constructive input they all provided as members of my supervisory committee.

A tremendous thanks to Steve Booth for all of the insight he provided while I was building my converter, as well as for helping to improve my gardening capabilities by sharing his extensive horticultural knowledge.

My time in Manhattan would not have been as enjoyable without Mr. Aswad Adib's considerable abilities and professional attire, Mr. Joseph Benzaquen's insight and recognition of the mafia with which we've all become acquainted, or Mr. Mohsen Pilehvar's extremely thorough and extremely silent editing services. Additionally, I suppose I should also extend my gratitude to my *former* lab mate Dr. Akanksha Singh, even though she abandoned the lab and took her exceptional capabilities with

her. I appreciate the thought they have all given to my often pointless questions, as well as the enthusiasm of everyone's periodic rants against certain word processing software and laboratory equipment.

Finally, none of this would have been possible without the unconditional love and support of my wife, Caitlin. Because of everything she has done, she doesn't have to read the rest of this dissertation.

## Dedication

To Caitlin, of course.

### Chapter 1

### Introduction

The foundations of this dissertation, which introduces corrective schemes for internal and external abnormalities in cascaded multilevel converters, are laid in this introductory chapter. The motivation and objectives of the research presented herein are detailed in Section 1.1, and a literature review is presented in Section 1.2 to introduce relevant state-of-the-art fault tolerant techniques. The contributions of this dissertation are presented in Section 1.3, and Section 1.4 concludes this chapter with an outline of this dissertation's organization.

### 1.1 Motivation and Objectives

Solid-state based dc-ac power converters are ubiquitous, essential for the efficient generation and utilization of electrical energy. These converters are utilized in everything from traction vehicles to manufacturing facilities to traditional and renewable energy generators and, given the diverse range of applications, ensuring their functionality is paramount [1–16]. At a minimum, converter failure is an inconvenience often necessitating costly repairs [4, 14–17], and in critical applications converter failures can

be hazardous. For instance, a converter failure occurring in a transportation vehicle during operation can adversely affect vehicle stability, thereby endangering passengers [4, 12, 14, 17]. As such, ensuring the reliable operation of converters, though the introduction of fault tolerant hardware and control, has become an important goal for the electrical engineering community [1–7,10–23]. This dissertation continues pursuing this goal of increased reliability, with a focus on identifying and resolving abnormal operating conditions encountered by a particular dc-ac power converter topology.

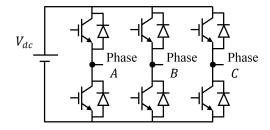

Traditionally, three-phase dc-ac converters utilized in industry have a two-level line-to-neutral voltage output. The three legs of a traditional two-level voltage source inverter (2L-VSI) each require two solid-state switches, such as IGBTs with anti-parallel diodes, as shown in Fig. 1.1. This minimalistic topology provides few opportunities for enabling fault tolerant operation, with continued post-fault operation achieved for instance through the utilization of redundant converter legs [24–26]. Due to the limited options for implementing fault tolerance in 2L-VSI, alternative converter topologies may be preferred when continued converter operation is essential. In particular, a relatively new class of converter topologies, called multilevel converters, have the potential to be used for fault tolerant applications.

Multilevel topologies have several advantages compared with traditional two-level converters, such as high efficiency due to lower switching frequencies and low electromagnetic emission due to low dv/dt [1–7,16,18–20,27–29]. Several multilevel topologies

**Fig. 1.1:** Conventional three-phase, two-level voltage source inverter topology.

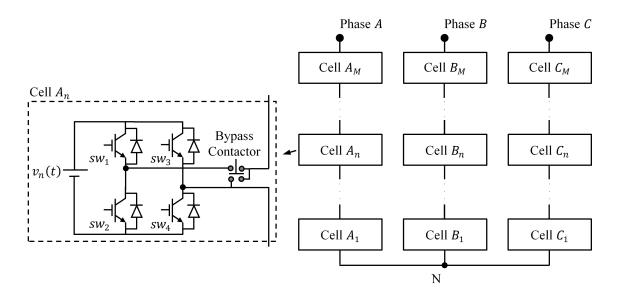

exist [1,4,5,16,24,27,29–32], but three of the most established are the neutral point clamped, the flying capacitor, and the cascaded H-bridge (CHB) multilevel converters [3–7,16,18–20,24,27,29,32,33]. The CHB topology, as shown in Fig. 1.2, has been identified as particularly promising for medium-voltage, high-power applications due in part to its inherent modularity and fault tolerance [3,16,24,29,34–37]. As such, this dissertation focuses on the CHB multilevel converter, which has been implemented and proposed for use in a wide range of applications, including active filters, renewable energy conversion systems, and traction motor applications [3–5,8,9,16,29,35,36,38].

Despite the benefits offered by the CHB converter, this topology requires many more switches and input sources than traditional 2L-VSI. These additional components increase the probability for internal fault events and other abnormal operating conditions, and the CHB's complexity increases the difficulty of isolating internal abnormalities. In addition to these internal abnormalities, application specific external nonidealities should also be accounted for when considering converter fault tolerance. However, due to the wide range of internal and external abnormalities which can occur during CHB

**Fig. 1.2:** Three-phase cascaded H-bridge multilevel topology with M cells per leg.

operation, it is not feasible to address all non-ideal operating conditions in one work. As such, the internal and external abnormalities investigated in this dissertation, outlined in the following subsections, were selected based on topology specific needs, i.e. the additional switches and sources required, as well as the promising prospective of using CHB to provide power in microgrid systems.

#### 1.1.1 Switch Faults

Solid-state semiconductor switches are known to be one of the most vulnerable parts of a power converter [4, 13–15, 17, 21, 23, 39–41]. Compared to traditional two-level voltage source inverters which utilize six switches, the probability of an IGBT fault is increased when using CHB converters due to the high number of semiconductor switches these topologies require [2, 4, 8, 19, 20, 24, 41]. These additional switches make the CHB topology inherently reconfigurable, however, allowing continued converter operation in the event of one or more faults [2–4, 24, 42].

Thermomechanical fatigue is the main cause of IGBT failures [15, 18, 21, 39], and due to the inherent power and thermal cycling in some applications, e.g. electric vehicle motor drives [43], this thermomechanical fatigue is difficult to avoid. Switch failures can be roughly classified as open- or short-circuit faults [1, 13–15, 17, 24, 41, 44, 45]. Although short-circuit failures can cause nearly immediate damage to a CHB cell [13, 14, 17, 20, 22, 41], the dangers of open-circuit faults cannot be neglected as extended operation with open-circuit failures can cause extensive damage to an entire system [1, 6, 9, 13, 14, 17, 41, 46]. Ultimately, the probability and consequences of an open-circuit fault event, e.g. due to thermomechanical fatigue, are non-negligible and must be addressed [13, 14, 17, 41, 46].

### 1.1.2 Utilization of Time-Variant DC Source Inputs

The CHB topology is unique because it requires several isolated dc sources. While these sources may be obtained using phase shifting transformers in grid-tied applications [2,4,5,16,33], the CHB is particularly suited for applications where isolated sources are inherently available, such as in applications utilizing batteries [27–29,31,37,47–49]. Batteries, as would be used in an electric or hybrid electric vehicle application [27–29, 37,47,49,50] or a grid-tied energy storage application [31,37,48,51–53] are time-variant sources, since a battery's terminal voltage is dependent upon battery chemistry, state of charge, temperature, current magnitude, and other factors [50,54–56]. This time-variance, combined with discrepancies in battery construction, unbalanced aging, or unequal discharging may cause input sources of a battery powered CHB to become unequal [37,47,49,50,57], negatively impacting the performance of typically utilized PWM schemes.

A further difficulty when using sources with unequal magnitudes in a CHB is that, under certain conditions, some sources receive an average regenerative power flow even when the overall converter is providing power [4, 33]. Note that a load-independent analytical method for identifying conditions which cause this discordant behavior is presented in this dissertation. Regardless, if a CHB cell source is a near fully charged battery, then an extended period of average regenerative power flow can lead to cell overcharging. This overcharging degrades the battery's cycle life and, depending on the battery chemistry, could cause battery overheating or a catastrophic failure such as ignition or explosion [47,50,57–59]. Nonetheless, the direct use of time-variant sources may be a desirable operating feature, depending on the application, and therefore the development of enabling methods is necessary.

### 1.1.3 Unbalanced Grid-Interactive Operation

In addition to stand-alone applications, cascaded H-bridge multilevel converters have a significant role as grid interfaces for renewable energy sources (RES) and battery energy sources (BES). This is particularly true in microgrids, which are seen as a key concept in smart-grid development [51,52,60]. Designed to operate in grid-connected and islanded modes [51–53,60–63], microgrids are a holonic means of facilitating RES integration into the power grid [51–53,62,63]. In addition to RES, the utilization of which has been increasing due to a wide range of factors including renewable portfolio standards arising from growing concerns about global climate change [34, 64, 65], microgrids typically incorporate BES to provide operating reserves [31,51–53,61,66], as well as traditional sources such as diesel generators [52,61,66]. Due to their utilization of independent sources, CHB converters are well suited to the interconnection of both BES and RES, particularly PV [29,31,34–36,48,51–53,61,66].

Irrespective of the input dc sources used, microgrid-interactive converters may be expected to provide auxiliary services, such as negative-sequence compensation [52, 60, 63], since harmonic- or negative-sequence currents drawn from traditional rotating generators can cause deleterious effects. This issue is particularly acute in microgrids, where smaller rotating generators can be used and loads may be unbalanced or contain nonlinear loads [52, 60, 63, 67]. When providing auxiliary services, however, converter reference waveforms required by carrier-based pulse width modulation (PWM) techniques may become distorted, i.e. nonsinusoidal, and unbalanced. Therefore, the maximum positive-sequence component of these waveforms must be reduced, since PWM references cannot exceed limits defined by a converter's dc bus voltages without causing overmodulation. Accordingly, the active- and reactive-power which a converter can supply are diminished when providing auxiliary services, and methods for maximizing dc bus utilization under these operating conditions must be developed.

### 1.2 Literature Review

In this section, a review of state-of-the-art fault tolerant approaches for addressing the challenges outlined in the Section 1.1 is presented.

#### 1.2.1 Switch Faults

Identification and isolation of open-circuit faults can be approached using algorithmic solutions, whereas short-circuit protection is often provided by hardware solutions [11, 12,14,17,18,41], such as the desaturation [20] or di/dt feedback methods [22]. Hardware is used for short-circuit protection largely due to the speed that these faults must be detected and corrected, often cited as 10 µs, in order to prevent damage to the complementary switch within a leg [11,14,18,24,41]. Furthermore, industrial drives typically include short-circuit protection [13,18,41], whereas protection is not included as a standard feature for open-circuit faults [23]. Accordingly, there is still an industry need for further advancements which protect against open-circuit faults [23,41], as presented in this dissertation, characterized by loss of IGBT control but continued operation of the faulty switch's anti-parallel diode [8,12,18]. Such faults are due, for instance, to wire bond liftoff or failure in gate-drive circuitry [6,17,18,44]. These open-circuit faults create deleterious effects which can cause further system damage if no remedial action is taken [1,6,9,13,14,18]. However, prior to any corrective reconfiguration, e.g. [8,42], the fault location must be pinpointed [16,19].

Various techniques for fault identification have been proposed [11,12,17,18,23,24,44], but are targeted toward implementation in two-level voltage source inverters and therefore do not aim to identify the exact location of a faulty switch in a multilevel converter. Other methods have been proposed for multilevel converters [6,7,13,18,19], but are not specifically intended for implementation in CHB converters.

One method designed for the identification of faulty switches in CHB multilevel converters is output voltage frequency analysis [8], where implementation requires a voltage sampling frequency  $f_m = Mf_s$  for a CHB with M cells per phase and a pulse width modulation (PWM) switching frequency  $f_s$ . The sampling requirement precludes the use of lower sampling frequencies, e.g. if M or  $f_s$  are large, or higher sampling frequencies, e.g. if high-speed instrumentation is available.

Artificial intelligence based techniques, employing e.g. artificial neural networks and genetic algorithms [9], can also be used to identify faulty switches in multilevel converters. This approach requires significant computational effort [6, 12], as well as application specific data or expert knowledge for training.

Techniques in [1] are also suitable for fault identification in CHB multilevel converters. The proposed approach analyzes current flow deviations caused by improperly operating zero-states in CHB cells. This method requires a diagnosis time of M fundamental cycles for an M cell CHB.

The fault detection techniques presented in [1,8,9] require utilization of symmetric input sources and specific PWM methods, potentially limiting their applicability. As such, there is a need for an open-circuit fault-detection technique which: (i) can be applied to symmetric and asymmetric converters, (ii) is independent of the PWM scheme utilized, (iii) identifies faults quickly, and (iv) does not have a significant computational burden.

### 1.2.2 Maintaining Balanced Input Sources

The isolated input sources required by CHB can be inherently supplied by sources such as batteries, but the time-variant nature of these sources can cause undesirable complications. Accordingly, many of the developed techniques utilized to modulate CHB require sources with equal magnitudes [4,16,68,69]. If sources with unequal magnitudes

are used, the sources are assumed to be time-invariant with known magnitudes existing in specific ratios [4, 28, 68] or cells are required to switch at low frequencies [29, 49].

Since multilevel PWM methods typically cannot effectively utilize time-variant sources with unequal voltage magnitudes in CHB, many applications utilizing battery sources instead employ techniques intended to ensure the magnitudes of these sources stay equal. For instance, converter topologies have been proposed for their potential to be used to balance batteries voltages, such as the double-star connected converter proposed in [47] or the boost inverter topology presented in [70,71]. These alternative topologies, however, can introduce further complications into systems. For instance, the topology proposed in [70,71] requires the use of floating capacitors which necessitate complex balancing schemes [72]. Furthermore, the possibility of directly utilizing time-variant sources should be explored for the CHB topology, due to the other benefits of this converter as well as its wide range of applications.

In some systems, such as hybrid and electric vehicles, the time-variant nature of batteries can be resolved by using dc-dc converters to regulate the available dc voltage [37, 47, 70, 73]. While this approach may enable the utilization of CHB converters and traditional modulation schemes, the inductor required by the dc-dc converters naturally increases the weight, size, cost and loss of the overall system [47, 70, 73]. Further, extending this solution to a battery powered CHB would require a dc-dc converter for each cell, increasing control complexity and device component count. Accordingly, approaches which can directly utilize batteries directly are valuable.

Unbalanced cell voltages caused the time-variant nature of battery sources can be mitigated via the use of battery balancing methods. Passive, also called dissipative, balancing techniques act by discharging high voltage cells, for instance through a resistive load, until all cell voltages are equal. While inexpensive and simply implemented, passive approaches are rarely implemented due to their inefficiency and slow operation [37, 47, 50, 74]. Active balancing methods are more attractive than passive solutions, operating for instance by transferring charge between cells using flying capacitors. These approaches are more efficient and provide balanced voltages more quickly than passive techniques, but they require additional components and control systems, thereby increasing system cost and introduce additional points of failure [29, 37, 47, 50, 74, 75]. Moreover, some balancing techniques require connections between dc sources, eliminating the isolation between sources required by CHB converters [29, 37, 50].

An alternative to battery balancing methods may provide a new path for utilizing time-variant sources. However, if sources are not balanced, then existing PWM techniques cannot be utilized without causing decreased system performance. Accordingly, a novel multilevel PWM technique must be developed to enable the direct utilization of time-variant dc sources.

#### 1.2.3 Effective Utilization of DC Sources

Modulation strategies used to generate converter outputs often aim to maximize do bus utilization, regardless of the converter topology being controlled. For three-phase, three-wire converters, maximal dc bus utilization requires line-to-neutral output voltages to contain a common-mode component, which can be added without affecting converter currents [8, 24, 31, 36, 48, 76–81]. Several techniques for creating appropriate common-mode components have been developed and are suitable for implementation in a wide range of converter topologies [42,77–81]. One commonly implemented method for generating a common-mode line-to-neutral component is third-harmonic injection, an approach detailed in Chapter 2. Space vector PWM (SVPWM) and other PWM techniques can also be used to create common-mode components which maximize dc bus utilization. While these techniques can be utilized to modulate CHB, they were not

specifically designed for the modular CHB structure and therefore can only be directly applied under certain circumstances, for instance when all CHB cells are functioning properly, precluding their use in fault tolerant applications. Nonetheless, many techniques for maximizing dc bus utilization have been developed to facilitate continued CHB operation after internal fault events [8, 24, 77, 78].

One prominent method for enabling CHB operation under internal fault conditions is introduced in [77]. This technique enables balanced line-to-line voltages to be produced by adjusting the phase shifts between PWM references, with phase shift angles obtained by solving a system of transcendental equations. Ultimately this approach adds a fundamental frequency common-mode component, and is therefore referred to as fundamental phase shift compensation (FPSC). The FPSC method is extended in [8], improving the flexibility and allowing increased line-to-line voltages under specific fault conditions. Due to their ubiquity, the FPSC and extended FPSC methods are reviewed in Chapter 2. Nonetheless, the FPSC techniques proposed in [77] and [8] have been developed only for balanced operating conditions for implementation in grid-tied applications.

The FPSC technique has also been modified in [80] for implementation in SVPWM modulated converter. The method proposed in [80], however, requires at least two of the CHB phases to have an equal number of operative cells, necessitating healthy cells to be bypassed if this condition is not met. The authors of [80] also extended the FPSC technique to a different PWM strategy in [81], though the proposed method can only be implemented if one CHB cell is faulty. Moreover, implementation in unbalanced systems was not considered in either [80] or [81].

In [78], the set of common-mode components which ensure linear-modulation is determined, and the injected common-mode component is computed as the mean value of set elements. The process for obtaining a suitable common-mode component using this approach is complex [26], and analysis presented in [78] only considered implementation in balanced systems.

While these techniques for maximizing dc bus utilization enable continued CHB converter operation after internal faults, analysis has only been presented for converters operating under balanced conditions. As such, there is still a need for a technique which can be be implemented during unbalanced operating conditions, for instance when a converter supplies auxiliary services such as negative-sequence compensation.

### 1.3 Contribution of Dissertation

Cascaded H-bridge multilevel converters are a promising topology for dc-ac conversion, but more work is needed to increase their reliability as well as their capacity to adequately operate during external non-idealities. This dissertation presents corrective schemes which enable continued CHB operation under internal and external abnormalities, with the following primary contributions:

- An analytical technique for identifying the active- and reactive-power which a grid-interactive converter can provide. This method enables a converter's operating region to be analyzed for varying converter parameters under nominal and abnormal conditions, facilitating the converter design process.

- A load-independent approach for identifying discordant operating conditions, i.e. conditions which cause some cells within a leg to provide power to other cells within a leg. Identifying the conditions which cause discordant operation is essential for determining whether hardware or control modifications are necessary to mitigate or eliminate this behavior.

- An atypical PWM technique for maximizing converter dc bus utilization. This

method can be implemented in real-time for a wide range of dc-ac converter topology operating under a ideal and abnormal conditions.

- Adaptive carrier-based PWM techniques which enable CHB to directly utilize time-variant sources. These methods adjust the amplitude and offset of carriers used for PWM generation, enabling symmetric output waveforms to be generated when cells utilize non-ideal inputs.

- A method for open-circuit IGBT fault detection in cascaded H-bridge (CHB) multilevel converters. Once potential fault locations have been identified using this approach, the fault location is systematically isolated and then verified, reducing the possibility of unnecessary corrective actions due to fault misidentification, e.g. an intermittent gate misfiring fault being classified as an open-circuit fault.

The efficacy of the developed techniques are supported by MATLAB/Simulink simulations as well as experimental data obtained using a laboratory-scale cascaded H-bridge multilevel converter.

## 1.4 Organization of Dissertation

The remainder of this dissertation is organized as follows:

An introduction to the cascaded H-bridge topology is provided in Chapter 2. Level-shifted and hybrid PWM, techniques typically utilized to generate gate signals for symmetric and asymmetric CHB, are also presented. Moreover fundamental phase shift compensation, a common approach for enabling CHB operation to continue after internal fault events, is reviewed.

An approach for identifying the operating region of grid-interactive CHB is presented in Chapter 3. The output region, defined by the linear modulation region and the filter coupling the converter to the grid, is analyzed first. The converter's operational region, a subset of the converter's output region, is then identified, with restrictions imposed by component VA limits, THD limitations, and the requirement that active-power is delivered by the converter. Finally, an analytical technique is presented for identifying discordant operating points, where some cells in a CHB regenerate power while the leg delivers power, or vice-versa.

A technique for maximizing dc bus utilization is presented in Chapter 4. This technique, compatible with carrier-based PWM methods and all voltage source converter topologies, injects references with the minimum zero-sequence component required to enable linear modulation. This method does not rely upon synchronization of waveforms, as third-harmonic injection does, nor does it require the use of lookup tables, as fundamental phase-shift compensation does. Moreover, this technique is easy to implement, and can be used when converter supplies auxiliary services such as negative-sequence compensation.

In Chapter 5, adaptive algorithms are developed to modify level-shifted PWM to allow CHB to directly utilize time-variant dc sources. The sensor-per-source algorithm is able to immediately respond to varying input sources by utilizing M voltage sensors and a current sensor. The sensor-per-leg algorithm is presented next, enabling direct utilization of time-variant dc sources with a single sensor, though a recalculation period is required when cell voltages are changed.

A technique developed for open-circuit fault identification and isolation in CHB is presented in Chapter 6. First, the effects of uncorrected open-circuit faults are identified. Next, the foundation is laid for the technique for detecting open-circuit faults utilizing a single voltage and current sensor. Due to sensor placement, this technique is well suited to work in tandem with the sensor-per-leg algorithm presented in Chapter 5. However, this open-circuit fault identification technique is implemented

as a subroutine, making it compatible with any switching pattern.

Finally, a summary of the presented research and this dissertation's contribution to state-of-the-art converters is presented in Chapter 7. Suggestions for future work to increase converter flexibility are also proposed in this concluding chapter.

# Chapter 2

# The Cascaded H-Bridge Multilevel

# Converter

The cascaded H-bridge multilevel converter is the dc-ac converter topology at the center of many of the techniques presented in this dissertation, and therefore the working principles of this converter are foundational for the work presented in future chapters. To that end, an overview of the CHB is provided in this chapter, beginning with an introduction to the CHB topology in Section 2.1. The level-shifted and hybrid PWM techniques, as well as a method for improving dc bus utilization during healthy converter operation, are presented in Section 2.2. In Section 2.3, a technique for enabling fault tolerance in CHB is introduced.

## 2.1 System Topology

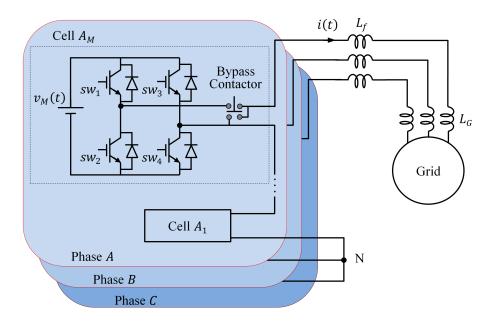

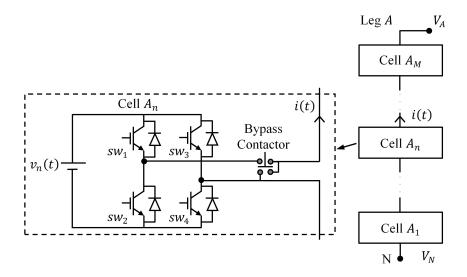

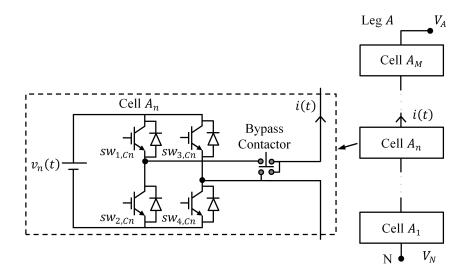

In this section, the symmetric and asymmetric CHB converter topologies are presented. Each CHB converter leg, as shown in Fig. 2.1 for a grid-interactive CHB, is used to generate a single electrical phase. Each leg consists of M series connected cells, or

Fig. 2.1: A grid-interactive cascaded H-bridge multilevel converter.

modules, with each cell generally including: (i) an H-bridge configuration of four IGBTs with anti-parallel diodes, (ii) a bypass contactor used to completely bypass the cell, e.g. in the event of a fault [3,24], and (iii) an isolated dc source input, such as batteries, fuel cells, or PV arrays. For PV applications, additional hardware is typically required in order to implement maximum power point tracking algorithms and to isolate the PV modules from the grid [35, 36, 64, 65].

For both grid-interactive and stand-alone CHB, passive filters are generally utilized to attenuate high frequency harmonics. The multilevel waveforms generated by CHB converters allow for the use of simpler inductive filters [34–36, 64, 65, 82], compared to the LCL filters typically used by traditional two-level inverters [82–84]. However, depending on the converter's switching frequency and the number of cells in each leg, utilization of an LCL filter may be advantageous. For grid-interactive CHB, system operators may also need consider the inherent grid impedance,  $Z_G$ , in addition to the impedance of the filtering impedance,  $Z_f$ . The magnitude of  $Z_G$  varies from one region

to the next, and can vary throughout the lifetime of an installed converter [83].

A CHB is said to be symmetric if all cell sources have equal magnitude, otherwise the CHB is asymmetric [3, 4, 33]. A symmetric CHB has many redundant switching states whereas an asymmetric CHB eliminates some or all redundant states to increase the number of unique voltage levels which the converter can generate [3–5]. Asymmetry may be intentionally introduced for a system [4], but it can also occur due to external factors. For instance, partial shading may cause asymmetry when using PV sources [34–36, 64, 65]. One difficulty when operating an asymmetric CHB is the existence of discordant output points, where power is transferred between cells within a leg, for instance causing one cell to have a net regenerative power flow when the overall converter leg is providing power [3, 4]. Depending on the input dc sources utilized by a CHB, discordant converter output points may be undesirable. For instance, if a CHB utilizes asymmetric batteries as input dc sources, then extended operation at a discordant output point can lead to battery overcharging even when the converter operates in motoring mode. The battery's cycle life can be negatively impacted by this overcharging and, depending on the battery chemistry, overcharging could even cause battery overheating or a catastrophic failure such as ignition or explosion [3,47,57].

A CHB leg's line-to-neutral voltage is equal to the sum of the output voltages of all cells within that leg, where cell  $A_n$  can be made to provide an output voltage of  $v_n$ , 0, or  $-v_n$  by appropriately controlling switches  $sw_1$ ,  $sw_2$ ,  $sw_3$ , and  $sw_4$  [3,27]. Notation is simplified by noting that  $sw_1$  and  $sw_2$  act in a complimentary manner, as do  $sw_3$  and  $sw_4$ , allowing the four available cell states to be uniquely identified according to the configuration of  $sw_1$  and  $sw_3$ . The four allowable cell switch configurations each correspond to a unique cell state,  $s_n(t)$ , as shown in Table 2.1. With the exception of Chapter 6, the two zero cell states are treated interchangeably throughout this dissertation, i.e.  $0_U = 0_L = 0$ .

**Table 2.1:** Cell  $A_n$  Switch Configurations, Output Voltages, and States

| $\overline{[sw_1, sw_3]}$ | Cell Output Voltage     | Cell State $s_n(t)$ |

|---------------------------|-------------------------|---------------------|

| [0, 0]                    | 0                       | $0_L$               |

| [0, 1]                    | $-v_{n}\left( t\right)$ | -1                  |

| [1, 0]                    | $v_n\left(t\right)$     | 1                   |

| [1,1]                     | 0                       | $0_U$               |

#### 2.2 PWM Methods