# SOME FURTHER CONSIDERATIONS IN THE DESIGN AND IMPLEMENTATION OF A LOW-POWER, 15-BIT DATA ACQUISITION SYSTEM/

by

JEFFREY DARREN BRADLEY

B. S., Kansas State University, 1985

A MASTER'S THESIS

submitted in partial fulfillment of the requirements for the degree

MASTER OF SCIENCE

Department of Electrical and Computer Engineering

KANSAS STATE UNIVERSITY Manhattan, Kansas

1986

Approved by:

Major Professor

V7750F P45550

## Acknowledgements

This work was sponsored and funded by the Systems Engineering Division 5238, Sandia National Laboratories, Albuquerque, New Mexico.

I would especially like to thank my major professor, Dr. M. S. P. Lucas for his friendship and insight during my research work. I would also like to thank Dr. J. Garth Thompson and Dr. Ruth Dyer for serving as my committee members, and Michelle White for her assistance in the preparation of some of the figures that appear in this thesis.

Finally, I would like to thank my wife, Lois, for her patience and understanding during my studies at KSU.

## CONTENTS

| <u>p</u> ag                                                |

|------------------------------------------------------------|

| List of Figures v                                          |

| Introduction                                               |

| CHAPTER 1. REVIEW OF THE EXISTING LOW-POWER DAS HARDWARE 3 |

| Introduction                                               |

| Analog Section 4                                           |

| Two Channel Track-and-Hold 4                               |

| Successive Approximation ADC 6                             |

| Control Logic                                              |

| Power Supply Filtering and Switching Network 14            |

| Theory of Operation, Analog Section                        |

| Digital Section                                            |

| Microprocessor Controller                                  |

| Supporting Digital Hardware 24                             |

| Theory of Operation, Digital Section                       |

| Interfacing with a Host System                             |

| Performance of the Existing Low-Power DAS30                |

| CHAPTER 2. INHERENT ERROR SOURCES IN THE LOW-POWER DAS 35  |

| Introduction                                               |

| Mismatch of Polarity Ranges                                |

| Improperly Offset DAC Output                               |

| Unusually Large Voltage Step at DAC Circuit's Output . 37  |

| Uncertain Reference for Polarity Determination 41          |

| Track-and-Hold Droop 41                                    |

| Droop During a Conversion 42                               |

|       | Droop   | ΟĪ   | Sec  | cond | ב          | sa | mρ | ıе | :a  | VC    | Ιt   | ac  | ie . | טע         | ırı | na | 1 ( | .or | IV E  | ers | <b>51</b> 0 | n   | 01 | : |   |             |

|-------|---------|------|------|------|------------|----|----|----|-----|-------|------|-----|------|------------|-----|----|-----|-----|-------|-----|-------------|-----|----|---|---|-------------|

|       | First   |      |      |      |            |    |    |    |     |       |      |     |      |            |     |    |     |     |       |     |             |     |    |   | • | 44          |

| Sys   | stem No | ois€ | • •  | •    | •          | •  | •  | •  | •   | •     | •    | •   | •    | •          | •   | •  | •   | •   | •     | •   | •           | •   | •  | • | • | 44          |

| Cor   | mparato | or F | Rela | ate  | đ          | Pr | ob | le | ms  | 3     | •    | •   | •    | •          | •   | •  | •   | •   | •     |     | •           | •   | •  | • |   | 46          |

|       | Improp  | per  | Pow  | er   | s          | up | pl | У  | Ву  | pa pa | SS   | in  | ıg   | •          |     | •  | •   | •   | •     | •   |             | •   | •  | • | • | 46          |

|       | Unwant  | ted  | Fee  | dba  | ac         | k  | •  | •  |     | •     | •    | •   | •    | •          | •   | •  | •   | •   | •     | •   |             | •   | •  | • | • | 4 8         |

|       | Input   | Noi  | se   |      | •          |    | •  |    |     | •     |      | •   |      |            |     | •  | •   | •   | •     | •   | •           | •   | •  | • | • | 49          |

|       | Input   | Off  | Eset | V    | 01         | ta | ge |    |     | •     |      |     | •    |            |     | •  | •   | •   | •     | •   |             | •   |    | • | • | 52          |

| CHAPT | ER 3.   | A P  | 4ICE | ROP  | RO         | CE | SS | OR | t-E | BAS   | ED   | ) E | ERF  | OF         | ۲ C | OM | IPE | ENS | ľA    | 'IC | ON          |     |    |   |   |             |

|       | IQUE .  |      |      |      |            |    |    |    |     |       |      |     |      |            |     |    |     |     |       |     |             | •   | •  | • | • | 55          |

| In    | troduct | tior | ı .  | •    | •          | •  | •  | •  | •   | •     | •    | •   | •    | •          | •   | •  | •   | •   | •     | •   | •           | . • | •  | • | • | 55          |

| The   | eory .  | • •  |      | •    | •          | •  | •  | •  | •   | •     | •    | •   | •    | •          | •   | •  | •   | •   | •     | •   | •           | •   | •  | • | • | 55          |

| Im    | plement | tati | ion  | •    | •          | •  | •  | •  | •   | •     | •    | •   | •    | •          | •   | •  | •   | •   | •     | •   | •           | •   | •  | • | • | 60          |

|       | Circu   | it M | ibol | ifi  | ca         | ti | on | s  | •   | •     | •    | •   | •    | •          | •   | •  | •   | •   | •     |     |             | •   | •  | • | • | 61          |

|       | Theory  | y of | E Or | pera | at         | io | n  | •  | •   | •     | •    | •   | •    | •          | •   | •  | •   | •   |       | •   | •           | •   | •  | • | • | 66          |

| In    | itial 1 | Resi | ults | 3    | •          |    |    | •  | •   | •     | •    | •   | •    | •          | •   |    | •   |     | •     | •   | •           | •   | •  | • | • | 70          |

| CHAPT | ER 4.   | RE(  | COM  | 1EN  | DA         | ΤI | ON | s  | FC  | R     | FU   | JΤU | JRE  | : 1        | ME  | LE | MI  | ENT | ['A'] | CIC | SNC         | 3 ( | F  |   |   |             |

|       | AS      |      |      |      |            |    |    |    |     |       |      |     |      |            |     |    |     |     |       |     |             |     |    | • | • | 75          |

| In    | troduct | tior | ı .  | •    | •          | •  | •  | •  | •   | •     | •    | •   | •    | •          | •   | •  | •   | •   | •     | •   | •           | •   | •  | • | • | 75          |

| Con   | ntinue  | ∄ De | eve] | Lopi | me         | nt | 0  | f  | th  | ıe    | Pr   | es  | ser  | ıt         | De  | si | gr  | 1   | •     | •   | •           | •   | •  | • | • | 75          |

|       | Quali   | ty c | of ( | Comp | po         | ne | nt | s  | •   | •     | •    | •   | •    | •          | •   | •  | •   | •   | •     | •   | •           | •   | •  | • | • | 76          |

|       | Diffe   | rent | :ia] | LL   | in         | ea | ri | ty | , ( | Cor   | ı Ce | ŗŗ  | ıs   | •          | •   | •  |     | •   | •     | •   | •           | •   | •  | • | • | 76          |

|       | Integ   | ral  | Lir  | nea  | ri         | ty | C  | on | CE  | ern   | ıs   | •   | •    | •          | •   | •  | •   | •   | •     | •   | •           | •   | •  | • |   | 77          |

|       | Crysta  | al ( | Osci | 111  | at         | or | F  | re | ·qυ | ıer   | су   | ,   | •    | •          | •   | •  | •   | •   | •     | •   | •           | •   | •  | • |   | 78          |

|       | Other   | Cor  | nsid | der  | at         | io | ns |    | •   | •     | •    | •   | •    | •          | •   | •  | •   | •   | •     | •   | •           | •   | •  | • | • | 79          |

| De    | velopme | ent  | of   | a    | <b>"</b> S | ec | on | d  | Ge  | ene   | era  | ıtj | or   | ı <b>"</b> | De  | si | gr  | 1   |       |     | •           |     | •  | • | • | 79          |

| SUMMA | RY      | • •  |      | •    | •          | •  |    | •  | •   | •     | •    | •   | •    |            | •   | •  |     |     |       | •   | •           | •   |    |   |   | 82          |

| APPEN | DIX A - | - Ci | ircı | ıit  | ת          | ia | ar | aπ | າຣ  | ar    | ıd   | Pa  | ırt  | :s         | Į.i | st | :s  | fo  | r     | tl  | ne          |     |    |   |   |             |

|       |         |      | kist |      |            |    | _  |    |     |       | _    |     |      |            |     |    |     |     |       |     |             |     |    |   | P | <b>\</b> -1 |

| APPENDIX B - | Circuit Diagram and Parts List for the Modified DAS        | B-1 |

|--------------|------------------------------------------------------------|-----|

| APPENDIX C - | Control Program for the Existing Low-Power DAS             | C-1 |

| APPENDIX D - | Control Program for Low-Power DAS Using Error Compensation | D-1 |

| APPENDIX E - | Development of the Track-and-Hold Droop Error Simulation   | E-1 |

| APPENDIX F - | Development of the Comparator Hysteresis Error Simulation  | F-] |

| References   |                                                            | R-] |

## LIST OF FIGURES

|      |                                                                                   |   | page |

|------|-----------------------------------------------------------------------------------|---|------|

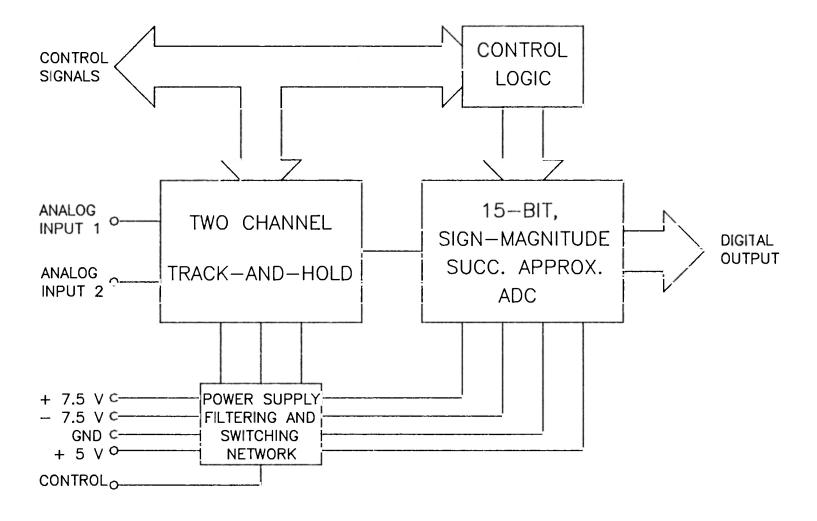

| 1.   | Block Diagram of the Analog Section                                               | • | 5    |

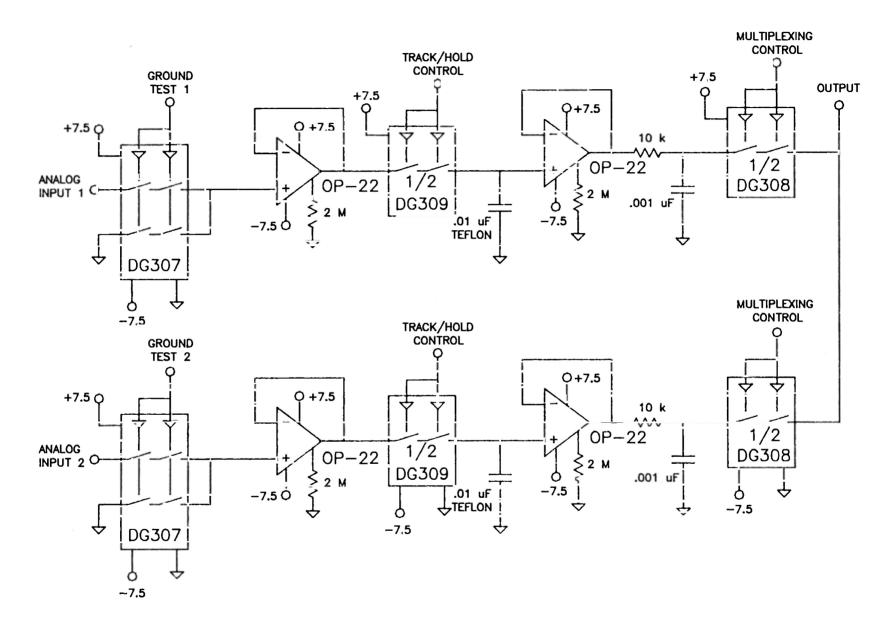

| 2.   | Circuit Diagram of the Track-and-Hold                                             | • | 7    |

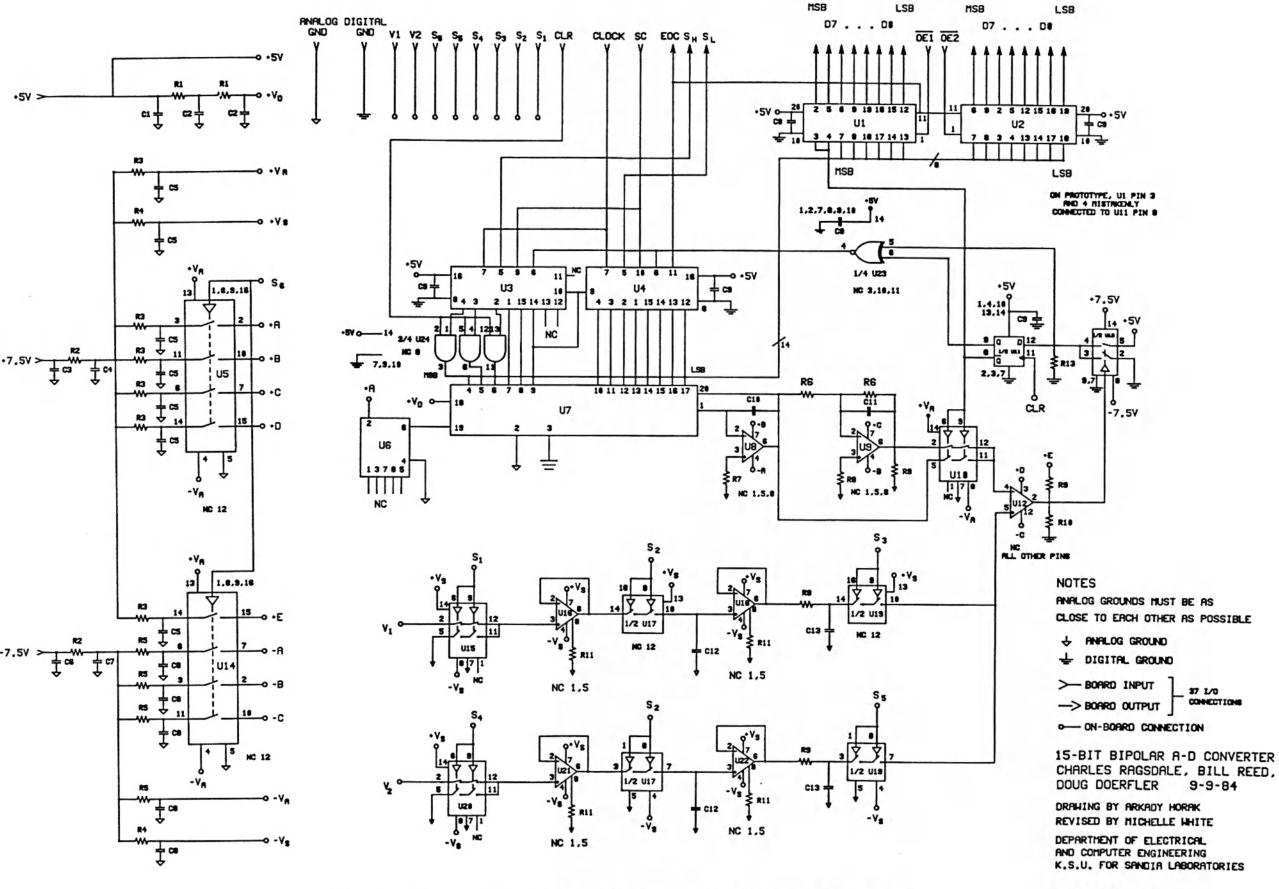

| 3.   | Circuit Diagram of the Successive Approximation ADC .                             | • | 9    |

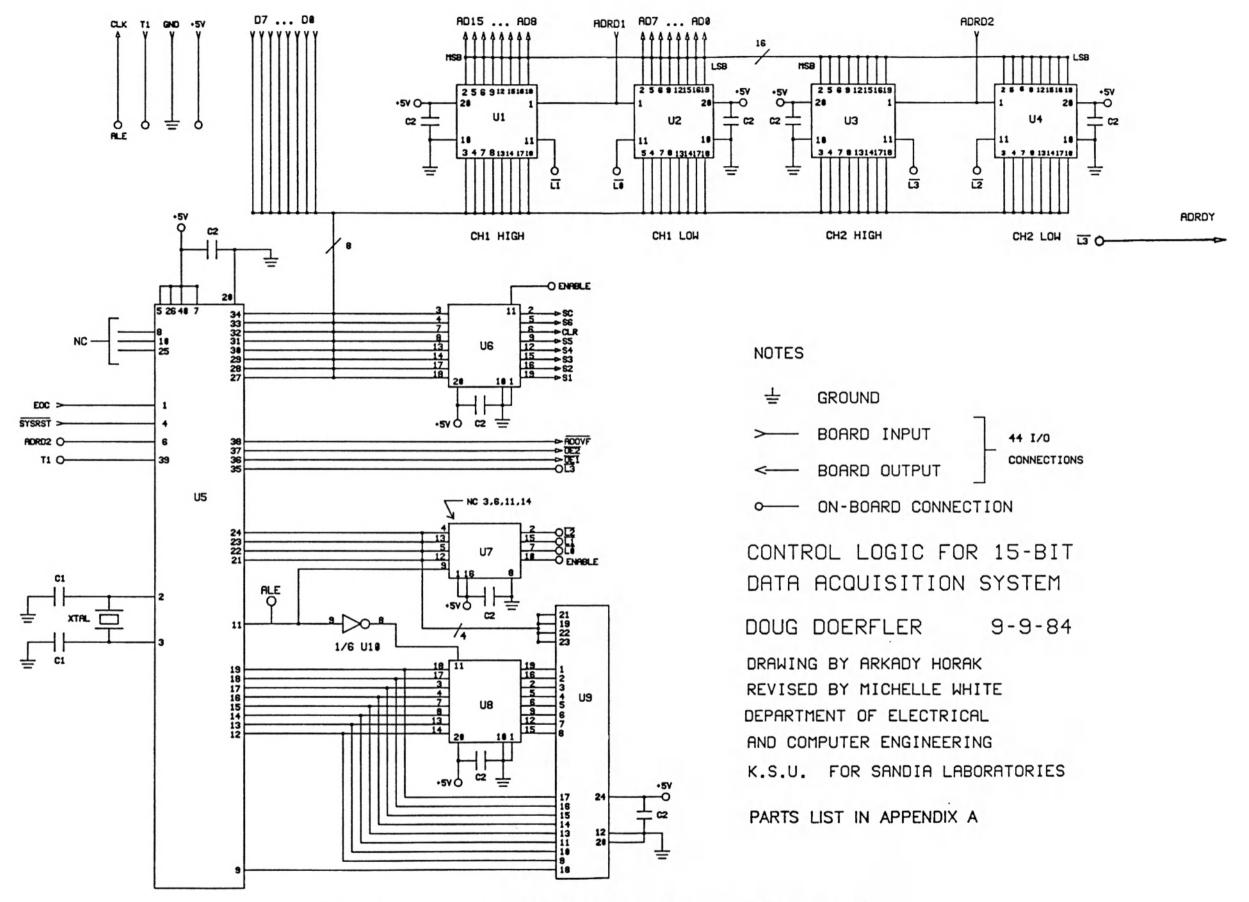

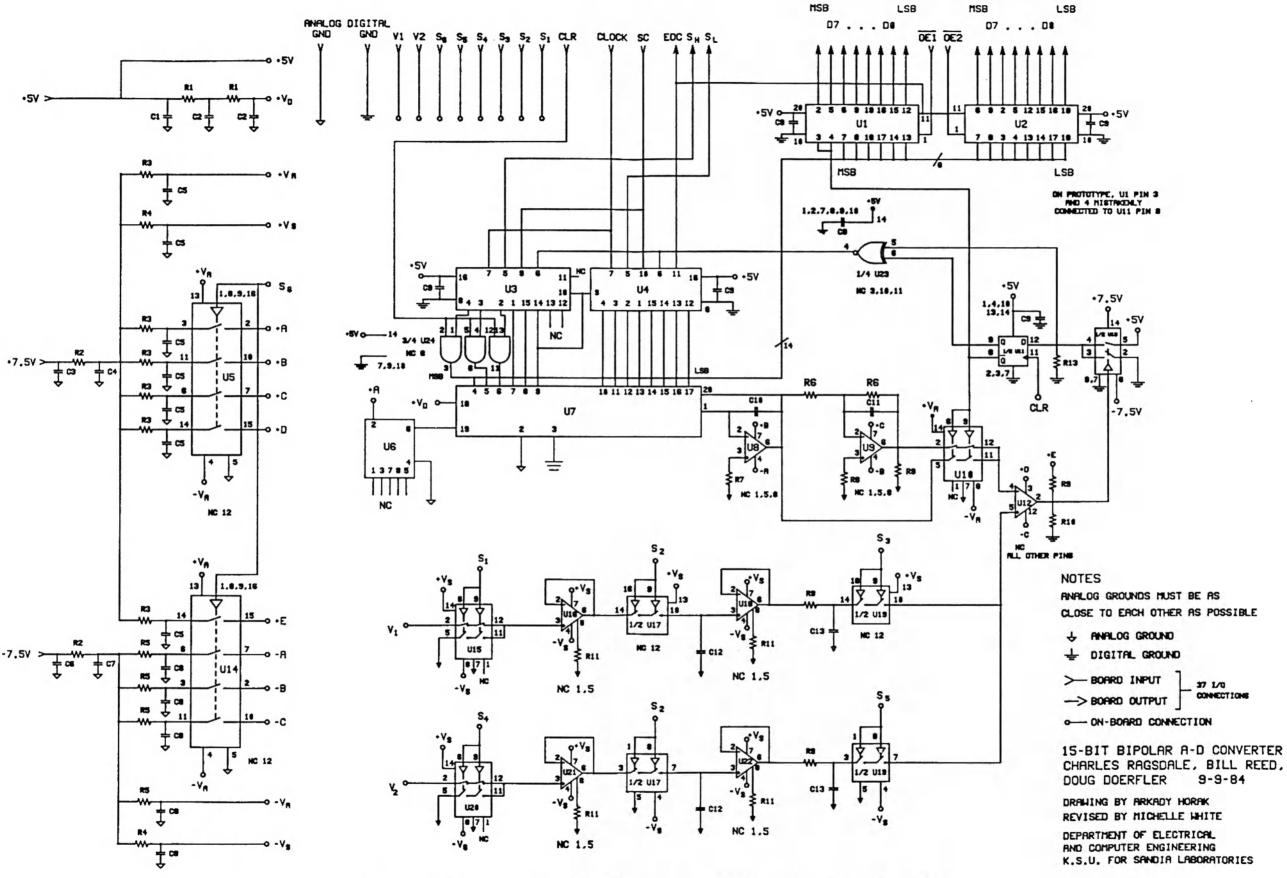

| 4.   | Circuit Diagram of the Control Logic                                              | • | 12   |

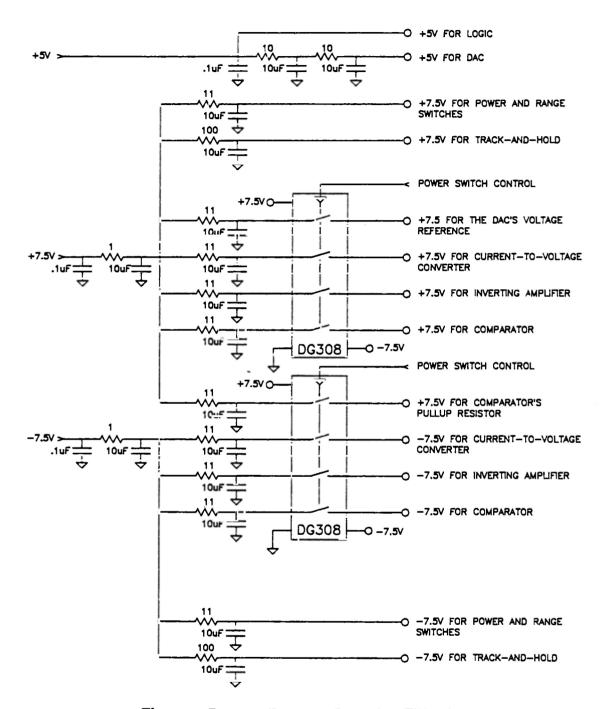

| 5.   | Power Supply Filtering and Switching Network                                      | • | 15   |

| 6.   | Circuit Diagram of the Analog Section                                             | • | 17   |

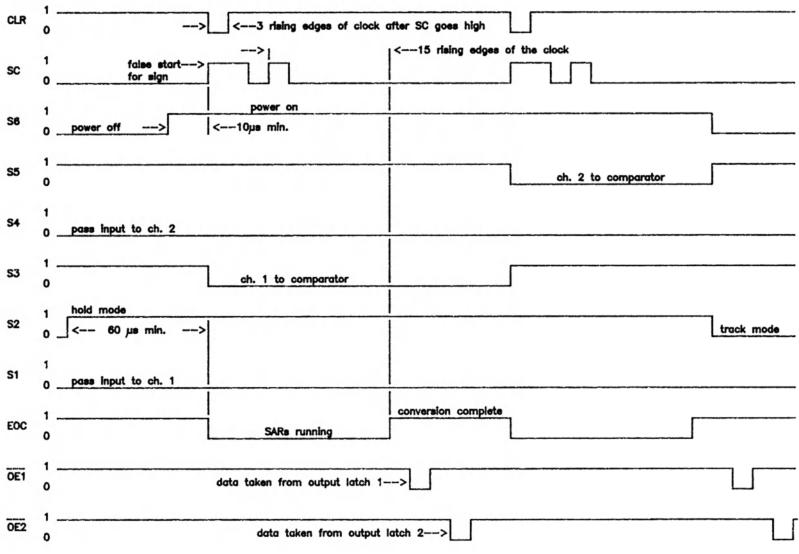

| 7.   | Timing Diagram for the Analog Section                                             | • | 18   |

| 8.   | Circuit Diagram of the Digital Section                                            | • | 22   |

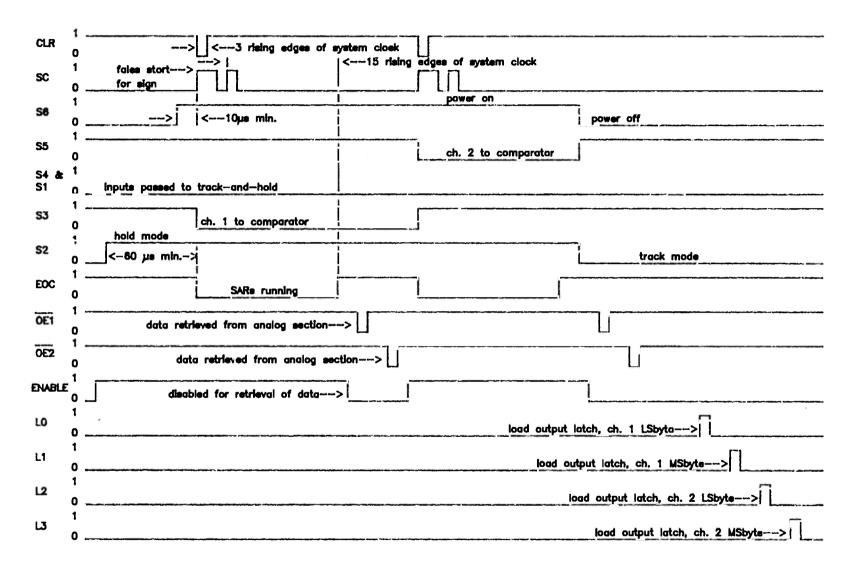

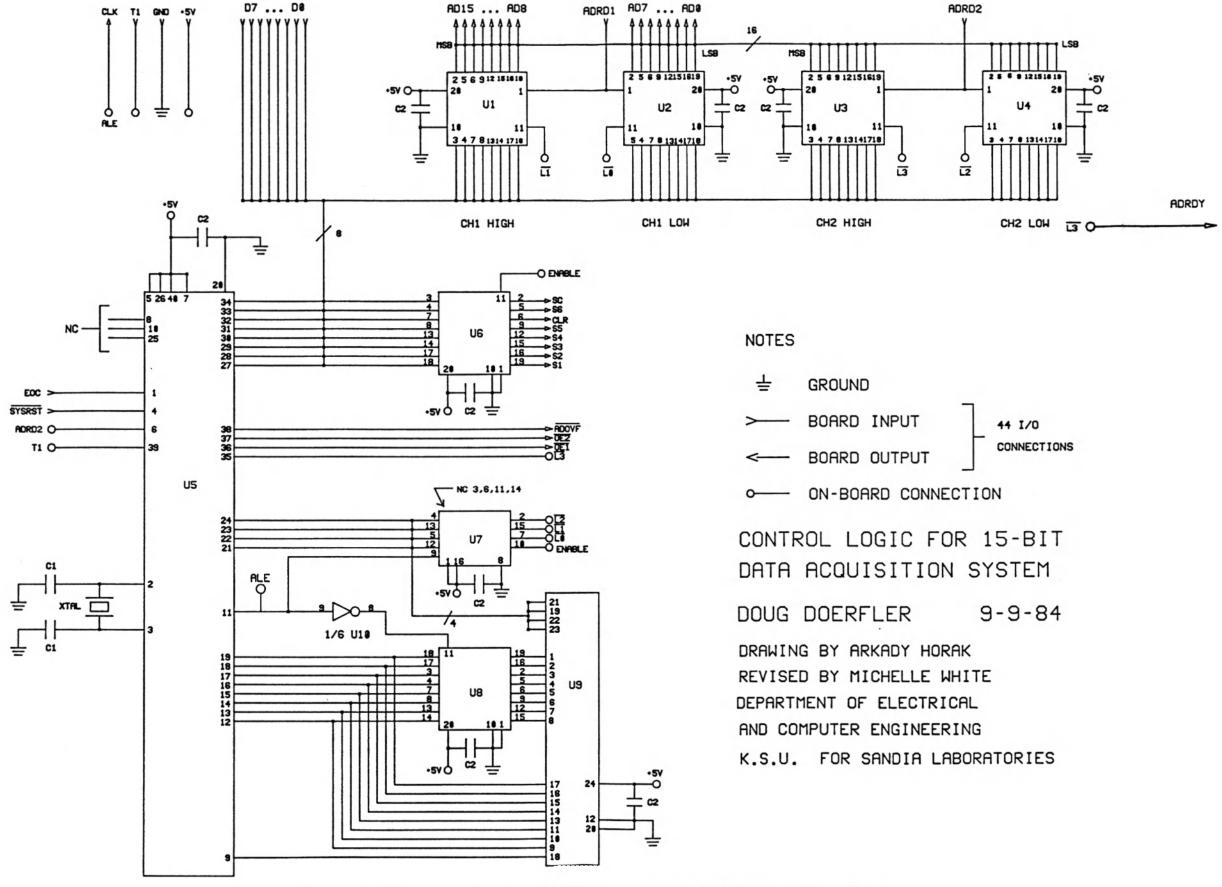

| 9.   | Timing Diagram for the Data Acquisition System                                    | • | 25   |

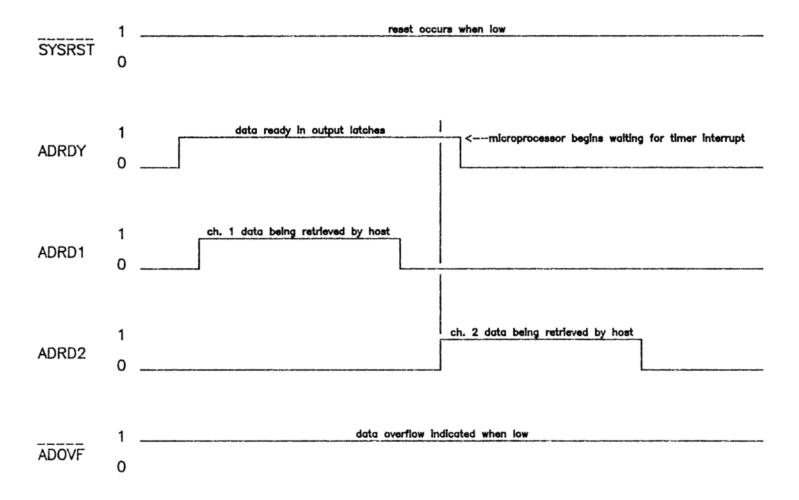

| 10.  | Timing Diagram for an Example Host System Interface .                             | • | 29   |

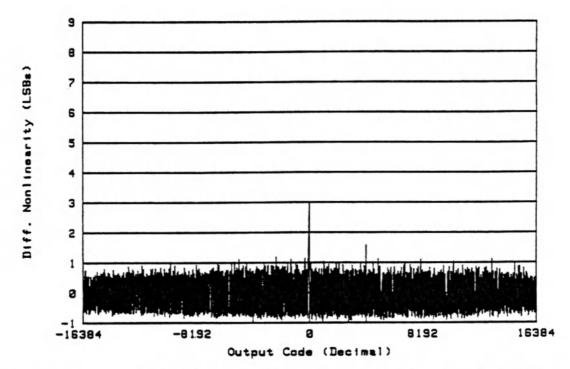

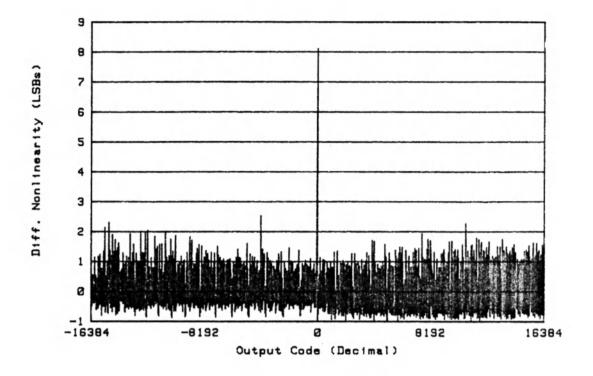

| lla. | Diff. Linearity Error as a Function of Output Code                                | • | 31   |

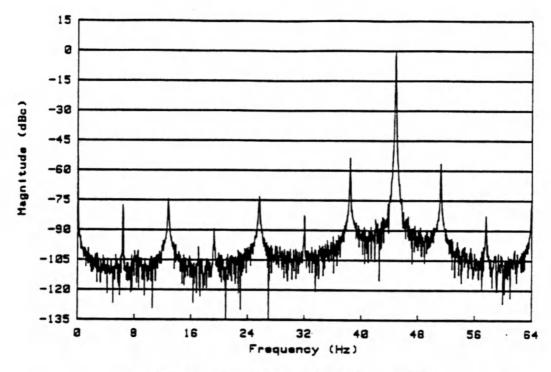

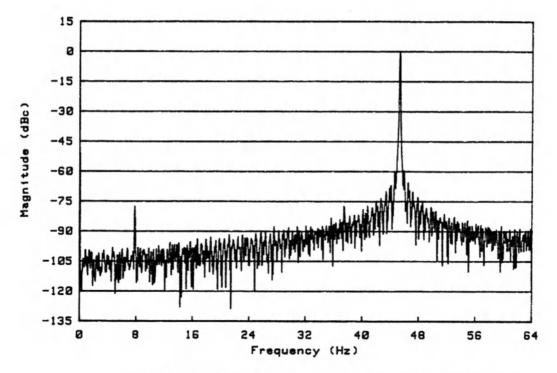

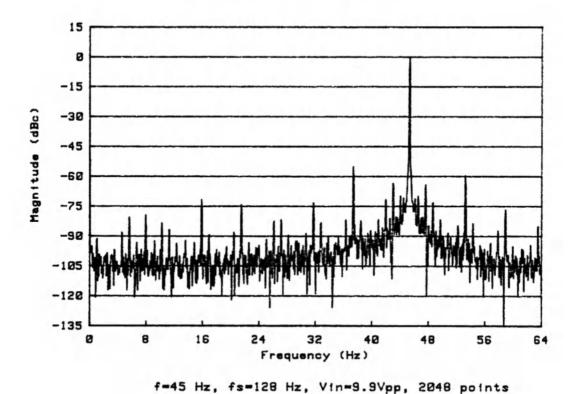

| 11b. | Fourier Transform Test Results for a Bipolar Input                                | • | 31   |

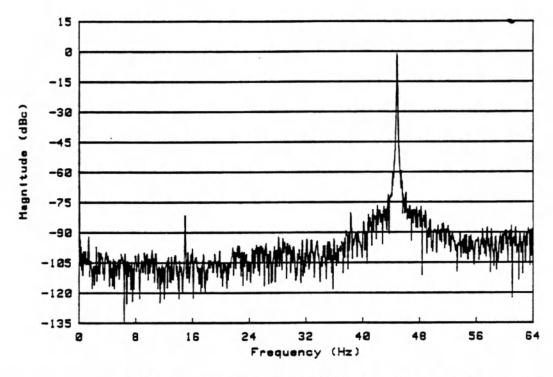

| 12.  | Fourier Transform Test Results for a Unipolar Input .                             | • | 33   |

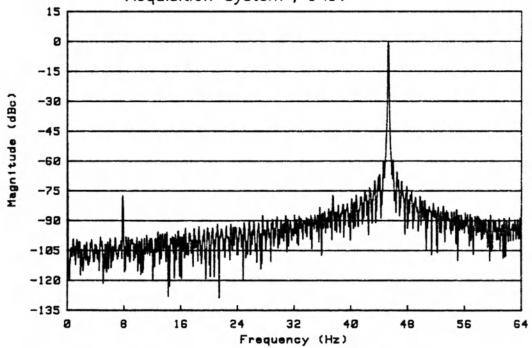

| 13.  | Fourier Transform Test Results for a Bipolar Input (Two channel PC board version) | • | 33   |

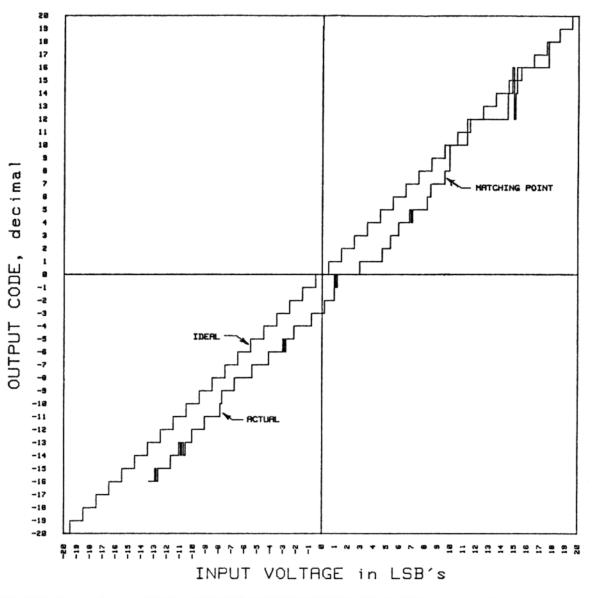

| 14.  | Transfer Characteristic of an ADC with Polarity Range Mismatch                    | • | 36   |

| 15.  | Transfer Characteristic of a Perfect ADC                                          | • | 38   |

| 16.  | Transfer Characteristic of an ADC When its DAC Output is not Offset               | • | 39   |

| 17.  | Results of Track-and-Hold Droop Error Simulation                                  | • | 43   |

| 18.  | Transfer Characteristic of an ADC with Comparator Noise                           | • | 50   |

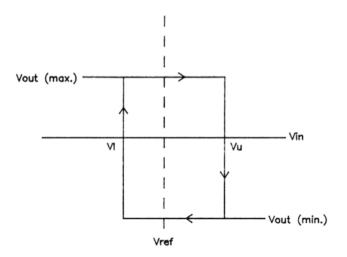

| 19.  | Switching Characteristic of a Comparator with Hysteresis                          | • | 51   |

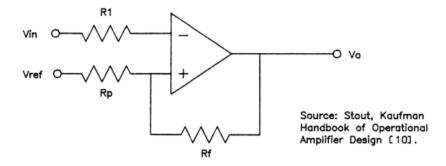

| 20.  | Circuit Diagram for a Comparator with Hysteresis                                  |   | 51   |

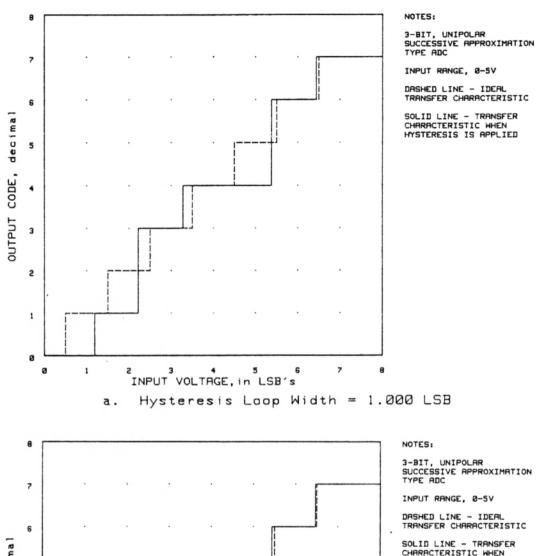

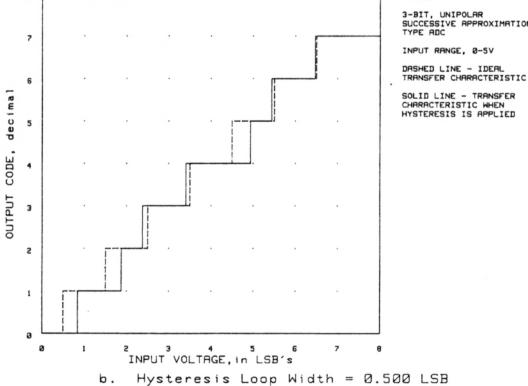

| 21. | Transfer Characteristic of an ADC with Comparator Hysteresis                                            | 53           |

|-----|---------------------------------------------------------------------------------------------------------|--------------|

| 22. | Transfer Characteristic of an ADC with Ranges Offset                                                    | 56           |

| 23. | Transfer Characteristic of an ADC After Correction is Applied                                           | 56           |

| 24. | Resistor Divider Networks Used to Create Polarity Range Offsets                                         | 62           |

| 25. | Modified Control Logic                                                                                  | 63           |

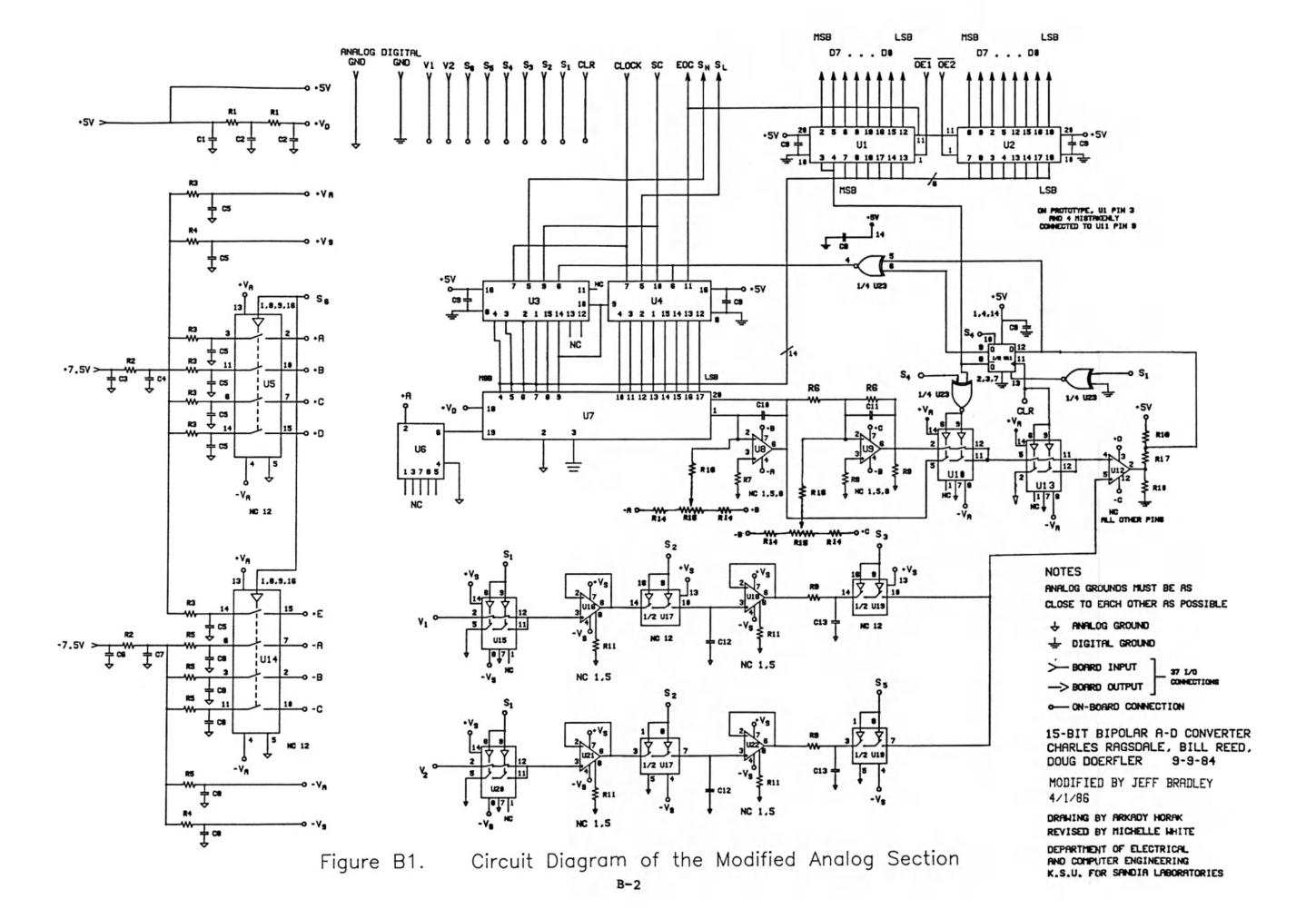

| 26. | Circuit Diagram of the Modified Analog Section                                                          | 64           |

| 27. | Timing Diagram for Obtaining Correction Codes                                                           | 67           |

| 28. | Rough Transfer Characteristic of the Error Compensated DAS Around the Zero Crossing                     | 72           |

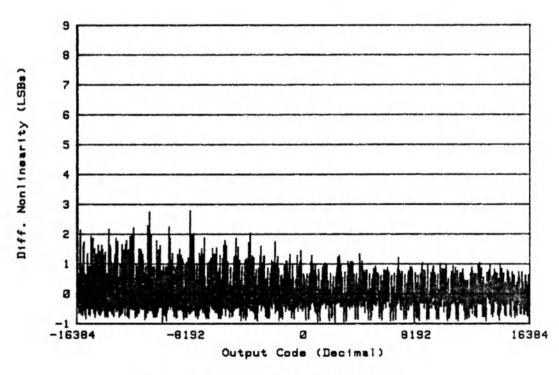

| 29. | Diff. Linearity Error as a Function of Output Code for the Unmodified DAS and the Error Compensated DAS | 73           |

| 30. | Fourier Transform Test Results for a Bipolar Input for the Unmodified DAS and the Error Compensated DAS | 74           |

| Al. | Circuit Diagram of the Analog Section                                                                   | A-2          |

| A2. | Circuit Diagram of the Digital Section                                                                  | A-5          |

| Bl. | Circuit Diagram of the Modified Analog Section                                                          | B-2          |

| El. | Input Voltage Droop for 4-Bit ADC Model                                                                 | E-4          |

| E2. | Results of Track-and-Hold Droop Error Simulation                                                        | E-5          |

| Fl. | Circuit Diagram for a Comparator with Hysteresis                                                        | F-3          |

| F2. | <u>•</u>                                                                                                | F <b>-</b> 3 |

| F3. |                                                                                                         | F-5          |

## SOME FURTHER CONSIDERATIONS IN THE DESIGN AND IMPLEMENTATION OF A LOW-POWER, 15-BIT DATA ACQUISITION SYSTEM

#### Introduction

A need for remote and/or battery powered instrumentation has created a demand for low-power, high-resolution data acquisition systems which are capable of functioning for extended periods of time. Applications for such systems can be found in satellite instrumentation packages, biological field experiments, and oil well logging equipment. Over the past several years, a low-power data acquisition system (DAS) has been developed by the Department of Electrical and Computer Engineering at Kansas State University.

The low-power DAS will simultaneously sample two analog voltage signals (within a ± 5 V range) and perform a 15-bit analog-to-digital conversion on both sampled inputs. The analog-to-digital conversion is performed by a sign-magnitude, successive approximation type analog-to-digital converter. For the application that the DAS was designed, the sampling rate is 128 samples/second for each of two channels. Control of the DAS is performed by a microprocessor. The presence of the microprocessor also gives the DAS the capability to do some of its own data processing and error correction. The calculated power consumption for the DAS at the 128 samples/second rate is 36.5 mw.

Since the development work on the DAS was done by several graduate students at KSU over a period of several years, the

documentation is somewhat fragmented. The purpose of this thesis is to present an overview of the DAS, and to analyze and suggest solutions to several error sources that are inherent in the design. The overview will serve to tie together previous work, (both documented and undocumented), and to form a background for the analysis. The analysis will point out the major sources of error in a prototype DAS and show how the microprocessor can be used to null out some of the errors.

The following topics are covered in this thesis and are presented in the order shown:

- \* A review of the existing low-power DAS hardware

- Inherent error sources in the low-power DAS

- A microprocessor-based error compensation technique

- · Recommendations for future implementations of the DAS

Coverage of related material and software listings are left to the appendices. It is assumed that the reader is acquainted with the successive approximation technique of analog-to-digital conversion and with the terminology related to the specification of analog-to-digital converters.

#### CHAPTER 1. REVIEW OF THE EXISTING LOW-POWER DAS HARDWARE

#### Introduction

This section reviews the existing hardware of a low-power data acquisition system (DAS). The initial design requirements for the DAS were:

- 1. conversion by successive approximation technique

- 2. 15-bit resolution

- 3. maximum differential linearity error of  $\pm 1/2$  LSB

- 4. maximum integral linearity error of ± 1 LSB

- 5. no missing codes

- 6. bipolar input voltage range, ± 5 V

- 7. maximum input frequency of 45 Hz

- 8. two analog input channels

- 9. two conversions (one per channel) every 1/128 sec.

- 10. digital output data in two's-complement form

- 11. microprocessor control

- 12. power supply voltages of + 7.5 VDC

- 13. power consumption of less than 80 mW (analog section)

The hardware consists of two parts: 1) an analog section consisting of a two channel track-and-hold and a 15-bit successive approximation type analog-to-digital converter (ADC), and 2) a digital section consisting of a microprocessor controller and supporting digital hardware. The analog section performs the

sampling and digitizing of two analog input signals. The digital section performs the control and data manipulation functions of the DAS and provides an interface between the analog section and a more general purpose host computer system.

The analog section is reviewed first. Next the digital section is reviewed. Finally, the performance of a single channel prototype DAS is reported, and briefly compared to that of a PC board version of the DAS.

The successive approximation type ADC was designed by Ragsdale. The two channel track-and-hold was designed by Reed. The control logic and microprocessor controller were designed by Doerfler. The methods for testing the prototype DAS were also developed and implemented by Doerfler.

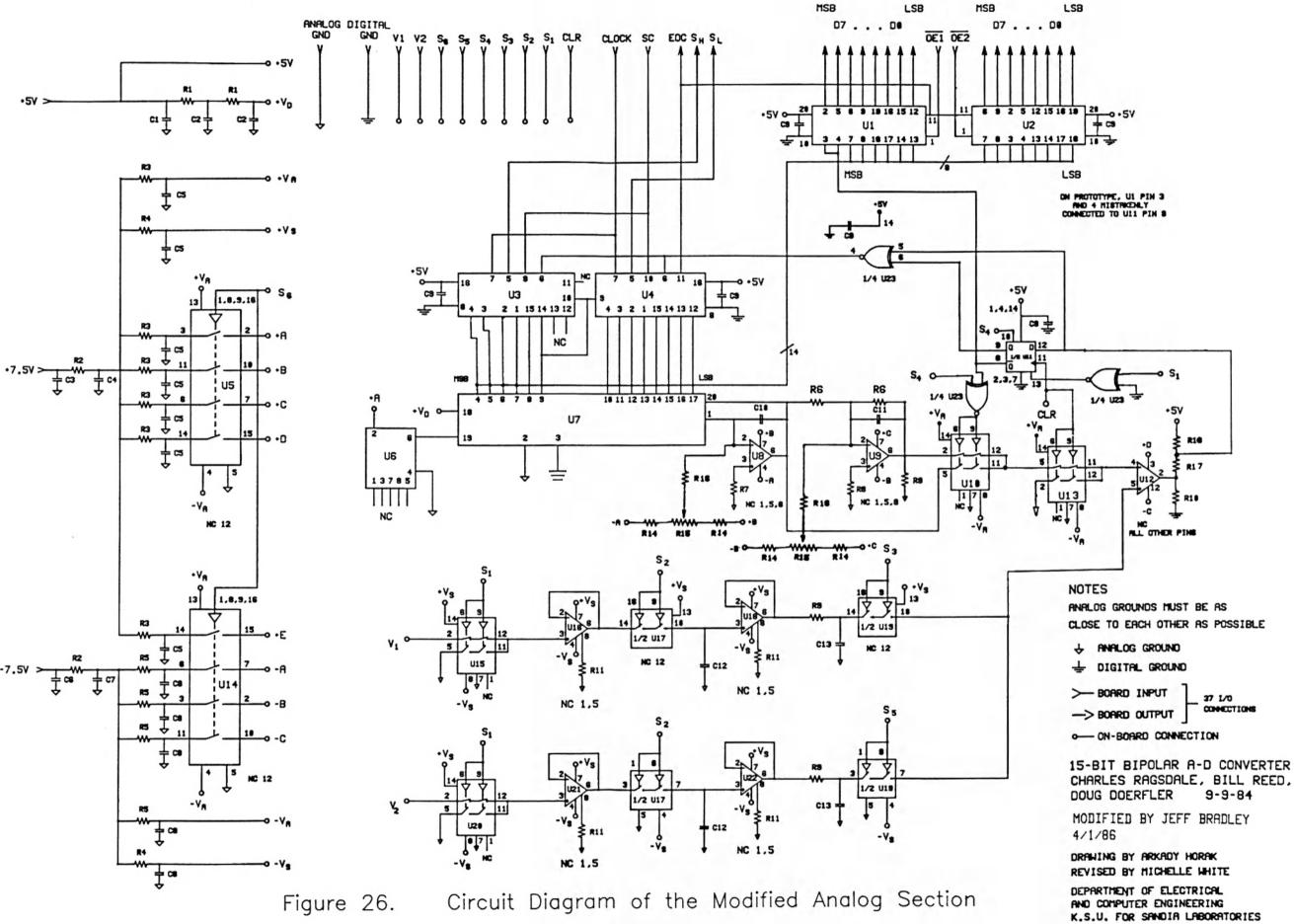

## Analog Section

The analog section of the low-power DAS consists of two major blocks, as shown in the block diagram, Figure 1: 1) a two channel track-and-hold, and 2) a 15-bit successive approximation type ADC. Two supporting blocks are also included in the analog section. These are the control logic and a power supply filtering and switching network. The following sub-sections discuss each of these blocks. A discussion of the theory of operation of the complete analog section is also given.

#### Two Channel Track\_and\_Hold

An open-loop voltage follower track-and-hold design is used in the low-power DAS. The advantages offered by this design are

Figure 1. Block Diagram of the Analog Section

simplicity and stable performance. Since the DAS's application requires two input channels, two identical track-and-holds are placed in parallel. Their outputs are multiplexed so that the ADC can perform a separate conversion on each sampled input. The track-and-hold timing and multiplexing are handled by the microprocessor controller.

A circuit diagram of the two channel track-and-hold is shown in Figure 2. Several other features of the circuit should be noted. The inputs to the track-and-hold can be grounded so that the ADC can perform a ground test. Switches are cascaded to improve the off-isolation between the input and output. Also, a low-pass filter is used on the output of each track-and-hold channel to reduce output noise. The measured power consumption for the entire track-and-hold circuit is 3.28 mw.

Although a detailed discussion of the two channel track-and-hold can be found in Reed,<sup>2</sup> a few comments about the track-and-hold components are given here. The Precision Monolithics (PMI) OP-22 programmable micropower operational amplifiers were chosen for this application for their low power consumption, low offset voltage, high gain, and high CMRR. The Siliconix DG309 switch used for selecting the track/hold mode was chosen for its low power consumption, small gate-to-drain capacitance, and small charge transfer. Teflon capacitors are used for the hold capacitors and were chosen for their low dielectric absorption.

#### Successive Approximation ADC

The successive approximation type ADC that is used in the low-power DAS is designed to provide 15-bit resolution over a

7

Figure 2. Circuit Diagram of the Track—and—Hold

± 5 V range. Operation of the ADC is handled by the microprocessor controller. The digital output data can be delivered to the microprocessor in either serial or parallel format. Low power consumption is achieved by turning off (power-switching) several of the components of the ADC when the conversion process is not taking place.

In this implementation, a unipolar 14-bit ADC is forced to act as a bipolar 15-bit ADC. This is done by first determining the polarity of the sampled input signal, and then performing a 14-bit conversion in the proper polarity range. The result of the 14-bit conversion represents the magnitude of the sampled input signal. The 15th bit (MSB) represents the polarity, or sign. This ADC therefore determines the digital output data in signmagnitude form.

A circuit diagram of the successive approximation type ADC is shown in Figure 3. The heart of the ADC is the Datel Intersil DAC-HAl4B 14-bit digital-to-analog converter (DAC). This DAC was chosen for its very low power consumption, wide supply voltage range, and rapid settling time. The last characteristic makes this DAC very useful in a power-switched application. A stable + 5 V reference for the DAC is provided by a PMI REF-02 precision voltage reference.

Digital data is delivered to the DAC by the successive approximation registers (SAR). Two 8-bit SARs are cascaded to form the 14 bits needed by the DAC. The SARs execute and control the binary search algorithm that is characteristic of the successive approximation technique. Once the SARs are started by the microprocessor controller, they automatically execute the binary

Figure 3. Circuit Diagram of the Successive Approximation ADC

search at a rate determined by the microprocessor provided system clock.

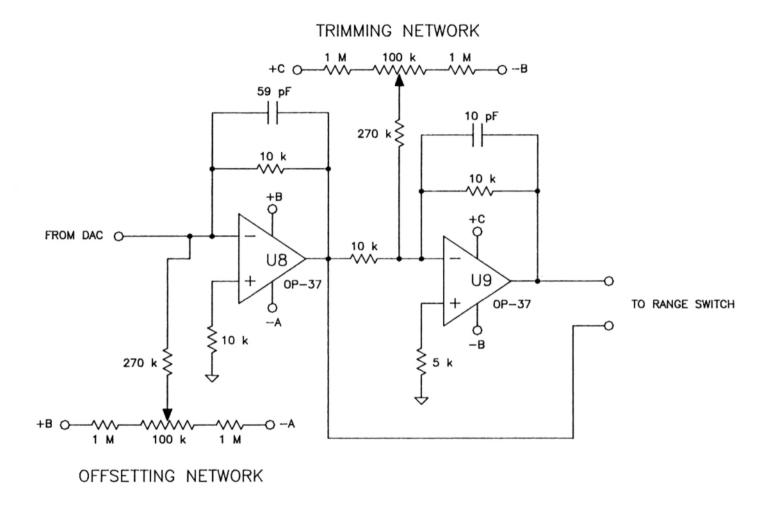

The current output of the DAC is converted to a negative voltage by a current-to-voltage circuit based on a PMI OP-37 precision high-speed operational amplifier. If the polarity of the sampled input signal voltage is negative, then the output of this op-amp is compared to the sampled input directly. If the polarity of the sampled input signal is positive, then the output of the current-to-voltage circuit is inverted by an inverting amplifier circuit also based on the OP-37. The output of the inverting amplifier is then compared to the sampled input. Feedback capacitors are included in both op-amp circuits to decrease their settling time. The OP-37 op-amp was chosen for its relatively low power consumption, high gain, high gain-bandwidth product, high slew rate, rapid settling time, and low offset voltages and currents.

A PMI CMP-04 low-power precision comparator makes all voltage comparisons for the determination of input signal polarity and for the binary search procedure. The CMP-04 was chosen for its low power consumption, high gain (high resolution), high CMRR, and rapid small signal response time. The output of the comparator is used by the SARs (after manipulation by control logic) to determine whether the bit being tested should be left set or should be reset.

As mentioned before, the digital output data can be delivered to the microprocessor controller in either serial or parallel format. If the data is to be delivered serially, then the bits are sent by the SARs to the microprocessor as they are

determined. If the data is to be delivered in parallel, then all bits are latched into a separate buffer at the end of the binary search. In this application, the output data is sent to the microprocessor in parallel format.

Several components of the ADC are power-switched to conserve power. These components are the REF-02 voltage reference, the OP-37 op-amps, and the CMP-04 comparator. Each of the power-switched components was carefully selected to gain the greatest benefit from power-switching. Their high performance, relatively low power consumption, and short turn-on settling time are all desirable characteristics for use in a power-switched mode. For this application, the sampling period is 1/128 s. Since the actual conversion process takes a small portion of this time, the power for these components can be turned off for most of the sampling period. For a sampling period of 1/128 s, the duty cycle for these components is roughly 15%. Obviously power-switching yields a significant savings in power consumption when the duty cycle is this low.

A detailed analysis of the design of the low-power, 15-bit successive approximation ADC can be found in Ragsdale.

## Control Logic

Very little control logic is required in the analog section.

The logic performs two functions: 1) assisting the microprocessor controller in the determination of the input signal

polarity, (sign bit), and 2) setting up the ADC to make the 14bit magnitude determination in the proper polarity range. The

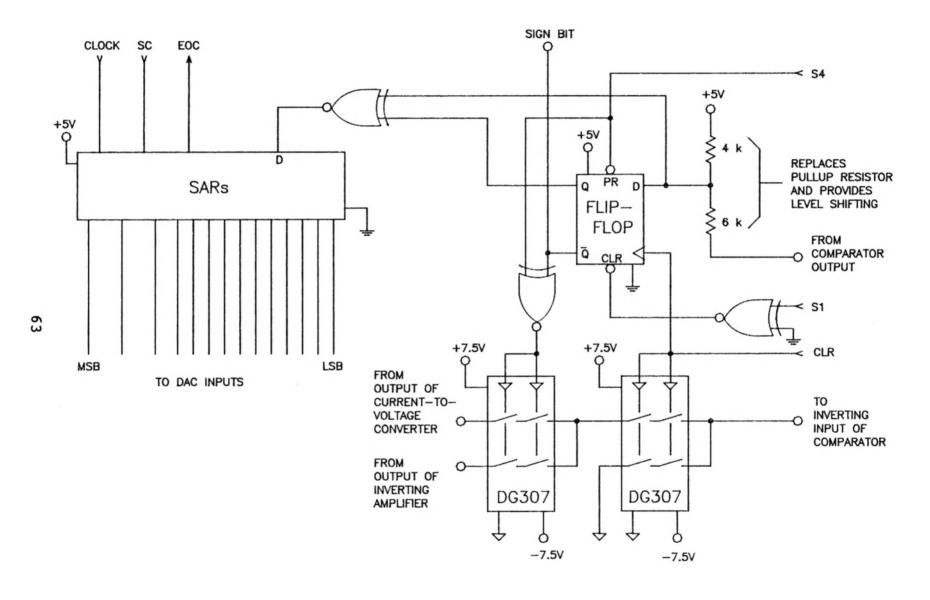

control logic is shown in Figure 4. Note that the SARs and the

Figure 4. Circuit Diagram of the Control Logic

switch on the outputs of the OP-37 op-amps, which were shown previously in Figure 3, are also shown here for clarity. Also, in the following text, a logic high is represented as a "1" and a logic low is represented as a "0".

During the determination of the sign bit, a 0 V reference is needed at the inverting input of the comparator. To accomplish this, a 00...00 code is required at the DAC input. However, the SARs are not able to deliver a 00...00 code on demand. To get around this problem, the SARs are "false started" and all bits that might be set to a "1" by the SARs during the sign determination period are forced to "0". This is done with three 74C08 AND gates and the CLR line from the microprocessor controller. Setting the CLR line to "0" causes the output of the AND gates to be "0" regardless of the level of the other inputs.

A Siliconix DG307 analog switch is used as a level shifter to convert the + 7.5 V and - 7.5 V comparator output to + 5 V and 0 V logic levels respectively. The 74C74 D flip-flop is used to store the sign bit that results from the input signal polarity determination, and to set up the ADC for the magnitude determination. After the sign bit is stored, the Q output of the flip-flop and a 74HC266 exclusive NOR gate are used to provide the correct logic levels to the D inputs of the SARs. For magnitude determination in the positive range, the logic levels required at the D inputs of the SARs are a "1" if the comparator output is + 7.5 V and a "0" if the comparator output is a - 7.5 V. For magnitude determination in the negative range, the required logic levels are reversed. The Q output of the flip-flop is used to select the proper OP-37 op-amp output for the

magnitude determination. If the sampled input signal is a negative voltage, the output of the current-to-voltage converter circuit is selected. If the sampled input signal is a positive voltage, the output of the inverting amplifier circuit is selected. The  $\overline{\mathbb{Q}}$  output of the flip-flop is also made available to the output latches of the analog section for use as the two most significant bits, or sign bits.

#### Power Supply Filtering and Switching Network

The power supply filtering and switching network is shown in Figure 5. Power supply filtering is required for the analog section to reduce the effects of system noise on the conversion accuracy. This noise comes from the operation of both the digital and analog components of the DAS. A three-pole low-pass filter is placed between the external power supply and each analog component; a two-pole low-pass filter is placed between analog components.

Several components of the ADC are power-switched to reduce their power consumption. Switching is performed by analog switches (Siliconix DG308) under microprocessor control. More detail on the power supply filtering and switching network can be found in Ragsdale. 1

## Theory of Operation. Analog Section

A step-by-step example of the analog section's operation is given here. The example will cover one conversion cycle (conversions performed on both inputs). The digital output data will be in parallel format, and will be taken from the analog board in

Figure 5. Power Supply Filtering and Switching Network

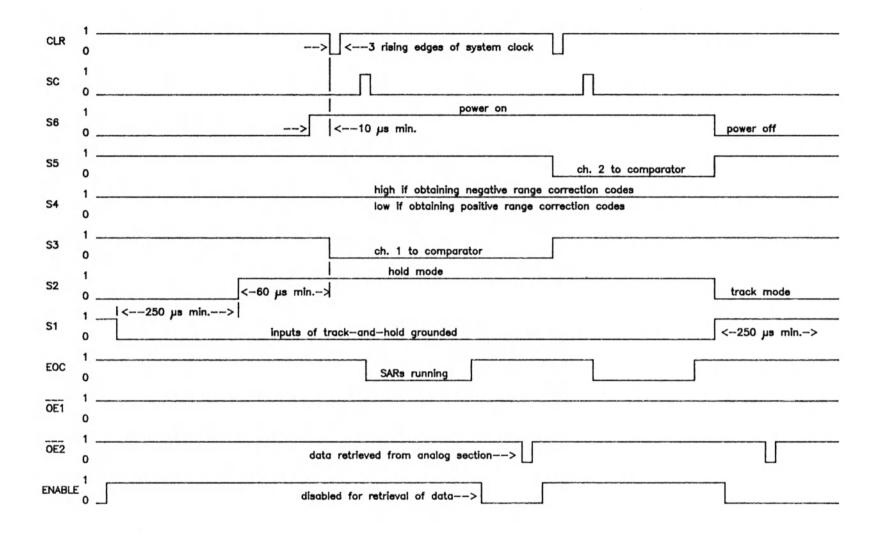

two bytes. Also, in the following text a logic high will be represented as a "l" and a logic low will be represented as a "0". The reader should refer to the circuit diagram for the complete analog section, Figure 6, and the accompanying timing diagram, Figure 7, while reading this section.

The microprocessor controller is required to provide ten control signals plus a clock signal to the analog section. The control signals are:

- 1.  $S_1$  ground test control for input channel 1

- 2. s<sub>2</sub> track/hold mode control for the track-and-hold

- 3.  $S_3$  multiplexing control for input channel 1

- 4. SA ground test control for input channel 2

- 5. Sr multiplexing control for input channel 2

- 6. S6 power-switching control

- 7. SC start conversion control

- 8. CLR sign determination control

- 9. OEl latch output enable, most significant byte

- 10. OE2 latch output enable, least significant byte

In return, the analog section provides the microprocessor with an end-of-conversion flag (EOC), two serial data lines ( $S_{\rm H}$  and  $S_{\rm L}$ ), and sixteen parallel data lines. Since the output data will be in parallel format for this example,  $S_{\rm H}$  and  $S_{\rm L}$  will be ignored here. Information on their use can be found in the literature.

Before a conversion cycle begins, the control signals are in the following states (see page 19):

Figure 6. Circuit Diagram of the Analog Section

PARTS LIST IN APPENDIX A

Figure 7. Timing Diagram for the Analog Section [5]

- 1.  $S_1 = 0$ , input signal passed to channel 1

- 2. S2 = "0", track-and-hold in track mode

- 3.  $S_3 = "1"$ , channel 1 cut off from ADC

- 4.  $S_A = "0"$ , input signal passed to channel 2

- 5.  $S_E = "1"$ , channel 2 cut off from ADC

- 6.  $S_6 = "\bar{u}"$ , power off

- 7. SC = "0", SARs waiting for the start signal

- 8. CLR = "1", normal state for the CLR line

- 9.  $\overline{OE1} = "1"$ , latch outputs in high impedance state

- 10. OE2 = "1", latch outputs in high impedance state

The track-and-hold's buffer amplifiers Ul6 and U21 and the hold capacitors Cl2 are tracking the input signals. The ADC is in a quiescent state.

The conversion cycle is started by setting  $S_2$  to "1". This puts both channels of the track-and-hold in the hold mode. The track-and-hold must then be allowed to settle for a minimum of 60  $\mu$ s. Next the power for the power-switched components is turned on by setting  $S_{\ell}$  to "1". The power-switched components are then allowed to settle for a minimum of 10  $\mu$ s.

After the input signals have been sampled and the power to the ADC has been switched on, the polarity (sign) determination process begins. Several things now happen simultaneously.  $S_3$  is set to "0", allowing the sampled signal from channel 1 to pass to the ADC's comparator. SC is set high, signalling the SARs to begin a conversion. This is the "false start" that was mentioned before in the Control Logic section. In response, the SARs set the EOC line to "0" and begin their usual binary search.

However, as discussed before, it is desired that the digital input to the DAC be 00...00 during the sign determination. This is accomplished by setting the CLR line to "0" at the same time that the SC line is set to "1".

During the sign determination process the sampled input is compared to a 0 V reference (ideally). The reference is taken from either the output of op-amp U8 or the output of op-amp U9, depending on whether the polarity of the last conversion was positive or negative. The comparator outputs + 7.5 V if the sampled signal is positive with respect to the reference or - 7.5 V if the sampled signal is negative with respect to the reference. These outputs are shifted to + 5 V and 0 V respectively.

The sign determination process is completed by setting the CLR line to "1". The shifted output of the comparator is latched into the flip-flop Ull by the rising edge of the CLR signal. A "1" is latched if the sampled input is positive; a "0" is latched if the sampled input is negative. Finally SC is set to "0" in preparation for the magnitude determination.

The magnitude determination is started by a pulse on the SC line. The conversion of the rest of the 14 bits now proceeds in the usual fashion for a unipolar 14-bit successive approximation converter with a 5 V span. The ADC is set up for the proper polarity range by the outputs of flip-flop Ull, as was discussed in the Control Logic section. The SARs automatically control the binary search.

When the conversion is finished the SARs set EOC to "1".

The rising edge of EOC clocks the output latches, causing the

results of the conversion to be held in the latches. The microprocessor controller is then free to retrieve the data from the output latches of the analog section. First the  $\overline{OE1}$  line is set to "0", enabling the outputs of latch Ul. The most significant byte of the data can then be read. After reading the first byte,  $\overline{OE1}$  is returned to "1". Data is retrieved from latch U2 in a similar manner, using the  $\overline{OE2}$  line to enable the outputs of U2. Conversion of the sampled signal from channel 1 is now complete.

To begin the conversion of the sampled signal from channel 2,  $S_3$  is set to "1" to cut off channel 1 from the comparator and  $s_5$  is set to "0" to pass the sampled signal from channel 2 to the comparator. The conversion of the sampled signal from channel 2 then proceeds in the same manner as described before for channel 1. At the end of the conversion,  $S_6$  is set to "0" to turn the power to the ADC off and  $s_2$  is set to "0" to put the two channel track—and—hold back into the track mode. The data for channel 2 is then retrieved from the analog section as described before. The two channel conversion cycle is now complete.

## Digital Section

The digital section of the low-power DAS consists of a microprocessor controller and supporting digital hardware, as shown in the circuit diagram, Figure 8. The digital section performs two functions. The first function is to control the analog section. The second function is to provide an interface between the analog section and a host computer system.

The digital section's components and theory of operation are

Figure 8. Circuit Diagram of the Digital Section

discussed in the following sub-sections. A discussion of the interfacing requirements for connection to a host computer system is also given.

#### Microprocessor Controller

The microprocessor used in the digital section is the Intel 80C39 CHMOS Single-Component 8-bit Microcomputer. The 80C39 is a low-power version of the Intel 8039 and is a component in the MCS-48 family. In addition to the CPU, the 80C39 has a 128 x 8 RAM, 27 I/C lines, and an 8 bit timer/counter on board. The 80C39 also provides a system clock for memory timing and other uses, at a frequency that is 1/15 of the crystal oscillator frequency. The low power consumption of the 80C39 makes this microprocessor ideal for battery powered operation. Near optimum power consumption for the combination of the analog and digital sections is achieved with a crystal oscillator frequency of 1 MHz. A 1 MHz crystal was chosen for its availability.

Twenty-four of the I/O lines are arranged into three 8-bit bidirectional ports, called BUS, PORT1, and PORT2. In this application, BUS is used as an address/data bus for an EPROM. PORT1 is used for sending control signals to the analog section, retrieving data from the analog section's output latches, and sending data to the digital section's output latches. PORT2 is used for controlling the latches on both the digital and analog sections, and for addressing the EPROM mentioned before.

The reader should refer to the literature for more specific information regarding the 80C39.7

## Supporting Digital Hardware

The 80C39 is supported by six 8-bit latches, one 4-bit latch, and a 32K-bit UV-erasable EPROM. All supporting hardware is CMOS to reduce power consumption. The EPROM, a 27C32, contains the program for the DAS's operation. Four of the 8-bit latches, (Ul - U4), are used for holding the two 16-bit data words that have resulted from a conversion cycle. These data words are available to the host computer system. One of the 8-bit latches, (U6), is used to hold the ADC's control signals while the 80C39 is using PORT1 for data transfer. The last 8-bit latch, (U8), is used for holding the lower eight bits of the EPROM's address while the BUS is being used to retrieve instructions from the EPROM. The 4-bit latch, (U7), is used for holding four of the latch control signals while the lower four bits of PORT2 are being used as the upper four address lines for the EPROM.

#### Theory of Operation. Digital Section

A step-by-step example of the digital section's operation is given here. This example will parallel the one given previously for the analog section. Again, a logic high will be represented as a "1" and a logic low will be represented as a "0". The reader should refer to the circuit diagram for the digital section, Figure 8, the circuit diagram for the analog section, Figure 6, and the timing diagram, Figure 9. The assembly language software for this example can be found in Appendix C.

In addition to the ten control signals listed before in Theory of Operation, Analog Section, the microprocessor provides

Figure 9. Timing Diagram for the Data Acquisition System [5]

five other control signals which are used within the digital section. They are:

- 1. ENABLE latch enable for U6, ADC control signals

- 2. L0 latch enable for U2, output data latch, channel 1, least significant byte

- 3. Ll latch enable for Ul, output data latch, channel l, most significant byte

- 4. L2 latch enable for U4, output data latch, channel 2, least significant byte

- 5. L3 latch enable for U3, output data latch, channel 2, most significant byte

These five control signals, plus  $\overline{\text{OE1}}$  and  $\overline{\text{OE2}}$ , are assigned to PORT2. The remaining eight control signals for the ADC are assigned to PORT1.

The microprocessor begins a conversion cycle by setting up its internal timer/counter to generate an interrupt at the beginning of the next conversion cycle. The timer/counter then runs by itself in the background while the microprocessor takes care of its duties. The microprocessor next sets ENABLE to "1" to allow the ADC control signals to pass through the latch U6.

After enabling latch U6, the microprocessor executes the control sequence described before in Theory of Operation, Analog Section. However, before the microprocessor can retrieve the data from the analog section, the latch U6 must be disabled by setting ENABLE to "0". This is done so that the control signals presently occupying PORT1 are not corrupted by the incoming data, which must also use PORT1. The data is retrieved in two 8-bit bytes as explained before. The two bytes are temporarily stored in RAM and the control signals for the ADC are reinitialized on

PORT1. Then the latch U6 is enabled again and the conversion cycle continues for channel 2 as described before.

When the conversion process for channel 2 is complete and the analog board has been returned to the quiescent state, latch U6 is disabled. The data is retrieved from the analog section again and temporarily stored in RAM. At this point the microprocessor is free to perform any processing on the data that is required. In this application the microprocessor must convert the sign-magnitude data into 2's complement form.

After the processing is done, the resulting data can be loaded into the four output latches, a byte at a time, through PORT1. A byte of data is loaded into an output latch by first setting its latch enable to "1", sending the data out through PORT1, and then setting the latch enable to "0". This is done for each of the four data bytes. Latch U3 must be loaded last, since its latch enable, L3, is also used to signal the host computer that data is present in the output latches. After the data has been loaded into the latches, the host system can retrieve the data from the output latches, either with or without handshaking.

At this point, the digital section is finished with its duties for the present conversion cycle. The microprocessor now waits in a loop until the timer/counter interrupts to signal the beginning of the next conversion cycle.

#### Interfacing with a Host System

To a host computer system, the DAS appears as a peripheral with a 16-bit data port and six control lines. The control lines

are:

- ADRDY flag signalling that data is present in the output latches, output from the digital section

- 2. ADRD1 output enable for latches Ul and U2, input to the digital section

- 3. ADRD2 output enable for latches U3 and U4, and flag signalling that data has been received, input to the digital section

- 4. Tl arbitrary flag, input to the digital section

- 5. SYSRST reset for the DAS, input to the digital section

- 6. ADOVF flag signalling data overflow, output from the digital section

Passage of data from the DAS to the host system can be accomplished with or without handshaking.

An example interfacing scheme is given here. It involves passing two 16-bit data words using partial handshaking. Refer to the timing diagram, Figure 10.

The digital section first signals the host system that data is present in the output latches by setting ADRDY (L3) to "1". The host system receives the signal and enables the outputs of latches Ul and U2 by setting ADRDl to "1". The host system then reads the data from these latches and returns ADRDl to "0". The host system repeats the process for latches U3 and U4 using the ADRD2 line. While the host system is retrieving the data, the microprocessor in the digital section is waiting for the ADRD2 line to be set to "1". When this occurs, the microprocessor responds by going to an idle state and waiting for its timer/-counter to signal the beginning of the next conversion cycle.

Figure 10. Timing Diagram for an Example Host System Interface

Alternatively, the Tl line could have been used to signal the microprocessor that the data had been retrieved by the host system. In another application, where continuous running of the DAS is not required, the Tl line could be used to signal the microprocessor to begin a conversion.

### Performance of the Existing Low-Power DAS

The performance of the low-power DAS is reported here. A full explanation of the test techniques used to obtain the following performance data is beyond the scope of this thesis; however, the test techniques are discussed in detail in Doerfler.4

Briefly, a spectrally pure, 45 Hz, bipolar sine wave was applied to the input of a single channel, wire-wrapped prototype DAS, and using automated test techniques, exhaustive performance data was compiled and processed over the full span of the DAS. Such dynamic test techniques yield results that more closely represent the DAS's real world performance. In order to investigate the errors introduced by the DAC within the DAS's ADC, the tests were repeated three different times with DACs from different lot numbers. A plot of the differential linearity error over the full span of the DAS is shown in Figure 11a. A plot of an FFT that was calculated from the data is shown in Figure 11b. Results are summarized in Table 1.

A very large differential linearity error at the 00...00 code is evident in Figure 11a. Significant harmonic distortion is apparent in Figure 11b. The data in Table 1 indicates that the

Figure 11a. Diff. Linearity Error as a Function of Output Code (DAC #1 used in ADC)

Source: Doerfler, "Techniques for Testing a 15—Bit Data Acquisition System", [4].

f=45 Hz, fs=128 Hz, Vin=9.9Vpp, 2048 points

Figure 11b. Fourier Transform Test Results for a Bipolar Input Source: Doerfler, "Techniques for Testing a 15—Bit Data Acquisition System", [4].

error at the 00...00 code is at least partially dependent on the DAC. Sources of the large 00...00 code error are examined in the next chapter.

Table 1

Performance Data for a Single Channel DAS Prototype that was Subjected to a Bipolar, Sine Wave Input

| Performance                            | DAC Used |    |    |

|----------------------------------------|----------|----|----|

| Figure                                 | 1        | 2  | 3  |

| Max. Diff. Linearity<br>Error (LSBs)   | 3        | 3+ | 5+ |

| # Missing Codes                        | 5        | 44 | 32 |

| Effective Linearity (# bits out of 15) | 9.1      | -  | -  |

The previous data suggests that the DAS does not perform well when subjected to a bipolar signal. However, it performs much better when subjected to a unipolar signal. Figure 12 shows an FFT plot calculated from data taken from the DAS when the input of the DAS was subjected to a unipolar sine wave. The harmonic distortion is much lower than in the previous case. Other results are summarized in Table 2.

Table 2

Performance Data for a Single Channel DAS Prototype that was Subjected to a Unipolar, Sine Wave Input

| Performance                            | DAC Used |   |    |

|----------------------------------------|----------|---|----|

| Figure                                 | 1        | 2 | 3  |

| Max. Diff. Linearity<br>Error (LSBs)   | 1+       | 2 | 2+ |

| Effective Linearity (# bits out of 14) | 13.3     | - | -  |

f=45 Hz, fs=128 Hz, Vin=4.9Vpp+2.5Vdc, 2048 points

Figure 12. Fourier Transform Test Results for a Unipolar Input Source: Doerfler, "Techniques for Testing a 15—Bit Data Acquisition System", [4].

f=45 Hz, fs=128 Hz, Vin=9.9Vpp, 2048 points

Figure 13. Fourier Transform Test Results for a Bipolar Input (Two channel PC board version)

Later testing of a PC board version of the DAS indicates that the harmonic distortion shown in Figure 11b is not directly related to the size of the differential linearity error at the 00...00 code. The FFT plot shown in Figure 13 was obtained from a PC board version of the DAS that has a differential linearity error at the 00...00 code of 8 LSB. The harmonic distortion shown in Figure 13 is much less apparent than the harmonic distortion shown in Figure 11b, and indicates that the effective linearity of the PC board DAS is about 13 bits. A possible explanation for the difference in performance between the prototype DAS and the PC board DAS is that the best straight lines drawn through the transfer characteristics of the negative and positive polarity ranges of each DAS are more colinear for the PC board DAS than for the prototype DAS. However, this theory has not been tested.

#### CHAPTER 2. INHERENT ERROR SOURCES IN THE LOW-POWER DAS

#### Introduction

Several inherent error sources in the low-power DAS which have not been formally considered before can now be discussed. The major source of error in this system is the mismatch between the polarity ranges. Other sources of error include track-and-hold droop, system noise, and comparator related problems. These error sources will be discussed in the following sections. Reference will be made to particular circuit components, so the reader should refer to Figure 6 while reading these sections.

# Mismatch of Polarity Ranges

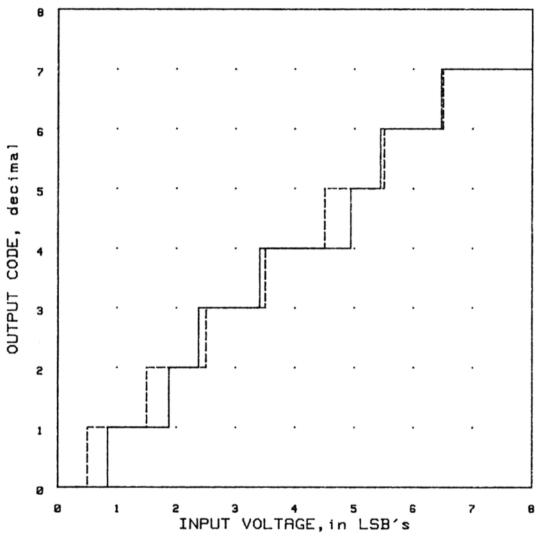

Preliminary tests performed by Doerfler showed that the existing DAS has a 3 - 5 LSB differential linearity error at the 00...00 code.<sup>4</sup> This error produces a mismatch of the positive and negative polarity ranges of the DAS, and can produce significant harmonic distortion. A mismatch of the polarity ranges will produce a transfer characteristic like the one shown in Figure 14.

There are several causes for the polarity range mismatch. The three major ones are 1) the DAC output has not been properly offset for use in a bipolar converter, 2) the DAC circuit's output voltage step between the 00...00 and 00...01 codes is greater than 1 LSB in width, and 3) the reference used for polarity determination depends on the polarity determined during

Figure 14. Transfer Characteristic of an ADC with Polarity Range Mismatch

the last conversion. These three causes will be considered here.

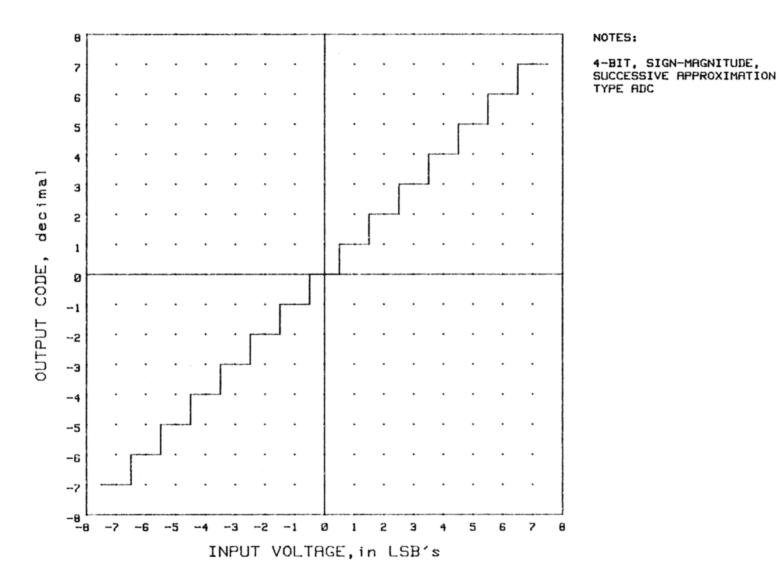

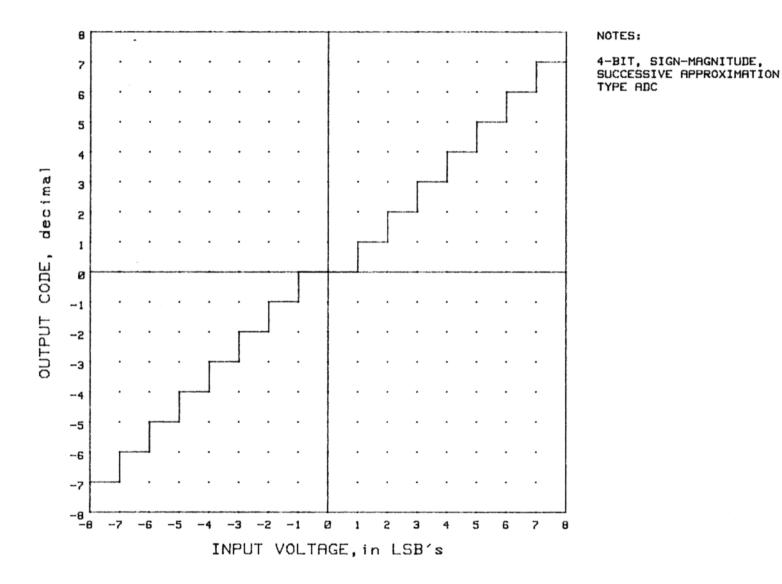

# Improperly Offset DAC Output

For proper bipolar operation, the output of the DAC used in a sign-magnitude, successive approximation type ADC must be offset by 1/2 LSB. A correctly adjusted DAC will allow the ADC to produce the ideal transfer characteristic shown in Figure 15. The range of analog voltages represented by the 00...00 code is 1 LSB wide and centered on 0 V. When the DAC output is not offset, (which is the case with the low-power DAS), the ADC produces a transfer characteristic like the one shown in Figure 16. The range of analog voltages represented by the 00...00 code is now 2 LSB wide. The result is a built-in differential linearity error of 1 LSB for the 00...00 code. Accurately offsetting the DAC output is not easily accomplished in the DAC circuit used in the low-power DAS. Fortunately, another method of correction is available, and is discussed in the next chapter.

# Unusually Large Voltage Step at DAC Circuit's Output

The previous cause of polarity range mismatch does not explain the 3 - 5 LSB differential linearity error at the 00...00 code, however. Another cause is that the voltage step at the output of the current-to-voltage circuit, which follows the DAC output current, is much greater than 1 LSB in width between the the DAC input codes of 00...00 and 00...01. This problem manifests itself in the following manner. The signal is, for example, a very small positive voltage. During polarity determination, the polarity is correctly determined to be

Figure 15. Transfer Characteristic of a Perfect ADC

Figure 16. Transfer Characteristic of an ADC When its DAC Output is not Offset

positive. However, the signal is not sufficiently positive to result in any output code except 00...00. This occurs over an analog voltage range of several LSB, and results in a "dead zone" where no measurement can be made.

This problem has been shown to be dependent on the DAC, as DACs from different lots produce different "dead zone" widths. Also, this problem is aggravated by the input offset current of the op-amp U8. In the design of the ADC, nulling the effects of input offset current was accomplished by including the resistor R7 between the noninverting input of U8 and the analog common. The 10 kohm value for R7 was computed in the usual manner for the condition when the inverting input of U8 sees an open circuit (ideally) when looking into the DAC output. condition exists when the DAC input code is 00...00, but for any other input code the inverting input of U8 sees a finite resistance which is dependent on the DAC input code. the 10 kohm value for R7 is not strictly correct for any condition except when the DAC input code is 00...00. On the other hand, the computed value for R7 is probably the best compromise.

Since the DAC itself is at least partially responsible for the large differential linearity error at the 00...00 code, a partial solution to this cause of polarity range mismatch would be to individually test each DAC to ensure that its output current step between the DAC input codes 00...00 and 00...01 is as close to the ideal as possible. This cause of polarity range mismatch can also be compensated for by the microprocessor-based compensation technique that is presented in the next chapter.

# Uncertain Reference for Polarity Determination

Another cause of polarity range mismatch is that the reference used to determine the polarity of the input signal depends on the polarity of the input signal during the last conversion. If the sampled input's polarity during the last conversion was negative, the output of op-amp U8 is used as the If the sampled input's polarity during the last reference. conversion was positive, the output of op-amp U9 is used as the The uncertainty about which op-amp output is used as the reference creates a problem if there is a mismatch of the output offset voltages of the two OP-37 op-amps stemming from differences in their input offset voltages and currents. Since close matching of the outputs of U8 and U9 was strived for in the design of the DAS, the effect of this error source should be However, this problem is easily eliminated be resetting the flip-flop Ull at the beginning of each conversion. solution is to use the analog common as the polarity determination reference instead of the outputs of the op-amps U8 and U9. Circuit modifications which allow the analog common to be used as the polarity determination reference are presented in the next chapter.

# Track-and-Hold Droop

Track-and-hold droop causes two problems. The first problem is that the sampled voltage being measured is changing during the successive approximation search. The second problem is that the sampled voltage held in the second channel is changing during the

conversion of the sampled voltage held in the first channel. The second problem arises from the fact that the two input channels are sampled simultaneously, but conversion of the two sampled voltages occurs in succession.

#### Droop During a Conversion

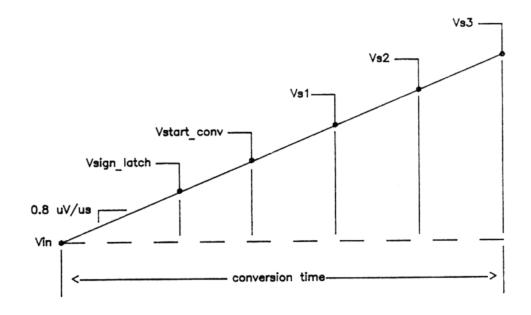

The droop rate for the track-and-hold was determined by Reed to be + 0.8  $\mu$ V/ $\mu$ s.<sup>2</sup> The droop is caused by op-amp bias currents and switch leakage currents. During the conversion of a sampled voltage, approximately 27 microprocessor instruction cycles take place, with a period of 15  $\mu$ s per instruction cycle. At the measured droop rate, the sampled voltage can change by 324  $\mu$ V, or 1.06 LSB. This analysis assumes that the droop rate is constant over the entire range of input voltages; this is probably not a good assumption.

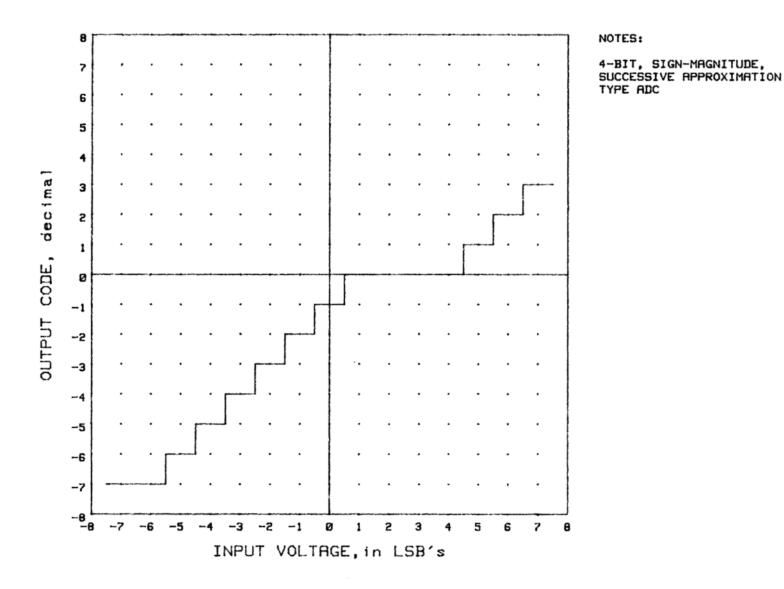

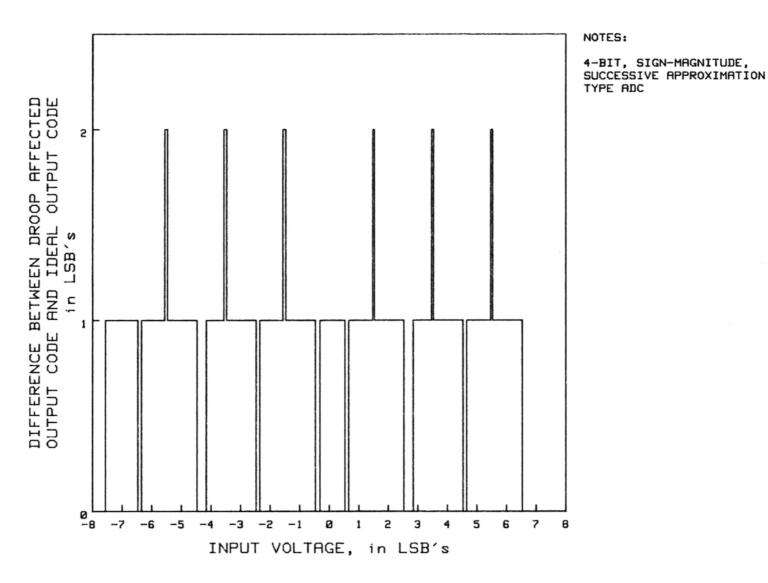

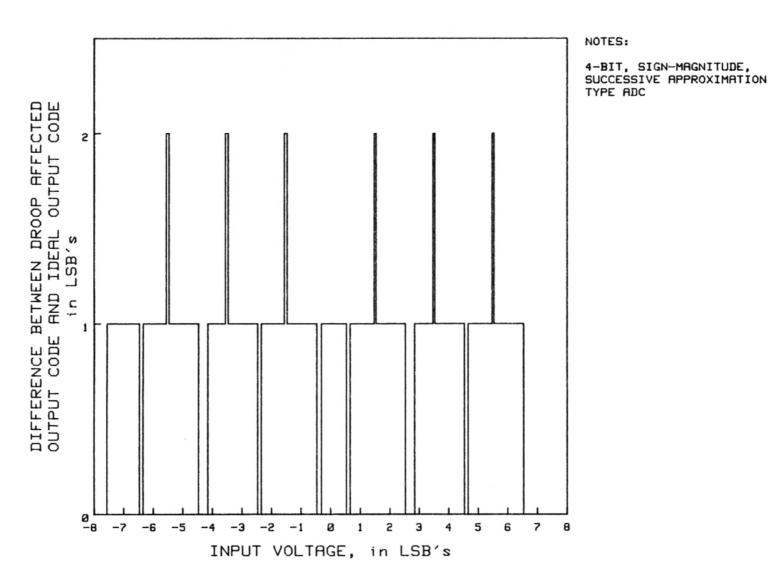

If the measured droop rate is accurate over the entire span of the DAS, then the first droop related problem appears to be a serious error because it causes uncertainty in the accuracy of the ADC's output code. A software simulation was written to investigate the effects of track-and-hold droop on the ADC's performance. The development of the simulation is shown in Appendix E. The simulation models the effects of the track-and-hold droop on an otherwise ideal bipolar 4-bit (3 bits plus sign) ADC over an input range of ± 5 V. The result of the simulation is shown in Figure 17. The plot shows the difference between the droop affected output code and the ideal output code, and indicates that the maximum error caused by the droop is 2 LSB.

Figure 17. Results of Track-and-Hold Droop Error Simulation

### Droop of Second Sampled Voltage During Conversion of First

Analysis of the second droop related problem is similar to the analysis of the first. During the conversion of the sampled voltage on channel 1 and the retrieval of the resulting data, approximately 52 microprocessor instruction cycles take place. At the measured droop rate, the sampled voltage on channel 2 would drift approximately 624 µV, or 2.05 LSB before conversion of the channel 2 voltage even begins. This results in an offset error between the channels. One solution would be to alter the channel 2 hold capacitor value to slow down the droop rate of the second channel relative to the first. However, care would have to be taken in the choice of the new capacitor value so that the signal acquisition performance of the second channel is not significantly degraded. Again another solution is available, and is presented in the next chapter.

# System Noise

Since the voltage differences handled by the ADC are in the range of hundreds of microvolts, the noise that the analog section is subjected to should be minimized. This noise comes from the system environment, from the digital section, and from within the analog section itself.

Noise pick-up from the environment can be reduced by enclosing the analog section in a shielding container. This also reduces noise pick-up from the digital section. Other techniques for reducing noise pick-up include shielding of the power supply and signal lines to protect them from noise, shielding of the

clock line between the analog and digital sections to reduce noise output from this line, and ensuring that the entire system is properly grounded so that no "ground loops" are formed.

Steps should also be taken to reduce noise problems within the analog section itself. These include all the usual PC board tricks, such as use of ground planes, use of guard loops on component inputs, and physical separation of analog and digital components and traces. Special care should be given to the placement of the SAR clock trace to avoid coupling of the clock into any of the analog signals or supplies.

One particular improvement to the existing DAS design would be to place part of the power supply filter network on the component side of the power supply switches, as close to the components' power supply pins as possible. The reason for this is that at radio frequencies, (the SAR clock frequency), even a few inches of trace metal between the filters and the components can allow significant noise pick-up. Furthermore, at higher frequencies, the power supply rejection ratio (PSRR) of the components is low enough to allow a noise signal on the power supply pins to affect the components' performance. This is especially important for the comparator because it is a high gain device that is operated in an open loop configuration, and is therefore prone to noise induced error and oscillation. The comparator is discussed in more detail in the following section.

### Comparator Related Problems

Proper functioning of the comparator is crucial to the performance of the ADC, since it is the central component in the determination of input signal polarity and in the successive approximation search. Since the comparator is a high gain device and is used in an open loop configuration, it is susceptible to unwanted feedback caused by parasitic effects. The solution to comparator related problems is to provide the comparator with the best circuit environment possible. 8 9

#### Improper Power Supply Bypassing

The most important part of the comparator's circuit environment is proper power-supply bypassing. Ideally the comparator should be provided with a low impedance power source under all conditions. However, as the comparator switches, the changing internal characteristics of the comparator create rapidly changing demands for power supply current. These current demands appear on the power supply lines as high frequency signals. these high frequencies the resistance and parasitic inductance of the power supply wires and traces become significant impedances. To the comparator, the power supply is no longer a low impedance power source. Since the PSRR of the comparator falls off at high frequencies, the resulting fluctuations of the power supply potentials have greater effect on the output of the comparator. A vicious circle develops between the fluctuations of the power supply potentials and the changing state of the comparator's internal circuitry, creating a sustained oscillatory condition.

The voltage signals generated on the power supply lines are also communicated to the power supply pins of other components, creating problems throughout the circuit. The solution to this problem is to place bypass capacitors between the comparator's power supply pins and the analog common. These capacitors act like small energy reservoirs that can provide a low impedance current source or sink for the comparator when one is needed. They also act as a short to ground for high frequency voltage noise on the power supply lines.

However, when bypass capacitors are used on several components, another problem is created. All the bypass capacitors are effectively paralleled and the combination of the capacitors and parasitic inductances can create a complicated, resonant circuit. The effects of the resonant circuit can be reduced by including a damping element in the power supply lines, such as a 10 ohm resistor. These resistors should be placed between a component's power supply pin and the power supply, on the power supply side of the bypass capacitor and as close to the component as possible. It should be noted that the resistor and bypass capacitor form a simple RC low-pass filter.

The existing low-power DAS has a power supply filtering network that performs the functions of the bypass capacitor and damping resistor. However, the filter network could be more effective if it were physically rearranged so that part of the filtering network was as close to the components as possible. In other words, a one or two pole low-pass filter could be placed at the edge of the board between the power supply and the power switches to reduce the amount of noise that is passed from the

power supply wires to the analog section. Then individual lowpass filters could be placed on the component side of the power switches, as close to the components as possible.

In the literature, the bypass circuit that is usually recommended is a 10 ohm resistor connected in series with the power supply line and a 10 µF tantalum capacitor in parallel with a 0.01 µF ceramic capacitor connected between the power supply pin and the analog common. The recommendation is based on experimentation which has shown this circuit to be adequate for most applications. The filtering network used in the low-power DAS is similar to the one mentioned above, and further experimental comparison of these two circuits would show which is better in this application.

### Unwanted Feedback

Another common problem for high gain comparators is feedback from the output to the input through stray capacitance and inductance. This problem can result in net positive feedback or oscillation in the comparator circuit. The solution to the feedback problem is to keep the source impedances at the comparator inputs low and reduce the stray capacitance and inductance between the output and the inputs as much as possible. Source impedances should be kept low to reduce error voltages across the impedances. These error voltages are produced by currents induced on the inputs by stray inductances or by current spikes on the inputs that are caused by the switching of the comparator. The stray capacitance and inductance between the output and the inputs of the comparator can be reduced by routing the output

away from the inputs and by providing a ground plane under the comparator and its associated traces.

# Input\_Noise

System noise that appears on the comparator inputs will create a "region of indecision" for the comparator. The region of indecision is a range of differential input voltages where the noise voltage amplitude is of the same order as the differential input voltage amplitude. In this region the noise will inhibit the comparator's ability to make a comparison of its input voltages, causing the output of the comparator to continuously wander between its rails in a random fashion. The effect on the ADC's performance is to obscure the ideally sharp transitions between the output codes in the ADC's transfer characteristic, as shown in Figure 18. In other words, there will be bands of analog input voltages where the ADC will not be able to precisely determine a digital representation, but will in successive conversion cycles produce several, (usually two), output codes for a given input voltage. Therefore, the system noise that the analog section is exposed to should be reduced as much as possible.

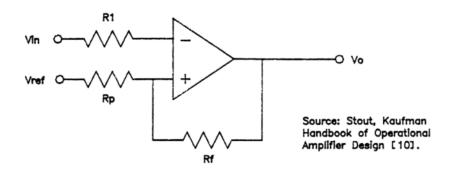

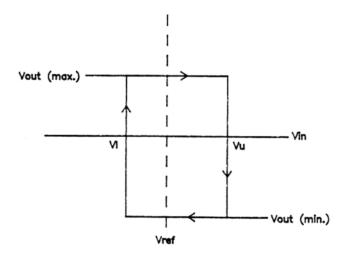

One technique used with comparators to increase their noise immunity is to introduce feedback to the noninverting input. This produces a hysteresis effect in the switching characteristic of the comparator, as shown in Figure 19. A comparator circuit which produces hysteresis is shown in Figure 20. A problem with this circuit, however, is that the placement of the hysteresis loop relative to the reference voltage is dependent on the

NOTES:

3-BIT, UNIPOLAR, SUCCESSIVE APPROXIMATION TYPE ADC

Figure 18. Transfer Characteristic of an ADC with Comparator Noise

Figure 19. Switching Characteristic of a Comparator with Hysteresis

Figure 20. Circuit Diagram for a Comparator with Hysteresis

reference voltage. If used in a successive approximation ADC, this can cause differential linearity errors.

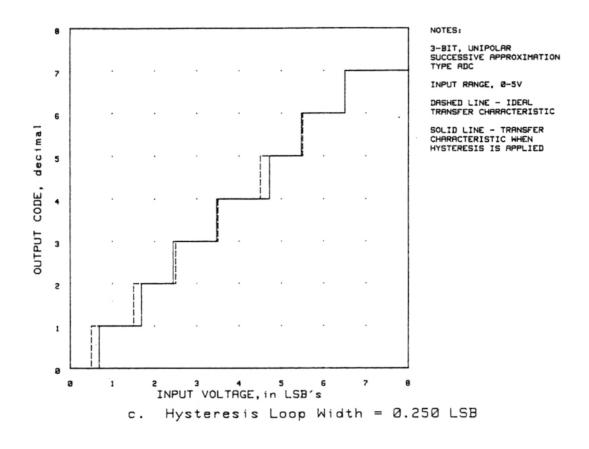

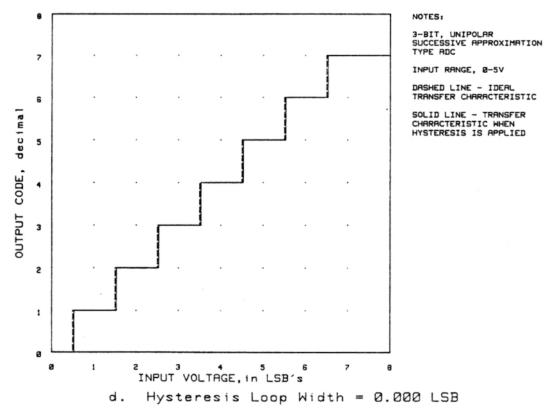

A software simulation was written to investigate the extent of the linearity error caused by comparator hysteresis in a successive approximation ADC. Development of the simulation is shown in Appendix F. The simulation models the effects of comparator hysteresis on an otherwise ideal 3-bit, unipolar successive approximation ADC with a 5 V span. The reference voltage shown in the comparator circuit, (Figure 19), is the output of the DAS's track-and-hold. From inspection of the results shown in Figures 21a - d, it appears that the hysteresis loop width would have to be less than 1/4 LSB so that the differential linearity error introduced by comparator hysteresis is relatively insignificant. For a 15-bit ADC with a 10 V span, 1/4 LSB corresponds to a voltage of 76.3 µV. To achieve a loop size this small, a feedback resistor value on the order of tens of megohms would be needed. Not only is a resistor this large not commonly available, but it could introduce significant thermal noise at the comparator input as well. Therefore, hysteresis is probably not a good solution for increasing the noise immunity of comparators used in high resolution successive approximation ADCs.

#### Input\_Offset\_Voltage

One other comparator related problem is the input offset voltage. The effect of the offset voltage is to create an offset error in the ADC's transfer characteristic. This is not a serious error and can be compensated for by the microprocessor-based error compensation technique presented in the next chapter.

Figure 21. Transfer Characteristic of an ADC with Comparator Hysteresis

Figure 21 (cont'd). Transfer Characteristic of an ADC with Comparator Hysteresis

#### CHAPTER 3. A MICROPROCESSOR-BASED ERROR COMPENSATION TECHNIQUE

#### Introduction

Since the DAS contains a microprocessor, it is desirable to use the microprocessor to correct for the DAS's errors. Several of the error sources discussed in the last chapter can be compensated for by the microprocessor-based technique that is discussed here. The errors that are compensated for are:

- polarity range mismatch

- offset between the track-and-hold's channels

- · comparator input offset

A theoretical discussion of the compensation technique is given first. Next an implementation of the compensation technique is shown for the low-power DAS. Finally, some initial results obtained from static and dynamic tests of the error compensated DAS are reported.

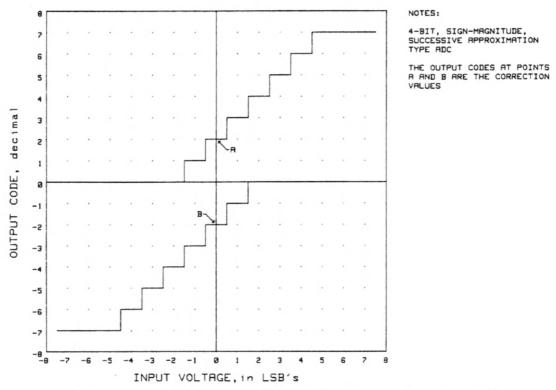

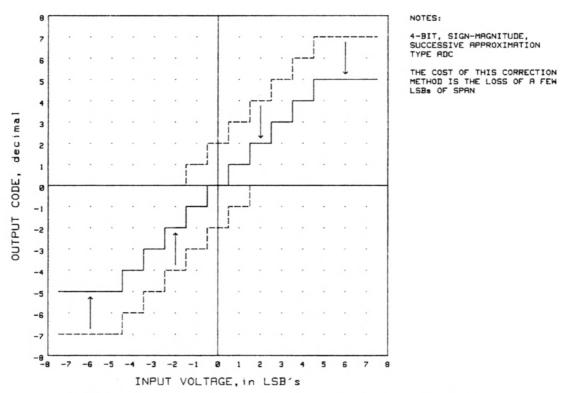

#### Theory

If the positive and negative polarity ranges of the ADC overlap so that small analog input voltages can be measured in either range, as shown in Figure 22, then the overlap can be compensated for in the microprocessor's software. This is done by shifting all the positive range output codes down toward the ideal transfer characteristic and shifting all the negative range

Figure 22. Transfer Characteristic of an ADC with Ranges Offset

Figure 23. Transfer Characteristic of an ADC After Correction is Applied

output codes up toward the ideal transfer characteristic, as shown in Figure 23. The required amount of shift is determined by finding the output codes that correspond to an input voltage of 0 V for both the positive and negative polarity ranges, (points A and B in Figure 22). Ideally, only the part of the positive range that is used to measure input voltages greater than 0 V and the part of the negative range that is used to measure input voltages less than 0 V are retained; the rest of the output codes are thrown away so that the two parts of the ADC's corrected transfer characteristic meet at an input voltage of 0 V.

To determine the required amount of shift for both polarity ranges, the track-and-hold inputs are connected to the analog common and two analog-to-digital conversions are performed. The negative polarity range is used for one of the conversions and the positive polarity range is used for the other. The two resulting output codes become the correction codes for the negative and the positive polarity ranges. In subsequent conversion cycles on an input signal, the correction codes are used by the microprocessor to shift all the output codes toward their ideal values. If the output code that results from a conversion is a negative value, then the magnitude of the negative polarity range correction code is added to the output code. If the output code that results from a conversion is a positive value, then the magnitude of the positive polarity range correction code is subtracted from the output code. Since the low-power DAS is a two channel system, two sets of correction codes are needed (one set for each channel).

To achieve the overlapping transfer characteristic shown in Figure 22, offsets must be introduced in the ADC's hardware. The range of input voltages measurable by the negative polarity range of the ADC must be offset toward the positive direction; the range of input voltages measurable by the positive polarity range of the ADC must be offset toward the negative direction. The overlapping region should extend far enough on either side of 0 V to include the magnitudes of the offset voltage between the track-and-hold channels, the comparator's input offset voltage, and error voltages caused by aging of components. The overlapping region must include the analog common voltage, (0 V). The offsets would be fixed at the time that the DAS is manufactured, and would be set at a large enough value to meet the preceding criteria.

The accuracy of the induced offsets is somewhat important. The offsets should ideally be X + 1/2 LSB in magnitude, where X is an integer. Variation from the ideal offset value will result in a differential linearity error at the 00...00 code and an offset error in the ADC's overall transfer characteristic. The differential linearity error will be between - 1 and + 1 LSB. The offset error will be between - 1/2 and + 1/2 LSB. These errors are not overly significant when compared to errors in other parts of the transfer characteristic.

The uncertainty about whether the output of the current-to-voltage converter or the output of the inverting amplifier (op-amp circuits containing U8 and U9 in Figure 6) is used as the polarity determination reference voltage can be eliminated by using the analog common as the reference. The effect of the

comparator's input offset voltage on the accuracy of the polarity determination is then unimportant as long as the magnitude of the offset is less than the difference between the voltage at the edge of the overlapping region and the analog common voltage.

When the ADC's polarity ranges are forced to overlap and are then corrected for with the microprocessor, many of the low-power DAS's original errors are also compensated for. This hardware overlap/software correction scheme then forms the basis for a microprocessor-based error compensation technique for the DAS. The concept behind this error compensation technique involves the replacement of uncontrollable errors with an error that is controllable and correctable. For instance, the effect of the wide voltage step at the DAC circuit's output between the 00...00 and 00...01 DAC input codes is eliminated. This is because the DAC is no longer used to generate the polarity determination reference voltage (when the analog common is used for that purpose) and because the 00...00 and 00...01 codes are not used in the magnitude determination. The polarity ranges are forced to match by the software-based shifting of their transfer characteristics. Also, errors caused by the comparator's input offset voltage are nulled. Since two sets of correction values are used, (one for each channel), the offset error between the channels is nulled as Finally, noise induced errors in the outcome of the polarity determination for very small voltages become unimportant since both ranges can be used to measure those small voltages.

This compensation technique is not without cost. A few LSBs of span are lost at the extremes of each polarity range. The amount of span lost at the positive extreme is equal to the

magnitude of the positive range correction code. The amount of span lost at the negative extreme is equal to the magnitude of the negative range correction code. Another problem involves the effect of noise on the determination of the correction codes. noise causes an error in the determination of the correction codes, then the output codes will not be shifted by the proper The result of this is that the transfer characteristics of the positive and negative polarity ranges will not match and an error at the 00...00 code will be created that could be as bad or worse than the original one. To minimize this possibility, the correction codes would have to be determined periodically. However, a trade-off exists between the power consumption of the DAS and the frequency of the determination of the correction The trade-off exists because the determination of the codes. correction codes must be accomplished during the extra time between normal conversion cycles; consequently the power-switched components of the DAS must be powered during that extra time. Another solution would be to use correction codes that are the result of a moving average of several previous correction codes. This solution is probably not desirable since it increases computation time and software complexity.

# Implementation

Since board space is an important consideration for the DAS in the particular application that it was designed for, it is desirable to use as few extra components as possible in an implementation of an error compensation scheme. If possible,

some of the extra unused devices on the existing low-power DAS should be used. The extra devices include:

- 1. 3 EX-NOR (exclusive NOR) gates

- 2. 1 AND gate

- 3. 1 D type flip-flop

- 4. 1 SPDT switch

- 5. 3 comparators

The following sub-sections describe the circuit modifications and the theory of operation for an implementation of the previously discussed error compensation technique. In the following text, a logic high will be represented as a "1" and a logic low will be represented as a "0".

# Circuit Modifications

An implementation of the hardware portion of the error compensation technique is shown in Figures 24, 25, and 26. Figure 24 shows a circuit that can be used to create the offsets in the ADC's polarity ranges. Figure 25 shows some modifications to the analog section's control logic and comparator circuit that will allow the microprocessor to find the correction codes and also will allow the analog common to be used as the polarity determination reference voltage. Figure 26 shows a complete circuit diagram of the analog section with all modifications in place.

The polarity range offsets are achieved by creating an offset voltage at the outputs of the op-amps U8 and U9. The offset voltage is created by introducing a small offset current

Figure 24. Resistor Divider Networks Used to Create Polarity Range Offsets

Figure 25. Modified Control Logic

at the inverting input of each op-amp with a resistor divider network. For the initial tests potentiometers were used to provide adjustibility. In the final product the divider network would be constructed with fixed value resistors. Since the output of the op-amp circuit containing U8 is inverted at the output of the op-amp circuit containing U9, the offset introduced in the circuit containing U8 is mirrored at the output of the circuit containing U9 and is fortunately in the correct direction. Therefore, the offset network used in conjunction with the circuit containing U8 creates the offsets for both ranges. The offset network used in conjunction with the circuit containing U9 is used to fine-tune the offset for the positive polarity range.

As shown in Figure 25, the polarity determination reference voltage is now the analog common instead of the virtual ground created by the DAC circuit at the output of either the op-amp U8 or the op-amp U9. The analog common is switched into the circuit using the SPDT analog switch U13. The original level shifting function of U13 is now performed by a resistor divider network. Switching control of U13 is performed by the CLR signal from the microprocessor. The AND gates (U24) are no longer needed since the DAC is not used to generate the reference voltage for the polarity determination.