#### THE ARCHITECTURE AND DESIGN OF A HIGH LEVEL LANGUAGE PROCESSOR

by

ROGER BREES B.S., Kansas State University, 1982

------

A MASTER'S THESIS

submitted in partial fulfillment of the requirements for the degree

MASTER OF SCIENCE

Department of Electrical Engineering

KANSAS STATE UNIVERSITY

Manhattan, Kansas

1984

Approved by:

22Hatt

Major Professor

| LD<br>2668    | A11202 663245                     |     |

|---------------|-----------------------------------|-----|

| 174           |                                   |     |

| 1984<br>. B73 | TABLE OF CONTENTS                 |     |

| 6.2           | I. INTRODUCTION                   | 1   |

|               | II. OBJECTIVES                    | 3   |

|               | III. ARCHITECTURE OVERVIEW        | 4   |

|               | IV. INSTRUCTION SET               | 23  |

|               | V. IMPLEMENTATION OVERVIEW        | 34  |

|               | VI. ARITHMETIC AND LOGIC UNIT     | 43  |

|               | VII. MAIN MEMORY                  | 46  |

|               | VIII. INSTRUCTION PROCESSING UNIT | 49  |

|               | IX. MICRO-PROCESSING UNIT         | 58  |

|               | X. STACK CONTROLLER               | 69  |

|               | XI. INPUT/OUTPUT PROCESSOR        | 74  |

|               | XII. MICRO-INSTRUCTIONS           | 88  |

|               | XIII. CONCLUSIONS                 | 140 |

|               | XIV. REFERENCES                   | 142 |

## LIST OF FIGURES

| 1.  | The Operand Stack for an Add Operation             | 4   |

|-----|----------------------------------------------------|-----|

| 2.  | The Operand Stack Used in Evaluating an Expression | 5   |

| з.  | The Control Stack                                  | 7   |

| 4.  | The Lexical Levels of the Procedures               | 12  |

| 5.  | The Display 1                                      | L 4 |

| 6.  | The Display for an Up-level Procedure Call         | 16  |

| 7.  | Variable Stack Linkages 1                          | 18  |

| 8.  | The Data Memory Map                                | 35  |

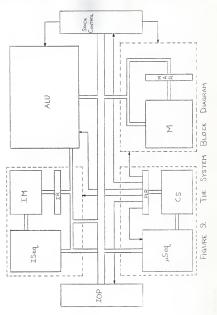

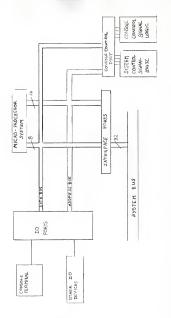

| 9.  | The System Block Diagram                           | 36  |

| 10. | The Instruction Processing Unit Block Diagram      | 38  |

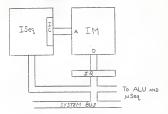

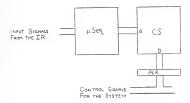

| 11. | The Micro-Procesing Unit Block Diagram             | 38  |

| 12. | The Input/Output Block Diagram                     | 41  |

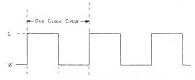

| 13. | PHI, the System Clock                              | 42  |

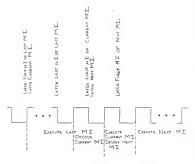

| 14. | A Simple Timing Diagram                            | 42  |

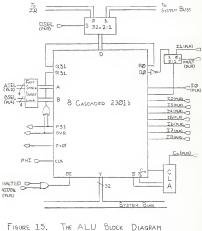

| 15. | The Detailed Block Diagram of the ALU              | 45  |

| 16. | The Detailed Block Diagram of the Main Memory      | 48  |

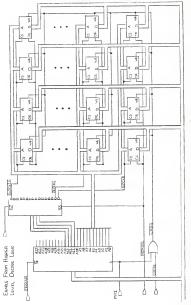

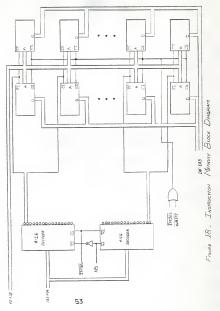

| 17. | The Detailed Block Diagram of the IPU              | 52  |

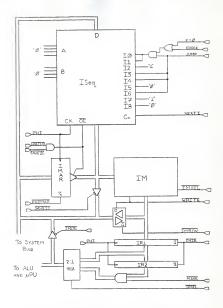

| 18. | The Instruction Memory Block Diagram               | 53  |

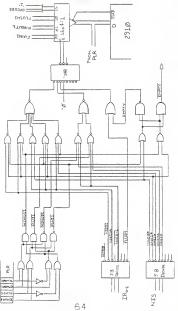

| 19. | The Detailed Block Diagram of the uPU              | 59  |

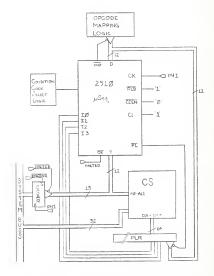

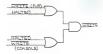

| 20. | The Micro-code Mapping Logic                       | 64  |

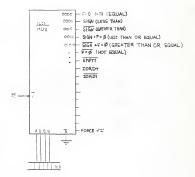

| 21. | The Generation of the CC* Signal                   | 65  |

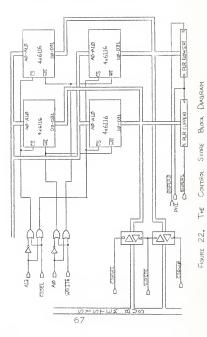

| 22. | The Block Diagram of the Control Store             | 67  |

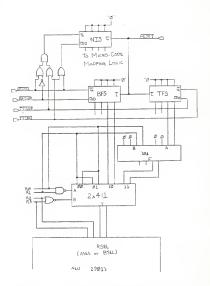

| 23. | The Pipeline Register                              | 58  |

| 24. | The  | Fast   | Stack  | Addre   | ss Map  | ping   | Logic  |         | •••••  | . 71 |

|-----|------|--------|--------|---------|---------|--------|--------|---------|--------|------|

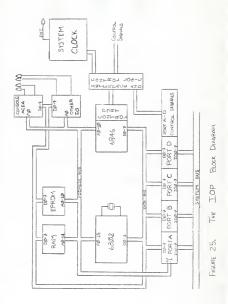

| 25. | The  | Detai  | led B  | lock D  | iagram  | of t   | he IOP |         |        | . 76 |

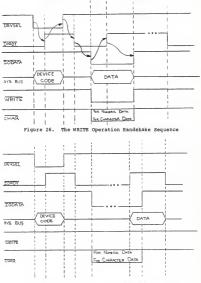

| 26. | The  | Write  | Opera  | tion 1  | Handsha | ke Se  | equenc | e       |        | . 79 |

| 27. | The  | Read   | Opera  | tion H  | andsha  | ke Se  | quence |         |        | . 79 |

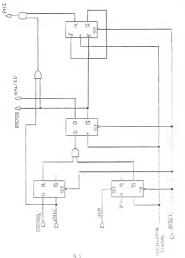

| 28. | The  | Syste  | em Clo | ck Ci   | rcuit   |        |        |         |        | . 82 |

| 29. | Gene | ration | of th  | e Cons  | ole Sup | plied  | Contr  | ol Sigr | als .  | . 86 |

| 30. | Inte | rfacin | q the  | Console | e Signa | ls wit | th the | System  | Signal | s 87 |

# LIST OF TABLES

| 1. | The Variables Known to the Procedures           | 11 |

|----|-------------------------------------------------|----|

| 2. | The Display Register Settings                   | 13 |

| з. | The Variable Addresses                          | 15 |

| 4. | The Instruction Set                             | 32 |

| 5. | The Instruction Processing Unit Control Signals | 51 |

| 6. | The Register Mapping Truth Table                | 72 |

| 7. | The ALU Register Assignments                    | 73 |

| 8. | System Control Signals Supplied by the Console  | 83 |

| 9. | Control Signals Generated by the Console        | 83 |

#### I. INTRODUCTION

Most computers being built are based on the concept presented by Von Neumann in the 1950's. This concept or architecture uses a single memory to store both data and the program instructions.

Typical machines today are also based on a register architecture. That is, there is some small number of highspeed general-purpose storage locations that can be used often for different functions. But the limited number means that many of the values in the registers must be shuffled back and forth from memory.

Programming languages, on the other hand, usually do not consider the program to be a part of the data. There are some exceptions to this. LISP, for example, is happy to rewrite the program thinking that it is modifying a list of some sort. The Block-structured languages (those derived from ALGOL especially) model a computer as a Harvard machine, i.e., a machine that has two independent memories - one for the data and one for the instructions. Thus the program can never modify the program.

Block-structured programming languages do not usually support the concept of a register. They define variables and constants when a block is entered, then use these for the storage of data. Further, the variables and the constants defined in the block disappear or are deactivated when the

block finishes. Some of the variables of other blocks can be referenced by the executing block. Others cannot. The scope of the variables is that part of the program in which they can be referenced. The rules defining when a variable can be referenced and when it cannot are clearly defined. By using a stack the scope of the variables can be maintained as the program executes.

The differences between the model of the computer seen by the programming language and the actual machine architecture is usually bridged by the compiler. The compiler is responsible for maintaining the variable scope in the register machine. The scope must be maintained as blocks are declared and dropped and as procedures are called and returned from. All this requires complex manipulations of pointers and lists.

This paper presents the design of a computer which closely supports block-structured languages. The machine has separate instruction and data memories, uses a stack to maintain the scope of variables during execution, and has an instruction set which resembles the instruction set of the block-structured languages.

## II. OBJECTIVES

The primary objective of this paper is to present the architecture and a possible implementation of a computer that closely supports high-level, block-structured programming Languages.

The three features that have been given precedence are;

- 1. Support for high-level constructs

- 2. Ease of use

- 3. Simplicity of design

Other features such as speed and hardware efficiency have been given secondary consideration.

The discussion and presentation of the design assume that the reader is familiar with digital design procedures. The features of the various processors used are not discussed, but are widely available in the literature (1),(2). The design is given in enough detail that it can be constructed.

No attempt has been made to incorporate some of the features that might be necessary to make this a "useful" machine. For example, characters are supported only in that the Input/Output can be made to treat the data it is reading or writing as a character. Characters can be handled without any special hardship, but they are inefficient in terms of the memory used.

### III. ARCHITECTURE OVERVIEW

Most of the block-structured programming languages are implemented using a stack. The computer described in this paper supports the stack concept directly. Its stack can be modelled as three separate stacks, each with a distinct function, and it implements these stacks as the major part of its architecture.

The first and simplest of the three stacks is the operand stack. An operand stack is used to hold the operands and results of operations. An operation, such as ADD, that requires two operands, uses the top two elements of the stack. The result of the operation is put back onto the top of the stack. Figure 1 shows the stack during an ADD operation. The level of the stack is reduced by one because the two operands are removed then the result put on.

| 1      |   | 1 |       | 1 1             |  |  |

|--------|---|---|-------|-----------------|--|--|

|        |   |   |       |                 |  |  |

| 1      | в | < | TOP   | 1 I             |  |  |

|        |   |   |       |                 |  |  |

| 1      | A | 1 |       | ! B + A   < TOP |  |  |

|        |   |   |       |                 |  |  |

| 1      |   | 1 |       | 1 . 1           |  |  |

|        | • |   |       | •               |  |  |

|        | • |   |       | •               |  |  |

| Before |   |   | After |                 |  |  |

Figure 1. Operand Stack for an Add Operation

By using an operand stack, the instruction that performs an operation does not need to specify where the operands come

from, nor where the result goes. These are always the same place: the top of the stack. A more complex example of the operand stack is shown in Figure 2. This example uses an operand stack to evaluate the expression A+(B-C/D)\*(2+F).

Figure 2. Operand Stack used in Evaluating an Expression

The second kind of stack used in high-level languages is a control stack. This stack is used to store linkage information when a procedure or subroutine is called. A procedure call causes a branch out of the instruction stream of the calling routine to that of the called routine. When the procedure has finished executing, it must cause a branch back into the calling routine. This return address could be stored in a dedicated memory location or in a register. However, if either of these were used the information would be lost if the called routine in turn called another routine. The return address could also be stored in a dedicated location local to the called routine. This breaks down if the routine ever recurses, (i.e. directly or indirectly calls itself) because the second return address is stored over top of the first. The other solution is to use a stack to hold the return addresses. When the subroutine is called, the return address is pushed onto the control stack. Then if more routines are called, their return address are also pushed onto the stack. When the routines finish and return to the routine that called them, the return addresses are popped off the stack.

Consider a main routine A which calls a subroutine B. B, somewhere in the course of its execution, calls another subroutine, C. Suppose that C calls subroutine B if some condition is met. If the condition is met on the first instance of C, then C calls B and B has recursed. Figure 3 shows the control stack for the case where the condition is met the first time but fails after that.

| 1 1          | 1 1                                   | 1 1                                   |

|--------------|---------------------------------------|---------------------------------------|

|              |                                       |                                       |

| 1 1          | 1 1                                   | 1                                     |

|              |                                       | · · · · · · · · · · · · · · · · · · · |

|              | 1 1                                   | RETURN B                              |

| <u>'</u>     |                                       | I KETUKA B I                          |

|              | I RETURN A I                          | RETURN A                              |

| 1 1          | I RETURN A I                          | I RETURN A I                          |

|              |                                       |                                       |

| In A         | A calls B                             | B calls C                             |

|              |                                       |                                       |

| 1 1          | 1 1                                   | 1 1                                   |

| · · · · ·    | · · · · · · · · · · · · · · · · · · · |                                       |

| 1            | RETURN B                              |                                       |

| · · · · ·    | I KEICKA B I                          |                                       |

| I RETURN C   | RETURN C                              | RETURN C                              |

| I REIORA C I | I REIDRA C I                          | I REIORA C I                          |

| I RETURN B   | I RETURN B 1                          | RETURN B                              |

| I KETOKA B I | I RETORA B I                          | I RETORN B I                          |

| RETURN A     | BETURN A 1                            | RETURN A                              |

| I REIORA A I | I RETORN A I                          | I REIORN A                            |

|              |                                       |                                       |

| C calls B    | B calls C                             | C returns                             |

When a routine finshes executing it returns to the calling routine by removing the return address at the top of the stack and branching to that location. The correct order is maintained by the nature of the Last-In-First-Out stack. The correct return address is always the one at the top of the stack when the routine finishes execution, although; many subroutines may have been called in between.

The third and most complex stack used in high-level languages is a variable stack. A variable stack is used to hold variables. The complexity arises from the necessity to maintain the scope of the variables. The scope of a variable is simply that part of the program in which that variable is known. The usual definition of scope is that a variable is known. The usual definition of scope is that a variable is known to all blocks declared within the same block as the variable, unless a new variable of the mase name is declared. In most ALGOL-derived languages a block may be in-line. That is, it may appear in the code as a section, set off by BEGIN and END statements, that may have variable names local to

itself. Example 1 on the following page demonstrates the scope of variables.

In the example, variables i, j, and mare declared in procedure A. Therefore they are known to all procedures declared within A unless those procedures declare a new variable with the same name. In the example, procedure B does declared a new variable named i. Thus the ideclared in A is inaccessible in B. The same scope rules apply to the new instance of i. It is known to all routines declared within procedure B unless they declare a new variable i. Procedure C does not declare any variable named i, so the one in B is known in C. The variable k, declared in procedure B, is also known to both procedures B and C.

The procedure named D is outside of both procedures B and C. So the variables of B and C are unknown in D, and those of D are unknown in B and C. An application of the scope rules to the variables of D shows that i and B from procedure A and j and 1 from procedure D are known to procedure D. Procedure E redeclares the variable i, so it is a different version from the one in A and D. All this is shown in Table 1. All variables known to a procedure are given and the procedure in which that instance of the variable was declared is given in parentheses.

```

PROGRAM A:

VAR i, j, m : INTEGER;

PROCEDURE B;

VAR i,k : REAL;

PROCEDURE C:

VAR j:REAL;

BEGIN

END; (*End of procedure C*)

BEGIN

END:

(*End of procedure B*)

PROCEDURE D;

VAR j,1:REAL;

PROCEDURE E;

VAR i:INTEGER;

BEGIN

END; (*End of procedure E*)

BEGIN

END;

(*End of procedure D*)

BEGIN

•

.

END;

(*End of main routine A*)

```

Example 1. A Program to Demonstrate Scope

These scope rules can be applied to more than just variable names. Procedure names, constants, functions, etc. all have scope within a program.

| ī | Procedure | I | Variables                    | ī |

|---|-----------|---|------------------------------|---|

| 1 | А         |   | i(A)<br>j(A)<br>m(A)         | 1 |

|   | в         |   | i(B)<br>j(A)<br>k(B)<br>m(A) |   |

|   | с         |   | i(B)<br>j(C)<br>k(B)<br>m(A) |   |

|   | D         | 1 | i(A)<br>j(D)<br>l(D)<br>m(A) |   |

|   | Е         |   | i(E)<br>j(D)<br>l(D)<br>m(A) | 1 |

Table 1. The Variables Known to theProcedures

When a block is entered during execution, space is set aside on the variable stack for the variables local to the block. The location of the variables in the stack will depend on the run time behavior of the program, but the variables will always be a fixed distance from the first location reserved on the stack for the block. A pointer to the first location is saved. A block is able to access all variables declared outside of it if those variables are included in the scope of

the block. Therefore a pointer to each of the variable spaces of the outer blocks must also be kept. These pointers can be kept in registers called display registers.

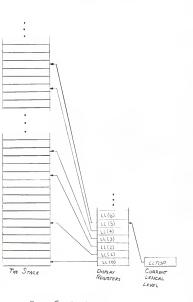

The pointers that must be available are dependent on the static hierarchical structure of the block declarations and not on the run time behavior. The hierarchy of declarations for Example 1 is shown in Figure 4. Each level of declarations is called a lexical level. A block has access to the variables of only one block at each lexical level that is lower than or equal to its own. A block may not access any variables in a block whose lexical level is higher than its own. Thus there is one display register for each lexical level. The lower level display registers need to be set to the blocks with lower lexical levels than the curent block. Table 2 shows how the display registers are set for each procedure in Example 1. LL(1x) indicates the display register for lexical level 1x. LLTOP indicates the current lexical level, and points to the highest valid display register. Figure 5 shows how these pointers all work together to define parts of the variable stack for each block.

Figure 4. The Lexical Levels of the Procedures.

| 1 | Procedure | 1 | Display Registers                      | ľ |

|---|-----------|---|----------------------------------------|---|

| I | A         | I | LL(0) to A                             | T |

| I | В         | ł | LL(0) to A<br>LL(1) to B               | ł |

|   | с         | ł | LL(0) to A<br>LL(1) to B<br>LL(2) to C | 1 |

| ł | D         | ł | LL(0) to A<br>LL(1) to D               | ł |

|   | E         |   | LL(0) to A<br>LL(1) to D<br>LL(2) to E |   |

Table 2. The Display Register Settings

Once the display is set for a given block, the variables can be accessed by the double 1x, n, where 1x selects the display register corresponding to lexical level 1x, and n is the index into that variable space to the desired variable. The location of a variable in the stack may not be known at run time, but it can always be referenced by the two-part address 1x,n. This address is known at compile time. Table 3 repeats Table 2 with the addition of the address double for each variable.

FIGURE 5. THE DISPLAY

| Procedure     | Variables                          | Address                                              |

|---------------|------------------------------------|------------------------------------------------------|

| <br>  A<br>   | i(A)<br>  j(A)<br>  m(A)           | LL(0),0  <br>  LL(0),1  <br>  LL(0),2                |

| I<br>I B<br>I | i(B)<br>  j(A)<br>  k(B)<br>  m(A) | LL(1),0  <br>  LL(0),1  <br>  LL(1),1  <br>  LL(0),2 |

| c             | i(B)<br>  j(C)<br>  k(B)<br>  m(A) | LL(1),0  <br>  LL(2),0  <br>  LL(1),1  <br>  LL(0),2 |

| <br>  D<br>   | i(A)<br>  j(D)<br>  l(D)<br>  m(A) | LL(0),0  <br>  LL(1),0  <br>  LL(1),1  <br>  LL(0),2 |

| 1<br>  E<br>  | i(E)<br>  j(D)<br>  l(D)<br>  m(A) | LL(2),0  <br>  LL(1),0  <br>  LL(1),1  <br>  LL(0),2 |

Table 3. The Variable Addresses

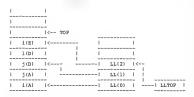

The scope rules can be applied to procedure names as well as variable names. Thus for Example 1, procedure E could have called procedure B. Procedure E is at lexical level 2, while procedure B is at lexical level 1. The display registers which define the scope of procedure E must be changed during such an "up-level" call to set the proper scope for procedure B. The display registers before the call to B, are shown in Figure 6A. The display registers, as they should be set after the call to procedure B are shown in Figure 6B.

-----| |<-- TOP k(B) | i(B) |<---------1 1(E) | i(E) | | 1 1 | 1(D) | | | j(D) | | 1 1 <u>|</u>\_\_\_\_| -----1 | j(A) | \_\_\_\_\_ LL(1) |<------- | | i(A) |<----| LL(0) | ----| LLTOP | \_\_\_\_\_

Figure 6B. The Display After the Call to Procedure B

The call sechanism needs to set the display pointers so the scope of the destination is correct. It must also save enough information to allow the scope of the calling routine to be restored once the called procedure finishes. It is simple to set the display registers so that the scope of the destination is correct. The call needs to look as if it came from the block in which the called procedure was declared. This will ensure that the scope is correct. The current lexical level is set to be that of the outside block. The called procedure performs a block entry which increments the current lexical level, then sets the display register for that level. The lexical level of the block in which a procedure is declared is known at compile time and can be included as part of the procedure entry instruction.

The values that must be saved in order to restore the scope of the calling routine are the lexical level, and the value of the display register for the calling routine. However, these are insufficient to completely restore the scope if the called routine is one or more levels higher than the calling block. For example, if a procedure at level 4 calls a procedure at level 2, all display registers from 2 to 4 must be restored to ensure that the scope of the calling routine is correct after the called procedure has finished. This requires that the display register be copied into the stack before a new block is entered. For the procedure call from level 4 to level 2 the variable stack with the linkages might be as shown in Figure 7.

Figure 7A. The Variable Stack Linkages Before the Call

To completely restore the scope of the calling routine, the lexical level and the display register for the calling block are restored from the stack. Then the next lower display register is restored by loading it with the value just below where the newly restored display register points. The next lower level pointer is restored in the same way. The relationship between the just-restored display register and the next lower display register can be written as

LL(1x-1) <-- S(LL(1x)-1)

The entire sequence for the restoration of the scope of the calling routine is;

LL(4) <-- S(TOP) Popped off the stack by Procedure Exit LL(3) <-- S(LL(4)-1) LL(2) <-- S(LL(3)-1)

This can be written as a procedure.

```

i = lx;

WHILE ( i>0 ) DO;

LL(i-1) = S(LL(i)-1);

i = i-1;

END WHILE;

```

The three kinds of stacks can be combined into a single physical stack. The display linkage information and the return address are stored together during a procedure call. This triple of values is called a Transfer Point. The operand stack sits on top of the variable stack. For the combined stack, a procedure entry requires the following steps:

- 1. Save the current display register.

- 2. Save the current lexical level.

- 3. Save the return address.

- Set the lexical level to that in which the procedure was declared.

- Do a block entry.

The steps necessary when entering a block are:

- 1. Save the current display register.

- 2. Increment the lexical level.

- 3. Set the new display register.

- Reserve the variable storage on the stack.

The class of languages derived from ALGOL allows a procedure or block to declare variables which retain their values from one invocation to the next. Pascal does not have this feature. To implement a random number generator in Pascal, the seed has to be passed back and forth to the procedure from one call to the next. In PL/I, the seed can be declared as an "OWN" variable. It can then be set by a call to the random number generator, and it will retain that value on the next call to the procedure. The calling program need not carry the variable SEED, which seems nothing to it.

OWN wariables can not be implemented with a stack. A HEAP is used to store variables which must not disappear between invocations of the procedure in which they are declared. The HEAP is also used for PL/I's "BASED" variables, which are normally used to implement list and tree structures.

The HEAP tends to become cluttered with areas which were in use at one time, but have since been discarded. PL/I uses

the functions ALLOCATE and FREE to claim and release blocks of memory. For operations of any extent which use the heap, garbage collection is necessary. There are many algorithms available for garbage collection (3).

#### IV. INSTRUCTION SET

There are two data types in this implementation. The numeric data type is used to represent integer numbers. (There are no floating point numbers in this implementation.) The other data type is logic. A value of the logic data type can have only two values; TRUE and FALSE.

The instruction set for this computer is almed at the ALGOL-like languages. It allows complete implementation of the ALGOL instruction set. In presented in "Compiler Construction: Theory and Practice" by Barrett and Couch (4). Pascal is mainly a subset of ALGOL, so it, too, should be completely supported. The instructions can be divided into 8 catagories. These are:

- 1. Arithmetic instructions

- Comparison instructions

- Logic instructions

- Data movement instructions

- 5. Stack and Heap maintenance instructions

- Block maintenance instructions

- 7. Jump instructions

- 8. Input/Output instructions

An arithmetic instruction is one which causes some arithmetic operation to be performed. Any operand is always taken from the top of the stack and the result is always put onto the top of the stack. The operands and result must be of the numeric data type. The arithmetic instructions are:

ADD - Pop the top two stack elements, add them, and put the result onto the stack.

- SUBTRACT Pop the top two stack elements, subtract thetop stack elementfrom the second element, and put the result onto the stack.

- NULTIPLY Pop the top two stack elements, multiply them together, and put the product onto the stack.

- DIVIDE Pop the top two stack elements, divide the second by the first, and put the guotient and remainder back onto the stack.

- NEGATE Pop the top stack element. Negate it, and push the result back onto the stack.

The comparison instructions pop two numeric operands from the stack and push a logic result whose value depends on the result of the compare. The comparsion instructions are:

- EQUAL Pop the top two numeric operands. Compare them. Push a TRUE result if and only if both operands are the same. Otherwise push a FALSE result.

- GREATER THAN Pop the top two numeric operands. Compare them. Push a TRUE result if and only if the second operand is larger than the top operand. Otherwise push a FALSE result.

- LESS THAN Pop the top two numeric operands. Compare them. Push a TRUE result if and only if the second operand is less than the top operand. Otherwise push a FALSE result.

The logic instructions require operands of the logic data type and produce a result of the logic data type. The operands are popped off the stack and the result is pushed onto it. The logical instructions are:

- NOT Pop the top operand. Complement it and push the result back onto the stack.

- AND Pop the top two operands off the stack. Logically AND them. Push the result back onto the stack.

OR - Pop the top two operands off the stack. Logically OR them. Push the result onto the stack.

The data movement instructions move data onto or off of the stack or heap. Some instructions require an operand. The operand can be of either data type or it can be an address. The data movement instructions are:

- LOAD Pop an address off the top of the stack. Fetch the value stored in that address and push that value onto the stack.

- LOAD CONSTANT c - Push the constant c onto the stack.

- LOAD LABEL z - Load a transfer point onto the stack. (More on labels later.)

- LOAD DATA 1x,j

- Push the value found in the variable whose address is lx, j onto the stack.

- LOAD HEAP 1

- Push the value found in location j in the heap onto the stack.

- LOAD HEAP ADDRESS 1

- Push the address of element j of the heap onto the top of the stack.

- REPLACE

- Pop the top of the stack. Pop an address from the new top of the stack and push the value pointed to by that address onto the stack. This instruction is only used by the Call-by-name parameter mechanism.

- STORE Pop the top element off the stack. Store it into the location whose address is at the new top of the stack. Pop the address off the stack.

- STORE DATA 1x, j

- Pop the top element off the stack and store that value into the variable whose address is 1x,j.

STORE HEAP 1 - Pop the top element off the stack. Store that value into location i in the heap. The Stack and Heap maintenance instructions change the value of the stack and heap pointers. They are: INCREMENT AND SAVE STACK - Pop the top element off the stack. Add that value to the top of stack pointer to form a new top of stack. Save the original value of the top of stack at the new top of the stack. INCREMENT STACK n - Add n to the top of the stack pointer. DECREMENT FROM STACK - Pop the top element off the stack. Subtract that value from the top of stack pointer. DECREMENT STACK n - Subtract n from the top of stack pointer. INCREMENT AND SAVE HEAP Pop the top element off the stack. Add that value to the bottom of the heap pointer. Push the new heap pointer value onto the top of the stack. INCREMENT HEAP n - Add n to the Heap pointer. DECREMENT AND SAVE HEAP - Pop the top element off the stack. Subtract that value from the bottom of the heap pointer. Push the result onto the stack. DECREMENT HEAP n - Subtract n from the Heap Pointer. The Block instructions handle the display chain and variable spaces. They are: BLOCK ENTRY n - Save the display register, increment the lexical

level, set the new display register, and reserve space on the stack for the variables of the block. (The entire sequence for a block entry is discussed below in the section on labels.)

BLOCK EXIT - Remove all the information saved on the block enter, (See below.) PROCEDURE ENTRY 1x - Enter procedure at lexical level 1x. (See below) LABEL ENTRY 1x - Set lexical level and stack pointer for the label. (See below) The jump instructions cause a branch in the program flow. They are: JUMP z - Jump to location z in the instruction stream. CONDITIONAL JUMP z - Pop the top stack element. Jump to location z if the value is FALSE, otherwise fall through to the next instruction. JUMP INDIRECT 1x, i - Jump to the destination whose address is stored in a variable whose address is 1x, j. CALL PROCEDURE z Jump to the procedure at z and save the return and display information. (see below) CALL PROCEDURE INDIRECT 1x, j - Jump to a procedure whose address is in a variable. Save the return and display information. - Branch to the place from which a procedure was called and restore all the display information. (See chapter 3) The Input and Output instructions cause a single value to

be read or written. All I/O instructions require a device code. The device code can be at the top of the stack or in the instruction word immediately following the I/O instruction. The Input/Output instructions are: READ Q

Read a numeric value from device Q and put it on the stack.

WRITE Q

Pop the top element off the stack and write its value to device Q.

READ CHARACTER Q

- Read a character from device Q and push it onto the stack.

WRITE CHARACTER O

Pop the top element off the stack and write it out to device Q as a character.

READ STACK

Pop a device code off the stack, then read a numeric value from that device and push it onto the stack.

WRITE STACK

Pop a numeric value off the stack, then write it out to a device whose device code is also popped off the stack.

READ CHARACTER STACK

Pop a device code off the stack and read a character from the selected device. Push the character onto the stack.

WRITE CHARCTER STACK

Pop a character off the stack. Write it out to a device whose device code is popped off the stack.

The LOAD LABEL instruction saves the current lexical level pointer, the current lexical level, and an instruction address on the stack. The three values saved by the LOAD LABEL are the same three values that are saved by the Procedure mechanism. This triple is called a transfer point. The label is placed on the stack so that the CALL PROCEDURE INDIRECT instruction can have a branch target. This indirect call is used during parameter evaluation. Other jump instructions cause a change in program flow but no return to the calling location is required. A transfer point does not need to be loaded onto the stack and any information in the stack above the variable space for the destination block is no longer needed. The jump mechanism loads the top of the stack pointer with the location just above the last variable. This is called the vorking pointer. The working pointer (WP) is saved by the Block Entry sequence. The Block Entry is then modified from that given in Chapter Three. The final form of the Block Entry sequence for a block having n variables is :

- Save the value of the top of stack pointer after the block entry is completed. (WP = TOP+n+2)

- Save the current lexical level pointer.

- Increment the current lexical level.

- Set the current lexical level pointer to point to the current top of the stack.

- Set the top of stack pointer to point to the first location above the variables. (TOP+n)

Everytime something is pushed onto the top of the stack, the top of stack pointer is incremented. So the value saved in step 1 and the value loaded into the Top of stack pointer in step 5 are the same value. Two values have been pushed onto the stack in between.

The order is important in many operations. If a jump out of a block is desired, the jump must be preceded by a LABEL ENTRY instruction to set the lexical level and the stack pointer to what they should be for the destination. A LABEL ENTRY performs the following operations:

- Set the current lexical level to that of the destination.

- Set the top of stack pointer to the value saved by the block entry of the destination block.

Any call to a procedure must include a PROCEDURE ENTRY instruction to set the lexical level to look as if the call came from the block in which the procedure was declared. This ensures that the scope is correctly set. The order for a procedure call then is:

- 1. CALL PROCEDURE (in the calling block)

- 2. PROCEDURE ENTRY (in the destination procedure)

- 3. BLOCK ENTRY (in the destination procedure)

The JUMP INDIRECT instruction is included to support an archaic ALGOL construct. A label can be passed to a procedure as a parameter. The procedure can then do a jump to that label. The return is bypassed and there is no guarantee that the program flow will ever reach the instruction after the call. This violates the philosophy of block-structured languages. The JUMP INDIRECT instruction must set the scope for the destination in the same manner that the procedure RETURM sets the scope.

Barrett and Couch give numerous examples of these instructions and their use in implementing the constructs of the ALGOL language.

The instructions set has forty-eight instructions. The instructions, their mnemonics, and their op-codes are given in Table 4. An instruction is one or two instruction words long. The first balf of the first word is always an op-code. This is

all that is necessary for some instructions. If nothing more is required, the last half is ignored. If needed, the second half is the lexical level. This is used by all the instructions that reference a variable location and by the LABEL ENTRY and PROCEDURE ENTRY instructions. The second word of an instruction, when used, has several meanings depending on the op-code in the first word.

The instructions are given in the format:

INSTRUCTION (operand),(operand)

The operands are those that are given in the instruction stream. All operands require one instruction word except the lexical level (lx), which is in the second half of the instruction word containing the op-code.

The abbreviations used in Table 4 are:

lx - lexical level

j - variable index

c - a data constant

z - a jump destination address

n - a pointer displacement

0 - an Input/Output device code

The op-codes are determined in part by the requirements of the mapping logic. (See chapter IX.)

| INSTRUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MNEMONIC | OP-CODE |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |         |

| 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ADD      | 40      |

| CTID TO & CT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CUD      | 40      |

| SUD INNUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NUL      | 42      |

| MULTIFLI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PIOLI    | 42      |

| DIVIDE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DIV      | 43      |

| NEGATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | NEG      | 20      |

| EQUAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | EQU      | 44      |

| GREATER THAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | GREAT    | 45      |

| LESS THAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LESS     | 46      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |         |

| NOT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | NOT      | 21      |

| AND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | AND      | 47      |

| OR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | OR       | 48      |