# STUDY AND PERFORMANCE CHARACTERIZATION OF TWO KEY RF HARDWARE SUBSYSTEMS: MICROWAVE DIVIDE-BY-TWO FREQUENCY PRESCALERS AND LOW NOISE AMPLIFIERS

by

#### SAFA KHAMIS

B.S., Kansas State University, 2011

#### A THESIS

submitted in partial fulfillment of the requirements for the degree

#### MASTER OF SCIENCE

Department of Electrical and Computer Engineering College of Engineering

> KANSAS STATE UNIVERSITY Manhattan, Kansas

> > 2013

Approved by:

Major Professor William B. Kuhn, Ph. D.

#### **Abstract**

This thesis elaborates on the theory and art of the design of two key RF radio hardware subsystems: analog Frequency Dividers and Low Noise Amplifiers (LNAs). Specifically, the design and analysis of two Injection Locked Frequency Dividers (ILFDs), one Regenerative Frequency Divider (RFD), and two different LNAs are documented. In addition to deriving equations for various performance metrics and topology-specific optimization criterion, measurement data and software simulations are presented to quantify several parameters of interest. Also, a study of the design of LNAs is discussed, based on three "regimes:" impedance matching, transconductance-boosting, and active noise cancelling (ANC). For the ILFDs, a study of injection-locked synchronization and phase noise reduction is offered, based on previous works.

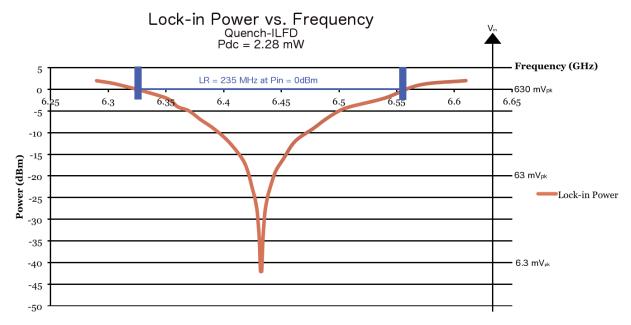

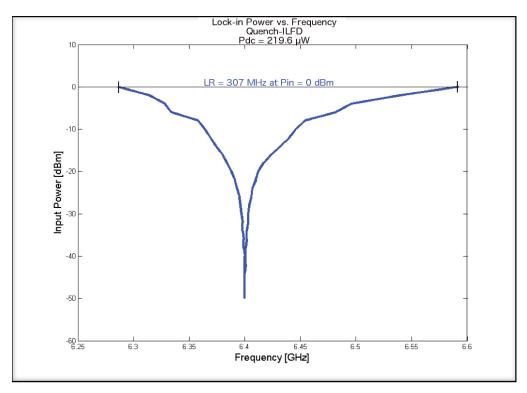

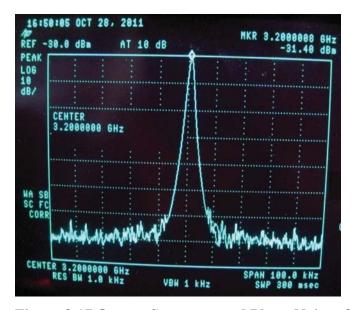

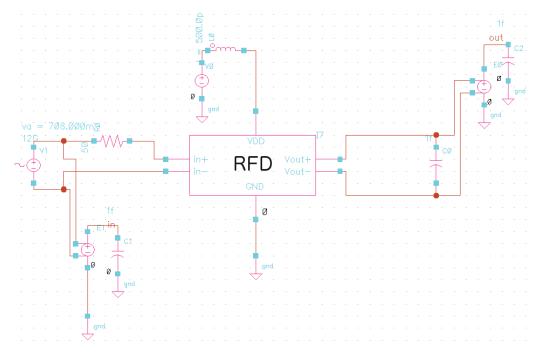

As the need for low power, high frequency radio devices continues to be driven by the mobile phone industry, Frequency Dividers that are used as prescalars in phase locked loop frequency synthesizers (PLLs) must too become capable of operation at higher frequencies while consuming little power. Not only should they be low power devices, but a wide "Locking Range" (LR) is also desired. The LR is the bandwidth of signals that a Frequency Divider is capable of dividing. As such, this thesis documents the design and analysis of two ILFDs: a Tail-ILFD and a Quench-ILFD. Both of these ILFDs are implemented on the same oscillator circuit, which consumes 2.28 mW, nominally. Measurements of the Tail and Quench-ILFDs' LRs are plotted, including one representing the Quench-ILFD operating at "very low" power. Also, an RFD is detailed in this thesis, which consumes 410  $\mu$ W. This thesis documents Locking Ranges for the Tail and Quench-ILFDs of 12% and 3.7% of 6.4 GHz respectively, during nominal operation. In "very low" power mode, the Quench-ILFD has a LR of 4.8% while consuming 219.6  $\mu$ W of power. For the RFD, simulations report a LR of 16.7% while consuming 410  $\mu$ W.

Recently in 2011, a wideband LNA topology by Nozahi et al., which employs Partial Noise Cancelling (PNC) of the thermal noise generated by active devices, was presented and claimed to achieve a minimum and maximum NF of 1.4 dB and 1.7 dB (from 100 MHz to 2.3 GHz), while consuming 18 mW from a 1.8 V supply. This thesis details the theory, design, and

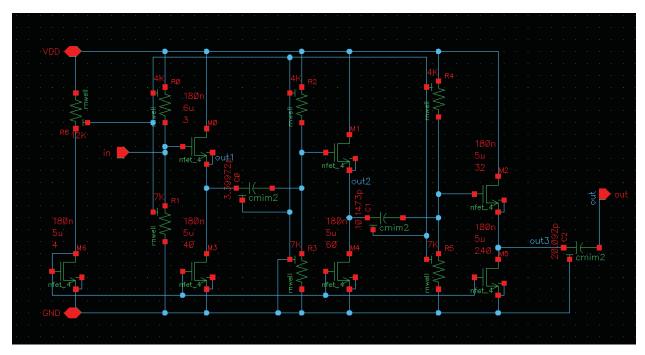

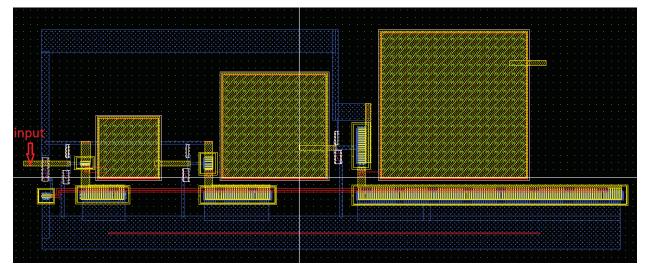

simulation results of a narrowband version of this PNC LNA. In order to compare the large-signal performance of this narrowband LNA to that of a well-known implementation, an LNA employing inductive source-degeneration (referred to as a "S-L LNA") is designed and analyzed through simulation. The PNC LNA operates at a frequency of 2.3 GHz while the S-L LNA operates at 2.8 GHz. Simulations report a NF of 1.76 dB for the PNC LNA and 2.3 dB for the S-L LNA, at their respective operating frequencies. Both LNAs consume roughly 15 mW of quiescent power from a 1.8 V supply.

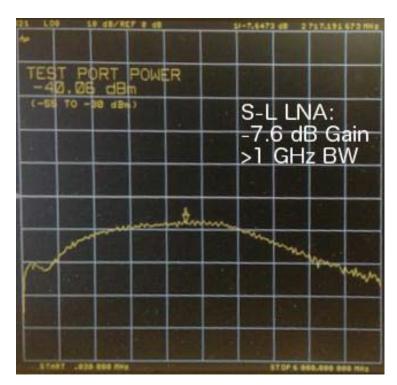

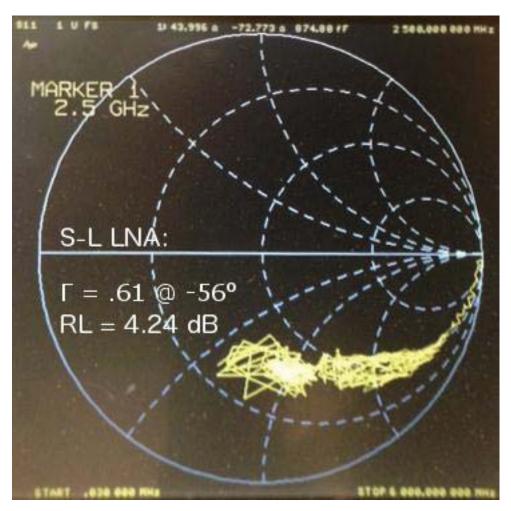

Lastly, a case for the suspected design and layout faults, which caused fabricated versions of the RFD and two LNAs documented in this thesis to fail, is presented. First, measurements of the two LNAs are shown, which display the input impedance of the S-L LNA and the  $s_{21}$  responses for both. Then, general layout concerns are addressed, followed by topology-specific circuit design flaws.

## **Table of Contents**

| List of Figures                                        | viii |

|--------------------------------------------------------|------|

| Acknowledgements                                       | xi   |

| Dedication                                             | xii  |

| Chapter 1 - Introduction                               | 1    |

| 1.1 Objective                                          | 1    |

| 1.2 Background                                         | 1    |

| 1.2.1 Divide-by-2 Injection-Locked Frequency Dividers  | 1    |

| 1.2.2 Low Noise Amplifiers                             | 2    |

| Noise Figure of Cascaded Systems                       | 3    |

| Optimizing Circuit Noise Figure                        | 6    |

| Chapter 2 - Background Theory and The State of The Art | 7    |

| 2.1 Divide-by-2 Injection-Locked Frequency Dividers    | 7    |

| 2.1.1 "Tail-ILFDs"                                     | 9    |

| 2.1.2 "Quench" ILFDs                                   | 13   |

| 2.1.3 Regenerative ILFDs                               | 15   |

| 2.2 Low Noise Amplifiers                               | 16   |

| 2.2.1 Impedance Matching Techniques                    | 17   |

| Wideband Designs                                       | 17   |

| Resistive termination                                  | 17   |

| Source Termination                                     | 22   |

| Shunt-Shunt Resistive Feedback                         | 24   |

| Narrowband Designs                                     | 25   |

| LC Matching Network                                    | 25   |

| 2.2.2 g <sub>m</sub> -Boosting Techniques              | 27   |

| Device Coupling Designs                                | 27   |

| Cascode Amplifier                                      | 28   |

| Active Coupling                                     | 29 |

|-----------------------------------------------------|----|

| Reactive Designs                                    | 30 |

| Common-Source Amplifier with Tuned Load             | 30 |

| Source-Inductor (S-L) Amplifier                     | 32 |

| 2.2.3 Active Noise Cancelling Techniques            | 34 |

| Common Gate – Common Source (CG-CS) LNA             | 35 |

| Cross-Coupled (CC) LNA                              | 37 |

| Differential Partial Noise Cancelling LNA           | 38 |

| 2.3 LNA Large-Signal Performance                    | 40 |

| 2.3.1 Compression of LNAs                           | 40 |

| 2.3.2 One-dB Dynamic Range                          | 42 |

| 2.3.3 Third Order Input and Output Intercept Points | 43 |

| Chapter 3 - Frequency Dividers                      | 44 |

| 3.1 Detailed Theory of Operation                    | 44 |

| 3.1.1 Injection Locked Frequency Dividers           | 44 |

| Injection Locking                                   | 44 |

| Reduction of Phase Noise                            | 48 |

| 3.1.2 Regenerative Frequency Dividers               | 51 |

| 3.2 CMOS Frequency Divider Implementations          | 51 |

| 3.2.1 Injection Locked Frequency Dividers           | 51 |

| Tail Injection Mode Operation                       | 52 |

| Quench Injection Locked Operation                   | 53 |

| 3.2.2 Regenerative Frequency Divider                | 56 |

| 3.3 Performance of Frequency Dividers               | 59 |

| 3.3.1 Injection Locked Frequency Dividers           | 60 |

| Tail-ILFD Locking Range Measurements                | 61 |

| Quench-ILFD Locking Range Measurements              | 62 |

| Phase Noise Measurements.                           | 65 |

| 3.3.2 Regenerative Frequency Divider                | 66 |

| Chapter 4 - Low Noise Amplifiers                     | 70  |

|------------------------------------------------------|-----|

| 4.1 Theory of Operation                              | 72  |

| 4.1.1 Cascode Source-Inductor Low Noise Amplifier    | 72  |

| Small Signal Parameters                              | 73  |

| Noise Figure                                         | 75  |

| Large Signal Parameters                              | 79  |

| 4.1.2 Partial Noise Cancelling Low Noise Amplifier   | 80  |

| Small Signal Parameters                              | 81  |

| Noise Figure                                         | 86  |

| Large Signal Parameters                              | 96  |

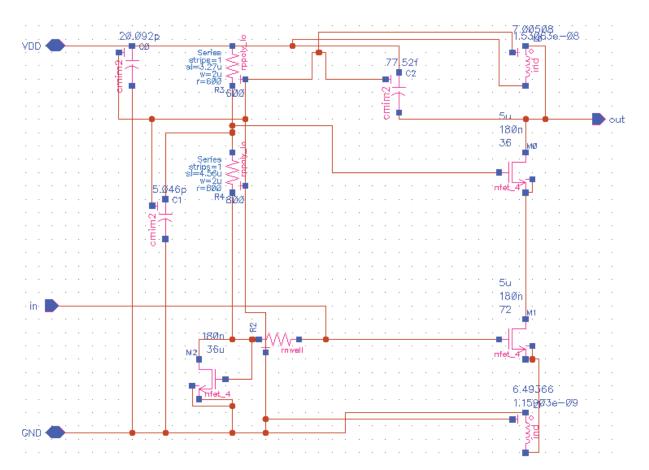

| 4.2 2.4-GHz CMOS Low Noise Amplifier Implementations | 97  |

| 4.2.1 Source-Inductor Low Noise Amplifier            | 97  |

| 4.2.2 Partial Noise Cancelling Low Noise Amplifier   | 99  |

| 4.3 Performance of Low Noise Amplifiers              | 102 |

| 4.3.1 Source-Inductor Low Noise Amplifier            | 103 |

| 4.3.2 Partial Noise Cancelling Low Noise Amplifier   | 108 |

| 4.4 Design and Suspected Device Layout Faults        | 114 |

| 4.4.1 Source-Inductor Low Noise Amplifier            | 119 |

| 4.4.2 Partial Noise Cancelling Low Noise Amplifier   | 121 |

| Chapter 5 - Conclusion and Future Works              | 122 |

| 5.1 Conclusions                                      | 122 |

| 5.1.1 Frequency Dividers                             | 122 |

| Injection Locked Frequency Dividers                  | 122 |

| Regenerative Frequency Dividers                      | 122 |

| 5.1.2 Low Noise Amplifiers                           | 123 |

| 5.2 Future Works                                     | 124 |

| 5.2.1 Frequency Dividers                             | 124 |

| 5.2.2 Low Noise Amplifiers                           | 125 |

| Changes to Layout                                    | 125 |

| References                                       | 127 |

|--------------------------------------------------|-----|

| Appendix A - 2.4-GHz Buffer Schematic and Layout | 129 |

# **List of Figures**

| Figure 1.1 Modern PLL Architecture                                         | 2  |

|----------------------------------------------------------------------------|----|

| Figure 1.2 Signal source followed by two cascaded 2PNs and load impedance  | 3  |

| Figure 2.1 SCL Divide-by-2 Circuit                                         | 7  |

| Figure 2.2 ILFD Block Diagram.                                             | 8  |

| Figure 2.3 Generic Tail-ILFD                                               | 10 |

| Figure 2.4 Switch-Based Single-balanced Mixer Scheme.                      | 11 |

| Figure 2.5 Frequency Spectrum of Arbitrary Square Wave                     | 12 |

| Figure 2.6 The Mixing of Two Signals                                       | 13 |

| Figure 2.7 Generic Quench-ILFD                                             | 14 |

| Figure 2.8 Transient Synchronization Mechanism of Quench-ILFD              | 15 |

| Figure 2.9 Regenerative Frequency Divider Block Diagram                    | 16 |

| Figure 2.10 Resistive Input Termination                                    | 17 |

| Figure 2.11 LNA Employing Resistive Input Termination                      | 18 |

| Figure 2.12 Simplified Noise Models for Resistance and MOSFET              | 19 |

| Figure 2.13 Simplified Noise Circuit of Resistive Termination LNA          | 20 |

| Figure 2.14 Simplified Noise Circuit of Source Termination CG LNA          | 23 |

| Figure 2.15 Simplified Noise Circuit of Shunt-Shunt Resistive Feedback LNA | 24 |

| Figure 2.16 Simplified Noise Circuit of LNA employing LC Matching Network  | 26 |

| Figure 2.17 Simplified Noise Circuit of Cascode Amplifier                  | 28 |

| Figure 2.18 Simplified Noise Circuit of Active Coupled LNA                 | 29 |

| Figure 2.19 Simplified Noise Circuit of CS Tuned Load LNA\                 | 31 |

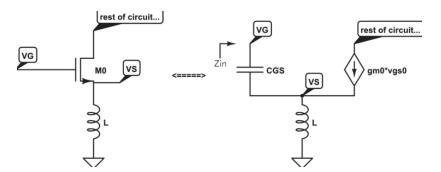

| Figure 2.20 Input Impedance of FET with Source Inductance                  | 32 |

| Figure 2.21 Simplified Noise Circuit of S-L LNA                            | 33 |

| Figure 2.22 Simplified Noise Circuit CG-CS LNA                             | 35 |

| Figure 2.23 Simplified Noise Circuit CC LNA                                | 37 |

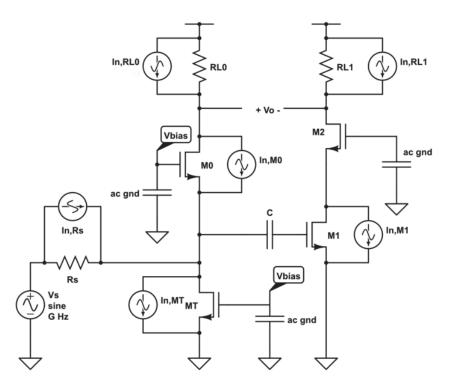

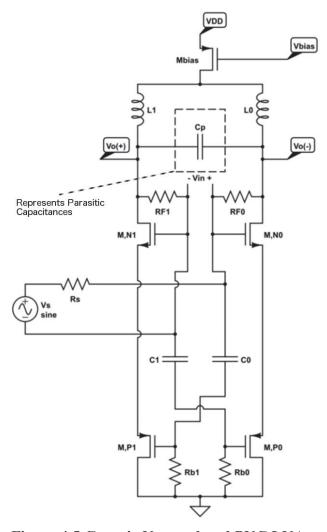

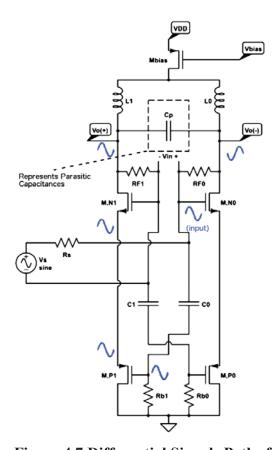

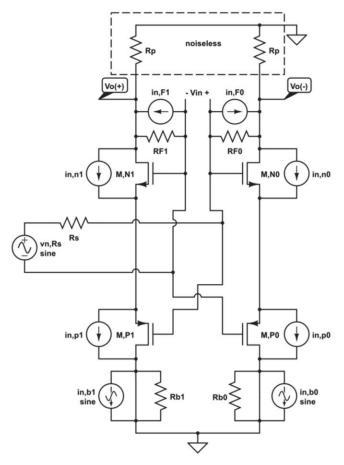

| Figure 2.24 Schematic of narrowband PNC LNA                                | 39 |

| Figure 2.25 Input-Referred and Output-Referred Compression                 | 41 |

| Figure 3.1 Model of Active Oscillator (after Adler)                                    | 45 |

|----------------------------------------------------------------------------------------|----|

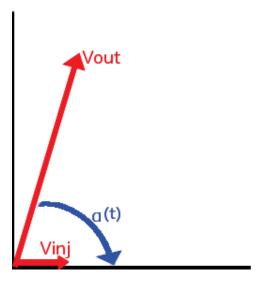

| Figure 3.2 Phasor Diagram of Output Signal and Injection Signal (after Adler)          | 46 |

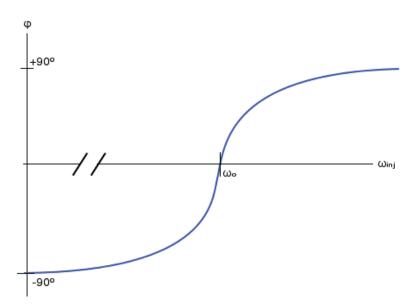

| Figure 3.3 Phase between Input and Output Signals vs Injection Frequency (after Adler) | 47 |

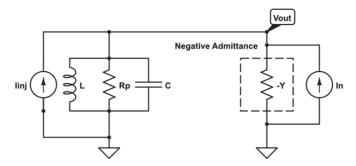

| Figure 3.4 Model for Oscillator Phase Noise under Injection Locking (after Razavi)     | 49 |

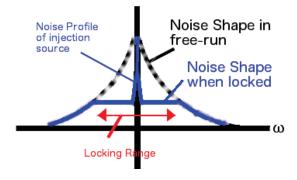

| Figure 3.5 Oscillator Phase Noise in Free-Run and Injection-Locked Mode (after Razavi) | 50 |

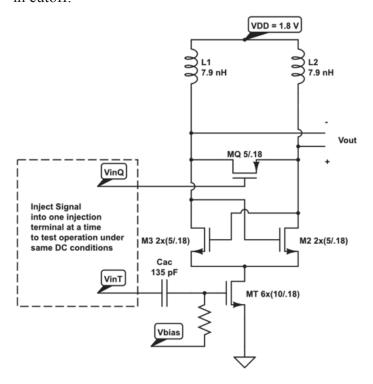

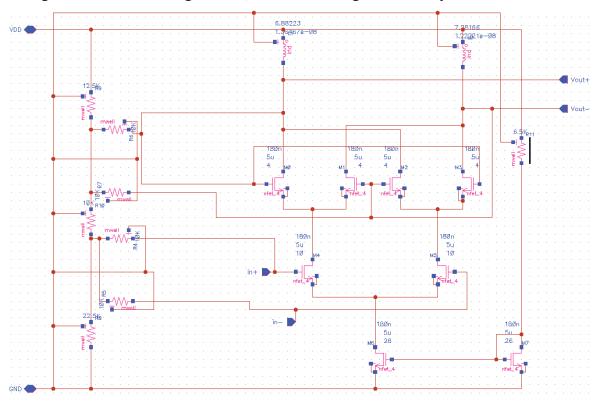

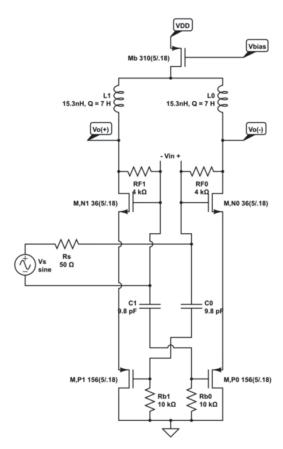

| Figure 3.6 Schematic of Tail and Quench-ILFDs using Cadence ICFB                       | 52 |

| Figure 3.7 Schematic of Tail and Quench-ILFDs                                          | 54 |

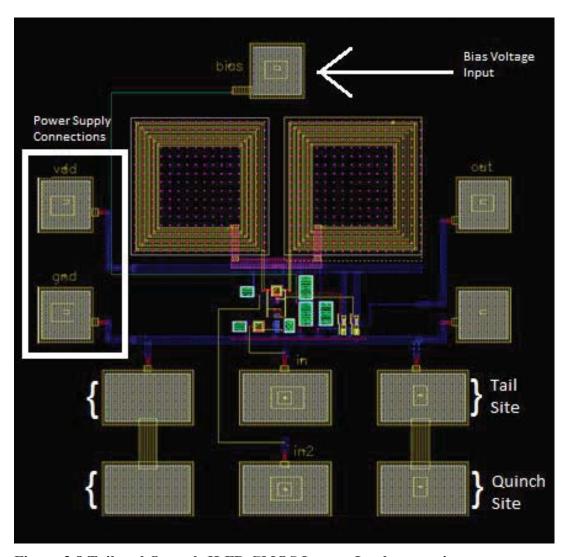

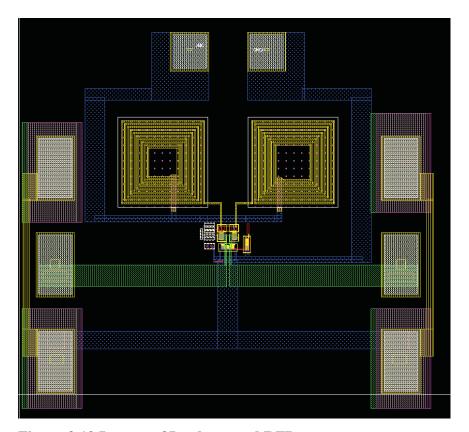

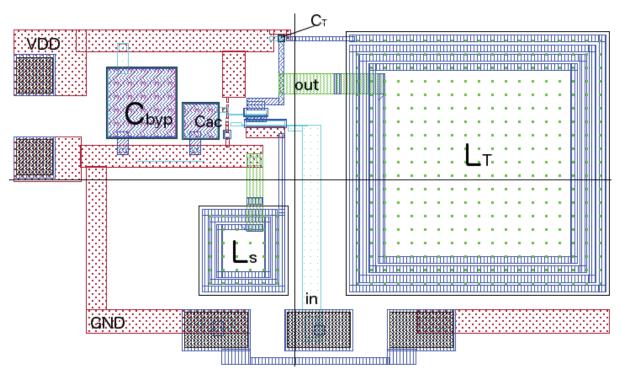

| Figure 3.8 Tail and Quench-ILFD CMOS Layout Implementations                            | 55 |

| Figure 3.9 Implemented RFD Schematic.                                                  | 56 |

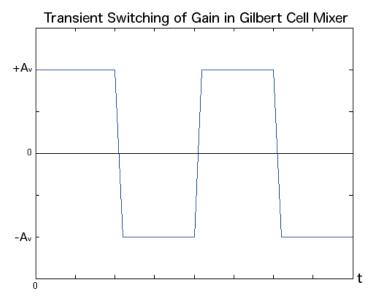

| Figure 3.10 Transient Switching of Gain in Gilbert Cell Mixer                          | 57 |

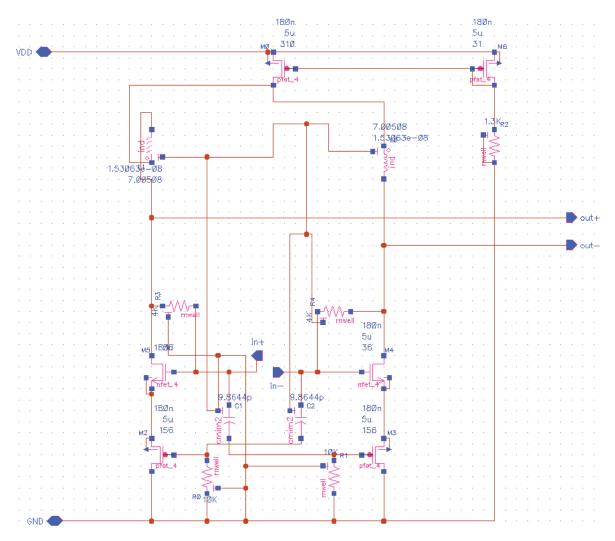

| Figure 3.11 Schematic of RFD Implemented in ICFB                                       | 58 |

| Figure 3.12 Layout of Implemented RFD.                                                 | 59 |

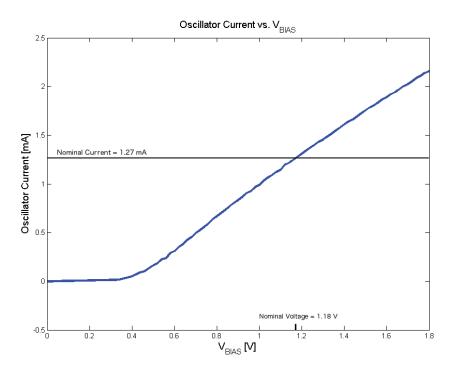

| Figure 3.13 Oscillator Current as a Function of Applied $V_{BIAS}$                     | 60 |

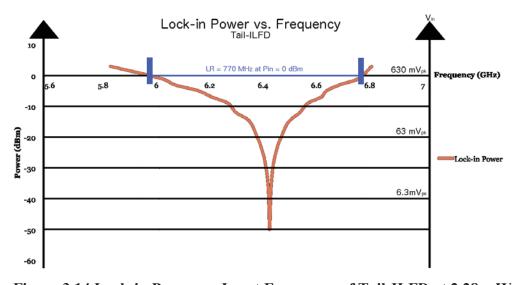

| Figure 3.14 Lock-in Power vs. Input Frequency of Tail-ILFD at 2.28 mW dc               | 61 |

| Figure 3.15 Lock-in Power vs. Input Frequency of Quench-ILFD at 2.28 mW dc             | 63 |

| Figure 3.16 Lock-in Power vs. Input Frequency of Quench-ILFD at 219.6 μW DC            | 64 |

| Figure 3.17 Output Spectrum and Phase Noise of locked ILFD                             | 65 |

| Figure 3.18 Testbench Setup used to Simulate RFD in Cadence ICFB                       | 67 |

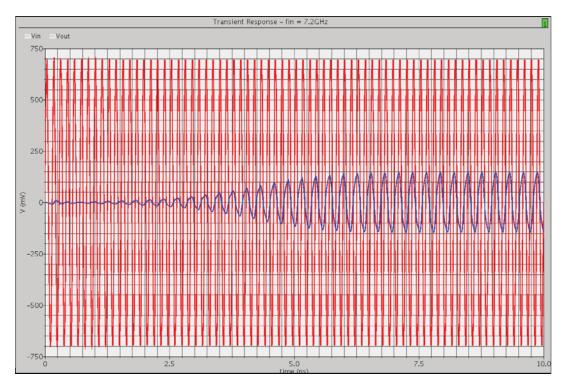

| Figure 3.19 Simulation of Lower-Bound of Divisible Frequencies                         | 68 |

| Figure 3.20 Simulation of Upper-Bound of Divisible Frequencies                         | 68 |

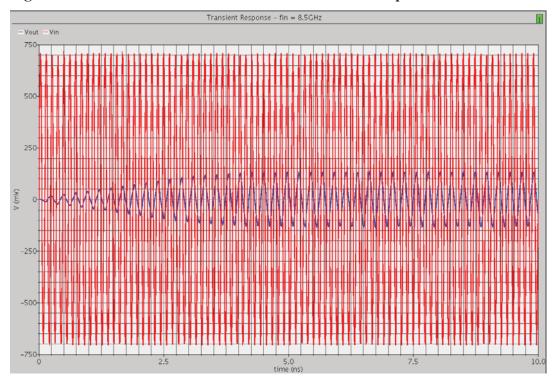

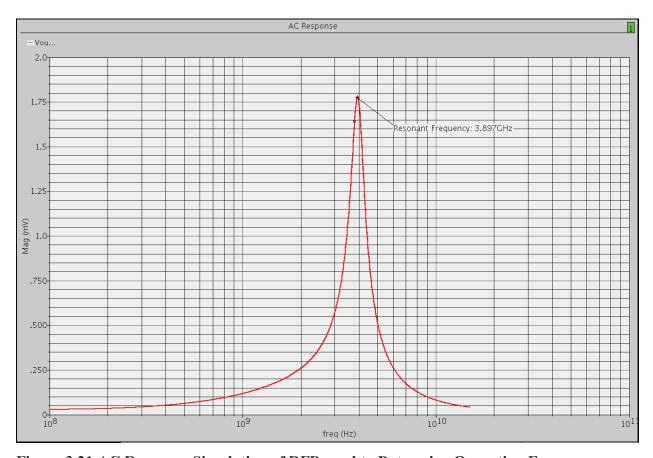

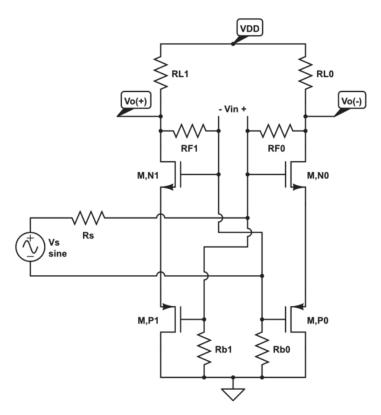

| Figure 3.21 AC Response Simulation of RFD used to Determine Operating Frequency        | 69 |

| Figure 4.1 Simplified Schematic of LNA Presented in [1]                                | 70 |

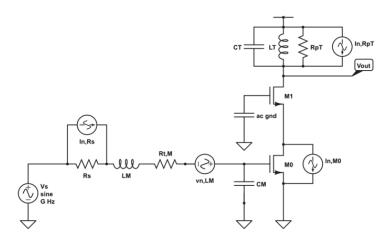

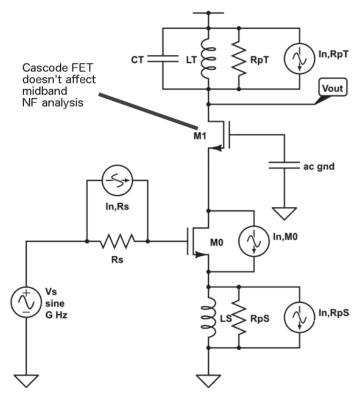

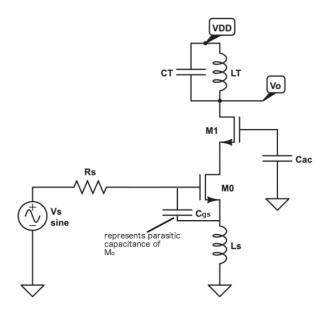

| Figure 4.2 Generic Cascode S-L LNA Schematic                                           | 72 |

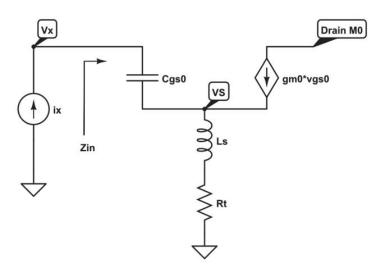

| Figure 4.3 Small-Signal Model used to obtain Input Impedance and Voltage Gain          | 73 |

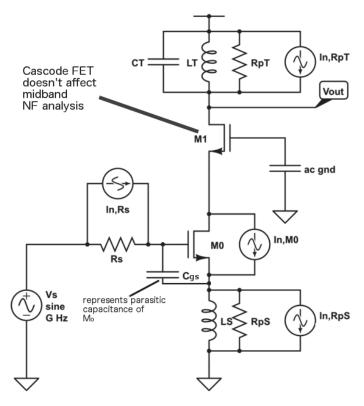

| Figure 4.4 Thermal Noise Model of S-L LNA                                              | 76 |

| Figure 4.5 Generic Narrowband PNC LNA                                                  | 81 |

| Figure 4.6 Half-Circuit Model of PNC LNA used to Determine Input Impedance             | 82 |

| Figure 4.7 Differential Signals Paths for Half-Circuit PNC LNA                         | 84 |

| Figure 4.8 Small Signal Model to Obtain $v_{o,(-)}/v_{in,(-)}$ of PNC LNA              | 85 |

| Figure 4.9 Midband Thermal Noise Model of PNC LNA                                   | 87  |

|-------------------------------------------------------------------------------------|-----|

| Figure 4.10 Half-Circuit Small Signal Model used to Obtain nFET Noise Contributions | 88  |

| Figure 4.11 Second Half-Circuit Model used to Obtain nFET Noise Contributions       | 90  |

| Figure 4.12 Small-Signal Model used to Determine Noise of Feedback Resistors        | 94  |

| Figure 4.13 Simplified Schematic of Implemented S-L LNA                             | 97  |

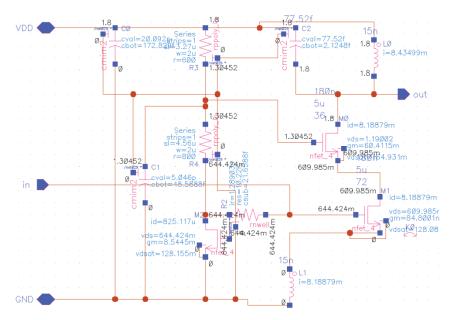

| Figure 4.14 Schematic of Implemented S-L LNA using Cadence Virtuoso ICFB            | 98  |

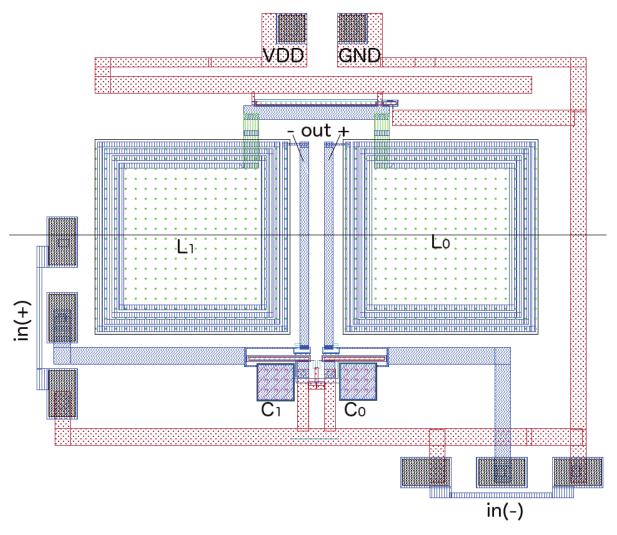

| Figure 4.15 Annotated Layout of Implemented S-L LNA using Cadence Virtuoso ICFB     | 99  |

| Figure 4.16 Simplified Schematic of Implemented PNC LNA                             | 100 |

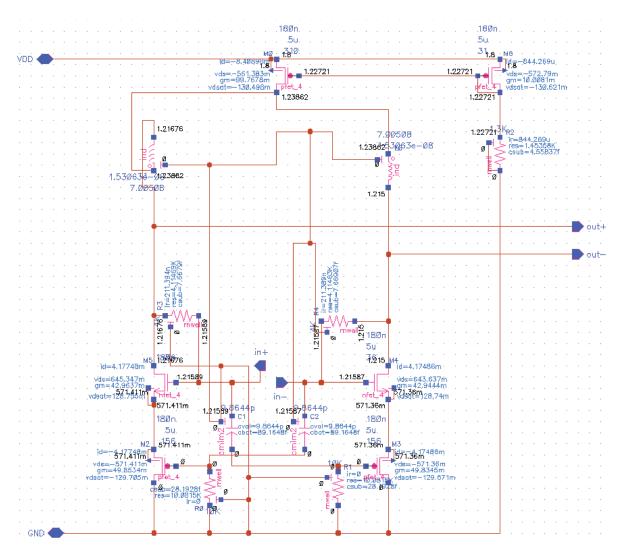

| Figure 4.17 Schematic of Implemented PNC LNA using Cadence Virtuoso ICFB            | 101 |

| Figure 4.18 Annotated Layout of Implemented PNC LNA using Cadence Virtuoso ICFB     | 102 |

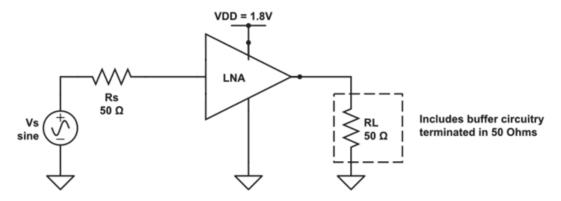

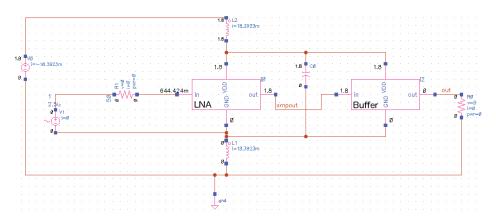

| Figure 4.19 Simulated LNA "Testbench" Environment.                                  | 103 |

| Figure 4.20 Annotated Layout of Implemented S-L LNA using Cadence Virtuoso ICFB     | 104 |

| Figure 4.21 Testbench Schematic of S-L LNA using Cadence Virtuoso                   | 104 |

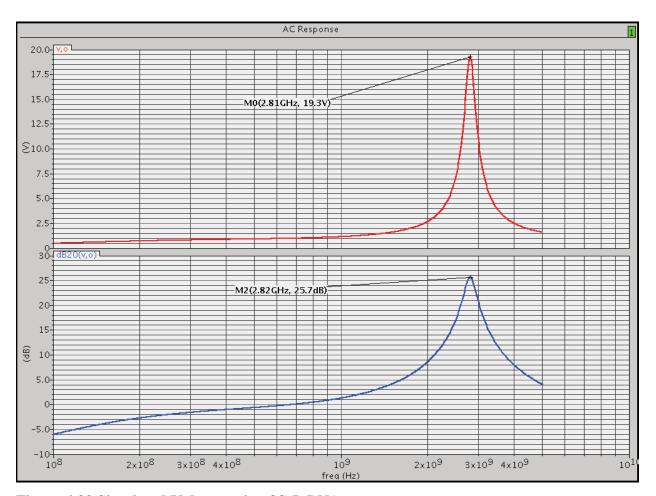

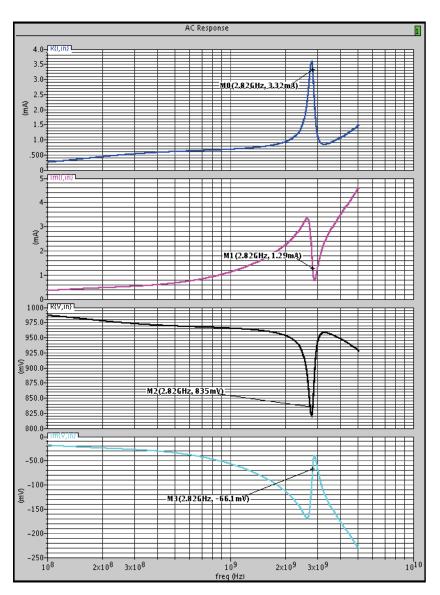

| Figure 4.22 Simulated Voltage gain of S-L LNA                                       | 105 |

| Figure 4.23 Simulated Input Impedance of S-L LNA                                    | 106 |

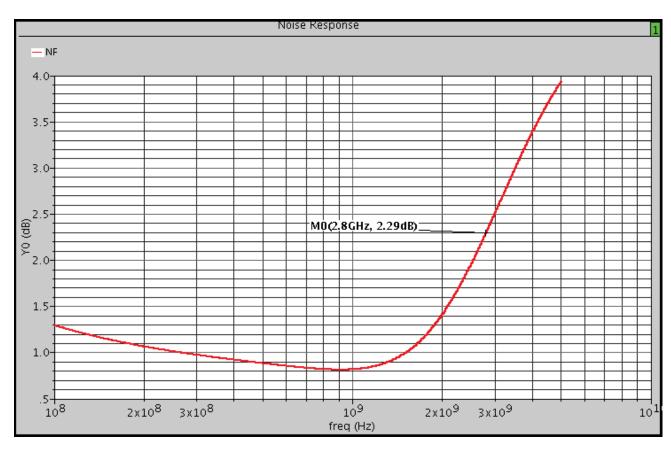

| Figure 4.24 Simulation of Noise Figure of S-L LNA                                   | 107 |

| Figure 4.25 Annotated Layout of Implemented PNC LNA using Cadence Virtuoso          | 109 |

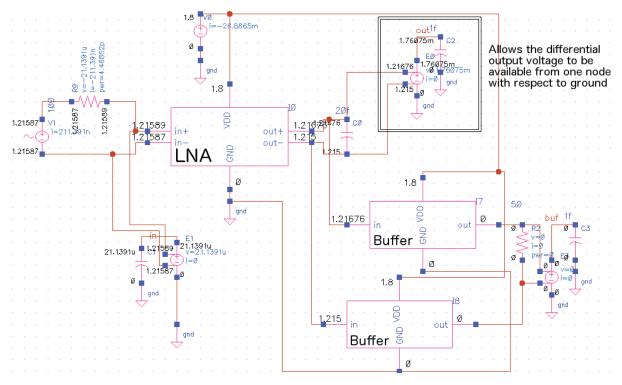

| Figure 4.26 Testbench Schematic of PNC LNA using Cadence Virtuoso                   | 110 |

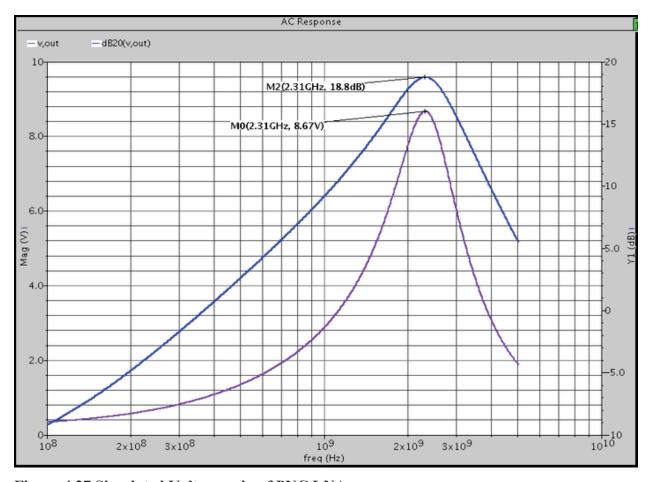

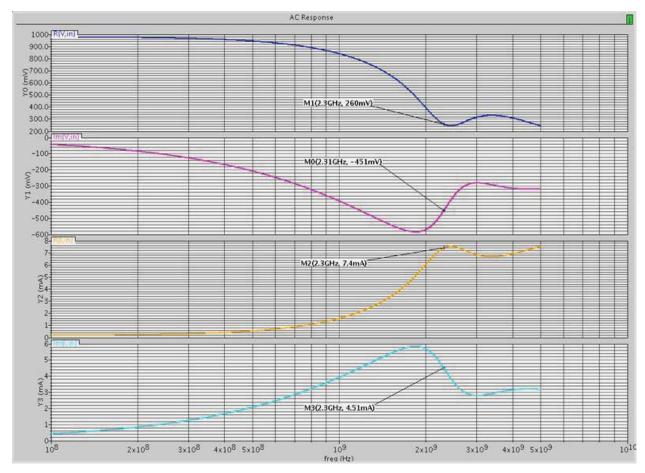

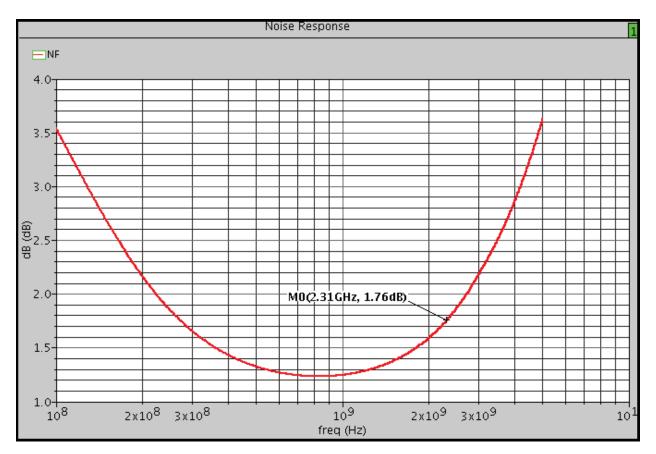

| Figure 4.27 Simulated Voltage gain of PNC LNA                                       | 111 |

| Figure 4.28 Simulated Input Impedance of PNC LNA.                                   | 112 |

| Figure 4.29 Simulated Output Noise Voltage of PNC LNA                               | 113 |

| Figure 4.30 Measured s <sub>21</sub> of Implemented S-L LNA in CMOS                 | 115 |

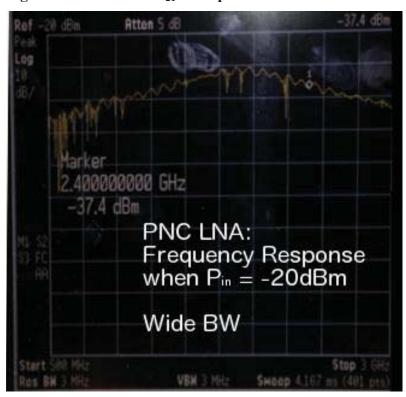

| Figure 4.31 Measured s <sub>21</sub> of Implemented PNC LNA in .180μ CMOS           | 115 |

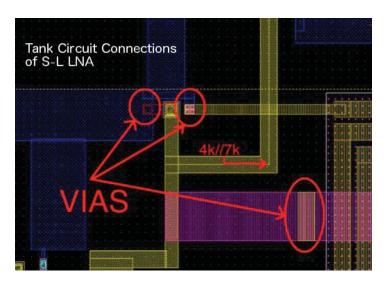

| Figure 4.32 Layout Close-up of S-L LNA Tuned Load                                   | 117 |

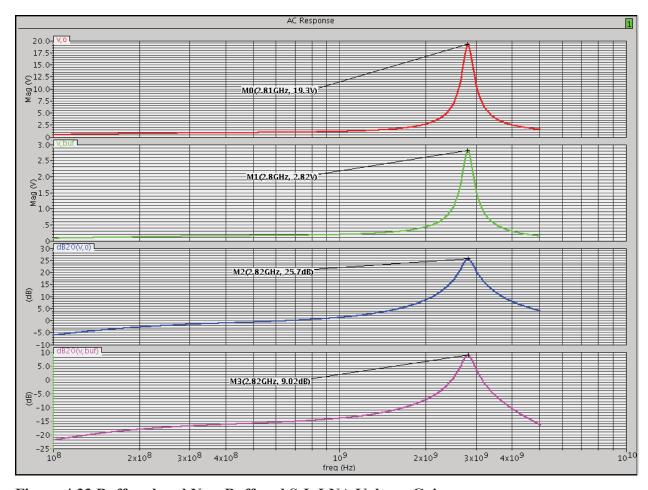

| Figure 4.33 Buffered and Non-Buffered S-L LNA Voltage Gain                          | 118 |

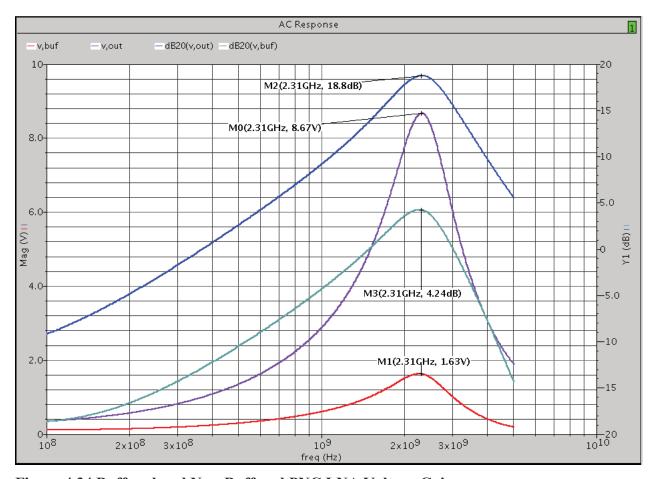

| Figure 4.34 Buffered and Non-Buffered PNC LNA Voltage Gain                          | 119 |

| Figure 4.35 Measured Input Impedance of S-L LNA                                     | 120 |

## Acknowledgements

This research was funded in part by Sandia National Laboratories. The author would like to thank Sandia for their support. Sandia National Laboratories is a multi-program laboratory managed and operated by Sandia Corporation, a wholly owned subsidiary of Lockheed Martin Corporation, for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-AC04-94AL85000.

I would like to thank my graduate advising professor, Dr. William B. Kuhn. Because of his dedicated guidance and unparalleled insight in electronics, I am confident in the engineering skills I have developed through my education. May his deep insight in the field continue to forward Kansas State University's contributions to modern science.

I would also like to thank my other committee members Dr. Stephen Dyer and Dr. Punit Prakash.

I took Electronics II with Dr. Dyer, a class that set up my path into the world of RFIC design. As a student, Dr. Dyer not only answered all of my off-the-wall questions and encouraged my curiosity, but also spent countless hours after class with me helping to develop my intuition and knowledge regarding the field of electronic design. He was and is my main inspiration.

## **Dedication**

First and foremost, I'd like to dedicate this work to my ever-loving parents, Sinaa Abdulamir and Imad Khamis. My mother, a mechanical engineer, and my father, a professor of statistics, always emphasized the importance of a strong education. Originally immigrating to the USA from Iraq in 1990, my parents witnessed their fair share of hardships, both culturally and financially. Despite raising 5 children on the meager "salary" of a Ph.D. graduate student, my parents always found the time to support me in my academic endeavors – whether that implied helping me with my homework during elementary school, or fiercely disciplining me when my performance was…less than satisfactory. After what seemed an eternity, my parents encouraged me to pursue electrical engineering upon graduation from high school, and never once doubted my abilities to overcome any challenge in my way. I can only hope that I've made my parents as proud as they have made me.

I must also thank my siblings: Marwa, Faddy, Jumanna, and Rami. Marwa, my eldest sister, always provided an excellent example as a student for me to follow, and witnessing her success as a pharmacist inspired me to finish the electrical engineering curriculum. Faddy, my younger brother by three years, is a soon-to-be medical student, and his MCAT score speaks for itself. With an impressive GPA, endless volunteer hours, and a history of leadership in his classes - I have no doubt that he will be very successful when he enters medical school. Jumanna, my younger sister who is in her early years of university, is a bright and edgy young lady who learned to think for herself at an early age. My youngest sibling, Rami, is a very intelligent middle school student who has outpaced the rest of us by far in terms of intelligence and maturity. I love and wish you all the best, and I know your successes will know no earthly bounds.

I'd also like to dedicate this to my closest childhood homies: Ayman Al-Ashtal and Sam Gharaibeh. While I was still a young man, Ayman set an unwavering and unmatched example of what true courage, heart, respect, and intelligence is. I have never met anyone who is more genuine and fearless than he. I hope with all my heart that we meet again soon and get back to where we was. Sam taught me the importance of questioning everything I believe to be true and

re-evaluating deep, personal beliefs on the basis of what I believe to be right in my heart. Talented, witty, and the most emotionally-intelligent person I know – I hope Sam continues to provide me with the advice that has improved my life over the several years that I've known him. Without Sam's one-of-a-kind advice and unique, cosmic perspective on life, I would not be the happy person I am today. You guys are my brothers.

Lastly, I'd also like to dedicate this thesis to Tifani "Tiffers" Sellers. As a truly caring, loving, and confident young lady – Tiffers embodies grace that is perpetually maintained, no matter what life may throw at her. Tiffers is a refreshingly honest woman that doesn't hesitate to speak her mind, and never sacrifices a shred of tact. Positively beautiful, inside and out. Thank you so much for keeping me company and supporting me while I wrote this thesis. Without you, I would have lost my mind a lot sooner than I did. Ha. I wish you nothing but the best in all your future endeavors.

## **Chapter 1 - Introduction**

### 1.1 Objective

This thesis focuses on two critical subcircuits needed to implement low power, high frequency radio receivers: analog Injection-Locked Divide-by-2 Prescalars and Low Noise Amplifiers (LNAs). Chapter 1 explains the background and motivation that drive the need for LNAs and Frequency Dividers in modern radio applications. In chapter 2, prior art and current industry implementations for these two subsystems will be explained in terms of performance features and limitations. Chapter 3 elaborates the theory, analysis, design, simulation, and layout of (i) a "Quench" Injection-Locked Frequency Divider (ILFD), (ii) a "Tail" ILFD, and then (iii) a Regenerative Frequency Divider (RFD), also known as a "Miller Divider". Next, Chapter 4 reports the theory, analysis, design, simulation, and layout of (i) a Source-Inductor LNA (S-L LNA) and (ii) a Partial Noise-Cancelling LNA (PNC-LNA) based on the works of [1]. Finally, Chapter 5 concludes the document by summarizing and comparing the performance of the researched Frequency Divider and LNA topologies.

## 1.2 Background

## 1.2.1 Divide-by-2 Injection-Locked Frequency Dividers

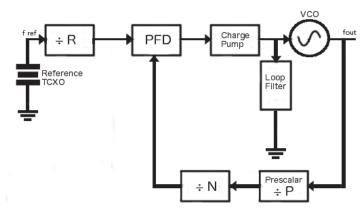

ILFDs are extensively used in Phase-Locked-Loop (PLL) Frequency Synthesizers, or simply "PLLs". Ideally, a PLL provides a stable output frequency with minimized *phase noise*. PLL's are used in a variety of RFIC subsystems, for both transmit and receive operations. Figure 1.1 shows the architecture of a modern PLL implementation. A stable reference frequency is generated using a temperature-compensated crystal oscillator (TCXO). This signal is divided by some value *R*. A Phase-Frequency Detector (PFD) provides a signal proportional to the difference in phase (or frequency) between the reference signal and the output signal, after being

divided by both *P* and *N*, respectively. This signal drives the Charge Pump that provides the tuning voltage to a VCO. The loop filter (lowpass type) is necessary for stability and to control the dynamics and response time of the feedback system.

Figure 1.1 Modern PLL Architecture

The output frequency generated by such a PLL can be expressed as:

$$f_o = \left(\frac{f_{ref}}{R}\right) NP \tag{1.1}$$

and the minimum step size is:

$$f_{step} = \left(\frac{f_{ref}}{R}\right) P \tag{1.2}$$

As a result, the prescalar block is a determining factor of the range of frequencies that can be generated, unless a fractional-N architecture is used [3] [4].

The reason prescalars need to be used in the first place is because the digital circuitry that composes the divide-by-N block in Figure 1.1 is often too slow to process the higher GHz frequencies employed in newer wireless receivers. Using a prescalar subverts this issue, by providing the digital circuitry with a lower frequency input that can be properly divided. As a result, the development of ILFDs remains a strong subject of interest among RFIC researchers.

#### 1.2.2 Low Noise Amplifiers

Low Noise Amplifiers serve as the first active stage for typical receiver architectures. The LNA and the passive circuitry that precedes it compose what is often referred to as the "front end" of a radio receiver. As the first active stage, the LNA determines many performance metrics of the entire radio system, such as the receiver sensitivity, out-of-band IIP3, and dynamic range. As mobile consumer technologies continue to support high-data and high-speed transmissions, it is paramount that these devices maintain sufficient operation in the context of these characterizations, while remaining low power. Unlike intermediate frequency (IF) amplifiers, buffer amplifiers, or chained amplifiers that typically appear in RF receivers, the design of LNAs requires input matching, gain boosting, noise cancelling, and frequency selective techniques in order to optimize receiver performance metrics, such as Noise Figure.

#### Noise Figure of Cascaded Systems

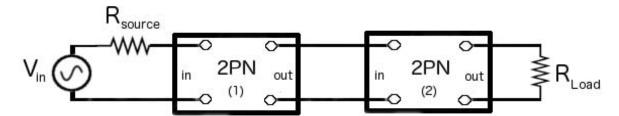

A receiver's *Noise Figure* (referred to as "F") is primarily established by the first stage in a cascaded network, if the gain of that stage is sufficiently large. H. T. Friis showed this in [2]. To illustrate this important point, consider Figure 1.2, which depicts a signal generator of voltage  $V_{in}$  with Thevenin impedance  $R_{source}$  and two cascaded 2-Port Networks (2PNs) with the second 2PN connected to a load:

Figure 1.2 Signal source followed by two cascaded 2PNs and load impedance

In the context of communication circuits, the above figure represents a receiver front-end consisting of an antenna of impedance  $R_{source}$ , an LNA, followed by perhaps an amplifying, mixing, or filtering stage.  $2PN_1$  represents the LNA and  $2PN_2$  represents the next stage.

A voltage source, such as  $V_{in}$ , provides maximum power transfer to a load when the next stage's input impedance is *matched* to the source impedance, i.e.  $R_{source} = R_{2PN,in}$ . When this is true, the maximum available signal power can be described by:

$$P_{signal} = \frac{[V_{in}(\frac{R}{R+R})]^2}{R} = \frac{V_{in}^2}{4R_{source}} = S_0$$

(1.3)

where R indicates both the source impedance and the input impedance of  $2PN_I$ . Next, a signal source of Thevenin resistance R will produce thermal noise power of magnitude:

$$P_{noise} = kTB \tag{1.4}$$

delivered to a matched load, where k is Boltzmann's constant (1.38x10<sup>-23</sup> J/ $^{\circ}$ K), T is the absolute temperature of the operating circuitry (typically 290  $^{\circ}$ K in room-temperature, low power devices), and B is the *effective* bandwidth of the receiver system. This bandwidth is typically set by the off-chip BPF, the LNA, or both.

To illustrate a typical figure of a modern receiver, consider a Bluetooth device operating at 2.45 GHz, with a bandwidth of 245 MHz. For the signal and noise powers given here, the SNR can be defined as:

$$SNR_{input} = \frac{S_0}{kTB} \tag{1.5}$$

The noise power produced by the source impedance appears at the input terminals of  $2PN_I$ , which is amplified by the network's power gain  $G_I$ . Due to the internal circuitry that comprises  $2PN_I$ , additional noise will be introduced because of thermal effects from individual circuit elements. Considering this additional noise, the total available noise power at the output terminals of  $2PN_I$  is:

$$P_{noise2PN1out} = F_1 G_1 kTB (1.6)$$

where  $F_1 \ge 1$  to account for the excess noise introduced. Similarly, the noise power that appears at the inputs of  $2PN_2$  will also be amplified, this time by the gain of the second network  $G_2$ . Now the total noise power at the output terminals of  $2PN_2$  can be expressed as:

$$P_{noise,2PN2out} = F_{12} G_1 G_2 kTB$$

(1.7)

$F_{12}$  represents the noise figure of the comprehensive system consisting of networks  $2PN_1$  and  $2PN_2$ . However, as  $2PN_2$  likely also contains thermal noise generating circuitry, it too will also have its own individual contribution to total available noise power at its output terminals. The noise power due solely to  $2PN_2$  is:

$$P_{noise,2PN2} = (F_2 - 1)G_2kTB \tag{1.8}$$

Whereas the noise contribution due to the circuitry of  $2PN_1$  is:

$$P_{noiss,2PN1} = (F_1 - 1)G_1G_2kTB (1.9)$$

Note that the  $(F_i - 1)$  factor originates from the fact that the initial kTB noise was introduced by the signal source, which is subtracted out to obtain the noise contribution of only the 2PN of interest. Another observation from the above expressions is that the noise power of the first 2PN is amplified twice before appearing at the load. The noise power of the second 2PN is only amplified once. To illustrate the consequence of this fact on the total system noise figure, consider the expression for total available noise power at the output terminals of  $2PN_2$ , due to each stage's own contribution:

$$\begin{split} P_{noise,2PN2out} &= G_1 G_2 k T B + (F_1 - 1) G_1 G_2 k T B + (F_2 - 1) G_2 k T B \\ &= G_1 G_2 k T B [1 + (F_1 - 1) + \frac{F_2 - 1}{G_1}] \\ &= G_1 G_2 k T B [F_1 + \frac{F_2 - 1}{G_2}] \end{split} \tag{1.10}$$

Equating this to (1.7) shows:

$$P_{noise,2PN2out} = G_1 G_2 kTB \left[ F_1 + \frac{F_2 - 1}{G_1} \right] = F_{12} G_1 G_2 kTB$$

(1.11)

Dividing both sides by the similar terms shows that the noise figure describing the entire system of 2PNs results in:

$$F_{12} = F_1 + \frac{F_2 - 1}{G_1} \tag{1.12}$$

so that for a system of power-amplifying stages, the noise figure is dominated by the first stage, if it is of sufficient power gain  $G_1$ . Expanding this analysis to a chain of 3 2PNs would reveal:

$$F_{123} = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 G_2}$$

(1.13)

#### Optimizing Circuit Noise Figure

To understand how to optimize the noise figure of a single stage such as  $F_1$ , consider the expression for the noise figure of a system composed of a signal source, one amplifying stage (such as an LNA), and a load impedance:

$$F = \frac{N_{out}}{N_{in}G} = \frac{N_{in}G + N_{sys}}{N_{in}G} = 1 + \frac{N_{sys}}{N_{in}G}$$

(1.14)

This suggests that for a low noise figure, the noise contribution from the stage's circuit should be minimized while keeping its power gain large in magnitude. The expression also implies a minimum theoretical noise figure of unity for a noise-less network, where all the noise power would have originated at the signal source.

Many different circuit-level techniques for the development of LNAs that optimize the above criterion have been researched and developed since the establishment of noise figure [5] [6]. In RF-tuned circuits, reactive components are used to provide matching and associated highgain and low-noise paths for received signals. In wideband applications, where frequency-selective components are not usable, methods of noise figure improvement have begun to focus more on clever CMOS topologies, such as "noise cancellation" [1].

Both wideband and narrowband receivers can benefit from noise-cancellation architectures. Many methods of noise cancelling in FET circuits have been developed, using active coupling, differential circuits, and/or feedback to mitigate individual FET noise contribution [6] [8]. These circuits often employ g<sub>m</sub>-boosting techniques and impedance matching as well. The study of LNA design techniques in this thesis focuses on adopting recently developed wideband noise cancellation circuits to narrowband LNAs to achieve good performance in terms of both noise figure and large-signal processing capabilities.

## **Chapter 2 - Background Theory and The State of The Art**

## 2.1 Divide-by-2 Injection-Locked Frequency Dividers

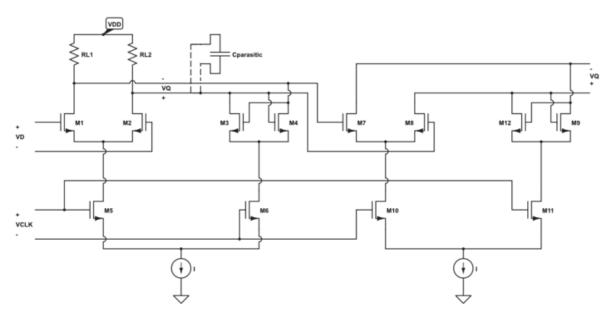

The output frequencies needed in modern PLL circuits are well into the GHz range, which is too high for programmable digital dividers, thus the need for prescalars. In the past, a common approach has been to use a high-speed Source Coupled Logic (SCL) divide-by-2 circuit based on the D flip-flop architecture [7]. Figure 2.1 shows such a circuit:

Figure 2.1 SCL Divide-by-2 Circuit

For the divider in figure 2.1, when  $V_{CLK}$  is positive, the first latch is transparent, and a differential voltage  $V_Q$  is established. FETs  $M_1$  and  $M_2$  form the "D" input. When  $V_{CLK}$  is negative, the cross-coupled pair formed by  $M_3$  and  $M_4$  latch the state and provides a fixed output to the second latch, which is now transparent. The maximum frequency this circuit can operate at is determined by:

$$\tau = \frac{c_{parasitic}}{\left(\frac{1}{R_L} - g_m\right)} \tag{2.1}$$

In current practice,  $f_{max}$  tends to be limited to ~3GHz, due to the parasitic capacitances illustrated in Figure 2.1. The capacitor  $C_{parasitic}$  represents the capacitance formed by the differential lines that connect the drains of  $M_3$  and  $M_4$  to the drains of  $M_1$  and  $M_2$ . Regardless of transistor sizing,  $C_{parasitic}$  remains a result of the metal traces that provide these connections. In addition to this,  $R_{L1}$  and  $R_{L2}$  also introduce some parasitic capacitance at this node. High-valued resistors may be formed by connecting a number of N-well regions in the substrate through metal connections, and have a fixed resistance-per-length ratio. The resistors introduce a parasitic capacitance (that increases with increasing resistance), which limits the maximum value of the load impedance. The parasitic capacitance  $C_{parasitic}$  and the limit on  $R_L$  imply that for a high  $f_{max}$ ,  $g_m$  must be maximized. For this reason, this type of frequency divider is known for its high power consumption, which is another reason it is inferior to alternatives such as injection-locked architectures.

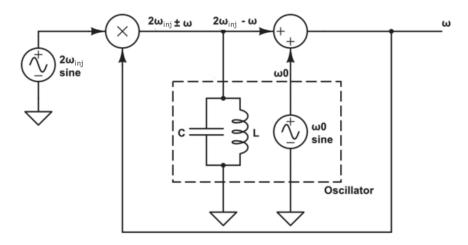

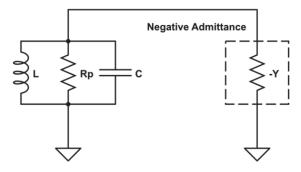

ILFDs work by forcing a free-running resonator to change its oscillation frequency by means of injecting signals at frequencies *near* the fundamental frequency of oscillation, directly into the resonator. Since the circuit is basically an oscillator, an inductor cancels parasitic capacitances, allowing the circuit to operate at significantly lower power than the SCL divider of Figure 2.1. Their primary disadvantage is a limited bandwidth of synchronization due to the oscillator's tuned load. Figure 2.2 can be used to understand the operation of a generic ILFD:

Figure 2.2 ILFD Block Diagram

The oscillator in Figure 2.2 has a fundamental frequency  $\omega_o$ . As can be seen above, an ILFD works by mixing the input signal (at twice the desired output frequency), with the output of the oscillator, of frequency  $\omega$ . The mixing product at  $2\omega_{inj}$  -  $\omega$  survives the filter, and reinforces the tank's oscillations at  $\omega_o$ .

When the deviation of  $\omega_{inj}$  from  $\omega_o$  is small (i.e. within the linear region of a tuned load's  $\partial \phi / \partial \omega$  relationship), the change in oscillation frequency from  $\omega_o$  to  $\omega_{inj}$  can be explained by the transient modification of the phase term of the sinusoidal output. In other words, this summing of the two signals in Figure 2.2 results in frequency modulation of the oscillator voltage. Using a phasor diagram to represent the frequencies and phase difference between the frequency-halved injection signal (at the output of the mixer in Figure 2.2) and the output oscillation, the locking of oscillators is mathematically treated in Chapter 3. The range of signal frequencies (centered around the fundamental frequency of the resonator), referred to as the "locking range," is dependent on the quality factors of the inductor and capacitor that make up the tank circuit. The quality factor (Q) is a metric of how much energy is lost during each cycle of oscillation, which also determines how long a resonant circuit will oscillate for a given input energy. The Q of the overall tank circuit is typically set by the on-chip inductor, and is given as:

$$Q_{LC} \approx Q_{L} = \frac{j\omega L}{R_{series}}$$

(2.2)

where  $R_{series}$  is the lumped resistances of the metal trace that forms the inductor, L is its inductance, and  $Q_L$  is its quality factor. Typically, capacitors implemented on-chip are of such high Q that the quality factor of the inductor dominates.

Two of the most popular ILFDs used as analog prescalars are the "Tail-ILFD" and the "Quench-ILFD."

#### 2.1.1 "Tail-ILFDs"

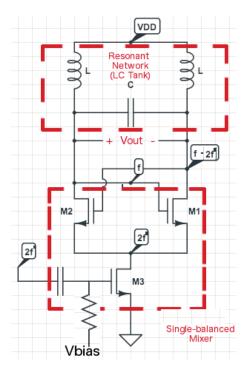

Tail-ILFDs are so named because the input signal is applied to the gate of MOSFET that provides the tail current for a differential pair-based negative-resistance oscillator. To understand how mixing, filtering, and injection-locking processes take place in a Tail-ILFD, observe the following figure, which is a generic schematic of a Tail-ILFD implemented using a single-balanced mixer and a negative-resistance oscillator:

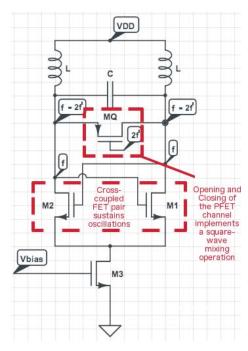

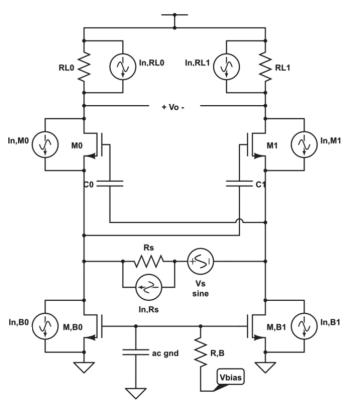

Figure 2.3 Generic Tail-ILFD

In Figure 2.3, the input signal is applied through an AC coupling capacitor directly to the gate of the current source FET,  $M_3$ . Because this FET is in a Common-Source amplifier configuration, this signal appears at the drain of  $M_3$  at a value of:

$$V_{DM3}(t) = V_{in}(t)A_{v}(t) \approx \frac{V_{in}(t)g_{ms}}{g_{ms}(t)}$$

(2.3)

where  $g_{m1}$  and  $g_{m3}$  are the transconductances of the  $M_1$  and  $M_3$ , respectively. The transconductance  $g_{m1}$  is a function of time since its gate is tied to the output voltage of the oscillator. Next, the input signal at the source of  $M_1$  is mixed with the oscillations of the tank, via

the cross-coupling of FETs  $M_1$  and  $M_2$ . To illustrate how this qualifies as a mixing operation, Figure 2.4 depicts a simple switch-based mixer scheme: multiplying a sine wave at a frequency  $f_1$  with a square wave at a frequency  $f_2$ .

Figure 2.4 Switch-Based Single-balanced Mixer Scheme

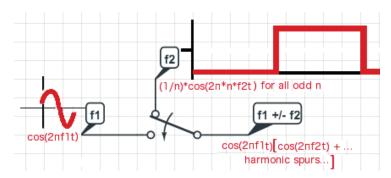

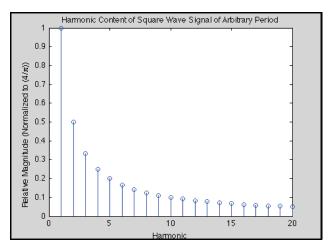

It is well known that for a square-wave pulse train the Fourier series is:

$$\begin{split} s_{squars}(t) &= V_{os} + \frac{4}{\pi} \sum n \left[ \frac{\cos(2\pi(2n-1)ft)}{2n-1} \right] \\ &= V_{os} + \frac{4}{\pi} \left( \cos(2\pi ft) + \frac{1}{3} (\cos(2\pi 3ft) + \frac{1}{5} (\cos(2\pi 5ft) + \dots) \right) \end{aligned} \tag{2.4}$$

where  $V_{os}$  is a dc value if the square wave is unipolar as in Figure 2.4. It can be seen from the expansion above that a square pulse train in time is composed of the fundamental frequency (calculated as the inverse of the period of one square wave) and its odd harmonics. The following figure is a graphic representation of the frequency spectrum of such a signal:

Figure 2.5 Frequency Spectrum of Arbitrary Square Wave

In the context of Figure 2.3, the switch is implemented by  $M_1$  in Figure 2.3, one of the cross-coupled FETs that compose the negative resistance of the active oscillator. The square wave represents whether or not  $M_1$ 's channel is open (magnitude of 1) or closed (magnitude of 0). An amplified version of the input signal at the Source of  $M_1$  appears at  $M_1$ 's Drain due to its Common Source (CS) configuration. The resultant signal is given by:

$$V_{DrainM1} = V_{DM3}(t) \left[ \left( \frac{1}{2} \right) + \left( \frac{4}{\pi} \right) cos(2\pi f_2 t) + \frac{1}{3} cos(2\pi 3 f_2 t) + \frac{1}{5} cos(2\pi 5 f_2 t) + \cdots \right]$$

(2.5)

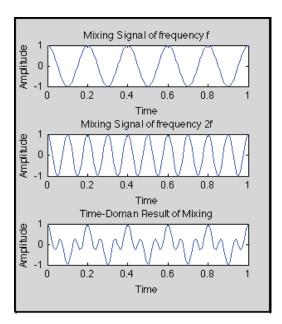

The signal injected into the tank contains not only the product of an ideal mixing operation of 2f and f, but also all of the attenuated odd-numbered harmonic components of the switch-controlling square wave. However, due to the LC network at the node of the injecting signal, all of the higher-frequency components of the mixing operation are shorted to AC ground. Figure 2.6 illustrates the waveform discussed, without the detailed magnitude information.

Figure 2.6 The Mixing of Two Signals

It is clear that the mixed signal, at the bottom of Figure 2.6, contains more than one frequency component. However the LC tank is tuned to the lower frequency component, selecting only the half-frequency of the 2f input.

Ultimately, a Tail-ILFD operates by mixing a signal of twice the desired locking-frequency with the fundamental frequency of the oscillatory network, thus injecting a signal into the tank. If the quality factor of this network is such that the impedance of it at the frequency of the injected signal is sufficiently high, then phase-locked oscillation at this injected frequency can be sustained indefinitely. The phenomenon that controls the input magnitude required for "injection-locking" is explored in detail in Section 3.1, and a condition for locking is given that applies for both Tail and Quench-ILFDs.

## 2.1.2 "Quench" ILFDs

Quench-ILFDs are based on the same block-diagram level architecture depicted in Figure 2.1. The main difference between the two is where the input signal is applied to the circuit.

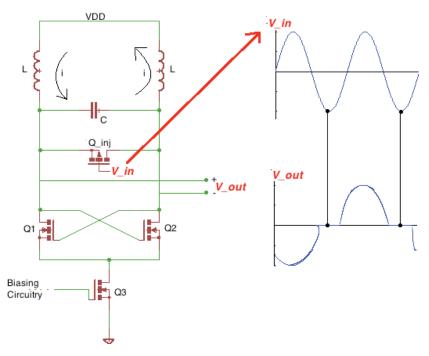

Quench-ILFDs are so named because the mixing operation is done by "quenching" the output terminals, i.e. momentarily connecting them via low impedance, as shown in Figure 2.7

Figure 2.7 Generic Quench-ILFD

In a Quench-ILFD, the mixing operation is performed directly at the output terminals of the circuit, implemented by connecting a FET between these two terminals and applying the input signal to its gate in Figure 2.7. As the input signal drives the FET between states of triode and cutoff, the square-wave mixing signal appears on the Quench FET,  $M_Q$ . That is, a low voltage on  $M_Q$ 's gate shorts  $M_1$ 's drain to  $M_2$ 's drain, which is a "multiply by zero." A high input voltage forces  $M_Q$  into cutoff, which is a "multiply by one." Other than this main difference, the Quench and Tail-ILFDs operate through essentially the same mechanisms.

While the means of synchronization of frequencies due to injection is not obvious upon inspection of a Tail-ILFD, seen in Figure 2.2, the placement of the "injection FET"  $M_Q$  offers some insight on how the injected signal, of roughly twice the frequency of the tank's resonant frequency, controls the instantaneous frequency of the oscillator. It also demonstrates the reduction in phase noise observed in all oscillators when they are injection-locked, including the

aforementioned Tail-ILFD. To illustrate this, Figure 2.8 displays the time domain waveforms of a Quench-ILFD:

Figure 2.8 Transient Synchronization Mechanism of Quench-ILFD

The voltages on the gate of  $Q_{inj}$  and of the output oscillations are depicted on the right (not to scale). The outputs are shorted together (thus forcing a "zero-crossing" of the oscillation waveform) when the voltage on the gate of the pFET  $Q_{inj}$  is at its minimum value. Controlling the output's zero-crossings forces the oscillation frequency to be exactly half of  $V_{in}$ 's frequency and significantly reduces the jitter, relative to its free-running case. The reduction of phase noise in injection locked oscillators is elaborated in Chapter 3.

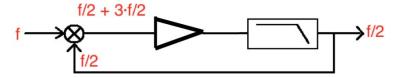

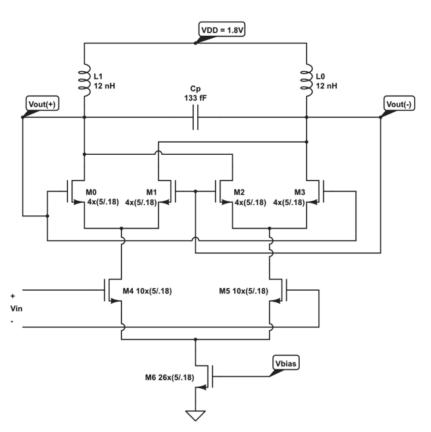

#### 2.1.3 Regenerative ILFDs

Regenerative Frequency Dividers (RFDs) are similar in concept to the ILFDs discussed above, but differ in the fact that they do not have a free running oscillation. The block diagram of a Regenerative Frequency Divider is shown below:

Figure 2.9 Regenerative Frequency Divider Block Diagram

Typical RFD implementations include the use of double-balanced mixers, followed directly by gain and filtering stages. The lowpass filter (LPF) is needed to provide mixer feedback at the desired locking frequency. It is important that the phase shift around the loop is an integer multiple of  $2\pi$ , in order to satisfy the Barkhausen criterion of sustained oscillations.

The *Gilbert Cell* and MOSFET switches are popular topologies used to implement IC mixers. The mixing products are then filtered in order to obtain the desired locking frequency, which is then amplified and fed back to the mixer. In Figure 2.9 a lowpass filter is shown, although a bandpass LC tank may be considered to operate at higher frequency with less power, as is the case with ILFD designs. In this way, regenerative frequency division can occur, so long as there is an input excitation. Otherwise, free-running oscillations do not exist in an ideal RFD.

## 2.2 Low Noise Amplifiers

The noise figure of a LNA is mainly dependent on its input impedance match with the signal source (usually an antenna or crystal-based BPF), its power gain, and the noise generated by the LNA circuitry. As such, most LNA developments have emphasized improvements within these three categories. Specifically, this thesis summarizes LNA prior art in three specific regimes: (i) *Impedance Matching*, ensuring that the source and the LNA input are of the same resistive impedance, (ii)  $g_m$ -Boosting, or ways of increasing overall power gain, and (iii) *Active Noise Cancelling* (ANC) design, which employs the use of various circuit topologies that either fully or partially cancel the noise of the LNA itself.

#### 2.2.1 Impedance Matching Techniques

Researched impedance-matching techniques are either wideband designs, which use resistive and active components, or narrowband designs, which use reactive components. Three wideband impedance matching designs are presented here: (i) Resistive termination matching, (ii) Source termination matching, and (iii) Shunt-Shunt resistive feedback matching.

#### Wideband Designs

#### Resistive termination

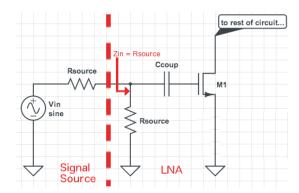

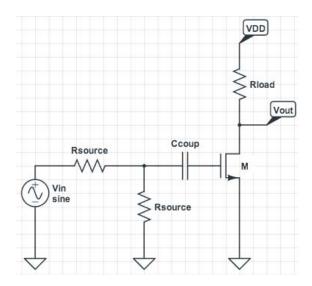

Resistive termination is the most straightforward approach to matching the LNA's input to any arbitrary source impedance. Observe the following figure, which demonstrates how this is accomplished:

Figure 2.10 Resistive Input Termination

In the figure above, the signal source is shown on the left of the dashed line. It has internal impedance described by  $R_{source}$ , which is usually  $50\Omega$  in standard RF communication hardware. Matching is accomplished by connecting a resistance equal to  $R_{source}$  between ground and gate of  $M_1$ , through the use of a low-impedance reactance. Note that this is purely an AC connection, as the DC-blocking capacitor prevents the resistive termination from affecting the

bias points of the devices. The input to the LNA is on the right of the dashed line, and "looking" into the LNA's input reveals an impedance of:

$$Z_{in} = R_{source} / \left[ \frac{1}{j\omega C_{coup}} + \frac{1}{j\omega C_{gateM1}} \right]$$

(2.6)

Typically, the reactance due to the coupling capacitor in series with the gate and overlap capacitances of the amplifying transistor ( $M_1$ , here) is very high, since minimally sized transistors are used for high-frequency operation. Of course, the coupling capacitor adds very little reactance at high frequencies, by design. So, if:

$$X_{CgateM1} >> R_{source}$$

(2.7)

Then the input impedance of the LNA is approximately:

$$Z_{in} \approx R_{sourcs}$$

(2.8)

leading to a matching of the impedances between the signal source and the LNA. However, this approach remains a last approach among RF design engineers, as it has a detrimental effect on the noise figure of the system. Observe the following figure, which is a noise model of a simple wideband, single-transistor LNA employing resistive input matching:

Figure 2.11 LNA Employing Resistive Input Termination

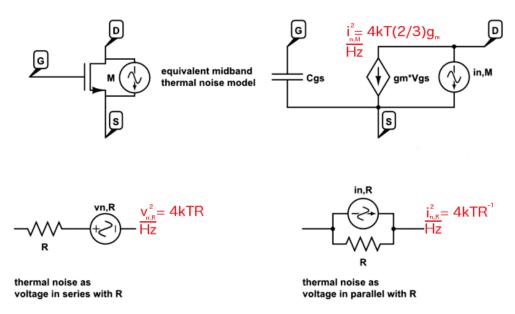

To analyze the noise figure of this topology, it is useful to replace the noisy components in the schematic with their appropriate noise models. Figure 2.12 below represents the models used for the thermal (or "Johnson") noise generated by any resistance R, and the thermal noise produced by a FET (of negligible source/drain impedance, high output impedance  $r_o$ , and ignoring flicker noise at high-frequency):

Figure 2.12 Simplified Noise Models for Resistance and MOSFET

As can be seen from Figure 2.12, the dominant noise source in a MOSFET at high frequencies is the thermal noise produced by the non-zero channel impedance, determined at the quiescent point of the transistor. This current spectral density is given as:

$$\left(i_{n,FET}\right)^2 = 4kT\left(\frac{2}{3}\right)g_m \tag{2.9}$$

which is given in units of  $A^2/H_Z$ . The  $(^2/_3)$  term is due to the pinch-off of the channel in the active mode of operation. The dominant noise source of any given resistance R is Johnson noise, and the current spectral density is:

$$\left(i_{n,R}\right)^2 = 4kT\left(\frac{1}{R}\right) \tag{2.10}$$

When needed, the voltage spectral density of a resistance may be used. The voltage spectral density,  $(v_{n,R})^2$ , is expressed in Figure 2.12, and is equal to 4kTR. By replacing the components in Figure 2.11 with the appropriate models, the effect of each noise source on the output SNR can be determined. Figure 2.13 shows the overall noise model for the LNA:

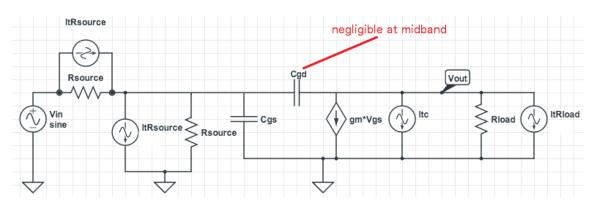

Figure 2.13 Simplified Noise Circuit of Resistive Termination LNA

To determine the Noise Figure for the circuit of Figure 2.11, the procedure is as follows: first, the output voltage (node  $V_{out}$  in the figure) that results from each noise current source is calculated. Next, the corresponding output power of each source's output voltage contribution is found using  $V^2/R_{load}$ , where all of the output power terms share the same  $R_{load}$  value. The total output noise power for the LNA is the sum of all these output power terms. By dividing the total output noise power by the output noise power that arises due to the source impedance only ( $R_s$ ), the NF of any LNA can be analyzed. The noise figure can then be found from:

$$F = \frac{SNR_{in}}{SNR_{out}} = \frac{Total\ Output\ Noise\ Power}{Output\ Noise\ Power\ dus\ to\ Source} \tag{2.11}$$

Firstly, the output noise power due only to the source is a consequence of the real part of the source impedance and is equal to:

$$P_{out,sourcs} = \left( \left( \frac{1}{2} \right) i_n \right)^2 R_{sourcs}) BG = \left( kTB \left( \frac{1}{R_{sourcs}} \right) R_{sourcs} \right) G = kTB \left[ R_s R_L(g_m)^2 \right] \quad (2.12)$$

where *B* is the effective bandwidth and *G* is the power gain of the LNA. Next, the noise due to the resistive-termination resistor is considered. Just like the signal source's internal resistance, the noise presented by this resistor is amplified by the LNA and is:

$$P_{out,R-term} = \left( \left( \frac{1}{2} \right) i_n \right)^2 R_{source} BG = kTB \left[ R_s R_L(g_m)^2 \right]$$

(2.13)

As mentioned, the main source of noise in a FET device operating at a high frequency is due to the thermal noise in the induced channel, and gate noise is typically insignificant [14]. The noise current power spectral density generated is approximated as:

$$i_n^2 = 4kT\left(\frac{2}{3}\right)g_m \tag{2.14}$$

This energy is dissipated through the load  $R_{load}$  such that the output noise power within a bandwidth B due originating solely from the FET is:

$$P_{out,FET} = \left(\left(\frac{1}{2}\right)i_n\right)^2 R_{load}B = 4kTB\left(\frac{2}{3}\right)g_m R_{load}$$

(2.15)

This noise appears directly at the output and therefore isn't multiplied by the power gain of the LNA, G. Lastly, the load resistor presents some noise power at the output node of:

$$P_{out,Rload} = \frac{4kTB}{R_{load}}R_{load} = 4kTB \tag{2.16}$$

Solving (2.11) by substituting in terms of (2.12) - (2.16) gives an analytical result for the theoretical minimum noise figure for such an LNA:

$$F = kTB \frac{\left[2R_sR_{load}(g_m)^2 + 4\binom{2}{s}g_mR_{load} + 4\right]}{[kTBR_sR_{load}(g_m)^2]}$$

(2.17)

Expression (2.17) shows how a higher LNA power gain has a preferable effect on the noise figure, by minimizing the impact of noise due to the circuitry on the output SNR. This equation also demonstrates the negative impact of resistive-termination impedance matching. Introducing a resistive element at the input of the LNA in this fashion results in a minimum theoretical noise figure of 2, or 3 dB, since:

$$\lim_{G \to \infty} \{F\} = \lim_{g_{m \to \infty}} \left\{ 2 + \frac{4\binom{2}{8}}{R_S g_m} + \frac{4}{R_S R_{load}(g_m)^2} \right\} = 2$$

(2.18)

when (2.18) is expressed by its decibel equivalent, the NF becomes:

$$10\log[F_{min}] = 10\log[2] = 3 dB \tag{2.19}$$

This degradation of noise performance leaves much to be desired, and as expected more sophisticated topologies exist in order to eliminate this effect.

What follows for the remainder of this chapter are summaries of very similar analyses of several different LNA topologies that fall into the regimes outlined in the beginning of section 2.2 - not only for impedance matching LNAs, but for g<sub>m</sub>-boosting and ANC LNAs as well. Note that some techniques improve performance in more than one regime. Also, these analyses are first order approximations of circuit behavior, since different IC processes will have different strengths and weaknesses in terms of gate oxide capacitance, substrate leakage, FET output impedances, electron and hole mobility, among a host of other process-based characteristics. Lastly, noise-less capacitors, midband operation, and exclusive use of long-channel device noise models are assumed in these analyses.

#### Source Termination

Source termination LNAs use an active device in order to set the input impedance, instead of a discrete resistor. The following figure is a noise model of a simple source termination Common-Gate (CG) LNA:

Figure 2.14 Simplified Noise Circuit of Source Termination CG LNA

Instead of simply placing a resistor of arbitrary value in shunt with the LNA's input, source termination establishes the input impedance by means of a FET. In this circuit,  $M_1$  is a current source, which biases  $M_0$ , the amplifying transistor. At midband, the impedance looking into the LNA can be expressed as:

$$R_{in} = \left(\frac{1}{g_{mo}}\right) / / r_{oM1} \approx \frac{1}{g_{mo}}$$

(2.20)

To obtain an impedance match, the transconductance of  $M_0$  is set to:

$$g_{m0} = \frac{1}{R_s} = 20 \, mS = 20 \, \frac{mA}{V}$$

(2.21)

in a 50  $\Omega$  communication system. This is a limitation of this circuit – the maximum transconductance is set by the value of the source impedance. Since the input FET is in a CG configuration, the midband gain is estimated as:

$$A_v = \frac{v_{out}}{v_s} \approx g_{m0} R_L \tag{2.22}$$

For this particular LNA topology, the noise originating from  $R_s$  yields an output noise power of  $kTBR_sR_L(g_{m,0})^2$ . Due to the impedance matching condition,  $R_s = (g_{m,0})^{-1}$ , so the output noise power from  $R_s$  can be simplified as  $kTBR_Lg_{m,0}$ . The output noise power contributions due to

the FETs can be estimated as  $kTB(^2/_3)R_Lg_{m,0}$  and  $kTB(^2/_3)R_Lg_{m,1}$  for M<sub>0</sub> and M<sub>1</sub>, respectively. The purely resistive load impedance contributes 4kTB of output noise power. The expression for the noise figure of this circuit based on these terms is:

$$F = \left(1 + \frac{2}{3}\right) + \frac{\frac{2}{3}g_{m,1}}{g_{m,0}} + \frac{4}{R_{L}g_{m,0}}$$

(2.23)

From (2.23), it can be seen that to optimize the noise performance for the LNA depicted in Figure 2.14, the transconductance of the tail FET  $M_1$  should be kept as low as possible, and the load resistor should be chosen such that  $R_L >> (4/g_{m,0})$ . In the case where  $g_{m,1}$  approaches zero and  $R_L$  approaches infinity, (2.23) yields a minimum theoretical noise figure of  $^5/_3$ , or 2.2 dB, for the simple source termination CG LNA topology.

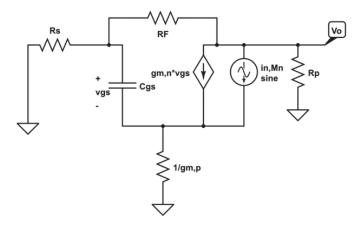

#### Shunt-Shunt Resistive Feedback

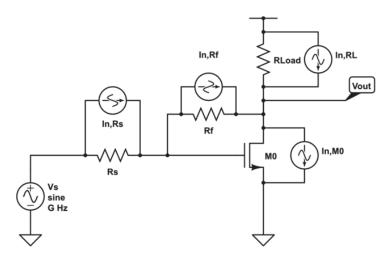

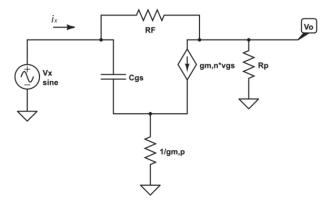

Shunt-shunt resistive feedback LNAs use a feedback resistor  $R_F$  to establish an input impedance based on the LNA's closed-loop gain. The following figure is a noise model for a simplified Shunt-Shunt feedback LNA:

Figure 2.15 Simplified Noise Circuit of Shunt-Shunt Resistive Feedback LNA

When analyzed using feedback theory (where A is open-loop gain and  $\beta$  is the feedback factor), it can be seen that the input impedance looking info this LNA is estimated to be:

$$R_{in} = \frac{A}{1 + A\beta} \approx \frac{g_{mo}(R_F//R_L)}{\left[\left(1 + g_{mo}(R_F//R_L)\right)\right]} = \frac{1}{\frac{1}{R_S//R_L} + \frac{1}{g_{mo}}}$$

(2.24)

However, for the feedback mechanism to properly work, the load impedance  $R_L$  must be much larger than  $R_F$ , so that the output current is diverted back to the LNA's input node. So, when  $R_F \ll R_L$ , (2.24) becomes:

$$R_{in} = \frac{A}{1+A\beta} \approx \frac{1}{\frac{1}{R_F} + g_{mo}} \approx \frac{1}{g_{mo}}$$

(2.25)

It can be seen from (2.25) that this LNA also uses the transconductance of the amplifying transistor to set the input impedance. Due to the feedback mechanism, half of  $M_0$ 's drain noise is cancelled, and the noise figure is:

$$F = 1 + R_s \left[ \frac{1}{R_F} + \frac{1}{R_L} + \frac{2}{3} g_{m,0} \right]$$

(2.26)

To obtain an optimal noise figure here, the transconductance of  $M_0$  should be matched to the inverse of the source impedance. In addition to this,  $R_s$ ,  $R_F$ , and  $R_L$  should be chosen such that:

$$R_s << R_F << R_L \tag{2.27}$$

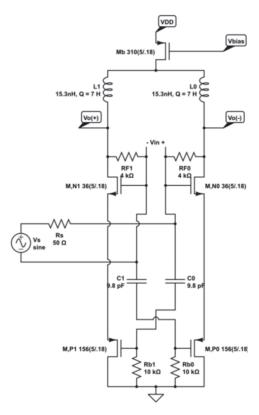

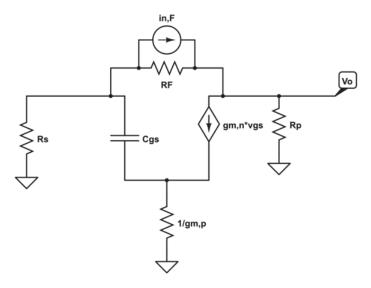

which, along with the impedance matching identity of  $R_s = (g_{m,0})^{-1}$ , results in the same theoretical minimum noise figure as for the source termination CG LNA: 2.2 dB. In [1], a shunt-shunt resistive feedback topology with a reduced NF of 1.7 dB (at 2.3 GHz) is realized through a technique of "noise cancellation." This topology, along with a cascode configuration (discussed later) and a tuned load, forms the basic topology for the PNC LNA studied in this thesis, discussed in Chapter 4.

Narrowband Designs

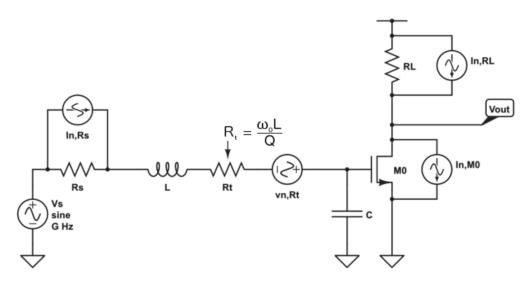

LC Matching Network

As many radios are designed for only one main frequency of operation, LC Matching Networks are often used to interface an LNA's typically high impedance to a lower source impedance, around a single center frequency. Ideally, these lossless components transform the input impedance to zero, at the resonant frequency of the LC network. This intends to provide full power transfer to the input of the LNA via resonance, and by properly designing the Q of the overall network, which includes C, L, and  $R_s$ , significant voltage gain can be obtained between the signal source and  $v_{gs}$  of the input FET, whose gate is in parallel with the capacitor of the matching network. The noise figure of this type of LNA is ideally 1, or 0 dB. In order to achieve such a low NF, the quality of the input RLC network at resonance must be very high, which depends on the quality of the inductor and the ratio of the capacitive reactance to  $R_s$ . To explain this dependence, observe Figure 2.16, which shows a noise model of a simple LC-matched common-source LNA.

Figure 2.16 Simplified Noise Circuit of LNA employing LC Matching Network

In the circuit of Figure 2.16, an inductor appears in series with the source impedance and resonates with a capacitance in parallel with the input FET's gate, which represents  $M_0$ 's parasitic capacitance and perhaps some explicit capacitance. While the capacitor is assumed to be noiseless, the noise of the inductor is represented as a thermal noise voltage originating from

the parasitic resistance of the inductor,  $R_t$ .  $R_t$  is the lumped resistance of the metal traces from which the inductor is fabricated, and at resonance is given as:

$$R_t = \frac{\omega_o L}{Q} \tag{2.28}$$

For an inductor of infinite Q, the noise current approaches zero. However, the resulting noise voltage  $v_{n,Rt}$  is amplified to the output with the same gain as the noise from  $R_s$ . Ideally, this voltage gain is inversely proportional to  $\omega CR_s$ , which is designed to be much less than one at  $\omega_o$ . The resulting NF for this LNA is:

$$F = 1 + \frac{\omega_o L}{QR_s} + \left(\omega_o CR_s + \frac{1}{Q}\right)^2 \left[ \frac{\frac{2}{s}}{R_s g_{m,0}} + \frac{1}{R_s R_L (g_{m,0})^2} \right]$$

(2.29)

In the case where  $\omega_o CR_s$  approaches zero and Q approaches infinity, (2.29) yields a theoretical minimum NF of 0 dB. In the case where  $\omega_o CR_s$  approaches infinity, but Q is low enough that  $R_t$  is equal to  $R_s$ , the minimum theoretical NF becomes that of the resistive termination CS LNA: 3 dB. As the parasitic resistance of the inductor increases, the NF further degrades, regardless of the LNA's gain.

## 2.2.2 g<sub>m</sub>-Boosting Techniques

Some  $g_m$ -boosting circuits are based on topologies that optimize signal gain, while still matching the signal source impedance. Two main types of  $g_m$ -boosting exist: (i) device coupling designs, and (ii) tuned-circuit designs.

**Device Coupling Designs**

## Cascode Amplifier

A common cure to the Miller capacitance that plagues Common-Source (CS) amplifiers is to use a cascode configuration. A noise model of a simple cascode amplifier, with an LC input matching network, is shown in Figure 2.17. The Miller capacitance of  $M_0$  (the input transistor) is now limited to:

$$C_{M0} = C_{G,M0}(1 + A_{V,M0}) = 2C_{G,M0}$$

(2.30)

where  $C_{G,M0}$  is  $M_0$ 's gate capacitance, and  $A_{V,M0}$  is the voltage gain from the gate of  $M_0$  to its drain. In (2.30), the transconductances of  $M_0$  and  $M_1$  are assumed to be equal, which results in  $A_{V,M0}$  being equal to one.

Figure 2.17 Simplified Noise Circuit of Cascode Amplifier

The noise current  $i_{n,MI}$  generated by  $M_1$  causes a voltage drop at its drain, the output terminal, of  $-i_{n,MI}R_L$ . The noise current is also injected into the source, and develops a source-gate voltage of  $i_{n,MI}(^1/g_{m,I})$ , when  $r_{o,M0}$  is sufficiently large. This voltage is amplified to the drain as  $i_{n,MI}(^1/g_{m,I})g_{m,I}R_L$ , due to its common-gate (CG) configuration. This effectively cancels the thermal noise current generated by  $M_1$ . The resulting noise figure for this LNA is:

$$F = 1 + \frac{\omega_o L}{QR_s} + \left(\omega_o CR_s + \frac{1}{Q}\right)^2 \left[\frac{\frac{2}{s}}{R_s g_{m,0}} + \frac{1}{R_s R_L (g_{m,0})^2}\right]$$

(2.31)

It can be seen that the NF expressed for this LNA in (2.31) is identical to the NF of the LC impedance-matched CS LNA, whose NF is expressed in (2.29). This is because the channel noise generated by  $M_1$  is cancelled, due to the cascode configuration. In the case where  $\omega_o CR_s$  approaches zero and Q approaches infinity, the theoretical NF for this LNA is 0 dB.

This circuit is an important circuit technique because high-frequency receivers often suffer from the Miller effect, and rely upon the cascode configuration to implement amplifying stages. Since the noise due to the cascode transistor  $M_1$  is cancelled completely when matched to  $M_0$ , this technique can be used in a wide variety of designs.

### **Active Coupling**

Figure 2.18 depicts the noise model for a simple LNA employing the use of active coupling g<sub>m</sub>-boosting [8]:

Figure 2.18 Simplified Noise Circuit of Active Coupled LNA

This LNA matches the input impedance via the source termination mechanism, using  $M_0$ , which is in common-gate (CG) configuration relative to  $V_s$ .  $M_T$  provides the bias current. The input signal is also fed to the gate of  $M_1$ , which is in a CS configuration. It can be seen in the figure above an amplified and inverted version of the input signal appears on the gate of  $M_0$ . When viewed from  $M_1$ 's output,  $M_0$  is in a CS configuration as well. Due to this active coupling, the effective transconductance of  $M_0$  becomes  $g_{m,0}(1+g_{m,1}/g_{m,B})$ , while matching the impedances between the LNA and the signal source through  $M_0$ . Note that  $M_1$ 's transconductance need not be equal to that of  $M_0$ .

The input impedance of this LNA is approximately  $^{1}/(2g_{m,0})$  when  $(g_{m,1}/g_{m,B})$  is equal to one, due to the  $g_m$ -boosting employed through FETs  $M_1$  and  $M_B$ . For impedance-matching, the transconductance of  $M_0$  is set so that  $^{1}/(2g_{m,0}) = R_s$ . This LNA has a gain of  $g_{m,0}R_L$  with respect to the source  $V_s$ . Assuming  $g_{m,0}R_s = (^{1}/_2)$  and  $g_{m,1} = g_{m,B}$ , the noise figure for this particular LNA is expressed as:

$$F = \left(1 + \frac{1}{3}\right) + 2\left[\frac{g_{m,T}}{g_{m,0}} + \frac{\frac{4}{9}}{R_s g_{m,B}} + \frac{1}{g_{m,0} R_L}\right]$$

(2.32)

Due to the active coupling, the noise figure contribution due to the input FET  $M_0$  is only  $(^1/_3)$ , whereas in non- $g_m$ -boosted applications source-termination results in NF contribution of  $(^2/_3)$ . However, (2.32) also shows that the NF contributions of all the other noise sources (besides that of  $R_s$ ) are double what they would be without the  $g_m$ -boosting circuitry. In the case where  $g_{m,0}R_L >> 2$  and  $g_{m,1} = g_{m,B}$ , the minimum theoretical NF is  $^4/_3$ , or 1.25 dB.

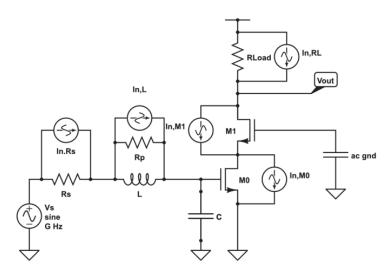

### Reactive Designs

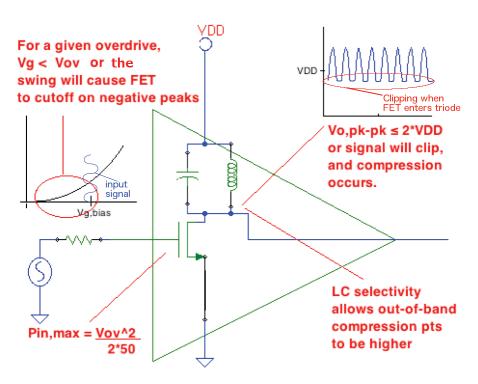

#### Common-Source Amplifier with Tuned Load

A common technique to achieve high gain and high output voltage-swing, while decreasing the noise contribution due to the load impedance, is to use a tank circuit as the load in a CS amplifier. As seen above, noise contributions due to capacitors and inductors (of high Q)

are negligible when compared to contributions due to resistors and active devices. Not only this, but since the impedance of an ideal inductor is  $0\Omega$  at dc, no biasing voltage is dropped over the tank circuit. Because a high quality tank stores its own energy, in the form of electric and magnetic field oscillations, the output voltage is actually able to swing higher than the supply voltage, without distorting the signal. Also, the tank is lossless, as there is no power lost to heat by these reactive devices. Indeed, using a tuned load is a wise approach to the design of any narrowband LNA. The noise model for a simple CS tuned load LNA is shown below:

Figure 2.19 Simplified Noise Circuit of CS Tuned Load LNA\

In the circuit of Figure 2.19,  $L_M$  and  $C_M$  implement the impedance matching.  $L_T$  and  $C_T$  compose the tank load. In the tank load, the noise current is attributed to the parallel equivalent resistance of the inductor  $L_T$ , where:

$$R_{p,T} = Q_T \omega_o L_T \tag{2.34}$$

The noise contribution due to (2.34) is inversely proportional to  $(Q_T)^2$ , whereas the noise contribution due to a resistive load has an effective Q of one. The noise figure for this LNA can be expressed as:

$$F = 1 + \frac{\omega_o L_M}{Q_M R_s} + \frac{\left(\omega_o C_M R_s + \frac{1}{Q_M}\right)^2}{R_s g_{m,0}} \left[ \frac{2}{3} + \frac{1}{Q_T^2 g_{m,0} Q_T \omega_o L_T} \right]$$

(2.35)

The last term in (2.35) is due to the tuned load circuitry. As the quality factor of  $L_T$  increases, less noise voltage is generated, which is approximated as  $\sqrt{(4kTB\omega_o L_T(Q_T)^{-1})}$ . The  $(\omega_o C_M R_S + 1/Q_M)$  term in the expression of (2.35) is the inverse of the quality factor of the input RLC network, and is designed to be much less than one at  $\omega_o$ . This, along with assuming an infinite quality factors  $Q_M$  and  $Q_T$ , implies a theoretical minimum noise figure for this LNA of 0 dB at an input frequency of  $\omega_o$ , regardless of the transconductance of  $M_0$ . This is because of the high gain associated with this type of reactive matching network, as well as the low-noise load. However, using a large transconductance value for the FETs  $M_0$  and  $M_1$  can further optimize the noise figure of this LNA in the case of finite Q factors.

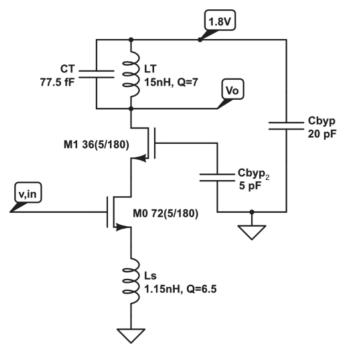

### Source-Inductor (S-L) Amplifier

The S-L amplifier is a heavily researched LNA, and is a great choice for narrowband receivers. It uses an inductor to resonate with the capacitance of an input FET, by placing the inductor in its source terminal. And by selecting the proper  $g_m$  for the FET, a real input impedance of arbitrary value can be generated. To understand this, refer to the following figure:

Figure 2.20 Input Impedance of FET with Source Inductance

For the network illustrated in Figure 2.20, it can be shown that  $Z_{in}$ , which is the complex impedance between the gate terminal and ground, is:

$$Z_{in} = j \left(\omega L - \frac{1}{\omega c_{gs}}\right) + \frac{g_{m,o}L}{c_{gs}}$$

(2.36)

Choosing an inductance value that resonates with the gate-source capacitance of the input FET sets the imaginary part of (2.36) equal to zero. Then,  $Z_{in}$  becomes:

$$Z_{in}|_{(\omega=\omega_0)} = \frac{g_{m,o}L}{c_{qs}}$$

(2.37)

which is a real value, implying resistive-only impedance at the LNA's operating frequency. Properly biasing the FET allows for matching to any arbitrary source resistance, through the control of its transconductance in conjunction with its aspect ratio that sets  $C_{gs}$ , and hence L.

The source-inductor technique for impedance matching, along with a tuned load impedance, can be used to implement a narrowband LNA with an impressive theoretical-minimum noise figure. The S-L LNA is a reliable topology that offers NFs as low as 1.2 dB [9]. Figure 2.21 shows the noise model for a simple S-L LNA.

Figure 2.21 Simplified Noise Circuit of S-L LNA

A brief description of the noise cancelling mechanisms introduced by the source inductance is offered here: the inductor  $L_s$ , resonating with the internal gate-source capacitance in  $M_0$ , creates a high-impedance node at  $M_0$ 's source terminal for signals of high frequency. Noise generated by  $M_0$ 's channel can be modeled as thermal noise current being injected into the source terminal, coming out of the drain terminal. The high impedance at the source node established by  $L_s$  in parallel with  $C_{gs}$  causes the ac current to be dropped across the capacitance  $C_{gs}$  of the FET  $M_0$ . This causes a negative ac voltage drop across its gate-source junction, which in turn causes a decrease in the ac drain current,  $g_{m0}v_{gs0}$ . In this fashion, noise voltage (due exclusively to  $M_0$  channel noise) at the drain of  $M_0$  is effectively cancelled. This technique is essentially a narrowband implementation of *source degeneration*.

The noise figure for this LNA is:

$$F = 1 + \frac{(\omega_o c_{gs})^2 \left[ \left( R_s + \frac{\omega_o L_S}{Q_S} \right)^2 + \left( \frac{R_s}{Q_S} \right)^2 \right] \left[ \sqrt{ \left( 2 + \frac{\omega_o L_S}{R_s Q_S} \right)^2 + \left( \frac{1}{Q_S} \right)^2 } \right] \left[ \frac{2}{3} g_{m,0} + \frac{1}{Q_S \omega_o L_S} + \frac{4}{Q_T^2 (Q_T \omega_o L_T)} \right]}$$

(2.38)

Observation of (2.38) implies that the noise figure has a dependence on the inverse square of the quality factors of the resonant circuits. In the case where  $Q_s$  approaches infinity, the added NF contribution is proportional to  $(\omega_o C_{gs}R_s)^2$ , which is the inverse of the quality factor of the input RLC network. However, this NF contribution is also proportional to  $2/((g_{m,0})^2 R_s)$ , an artifact of the fact that the LNA now presents a voltage divider of one half at its input. The choice of  $g_{m0}$  is dependent on the value of  $R_s$ , and must be sized appropriately for a proper match with the signal source to have the NF of (2.38). Later, in Chapter 4, the theory of operation and NF analysis for this LNA are further detailed. Also, expressions for voltage gain, Q-based input and output impedances, and maximum input power levels are derived.

## 2.2.3 Active Noise Cancelling Techniques

Active Noise Cancelling LNAs minimize the noise figure by actively cancelling the noise generated by the FETs in the circuit itself. Often, these noise-cancelling architectures also perform impedance matching or  $g_m$ -boosting. The two ANC LNAs presented in this document

are the (i) Common Gate – Common Source (CG-CS) LNA [6], and the (ii) Cross-Coupled (CC) LNA [14].

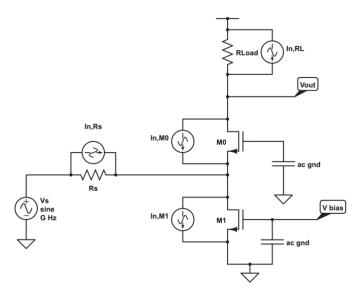

## Common Gate - Common Source (CG-CS) LNA

To understand the operation of a CG-CS LNA, refer to the following figure, which is a noise model of a simple CG-CS LNA:

Figure 2.22 Simplified Noise Circuit CG-CS LNA

In the circuit of Figure 2.22,  $M_0$  establishes the input impedance as  $(g_{m0})^{-1}$ , due to its source termination configuration. The output impedance of the tail FET  $M_T$ , as well as the reactance due to the gate of  $M_1$ , appear in parallel with  $(g_{m0})^{-1}$ , but are assumed to be of such high value that they are negligible when calculating the LNA's input impedance.

Single-ended to differential conversion is achieved by ac coupling the input signal, which is originally fed into the source terminal of  $M_0$ , to the gate of  $M_1$ , which is in a CS amplifier

configuration. Conversely,  $M_0$  is in a CG configuration. If  $g_{m0} = g_{m1}$  and  $R_{L0} = R_{L1}$ , then the output (taken differentially between the drains of  $M_0$  and  $M_1$ ) voltage due to some  $V_s$  is:

$$V_{out,diff} = \frac{1}{2}V_s(2g_mR_L) \tag{2.39}$$

And the voltage gain is:

$$A = \frac{V_{out,diff}}{V_s} = g_m R_L \tag{2.40}$$

In addition to single-ended-to-differential signal conversion,  $M_0$ 's channel noise is fully cancelled.  $M_0$ 's thermal noise current is injected *out* of the drain terminal (causing a negative voltage drop at the positive output terminal) and *into* the source terminal. This current injection to the input node of the LNA is amplified to the drain of  $M_0$ , as a positive voltage. When components are selected properly, the voltage at the drain due to the current injection into its source cancels one half of the noise voltage. The voltage at the positive output terminal due to these mechanisms results in:

$$V_{n,(+)} = -i_{n,m0}R_{L0} + \frac{1}{2}\frac{i_{n,m0}}{g_{m0}}g_{m0}R_{L0} = -\frac{1}{2}g_{m0}R_{L0}$$

(2.41)

The other half of the noise voltage due to  $M_0$  is cancelled using  $M_1$ . The aforementioned source voltage at the LNA's input due to the channel noise of  $M_0$  is also amplified by  $M_1$ , and appears at the negative output terminal. The voltage at the drain of  $M_1$  due to the thermal noise of  $M_0$  is:

$$V_{n,(-)} = -\frac{1}{2} \frac{i_{n,m_0}}{g_{m_0}} g_{m_1} R_{L_1} = -\frac{1}{2} g_{m_0} R_{L_0}$$

(2.42)

when perfect matching is assumed. Since the output is taken differentially, the total output noise voltage due to the channel noise of  $M_0$  becomes:

$$V_{out} = V_{+} - V_{-} = -\frac{1}{2}g_{m0}R_{L0} - (-\frac{1}{2}g_{m0}R_{L0}) = 0 V$$

(2.43)

which implies full noise-cancellation of the thermal noise induced in the channel of  $M_0$ . For the full amplifier, only partial noise cancellation takes place, since  $M_1$  has no similar feedback mechanism.

The noise figure for this LNA is:

$$F = \left(1 + \frac{2}{3}\right) + R_s \left[\frac{2}{3} g_{m,T} + \frac{1}{2R_L}\right]$$

(2.44)

The factor of  $\frac{2}{3}$  is due to the non-cancelled noise of  $M_1$ , which is matched to the FET providing the source-termination,  $M_0$ . From inspection of (2.44), an approach to minimizing the noise figure of this particular LNA would be to minimize the transconductance of the tail FET,  $M_T$ . The minimum theoretical NF produced by (2.44) is 2.2 dB.

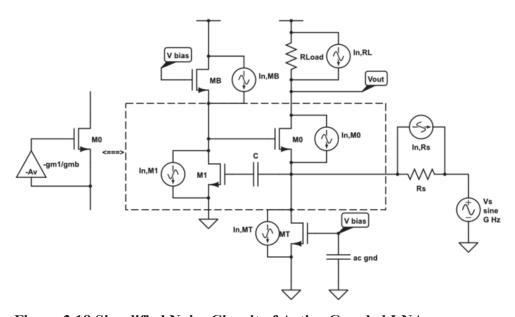

#### Cross-Coupled (CC) LNA

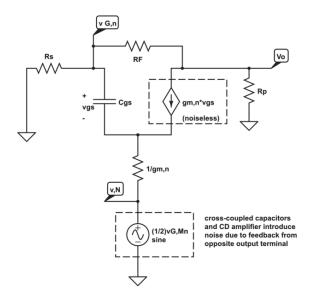

The CC LNA is a fully differential common-gate amplifier that uses cross-coupling between a pair of amplifying transistors to fully cancel their thermal noise contributions. The coupling is done between the gate of one FET in the differential pair, and the source of the other. Figure 2.23 shows a noise model of a simple CC LNA, adapted from the capacitor cross-coupled common-gate LNA of [14]:

Figure 2.23 Simplified Noise Circuit CC LNA

Similar to the situation for the CG-CS LNA, half of the channel noise due to  $M_0$  is cancelled due to its source-termination/common-gate configuration. The other half is cancelled by inverting and amplifying the noise voltage at the source of  $M_0$ , using  $M_1$  in a common-source configuration, and then taking the output differentially. This is achieved using the cross-coupling capacitors  $C_0$  and  $C_1$ , which act as bypass capacitors.  $M_1$ 's configuration mirrors that of  $M_0$ , and its contribution to the output noise voltage is cancelled in an identical manner. Also, by providing an ac ground at the gate of the current sourcing FETs  $M_{B,0}$  and  $M_{B,1}$ , the thermal noise contribution of  $R_B$  will not appear at the output. In this first-order analysis, the only noise sources that remain in this circuit are the source impedance  $R_s$ , the channel noise of the current source FETs, and the load impedances  $R_{L0}$  and  $R_{L1}$ . Assuming ideal matching between components, the noise figure for this LNA is expressed as:

$$F = 1 + \frac{4}{3} \left( \frac{g_{m,B}}{g_{m,0}} \right) + \frac{1}{g_{m,0} R_{L,0}}$$

(2.45)