# ELECTRICAL CHARACTERISTICS OF GALLIUM NITRIDE AND SILICON BASED METAL-OXIDE-SEMICONDUCTOR (MOS) CAPACITORS

by

#### MD TASHFIN ZAYED HOSSAIN

B.S., Bangladesh University of Engineering & Technology, 2001 M.S., North Carolina A&T State University, 2009

#### AN ABSTRACT OF A DISSERTATION

submitted in partial fulfillment of the requirements for the degree

DOCTOR OF PHILOSOPHY

Department of Chemical Engineering College of Engineering

KANSAS STATE UNIVERSITY Manhattan, Kansas

2013

# **Abstract**

The integration of high- $\kappa$  dielectrics with silicon and III-V semiconductors is important due to the need for high speed and high power electronic devices. The purpose of this research was to find the best conditions for fabricating high- $\kappa$  dielectrics (oxides) on GaN or Si. In particular, high- $\kappa$  oxides can sustain the high breakdown electric field of GaN and utilize the excellent properties of GaN.

This research developed an understanding of how process conditions impact the properties of high-κ dielectric on Si and GaN. Thermal and plasma-assisted atomic layer deposition (ALD) was employed to deposit TiO<sub>2</sub> on Si and Al<sub>2</sub>O<sub>3</sub> on polar (*c*-plane) GaN at optimized temperatures of 200°C and 280°C respectively. The semiconductor surface treatment before ALD and the deposition temperature have a strong impact on the dielectric's electrical properties, surface morphology, stoichiometry, and impurity concentration. Of several etches considered, cleaning the GaN with a piranha etch produced Al<sub>2</sub>O<sub>3</sub>/GaN MOS capacitors with the best electrical characteristics. The benefits of growing a native oxide of GaN by dry thermal oxidation before depositing the high-κ dielectric was also investigated; oxidizing at 850°C for 30 minutes resulted in the best dielectric-semiconductor interface quality. Interest in nonpolar (*m*-plane) GaN (due to its lack of strong polarization field) motivated an investigation into the temperature behavior of Al<sub>2</sub>O<sub>3</sub>/*m*-plane GaN MOS capacitors. Nonpolar GaN MOS capacitors exhibited a stable flatband voltage across the measured temperature range and demonstrated temperature-stable operation.

# ELECTRICAL CHARACTERISTICS OF GALLIUM NITRIDE AND SILICON BASED METAL-OXIDE-SEMICONDUCTOR (MOS) CAPACITORS

by

#### MD TASHFIN ZAYED HOSSAIN

B.S., Bangladesh University of Engineering & Technology, 2001 M.S., North Carolina A&T State University, 2009

#### A DISSERTATION

submitted in partial fulfillment of the requirements for the degree

DOCTOR OF PHILOSOPHY

Department of Chemical Engineering College of Engineering

KANSAS STATE UNIVERSITY Manhattan, Kansas

2013

Approved by:

Major Professor Dr. James H. Edgar

# Copyright

MD TASHFIN ZAYED HOSSAIN

2013

### **Abstract**

The integration of high- $\kappa$  dielectrics with silicon and III-V semiconductors is important due to the need for high speed and high power electronic devices. The purpose of this research was to find the best conditions for fabricating high- $\kappa$  dielectrics (oxides) on GaN or Si. In particular, high- $\kappa$  oxides can sustain the high breakdown electric field of GaN and utilize the excellent properties of GaN.

This research developed an understanding of how process conditions impact the properties of high-κ dielectric on Si and GaN. Thermal and plasma-assisted atomic layer deposition (ALD) was employed to deposit TiO<sub>2</sub> on Si and Al<sub>2</sub>O<sub>3</sub> on polar (*c*-plane) GaN at optimized temperatures of 200°C and 280°C respectively. The semiconductor surface treatment before ALD and the deposition temperature have a strong impact on the dielectric's electrical properties, surface morphology, stoichiometry, and impurity concentration. Of several etches considered, cleaning the GaN with a piranha etch produced Al<sub>2</sub>O<sub>3</sub>/GaN MOS capacitors with the best electrical characteristics. The benefits of growing a native oxide of GaN by dry thermal oxidation before depositing the high-κ dielectric was also investigated; oxidizing at 850°C for 30 minutes resulted in the best dielectric-semiconductor interface quality. Interest in nonpolar (*m*-plane) GaN (due to its lack of strong polarization field) motivated an investigation into the temperature behavior of Al<sub>2</sub>O<sub>3</sub>/*m*-plane GaN MOS capacitors. Nonpolar GaN MOS capacitors exhibited a stable flatband voltage across the measured temperature range and demonstrated temperature-stable operation.

# **Table of Contents**

| List of Figures                                                                            | ix          |

|--------------------------------------------------------------------------------------------|-------------|

| List of Tables                                                                             | xiii        |

| Acknowledgements                                                                           | xiv         |

| Dedication                                                                                 | xv          |

| Chapter 1 - Introduction                                                                   | 1           |

| 1.1 Dissertation outline                                                                   | 1           |

| 1.2 Technical Background                                                                   | 4           |

| 1.2.1 MOS capacitors and capacitance-voltage measurement                                   | 5           |

| 1.2.2 Equivalent circuit model of MOS capacitor                                            | 12          |

| 1.2.3 Experimental approach                                                                | 13          |

| 1.2.4 MOCVD of GaN epilayer                                                                | 16          |

| 1.2.5 Atomic layer deposition                                                              | 17          |

| 1.2.6 Fabrication of metal contact                                                         | 21          |

| 1.2.7 Challenges with gate oxides and semiconductors                                       | 22          |

| 1.2.8 Motivation for the selection of materials in MOS capacitor                           | 23          |

| 1.2.8.1 Sapphire                                                                           | 23          |

| 1.2.8.2 GaN                                                                                | 25          |

| 1.2.8.2.1 Polarization in GaN                                                              | 27          |

| 1.2.8.2.2 Properties of GaN                                                                | 29          |

| 1.2.8.2.3 GaN MOSFET structure                                                             | 30          |

| 1.2.8.2.4 MOS-HEMTs                                                                        | 31          |

| 1.2.8.3 Dielectrics                                                                        | 32          |

| 1.2.9 Current conduction through dielectric                                                | 35          |

| 1.2.10 Gate Metal                                                                          | 35          |

| 1.2.11 Non-ideal effects in MOS capacitors                                                 | 38          |

| 1.3 References                                                                             | 40          |

| Chapter 2 - Influence of Atomic Layer Deposition Temperatures on TiO <sub>2</sub> /n-Si MC | S Capacitor |

|                                                                                            | 48          |

|                                                                                      | Abstract                                                                                                 | 48                                                 |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|                                                                                      | 2.1 Introduction                                                                                         |                                                    |

| 2.2 Experimental                                                                     |                                                                                                          | 50                                                 |

| 2.2.1 TiO <sub>2</sub> ALD Film growth and metal contact deposition                  | 50                                                                                                       |                                                    |

|                                                                                      | 50                                                                                                       |                                                    |

|                                                                                      | 2.3 Results and Discussion                                                                               | 51                                                 |

|                                                                                      | 2.4 Conclusion                                                                                           | 62                                                 |

|                                                                                      | 2.5 Acknowledgments                                                                                      | 63                                                 |

|                                                                                      | 2.6 References:                                                                                          | 64                                                 |

| Chap                                                                                 | pter 3 - Effect of ALD growth temperature and GaN surface treatment on A                                 | Al <sub>2</sub> O <sub>3</sub> / <i>n</i> -GaN MOS |

| (                                                                                    | Capacitors                                                                                               | 66                                                 |

|                                                                                      | Abstract                                                                                                 | 66                                                 |

| 3.1 Introduction 3.2 Experimental details 3.3 Results and Discussion 3.4 Conclusion: | 67                                                                                                       |                                                    |

|                                                                                      | 69                                                                                                       |                                                    |

| 3.3 Results and Discussion                                                           |                                                                                                          |                                                    |

|                                                                                      | 81                                                                                                       |                                                    |

|                                                                                      | 82                                                                                                       |                                                    |

|                                                                                      | 3.6 References:                                                                                          | 83                                                 |

| Chap                                                                                 | pter 4 - Insulating gallium oxide layer produced by thermal oxidation of g                               | gallium-polar GaN                                  |

|                                                                                      |                                                                                                          | 86                                                 |

|                                                                                      | Abstract                                                                                                 | 86                                                 |

|                                                                                      | 4.1 Introduction                                                                                         | 87                                                 |

|                                                                                      | 4.2 Experimental procedures                                                                              | 89                                                 |

|                                                                                      | 4.3 Results and Discussion                                                                               | 90                                                 |

|                                                                                      | 4.4 Conclusion                                                                                           | 94                                                 |

|                                                                                      | 4.5 Acknowledgements                                                                                     | 95                                                 |

|                                                                                      | 4.6 References                                                                                           | 96                                                 |

| Chap                                                                                 | pter 5 - Al <sub>2</sub> O <sub>3</sub> / $n$ -GaN MOS capacitors based on polar $c$ -plane and nonpolar | olar <i>m</i> -plane GaN                           |

| (                                                                                    | crystal faces                                                                                            | 98                                                 |

|                                                                                      | Abstract                                                                                                 | 98                                                 |

|                                                                                      | 5.1 Introduction.                                                                                        | 99                                                 |

| 5.2 Experimental details   | 100 |

|----------------------------|-----|

| 5.3 Results and Discussion | 102 |

| 5.4 Conclusion             | 106 |

| 5.5 References             | 107 |

# **List of Figures**

| Figure 1.1 Si MOSFET                                                                                                                                                                                                                                                                 | 5                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Figure 1.2 MOS capacitor structures, C-V plots and band diagrams in (a) accurdence depletion, and (c) inversion region <sup>24</sup>                                                                                                                                                 |                           |

| Figure 1.3 ac voltage superimposed on dc voltage during C-V measurement <sup>26</sup>                                                                                                                                                                                                | 10                        |

| Figure 1.4 Low-frequency and high frequency capacitance-voltage plots <sup>27</sup>                                                                                                                                                                                                  | 11                        |

| Figure 1.5 (a) Small-signal equivalent circuit model for MOS capacitor, (b) simplification obtain series resistance in strong accumulation                                                                                                                                           |                           |

| Figure 1.6 Equivalent circuit of the parallel capacitance and conductance with series                                                                                                                                                                                                | resistance 13             |

| Figure 1.7 Wire jumper (red cable) between probes                                                                                                                                                                                                                                    | 15                        |

| Figure 1.8 Schematic of an ac impedance meter <sup>30</sup>                                                                                                                                                                                                                          | 15                        |

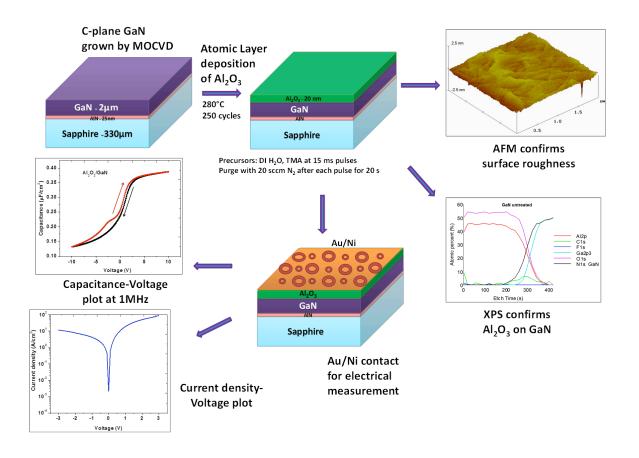

| Figure 1.9 Experimental approach in the research                                                                                                                                                                                                                                     | 16                        |

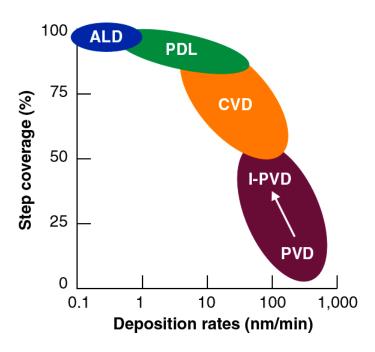

| Figure 1.10 Step coverage (%) vs deposition rate <sup>36</sup>                                                                                                                                                                                                                       | 17                        |

| Figure 1.11 Schematic of the ALD process (a) TMA pulse in the reaction chamber reacts with hydroxyl group, (c) Termination of reaction after one monolay reacts with dangling methyl groups forming Al-O strong bond, (e) formation groups and, (f) after 3 ALD cycles <sup>38</sup> | er, (d) water of hydroxyl |

| Figure 1.12 Basic steps of photolithography                                                                                                                                                                                                                                          | 22                        |

| Figure 1.13 Advantage of GaN devices <sup>55</sup>                                                                                                                                                                                                                                   | 26                        |

| Figure 1.14 GaN technology timeline                                                                                                                                                                                                                                                  | 27                        |

| Figure 1.15 GaN wurtzite structure showing Ga-face and N-face polarity <sup>64</sup>                                                                                                                                                                                                 | 28                        |

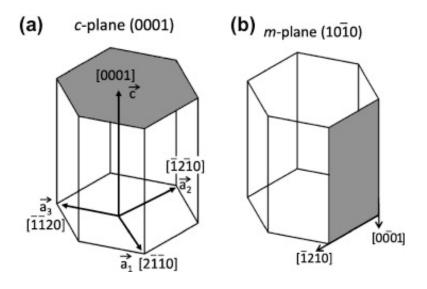

| Figure 1.16 GaN planes: (a) polar <i>c</i> -plane and (b) nonpolar <i>m</i> -plane <sup>38</sup>                                                                                                                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

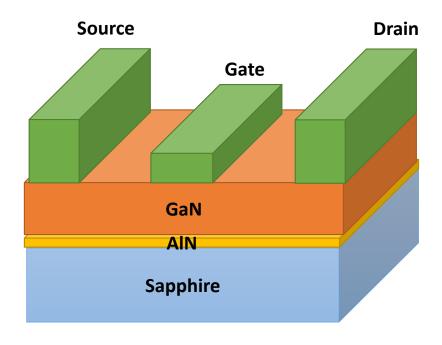

| Figure 1.17 GaN MOSFET                                                                                                                                                                                                                                                                                                                |

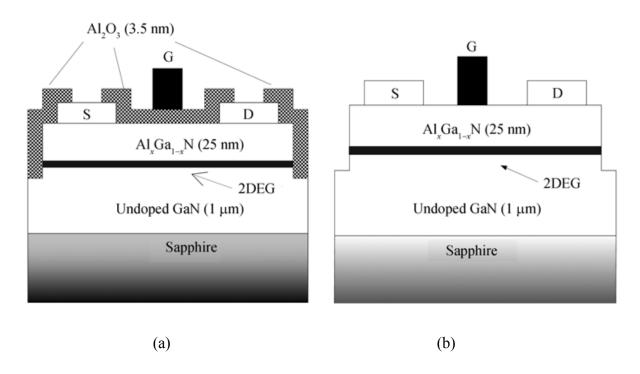

| Figure 1.18 Cross section of (a) Al <sub>2</sub> O <sub>3</sub> /AlGaN/GaN MOS-HEMT, (b) AlGaN/GaN HEM fabricated by Yue <i>et al.</i> <sup>69</sup>                                                                                                                                                                                  |

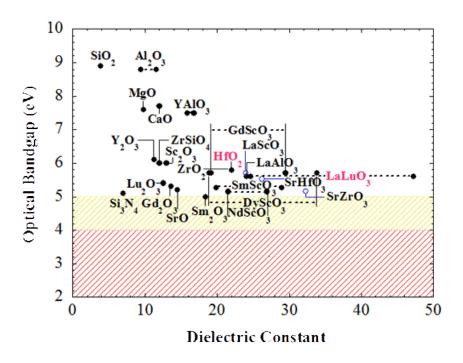

| Figure 1.19 Plot of dielectric constant vs the optical bandgap of gate dielectrics <sup>4</sup>                                                                                                                                                                                                                                       |

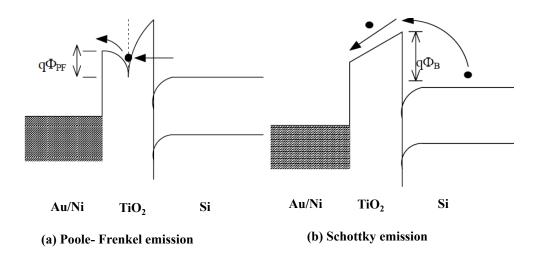

| Figure 1.20 Energy-band diagrams showing conduction mechanisms of (a) Frenkel Pool emission and (b) Schottky emission mechanism for Au/Ni/TiO <sub>2</sub> /n-Si MOS structure 3                                                                                                                                                      |

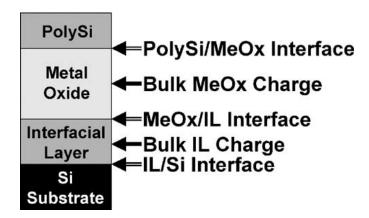

| Figure 1.21 Location of charge to cause threshold voltage shift 105                                                                                                                                                                                                                                                                   |

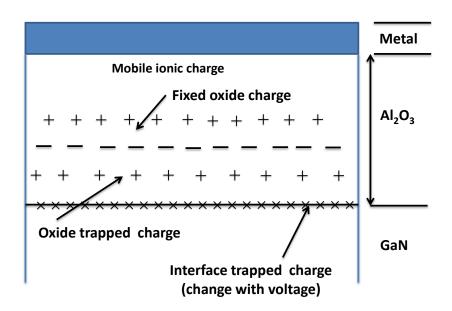

| Figure 1.22 Location of oxide charges in MOS structure                                                                                                                                                                                                                                                                                |

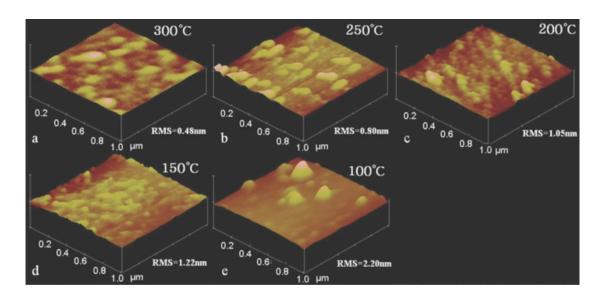

| Figure 2.1 Three-dimensional AFM images of $TiO_2$ on Si deposited at different ALL temperatures. The Z height is 30 nm for all images. (a) $300^{\circ}$ C (RMS = 0.48 nm), (b) $250^{\circ}$ C (RMS = 0.80 nm), (c) $200^{\circ}$ C (RMS = 1.05 nm), (d) $150^{\circ}$ C (RMS = 1.22 nm), and (e) $100^{\circ}$ C (RMS = 2.202 nm). |

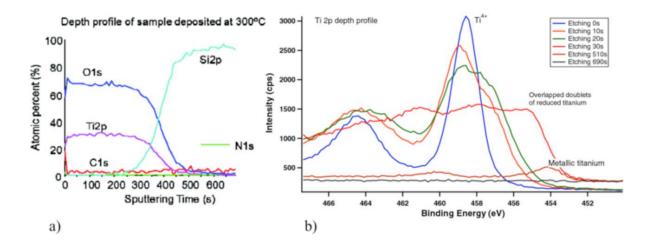

| Figure 2.2 (a) XPS depth profile of sample deposited at 300°C. (The shape of the depth profile similar for all the samples. Only one is demonstrated.)(b)XPS depth profile of Ti 2p a different sputtering times. The 2p <sup>3</sup> of Ti <sup>4+</sup> and metallic Ti peaks are 458.5 eV at 0 second and 454.2 eV at 510 seconds  |

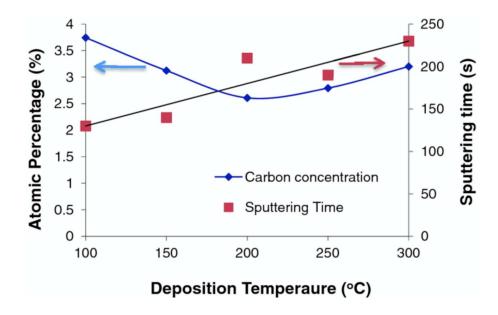

| Figure 2.3 (Left axis) Average atomic carbon concentration in the TiO <sub>2</sub> layers versus ALI temperature. (Right axis) Sputtering time to remove the oxide layer and expose the Substrate versus ALD deposition temperature.                                                                                                  |

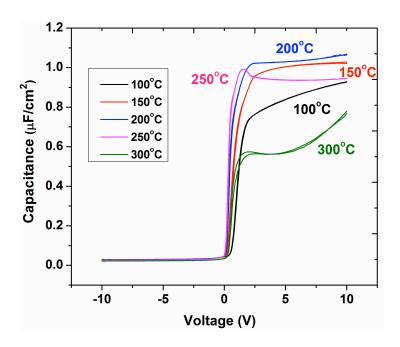

| Figure 2.4 C-V measurement for TiO <sub>2</sub> /Si MOS capacitors at different ALD temperatures 5                                                                                                                                                                                                                                    |

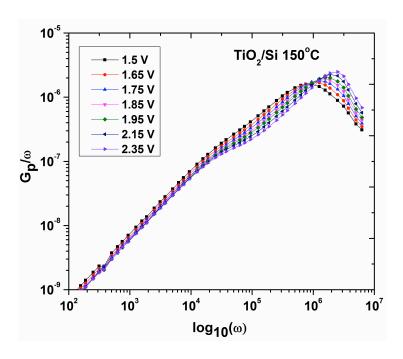

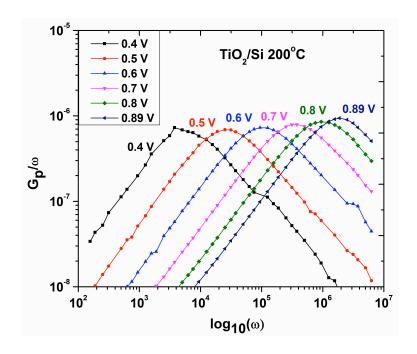

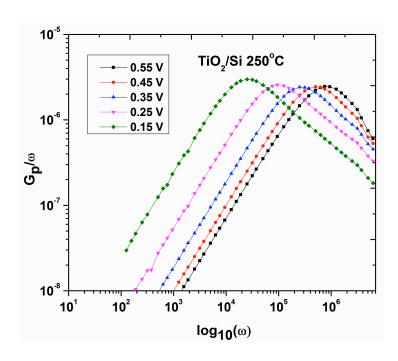

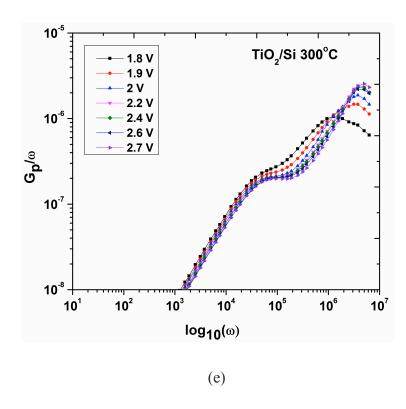

| Figure 2.5 versus as a function of gate voltage in the depletion region for TiO <sub>2</sub> /Si MO capacitors at (a) 100°C, (a) 150°C, (a) 200°C, (a) 250°C, and (a) 300°C                                                                                                                                                           |

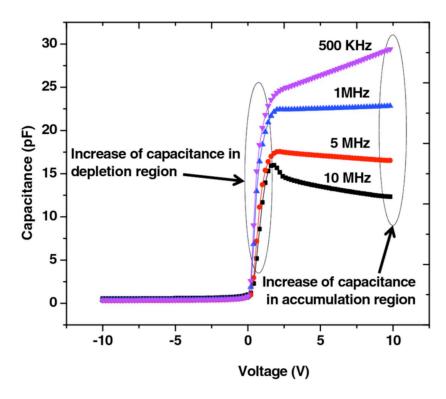

| Figure 2.6 (a) Simplified circuit of MOS capacitor including series resistance. (b) Interface tra                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| density distributions of ALD samples at different deposition temperatures                                                                                                                                                                                       |

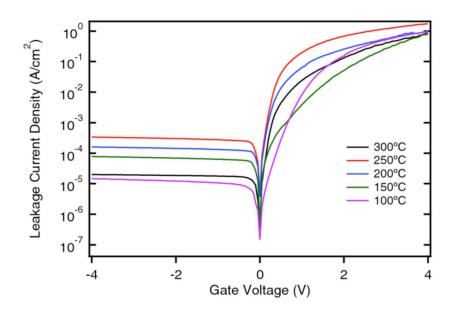

| Figure 2.7 Measured capacitance vs gate voltage as a function of frequency for the TiO <sub>2</sub> /Si a                                                                                                                                                       |

| 200°C deposition temperature.                                                                                                                                                                                                                                   |

| Figure 2.8 I–V characteristics of TiO <sub>2</sub> /Si MOS capacitor at different ALD temperatures 6                                                                                                                                                            |

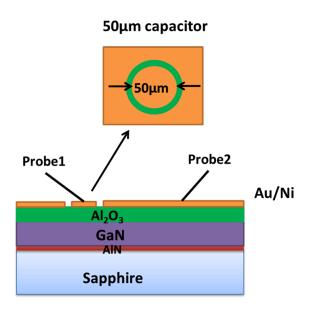

| Figure 3.1 Schematic showing position of only one capacitor in a sample                                                                                                                                                                                         |

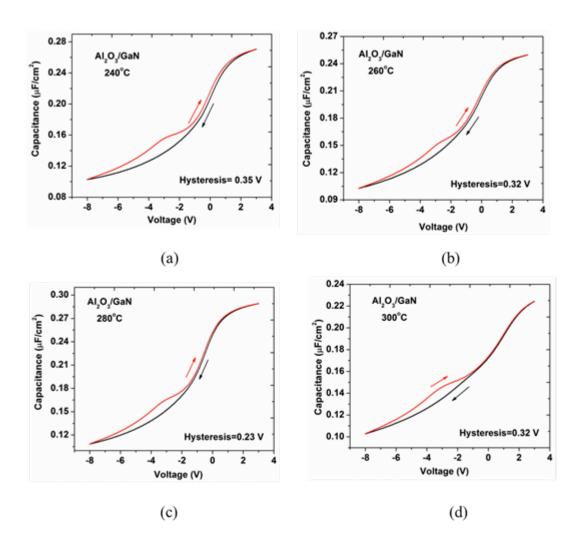

| Figure 3.2 Hysteresis of C-V plots at 1MHz of Al <sub>2</sub> O <sub>3</sub> /GaN MOS capacitors at (a) 240°C, (b) 260°C, (c) 280°C and (d) 300°C ALD temperatures                                                                                              |

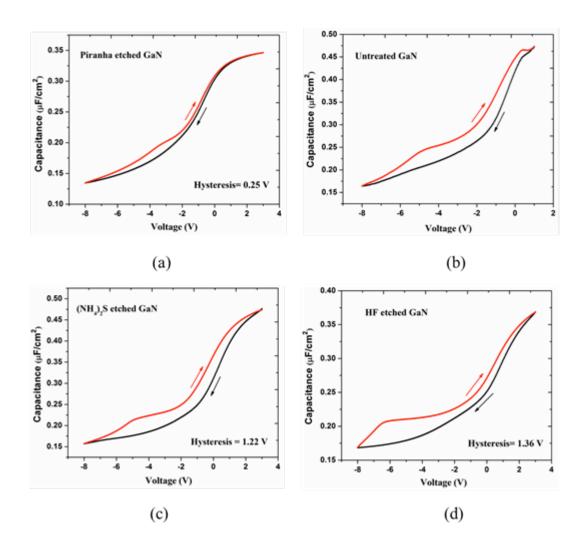

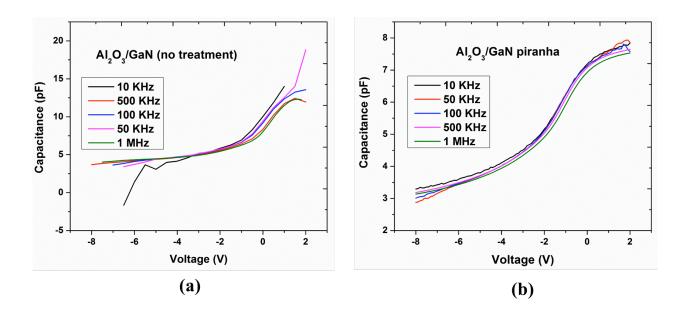

| Figure 3.3 Capacitance-voltage hysteresis plots of Al <sub>2</sub> O <sub>3</sub> /GaN for (a) piranha, (b) no treatmen (c) (NH <sub>4</sub> ) <sub>2</sub> S, and (d) 30% HF surface treatments at 280°C ALD deposition temperature 7                          |

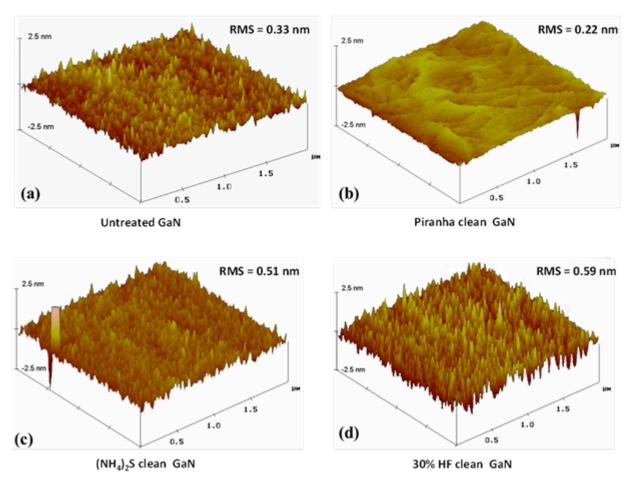

| Figure 3.4 Atomic force microscopy images of Al <sub>2</sub> O <sub>3</sub> where GaN surface pretreated with (a) network treatment, (b) piranha, (c) (NH <sub>4</sub> ) <sub>2</sub> S, and (d) 30% HF before deposition of Al <sub>2</sub> O <sub>3</sub>     |

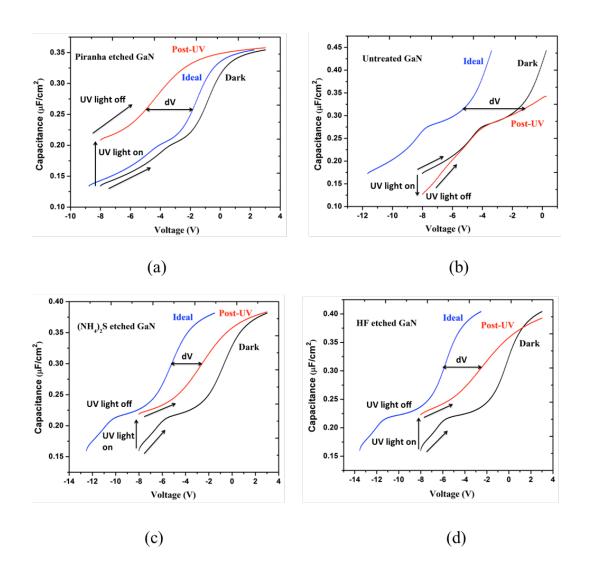

| Figure 3.5 C-V plots measured at dark, post-UV exposure and ideal C-V plot for MOS capacitor with (a) piranha, (b) Untreated (c) (NH <sub>4</sub> ) <sub>2</sub> S, (d) 30% HF etched GaN surface before oxide deposition                                       |

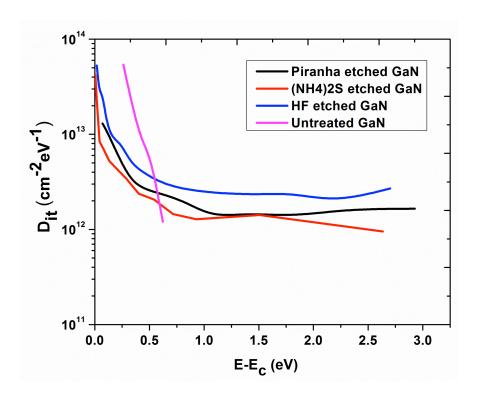

| Figure 3.6 Plots of $D_{it}$ (cm <sup>-2</sup> eV <sup>-1</sup> ) vs. energy (eV) from the conduction band (E <sub>c</sub> ) of Al <sub>2</sub> O <sub>3</sub> /Gal for no treatment, 30% HF, (NH <sub>4</sub> ) <sub>2</sub> S, and piranha surface treatments |

| Figure 3.7 Least frequency dispersion in piranha treated sample (b)                                                                                                                                                                                             |

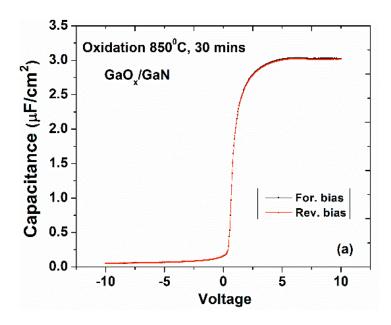

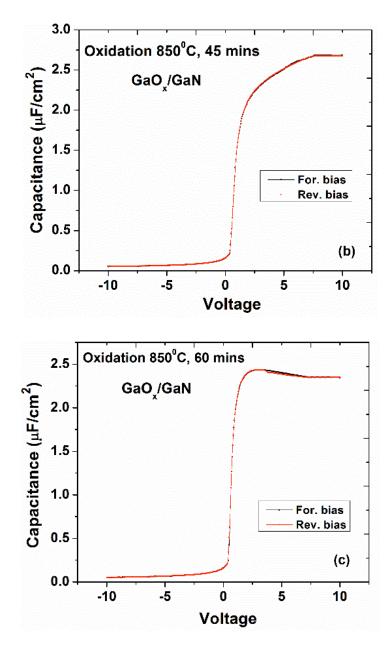

| Figure 4.1 High frequency C-V measurement of GaO <sub>x</sub> /GaN MOS capacitor, oxidized at 850° for (a) 30 mins, (b) 45 mins and (c) 60 mins.                                                                                                                |

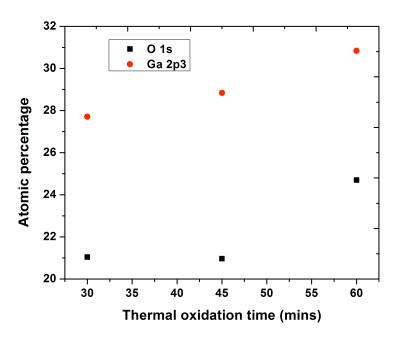

| Figure 4.2 Atomic percentage of oxygen and gallium for GaO <sub>x</sub> /GaN MOS capacitor, oxidized a 850°C for 30 mins, 45 mins and 60 mins                                                                                                                   |

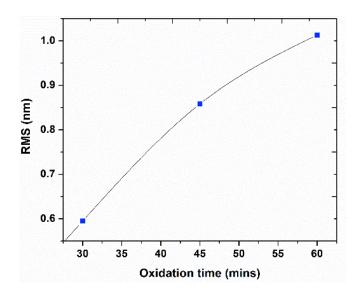

| Figure 4.3 GaO <sub>x</sub> surface roughness vs. oxidation time from AFM                                                                                                                                                                                       |

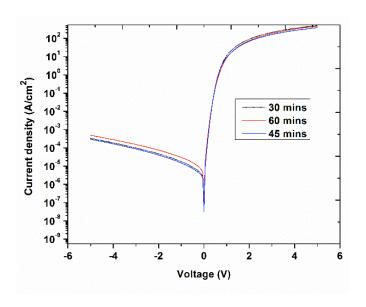

| Figure 4.4 Leakage current at reverse bias                                                                                                                                                           | 94    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

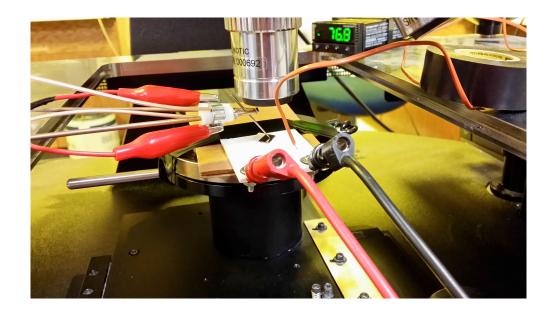

| Figure 5.1 Experimental setup for high temperature measurement                                                                                                                                       | . 101 |

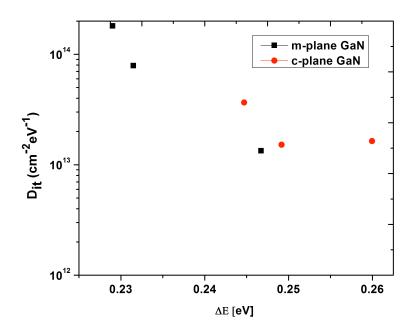

| Figure 5.2 Interface trap density, D <sub>it</sub> as a function of the energy separation from the conduband edge for <i>c</i> - and <i>m</i> -plane GaN MOS capacitors measured at room temperature |       |

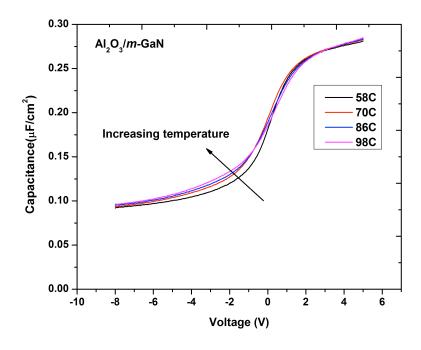

| Figure 5.3 Capacitance-voltage plot as a function of temperature for <i>m</i> -plane GaN 1 capacitors at 100 KHz and dc sweep rate of 0.1 V/s                                                        |       |

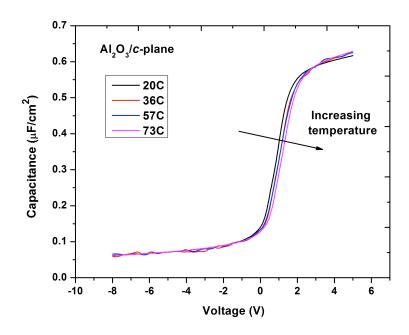

| Figure 5.4 Capacitance-voltage plot as a function of temperature for <i>c</i> -plane GaN 1 capacitors at 100 KHz and dc sweep rate of 0.1 V/s                                                        |       |

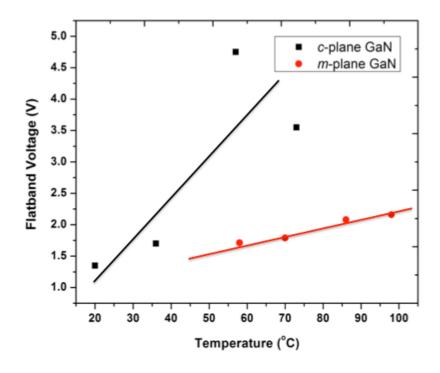

| Figure 5.5 Flatband voltage as a function of temperature for <i>c</i> - and <i>m</i> -plane GaN MOS capac                                                                                            |       |

# **List of Tables**

| Table 1-1 Transistor count, frequency, and market growth in integrated circuits <sup>7</sup>                                                                                                                             | 4       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Table 1-2 GaN substrates <sup>46</sup>                                                                                                                                                                                   | 24      |

| Table 1-3 GaN/sapphire defects                                                                                                                                                                                           | 25      |

| Table 1-4 Important properties of semiconductors <sup>45</sup>                                                                                                                                                           | 30      |

| Table 1-5 Static dielectric constant (κ) of gate dielectrics <sup>70,86</sup>                                                                                                                                            | 34      |

| Table 1-6 Previous studies of high-κ gate oxide on GaN                                                                                                                                                                   | 37      |

| Table 2-1 Oxygen and titanium ratio, average carbon concentration, thickness, dielectric of TiO <sub>2</sub> and calculated values of D <sub>it</sub> for TiO <sub>2</sub> /Si samples prepared at differe temperatures. | ent ALD |

| Table 3-1 C-V characteristics showing effect of ALD deposition temperatures                                                                                                                                              | 74      |

| Table 3-2 C-V characteristics showing effect of GaN surface treatment                                                                                                                                                    | 75      |

| Table 3-3 XPS analysis showing atomic percentage of carbon concentration in oxid Al <sub>2</sub> O <sub>3</sub> /GaN interface                                                                                           |         |

| Table 4-1 Oxygen concentration for GaO <sub>x</sub> /GaN samples oxidized for 60 mins at oxidation temperature                                                                                                           |         |

| Table 4-2 Oxide thickness and O:Ga ratio from XPS                                                                                                                                                                        | 92      |

| Table 4-3 Interface trap density                                                                                                                                                                                         | 93      |

# Acknowledgements

I express my gratitude to my major Professor, Dr. James Edgar for giving me the opportunity to explore in the world of semiconductor device fabrication and characterization. The completion of my Ph.D. would never have been possible without his countless support, encouragement, significant guidance and financial support. He spent endless hours proofreading my manuscripts and provided me excellent suggestions. I am very grateful to the scientists of Naval Research Laboratory. I am grateful to Dr. Chip Eddy Jr., Dr. Nelson Garces, Dr. Neeraj Nepal for device fabrication and ellipsometry and Dr. Jennifer Hites for MOCVD growth of GaN layer on sapphire. I also wish to thank them for their valuable comments on our manuscripts and for their collaboration. My special thanks to my friend Daming Wei for his hard work for XPS, AFM and XRD measurements and data interpretation. I am extremely grateful to Dr. Andrew Rys for many fruitful discussions throughout the research and kindly letting me use his LCR meter. I express my gratitude to Dr. Vikas Berry for letting me use the UV light source. I wish to thank Dr. Daniel Boyle and Dr. Gurpreet Singh for the training on scanning electron microscopy. I express my appreciation to Dr. Jennifer Anthony of Kansas State University and Jason Schmitt, Dr. Troy Baker and Ashley Mayo of Nitride solutions for the x-ray diffraction measurement. I would like to send warm thanks to my committee members, Dr. John Schlup and Dr. Keith Hohn for their guidance and encouragement.

I would like to thank Dr. Harry Meyer III of Oak Ridge National Lab for the x-ray photoelectron spectroscopy measurement. I am grateful to all the faculty members and the staff of the Chemical Engineering Department at Kansas State University. I thank many past and present graduate students – Dr. Clinton Whiteley, Dr. Nihar Mohanty, Dr. Yi Zhang, Clint Frye, Balaji Padavala, Romil Bhandavat and Phong Nguyen for their various help and useful conversations. I wish to thank Florence Sperman, Karey Debardeleben, and Pat Nelson in the office and Dave Threewit for experimental setup.

Finally, my heartfelt gratitude to Almighty Allah, my parents, brother and my sincere appreciation to my wife and son Alvan.

# **Dedication**

I dedicate this dissertation to my father Md. Mosharrof Hossain, mother Hamida Hossain, brother Md. Tanzin Riad Hossain, wife Mahfuza Lima, and son Alvan.

# **Chapter 1 - Introduction**

#### 1.1 Dissertation outline

Metal-oxide-semiconductor capacitor (MOSCAP) is the fundamental building block to constitute microprocessor. The efficiency and reliability of the microprocessor depends greatly on the process condition of the fabrication of each element of the MOSCAPs. The ultimate goal is to obtain minimum leakage current through the gate oxide and minimize the interface traps in insulator-semiconductor interface. Achievement of these goals is highly dependent on the technique used to fabricate the MOSCAPs. If the MOSCAPs are optimized during fabrication, the electrical characteristics would improve significantly and the microprocessors can perform effectively.

This research aims to find the best conditions to fabricate high-k dielectrics (oxides) on GaN or Si. GaN is a wide bandgap semiconductor with exceptional material properties that play a key role in power electronics. The Si/SiO<sub>2</sub> interface is the heart of the modern metal-oxidesemiconductor field effect transistors but as transistors are down scaled, SiO2 as a gate dielectric causes several problems; a high leakage current, reduced drive current, reliability degradation and impurity penetration <sup>1</sup>. Therefore, finding an alternate gate dielectric is essential, and much research across the globe has been devoted to investigate alternative high-κ dielectrics in MOS transistors. The motivation of using high-k dielectrics is to reduce the leakage current without any reduction in oxide capacitance. In this research, Al<sub>2</sub>O<sub>3</sub> and TiO<sub>2</sub> were used as high-κ dielectrics and were deposited on GaN and Si, respectively, by atomic layer deposition, a technique chosen for its exceptional uniform oxide film control. But deposited high-κ dielectrics do not form low defect density interfaces with semiconductors as well as SiO2 with Si; there are many defects at the interface on silicon and III-V nitride (or III-N) semiconductors. Using high-κ oxide shows the flatband voltage to shift from its ideal position in capacitance-voltage measurement due to the existence of uncompensated charge in the dielectric and on silicon substrate; high-κ oxide can alter the oxide thickness by creating an interfacial layer.

In this research, methods to improve the high-κ dielectric-semiconductor interface and minimize leakage current density were investigated. The research focuses on fabrication and

characterization of the MOSCAPs, the fundamental element of the integrated circuits. The hypothesis is that if the dielectric-semiconductor interface quality and leakage current density of the MOS capacitors can be improved, the advantages will definitely be seen at the output of the various transistor devices used in power electronics and memory technology.

The properties of the high-κ dielectric and its interface with the semiconductor were evaluated using electrical measurements, such as capacitance-voltage (C-V) and current-voltage (I-V) measurements. C-V measurements were taken to determine the flatband voltage, threshold voltage, fixed charges and dielectric-semiconductor interface trap charges. I-V measurements were done to obtain the leakage current density. This research explored dry thermal oxidation of GaN. Thermal oxidation of Ga<sub>2</sub>O<sub>3</sub> on GaN is a cheaper and simple process. The high interface trap density and foreign contaminants observed with the deposited dielectrics on GaN can be minimized with thermal oxidation. The GaN surface treatment before atomic layer deposition of the dielectric plays a significant role in reducing device defects. Finding the best semiconductor surface treatment with least surface roughness and impurity concentration along the depth of the device was an essential part of this research. Therefore, one of the goals of this research was to connect the electrical performance attributes to the physical and chemical properties of the devices. The chemical properties of the deposited dielectric on semiconductor were characterized by x-ray photoelectron spectroscopy (XPS) and surface roughness of the deposited dielectric was characterized by atomic force microscopy (AFM).

The first chapter of this dissertation presents the technical background of this research. It discusses the fundamental knowledge required for a basic understanding of MOS capacitors. The electrical measurement technique and characterization of MOS capacitor by capacitance-voltage measurement were discussed. Since this research revolves around Al<sub>2</sub>O<sub>3</sub> gate oxide on GaN and TiO<sub>2</sub> on Si, an explanation is provided about the motivation for the selection of the high-κ dielectrics and the semiconductor, GaN. An explanation is provided about selecting sapphire as a substrate for the growth of GaN. The non-ideal effects of the MOS capacitor and defects are discussed. This chapter concludes by reviewing the previous work on high-k gate oxides on GaN MOS devices.

The second chapter describes the influence deposition temperature has on the structure, composition and electrical properties of TiO<sub>2</sub>/Si MOS capacitors. The extraordinarily high dielectric constant of TiO<sub>2</sub>, its deposition by plasma atomic layer deposition, and what impact TiO<sub>2</sub> had on leakage current density motivated this study.

The third chapter examines the electrical properties of Al<sub>2</sub>O<sub>3</sub> on GaN, as prepared by thermal atomic layer deposition. The factors examined included the wet chemical etching of the GaN, the deposition temperature. Cleaning of the semiconductor prior to oxide deposition is very critical to fabricate high performance semiconductor devices. This study was motivated by the findings of Nepal *et al.* <sup>2</sup> and further study was done to investigate the effect of semiconductor surface treatment on average density of oxide trapped charge and Al<sub>2</sub>O<sub>3</sub>/GaN interface trap density.

The fourth chapter describes a study of the dry thermal oxidation of GaN at different process conditions with the objective of finding the best process condition to obtain a very thin native oxide of GaN with the best electrical properties. The hypothesis is that the native thermal oxidation may result in a low interface trap density compared to deposited dielectric films, not native to the semiconductor.

In fifth chapter, an investigation was done on nonpolar (*m*-plane) GaN-based MOS capacitors with Al<sub>2</sub>O<sub>3</sub> as the gate dielectric. The study was motivated by the advantages of the *m*-plane GaN (lack of polarization effect, normally off operation) transistors, including low power consumption and failsafe operation in the power electronics industry. GaN MOSFETs are capable of exceptional performance in high temperature electronics, but their performance is deteriorated if polar GaN orientations are used since spontaneous polarization charge causes an unwanted threshold voltage shift and eventually causes the device to fail. Therefore, in this study, MOS capacitors were fabricated both on *c*- and *m*-plane GaN to investigate the temperature behavior. The work of Matocha et al. <sup>3</sup> on SiO<sub>2</sub>/GaN on polar and nonpolar GaN crystal planes motivated this study with Al<sub>2</sub>O<sub>3</sub>/GaN MOS capacitors.

# 1.2 Technical Background

The semiconductor industry has achieved phenomenal growth over the last few decades due to rapid advancements in device (transistor) integration technologies. Hundreds of millions of field-effect transistors (FETs) are found in modern microprocessors. The transistor was first proposed by J.E.Lilienfeld in 1928, but due to surface states (electron traps) at the interface between semiconductor and insulator, it was not possible to achieve success during that time <sup>4</sup>. A breakthrough was achieved in 1960 by D. Kahng, when he fabricated a field effect transistor that had low trap interface between Si and its native oxide, SiO<sub>2</sub> <sup>5</sup>. The first integrated circuit with two transistors was made by Jack Kilby in 1958 at Texas Instrument; today a 16GB flash memory chip consists of more than 4 billion transistors. Since the integrated circuit was first invented, the transistor count has increased by orders of magnitude (Table 1.1). The limitations of bipolar transistors (quiescent power dissipated when circuit is not switching) were rectified by the invention of Metal Oxide Semiconductor Field Effect Transistors (MOSFETs) in 1960s as it draws almost zero current when idle. Based on an observation of Gordon Moore <sup>6</sup>, the cofounder of Intel in 1965, the number of transistors has doubled every 26 months by scaling down the size of the transistors and thus reducing the cost of a chip.

Table 1-1 Transistor count, frequency, and market growth in integrated circuits <sup>7</sup>

|                   | 1 <sup>st</sup> generation | 2 <sup>nd</sup> generation | 3 <sup>rd</sup> generation | 4 <sup>th</sup> generation |

|-------------------|----------------------------|----------------------------|----------------------------|----------------------------|

| Year              | 1985                       | 1993                       | 2004                       | 2010                       |

| Transistor counts | $10^5 - 10^6$              | $10^6 - 10^7$              | $10^8 - 10^9$              | $10^9 - 10^{10}$           |

| Clock             | $10^{7}$                   | 108                        | 10 <sup>9</sup>            | 10 <sup>9</sup>            |

| frequencies       | 10                         | 10                         | 10                         | 10                         |

| Worldwide         | \$25B                      | \$60B                      | \$170B                     | \$250B                     |

| Market            | \$23 <b>D</b>              | \$000                      | \$1/00                     | \$230D                     |

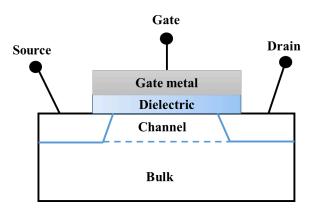

The transistor can act as an amplifier or a digital switch and it can be turned on or off by applying a bias to the gate. The MOSFET consists of drain, source, gate and bulk (Figure.1.1). The source and drain are the two terminals of the switch, which are electrically connected or isolated by applying a bias to the gate. The gate bias controls the channel that is insulated from gate by a dielectric. In inverters, power transistors are used as a switch.

Figure 1.1 Si MOSFET

### 1.2.1 MOS capacitors and capacitance-voltage measurement

Hundreds of millions of field effect transistors (FETs) constitute modern microprocessor and the metal oxide semiconductor (MOS) capacitor is the central part of these transistors. MOS capacitors are the basis of digital logic circuits, random access memories (RAMs) and chargecoupled devices (CCDs). It operates using the field effect. MOS capacitors have two heterojunctions, a metal-dielectric and a dielectric-semiconductor. It is a transistor without source or drain, and it is formed when two conducting layers are isolated by a dielectric. The practical application of the MOS capacitor depends greatly on the quality of the dielectricsemiconductor interface. The metal contact of the MOS capacitor in a MOSFET is known as the gate and the dielectric as the gate oxide. Capacitance-voltage measurements are widely used to characterize MOS capacitors, to gain insights to improve of device performance. A C-V measurement is done to obtain interface trap density 8-12, oxide thickness 13-15, effective mobility <sup>16-18</sup> and substrate doping profile <sup>19-21</sup>. Compared to a parallel plate capacitor, the metal contact constitutes one plate with the dielectric and the majority carriers in the semiconductor constitute the other plate. In general, capacitance is the change in charge (integration of current over time) in a device with change in voltage,  $C = \Delta Q/\Delta V$ . Also, capacitance is expressed by  $C = A \epsilon_r \epsilon_0 / T_{ox}$ where A is the area of the capacitor,  $\varepsilon_r$  is the dielectric constant of the gate oxide,  $\varepsilon_0$  is the permittivity in free space ( $\varepsilon_0 = 8.854 \times 10^{-14}$  F/cm), and  $T_{ox}$  is the thickness of the gate oxide. As the capacitance of a dielectric is proportional to  $\varepsilon_r$  and inversely proportional to dielectric

thickness, a high gate dielectric capacitance is required to meet the drive current for proper operation in scaled semiconductor devices.

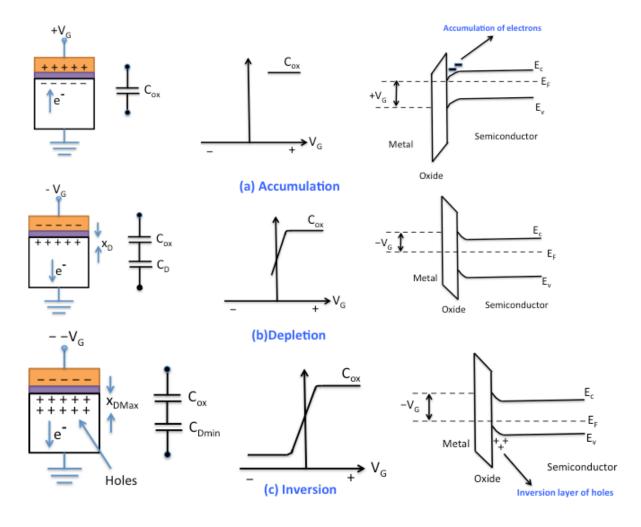

There are three characteristics region of operation of an MOS capacitor; accumulation, depletion and inversion. In the accumulation region, for an n-type semiconductor, application of positive gate voltage greater than flatband voltage ( $V_{GB} > V_{FB}$ ) results in accumulation of negative charges (electrons) at the semiconductor surface just below the oxide-semiconductor interface (Figure 1.2a). V<sub>FB</sub> is the flatband voltage where ideally there is no electric field across the oxide but in reality a built-in voltage is created due to difference in work function of metal and semiconductor and this results in band bending even when no voltage is applied. The flatband voltage is also the gate voltage that neutralizes the built-in potential, so there is no potential difference between the semiconductor surface and the bulk of the semiconductor (surface potential =  $0 = V_G - V_{FB}$ , at flat band condition) <sup>22</sup>. The oxide capacitance can be measured as a function of gate voltage by superimposing a small ac signal on gate voltage. The change in applied gate voltage ( $\Delta V_G$ ) leads to accumulation charge density ( $\Delta Q = C_{ox} \Delta V_G$ ). Capacitance per unit area is voltage independent and is determined by the gate oxide thickness,  $C_{ox}$  (F/cm<sup>2</sup>) =  $\varepsilon_r/T_{ox}$ . Due to gate voltage, penetration of electric field into semiconductor or accumulation layer thickness can be determined from Poisson's equation and is known by Debye length (L<sub>D</sub>), which is inversely proportional to doping level. At the flatband condition, the capacitance  $(1/C_{FB} = 1/C_{ox} + 1/C_s)$  is a series combination of gate-oxide capacitance and semiconductor capacitance ( $C_s = \varepsilon_s/L_D$ ) where  $\varepsilon_s$  is the dielectric constant of the semiconductor. The band diagram of the accumulation region shows that the difference in Fermi level (E<sub>F</sub>) between the metal and the semiconductor is equal to the applied gate voltage. Assuming downward bending for an *n*-type semiconductor, the application of a positive gate voltage shifts E<sub>F</sub> towards the conduction band edge of the semiconductor (E<sub>C</sub>) and electrons accumulates at the surface of the semiconductor underneath the oxide. The flatband voltage from the C-V plot was obtained at the corresponding capacitance (C<sub>FB</sub>), which is expressed as

$$C_{FB} = \frac{\varepsilon_{S} C_{ox}}{C_{ox} \lambda + \varepsilon_{S}}$$

(1)

where  $\varepsilon_s$  is the permittivity of the semiconductor,  $C_{ox}$  is the oxide capacitance in accumulation region and  $\lambda$  is the Debye length expressed as

$$\lambda = \sqrt{\frac{\varepsilon_S kT}{q^2 N_D}} \tag{2}$$

where N<sub>D</sub> is the doping density and k is the Boltzmann's constant.

In the depletion region, a negative dc gate voltage is applied and the majority carriers electrons are repelled from the oxide-semiconductor interface creating a depletion region to a depth  $x_D$ . This negative gate voltage is balanced by positive charge from the ionized semiconductor donor atoms. The capacitance of the depletion region per unit area is given by  $C_D = \varepsilon_s/x_D$ .  $x_D$  increases with gate voltage, and the overall capacitance of the MOS structure in the depletion region ( $1/C = 1/C_{ox} + 1/C_D$ ) consists of  $C_{ox}$  and variable depletion capacitance ( $C_D$ ). From Figure 1.2b, it can be observed from C-V plot in depletion region, as gate voltage becomes more negative, the capacitance decreases with increase in depletion depth  $x_D$ . The band diagram in depletion region shows an upward bending of the semiconductor conduction band and as a result,  $E_F$  remains away from both the conduction band ( $E_C$ ) and valence band ( $E_V$ ) edges. In depletion, gate charge per unit area,  $Q_G = Q_D = N_D x_D$ .

In the inversion region, the magnitude of dc gate voltage becomes more negative, and this attracts minority carriers (holes) in the semiconductor to the surface and inversion layers of holes are created (Figure 1.2c). The gate voltage at which this inversion occurs is called the threshold voltage. It is also the voltage at which a transistor actually turns on. After formation of inversion layer, the depletion depth  $x_D$  does not expand and remains "pinned" at  $x_{DMax}$ . The band diagram in inversion region shows that band bending placed  $E_F$  close to  $E_V$ , leading an exponential increase of holes in inversion layer. In inversion, gate charge per unit area,  $Q_G = N_D x_D + Q_I$  where  $Q_I$  is the charge density in the inversion layer and gate charge is compensated mostly by inversion charge density in inversion region. The threshold voltage of a MOS capacitor is expressed as  $^{23}$

$$V_{th} = V_{FB} \pm \left[ \frac{A}{C_{ox}} \sqrt{4\varepsilon_s q |N_{bulk} \phi_B|} + 2|\phi_B| \right]$$

(3)

where  $\epsilon_s$  is the permittivity of the semiconductor, q is the electron charge (1.6×10<sup>-19</sup>C), N <sub>bulk</sub> is the bulk doping and  $\phi_B$  is the bulk potential. The bulk potential is expressed as

$$\phi_{B} = -\frac{kT}{q} \ln \left( \frac{N_{bulk}}{N_{i}} \right) (Dopetype)$$

(4)

where T is the test temperature,  $N_i$  is the intrinsic carrier concentration and conductivity type is -1 for a n-type semiconductor

Figure 1.2 MOS capacitor structures, C-V plots and band diagrams in (a) accumulation, (b) depletion, and (c) inversion region <sup>24</sup>.

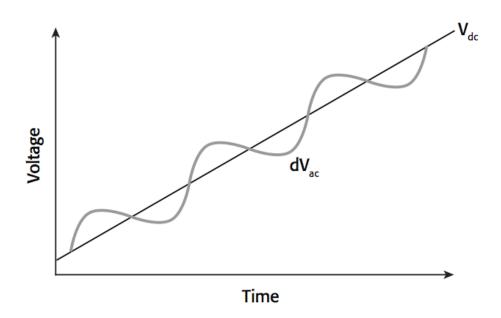

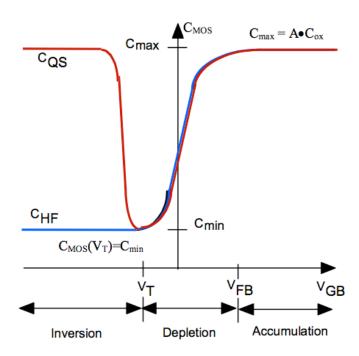

C-V measurements can be done in quasistatic or high frequency conditions. During high frequency (100 kHz to 1MHz) C-V measurement, an ac signal is superimposed on a dc gate voltage (Figure 1.3). Due to high frequency ac signal,  $Q_I$  cannot provide the charge necessary for additional  $\Delta Q_G$  because there are no additional holes in the substrate; and, in order to satisfy charge neutrality, majority carriers respond to the high frequency ac voltage by thermal generation and recombination  $^{25}$ . Also, the oxide-semiconductor interface traps do not respond to high frequency ac gate voltage but can follow the slow change in dc gate voltage. This leads to a stretch out of the high frequency C-V curve. Quasistatic measurements (equilibrium condition) are taken at a very low frequency (1-10 Hz), which is almost dc (Figure 1.4). In quasistatic measurement  $Q_I$  can follow changes in  $Q_G$ . The asymmetrical shape of the high frequency C-V

plot can be used to determine the conductivity type of the semiconductor. For a MOS capacitor with a *p*-type semiconductor, the C-V plot sweeps from accumulation to inversion region as gate voltage becomes more positive and for MOS capacitor with an *n*-type semiconductor, the gate voltage approaches a negative value when sweeping from accumulation to inversion.

Figure 1.3 ac voltage superimposed on dc voltage during C-V measurement <sup>26</sup>

Figure 1.4 Low-frequency and high frequency capacitance-voltage plots <sup>27</sup>

In a high frequency capacitance-voltage plot, the accumulation region defines the oxide capacitance,  $C_{ox}$ ; and most MOS capacitor characterization is dependent on  $C_{ox}$ . Therefore, it is important to select the start and stop voltage so that the depletion region remains within 1/3 to 2/3 of the dc voltage sweep range, and the device can be biased into strong accumulation region. During dc voltage sweep, the delay time is optimized to keep the device in equilibrium, otherwise a skewed C-V plot is obtained when the dc sweep rate is too fast. If the delay time is too small or the duration of the dc sweep is very short, the MOS capacitor does not have enough time to generate minority carriers for the formation of the inversion layer. It is better to start the dc voltage sweep from accumulation, because starting the sweep from inversion creates a non equilibrium situation that requires time to recover before the C-V sweep is initiated. Sometimes, sweeping the dc voltage from inversion is necessary to investigate hysteresis, and in that case, light can be used to generate minority carriers so equilibrium is reached quickly, and the hold time can be minimized before dc sweep. A device is in equilibrium if no hysteresis is observed while sweeping the dc voltage either from the accumulation or the inversion end.

### 1.2.2 Equivalent circuit model of MOS capacitor

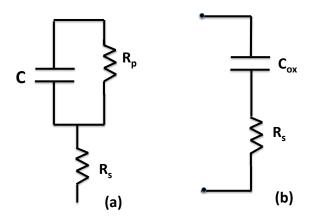

Basic impedance parameters can be obtained by measuring the amplitude of the impedance. In order to extract actual capacitance from the impedance of MOS devices, an equivalent circuit model is required. There are parallel and series model as the two common ac impedance models. There are series circuit model for low leakage devices and parallel circuit model for low series resistance devices (Figure 1.5). A parallel model is also used to measure low values of the capacitance of dielectrics and contain interface trap information.

Current due to the small alternating (ac) signal response passes through the MOS capacitors connected to a circuit, and the ratio of alternating (ac) current to ac voltage (admittance) of the MOS capacitor consists of information about the MOS structure. Admittance is the reciprocal of impedance (Y = 1/Z). In alternating current, impedance (Z = R + jX) is the sum of a real number, the ac resistance, and an imaginary part, the reactance (X). Admittance (Y = G + jB) is the sum of a real number, the ac conductance and an imaginary part, the susceptance (X). In the accurate model of the small-signal equivalent circuit, X is the actual frequency independent device capacitance, X0 is the effective device resistance due to tunneling through the oxide, and X1 is the series resistance of the substrate and the gate X2.

Figure 1.5 (a) Small-signal equivalent circuit model for MOS capacitor, (b) simplified model to obtain series resistance in strong accumulation

The admittance in strong accumulation in Figure 1.5b is  $Y_{ma} = G_{ma} + j_{\omega} C_{ma}$ , where  $G_{ma}$  and  $C_{ma}$  are the measured conductance and capacitance, respectively. The series resistance is expressed as

$$R_{s} = \frac{G_{ma}}{G_{ma}^{2} + \omega^{2} C_{ma}^{2}} \tag{5}$$

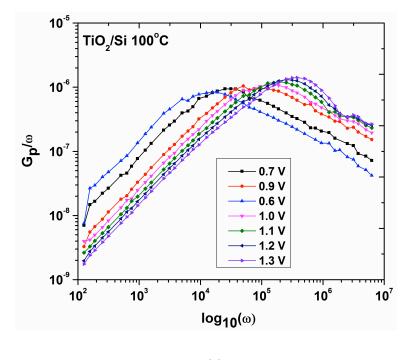

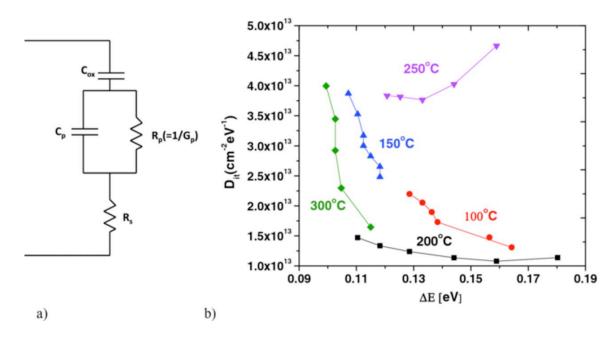

The equivalent parallel conductance method possess the same interface trap information as the equivalent parallel model, but the conductance method is more sensitive because conductance is directly related to the energy loss by the ac signal during capture and emission of carriers by interface traps (Figure 1.6). The Conductance method is more accurate in determining the interface trap density <sup>29</sup>. This model was used to determine interface trap density in chapter 2 and 5.

Figure 1.6 Equivalent circuit of the parallel capacitance and conductance with series resistance

## 1.2.3 Experimental approach

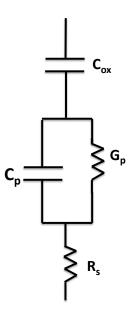

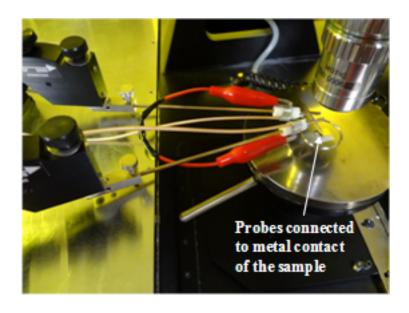

In this project, the fabrication of MOS capacitor samples was done at Naval Research Laboratory (NRL), Washington DC. The process of fabrication involves growth of GaN on sapphire, deposition of the dielectrics on GaN or Si and deposition of metal contact by photolithography. The thickness of the dielectric was also measured in NRL using ellipsometry. At different stage of the fabrication process, the samples were sent to Kansas State University for surface characterization. After completion of the fabrication process, I was involved in electrical characterization of the samples using capacitance-voltage and current-voltage measurement. My group mate Daming Wei was involved in surface characterization using AFM, XPS and XRD.

Capacitance-voltage measurements were performed using a Keithley 4200 semiconductor characterization system, which is an ac impedance meter. In an ac impedance meter (Figure 1.8), the ac voltage originates from the high current terminal (HCUR) and the current at the output of the device under test (DUT) is measured at the low current terminal (LCUR). The voltage of the device under test is measured by the difference between the high (HPOT) and low terminal (LPOT). Stray capacitance is minimized by using a short coaxial cable between measurement leads. The impedance should be identical to the coaxial cable and the ac impedance meter. BNC connectors are attached to the coaxial cables to minimize deviation from the actual value due to a high series contact resistance. The dc current-voltage is measured using low noise triaxial cables. When the ac signal passes through a cable, a phase shift occurs that is proportional to the cable length and ac signal propagation delay. Therefore, cable length compensation is done to rectify the phase offset for a particular cable <sup>30</sup>. It is important in high frequency measurement to connect a very short wire jumper (red wire in Figure 1.7) between the two probes heads to confirm good ground connection and to prevent a large inductance and error in capacitance measurement.

Figure 1.7 Wire jumper (red cable) between probes

Figure 1.8 Schematic of an ac impedance meter <sup>30</sup>

Figure 1.9 Experimental approach in the research

# 1.2.4 MOCVD of GaN epilayer

The GaN epilayers were grown by metal organic chemical vapor deposition (MOCVD). MOCVD has a faster growth rate than MBE and is thermodynamically stable. Ga-polar *c*-plane wurtzite GaN epilayers on sapphire were employed for the fabrication of Al<sub>2</sub>O<sub>3</sub>/n-GaN MOS capacitors. The epilayers consisted of a 1.5μm thick Si-doped, *c*-plane GaN grown on *a*-plane sapphire via MOCVD, using a 25 nm thick AlN buffer layer. The GaN epilayers were deposited at 1050°C, 150 Torr, using a V/III ratio of 3500. The precursors for the GaN epilayers were trimethylgallium and ammonia. Silicon doping, on the level of 1x10<sup>18</sup> cm<sup>-3</sup>, was achieved through the addition of silane.

### 1.2.5 Atomic layer deposition

Atomic layer deposition (ALD) is used to deposit high-k dielectrics for many applications including pin-hole free passivation layers for OLEDs <sup>31</sup>, fuel cells <sup>32</sup>, organic semiconductors <sup>33</sup>, adhesion layers <sup>34</sup>, BioMEMS <sup>35</sup> and passivation of crystal silicon solar cells as examples. During atomic layer deposition, deposition occurs due to chemisorption of precursor vapor one atomic layer per each cycle, pinhole and particle free. Conformal deposition is possible on structures with high aspect ratios. It is a self-limiting layer-by-layer deposition process. Compared to other deposition methods, ALD is capable of the highest step coverage (Figure 1.10).

Figure 1.10 Step coverage (%) vs deposition rate  $^{36}$

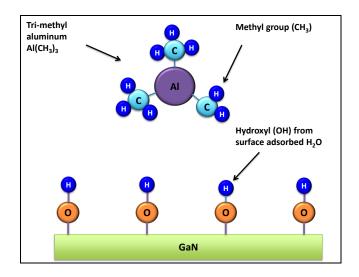

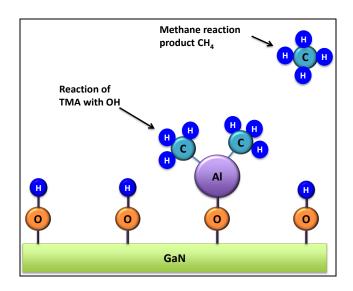

During thermal ALD, Al<sub>2</sub>O<sub>3</sub> is deposited using the precursor trimethylaluminum (TMA) and water, and methane is formed as a byproduct. During plasma ALD, an O<sub>2</sub> plasma is used instead of water. With a plasma discharge, the oxygen is dissociated. Plasma ALD enables deposition at a low temperature than thermal ALD and there is reduction in purge time of the

precursor as water is not used. The surface chemistry during atomic layer deposition of  $Al_2O_3$  can be described as follows where the asterisks refers to surface species  $^{37}$

$$AlOH^* + Al(CH_3)_3 \rightarrow AlOAl(CH_3)_2^* + CH_4$$

$$AlCH_3^* + H_2O \rightarrow AlOH^* + CH_4$$

The driving force for the reaction is the formation of a strong Al-O bond. The overall exothermic reaction with an enthalpy of 376 kcal/mole is as follows

$$2Al(CH_3)_3 + 3H_2O \rightarrow Al_2O_3 + 3CH_4$$

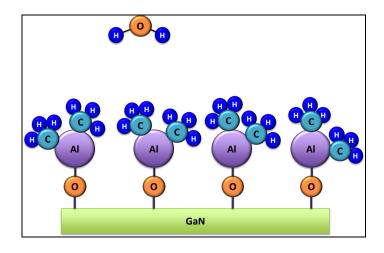

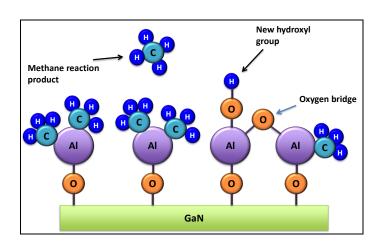

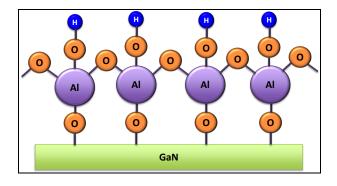

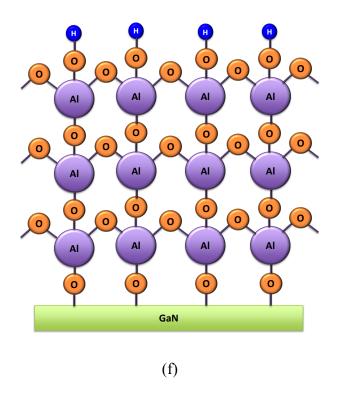

Due to contact with air, the GaN surface is terminated with hydroxyl groups (Figure 1.11a). The GaN epilayer on sapphire is placed inside ALD reactor and TMA is introduced as the first precursor. The TMA precursors (which don't react with each other) react with GaN surface hydroxyl groups and a single saturated monolayer is formed (Figure 1.11c). Methane is formed and both the methane and unreacted TMA are pumped out of the reactor. During the next half cycle, water vapor is introduced and creates saturated monolayer of oxygen on top of the aluminum atoms, and methane is formed as the reaction product. The methane and water are pumped away from the ALD reactor. Again TMA is introduced to start another cycle and the cycle repeats until target thickness of the dielectric is achieved (Figure 1.11f). In this research, the carrier gas of the precursors was 20 sccm ultra high purity nitrogen. The TMA pulse was 0.015 sec, the nitrogen purge was 20 secs, and the DI water pulse was 0.015 sec. The temperature of the reactor was 280°C for Al<sub>2</sub>O<sub>3</sub> deposition at optimized conditions but other temperatures were also examined.

(a)

(b)

(c)

(d)

(e)

Figure 1.11 Schematic of the ALD process (a) TMA pulse in the reaction chamber, (b) TMA reacts with hydroxyl group, (c) Termination of reaction after one monolayer, (d) water reacts with dangling methyl groups forming Al-O strong bond, (e) formation of hydroxyl groups and, (f) after 3 ALD cycles <sup>38</sup>

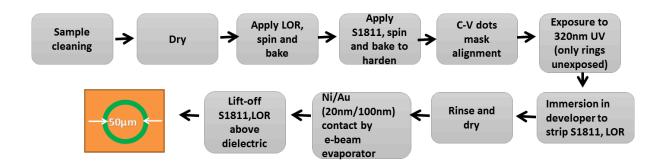

### 1.2.6 Fabrication of metal contact

Metal contacts (Ni/Au) were fabricated using standard method of photolithography and e-beam evaporation. In this study, prior to any photolithography steps, the GaN samples were cleaned with warm acetone (~ 40°C), followed by rinsing in DI water and then drying off with compressed nitrogen. Excess water and moisture were removed by placing the samples on a hot plate at 175°C for approximately 5 minutes. Gradually lift-off resist (LOR) 5A (Microchem) and positive photoresist S1811 (Microchem) was applied. The photoresist was baked to harden, to improve the adhesion of the photoresist film, and to make it less susceptible to contamination. The photolithography mask was designed to produce circular capacitors of four different sizes

(50μm, 100μm, 150μm and 300μm). The sample was exposed to 320 nm UV light source for 35 seconds after mask alignment. Samples were immersed in developer CD-26 (RohmHaas) for 75 seconds to strip S1811 and lift-off resist from circular capacitors keeping unexposed photoresist only on the rings outside the capacitors (Figure 1.12). The samples were then rinsed in DI water and dried with N<sub>2</sub>. Ni/Au (20nm/100nm) metal contacts were deposited by e-beam evaporation (TEMESCAL E-beam evaporator EC-200). Lift-off of S1811, LOR above Al<sub>2</sub>O<sub>3</sub> around circular rings was done using PG remover at 80°C for 20 minutes, followed by cleaning of the sample with DI water and N<sub>2</sub>.

Figure 1.12 Basic steps of photolithography

For electrical measurements, the option of a top to the bottom contact was possible for Si based MOS capacitors but for GaN based MOS capacitors, only top to top contact are possible, since the GaN epilayer is on top of sapphire, an electrically insulating material.

## 1.2.7 Challenges with gate oxides and semiconductors

There are several challenges to fabricating MOSFETs as the complementary metal-oxide-semiconductor (CMOS) is scaled downward. A reduction in the dielectric thickness leads to exponential increase in direct tunneling current through the gate oxide <sup>39</sup>. High leakage current leads to increased power consumption and excess heat generation. As a result, electrical breakdown of the gate oxide may occur.

Nitrogen vacancies, native donor defects, creates *n*-type conductivity in undoped GaN <sup>40</sup>. Argon bombardment can remove nitrogen from GaN resulting in excess nitrogen vacancies and Fermi level pinning <sup>41</sup>. Point defects can be created in gate oxides as oxygen vacancies and degrade the electrical properties at the oxide-semiconductor interface (Y<sub>2</sub>O<sub>3</sub>/Si <sup>42</sup>, HfO<sub>2</sub>/Si <sup>43</sup>) of the device. Positive fixed charge is created in oxides due to point defects that cause a shift in the flatband voltage and electron traps are created that causes threshold voltage instability. Surface contamination of the semiconductor prior to deposition of dielectrics can form point defects by reaction among impurities and dielectrics. Degradation of semiconductor surface during plasma resist strip and oxide etch is a challenge as it increases semiconductor surface roughness and leads to defects in gate oxide at oxide/semiconductor interface <sup>44</sup>.

# 1.2.8 Motivation for the selection of materials in MOS capacitor

# **1.2.8.1 Sapphire**

In this research, sapphire was the substrate of choice to grow GaN epilayers due to its low cost <sup>45</sup>, wide availability, hexagonal symmetry, and ease of handling and pregrowth cleaning. GaN epitaxial thin films are usually grown on sapphire by MOCVD, MBE and HVPE. This heteroepitaxy results in a high density of dislocations and cracks due to the mismatch (14% lattice mismatch) in lattice parameters and coefficients of thermal expansion between the GaN thin film and sapphire. Although the lattice mismatch (3.3%) between SiC and GaN is much lower compared to GaN and sapphire (14.8%), still sapphire is the most widely used and cheapest substrate to grow smooth films of [0001] oriented GaN (Table 1.2).

**Table 1-2 GaN substrates** 46

|                    | Lattice constant<br>mismatch (%) | Dislocation<br>density<br>(cm <sup>-2</sup> ) |

|--------------------|----------------------------------|-----------------------------------------------|

| GaN on bulk<br>GaN | 0                                | $10^4$ -5×10 <sup>6</sup>                     |

| GaN on SiC         | 3.5                              | $1 \times 10^{9}$                             |

| GaN on sapphire    | 14                               | 5×10 <sup>9</sup>                             |

| GaN on Silicon     | 17                               | 1×10 <sup>11</sup>                            |

Sapphire is stable at high temperature (~1000°C), which is essential for epitaxy. Threading dislocation densities of epitaxial GaN on sapphire and SiC are typically between 10<sup>8</sup> to 10<sup>10</sup> cm<sup>-2</sup>. Despite the high threading dislocation density, light-emitting diodes based on GaN on sapphire demonstrate good luminescence efficiency <sup>47</sup>. Unlike most semiconductors, the presence of dislocations in GaN does not cause fast degradation of the optical or electric properties and thus sapphire still remains a good substrate for GaN electronics. The threading dislocations defects originate at the substrate/GaN interface and propagate into the epilayer. Sapphire has a higher thermal expansion coefficient than GaN, so GaN films grown on sapphire experience compressive strain. This strain is released by the formation of threading dislocations (Table 1.3). Yam *et al.* <sup>48</sup> studied dislocation density of GaN on sapphire grown by HVPE and found a reduction of the threading dislocation density with increasing GaN films thickness.

Table 1-3 GaN/sapphire defects

| GaN growth method | Substrate | Type of defect         | Source of defect                 | Reference                       |

|-------------------|-----------|------------------------|----------------------------------|---------------------------------|

| MOCVD             | Sapphire  | Threading dislocations | Nucleation layer                 | Kapolnek et al. 49              |

| MOCVD             | Sapphire  | Grain boundaries       | Misorientation of crystal grains | Xu <i>et al</i> . <sup>50</sup> |

Many different materials have been investigated as substrates for the epitaxial growth of GaN since bulk GaN crystals are scarce and expensive. Both a- and c-plane sapphire is being used for GaN growth and fabrication of LEDs. The lattice mismatch between GaN and a-plane sapphire is less than 2% <sup>36</sup>. The orientation of GaN is (0001) on both a- and c- plane sapphire. The crystal quality of GaN film grown on a-plane sapphire was identical compared to c-plane sapphire <sup>51</sup>. The advantage of a-plane sapphire is the presence of the cleavage plane (r-plane, (1012)) normal to the sapphire surface <sup>36</sup>. GaN epilayer grown on a-plane sapphire can be cleaved towards r-plane to obtain edge-emitting lasers.

High-quality nitride films can be grown on c-plane sapphire by the formation of a thin AlN buffer layer at low temperature <sup>52</sup>. Keller *et al.* <sup>53</sup> reported that nitrodizing sapphire by exposure to ammonia reduced the dislocation density in the GaN layer from  $2 \times 10^{10}$  to  $4 \times 10^{8}$  cm<sup>2</sup>. The AlN thin film is crystallographically rotated 30° in-plane with respect to the sapphire lattice; and, as a result, it decreases the lattice mismatch and strain between sapphire and GaN epilayer.

## 1.2.8.2 GaN

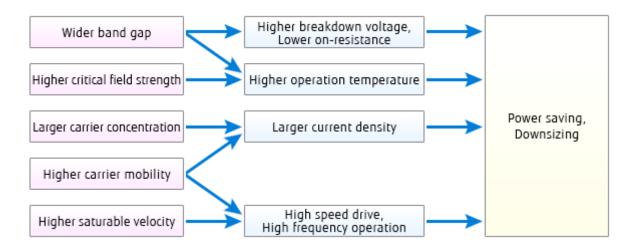

The market for GaN power semiconductors is expected to grow from nearly zero in 2011 to over \$1 billion in 2021. Power supplies, solar inverters, and industrial motor drives are some of the markets for GaN electronics <sup>54</sup>. The cost of a GaN fabrication process is going down by growing GaN on top of silicon substrates with an aluminum nitride buffer layer. GaN high power HEMTs and MMICs are designed for high power, high efficiency amplifiers. GaN HEMT power devices can significantly reduce conduction and switching loss and help to solve environmental

issues with smaller power units <sup>55</sup>. GaN based devices are power saving and attractive for microwave power amplifiers, RADAR and satellite communication, hybrid electric vehicles, and the multi-billion dollar commercial lighting market (Figure 1.13).

Figure 1.13 Advantage of GaN devices 55

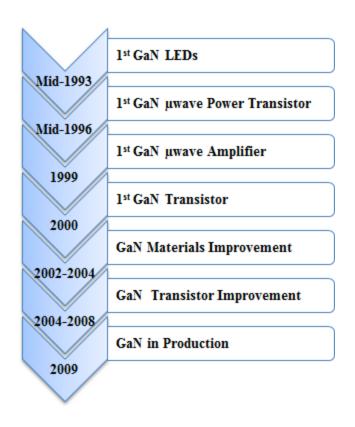

Due to the small bandgap of Si (1.12eV), Si-based power transistors shows inferior performance at high temperature (200°C), which has motivated researchers to investigate the performance of GaN based power devices. The first breakthrough with GaN semiconductor occurred in early 1990s with the invention of GaN based light-emitting diodes, other rapid developments in various applications have occurred since (Figure 1.14) <sup>56</sup>. GaN can be used to manufacture power electronics to create faster, heat-resistant and energy efficient transistors. For transistor applications, GaN is excellent for high frequency combined with high power, which is used for broadcast and cell phones.

To achieve *n*-type conductivity (carrier concentration  $10^{17}$ - $10^{19}$  cm<sup>-3</sup> <sup>57</sup>) in GaN, Si doping (Si activation energy ~ 27meV <sup>58</sup>) is effective. In contrast, *p*-type conductivity in GaN (~ $10^{16}$  cm<sup>-3</sup> <sup>59</sup>) is difficult to achieve due to hydrogen passivation and nitrogen vacancies. GaN can be made *p*-type by Mg doping and it is difficult to achieve high hole concentrations, due to the high activation energy of Mg acceptors<sup>60</sup> (Mg activation energy ~ 182 meV <sup>61</sup>).

Figure 1.14 GaN technology timeline

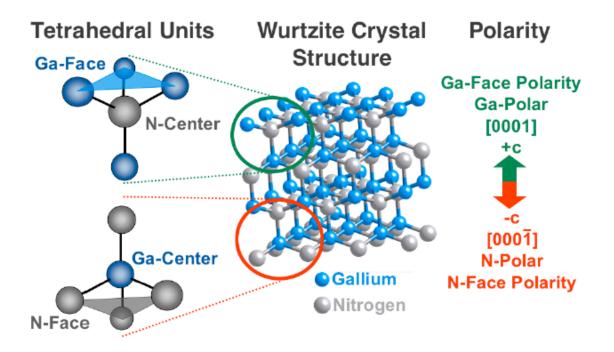

### 1.2.8.2.1 Polarization in GaN

Spontaneous and piezoelectric (induced) polarizations are present in GaN (0001) planes. Wurtzite GaN has spontaneous charge along the [0001] direction, where negative charges form on the Ga face and positive charges on the N face (Figure 1.15). The piezoelectric field is not observed in orientations perpendicular to [0001] direction (the *a*- or *m*-planes) or other nonpolar planes <sup>62</sup>. The spontaneous polarization within the crystal is due to combination of ionization and irregular arrangement of gallium and nitrogen atoms<sup>45</sup>. The piezoelectric polarization is caused by crystal strain (mechanical perturbation) in the material, which changes the c/a ratio in wurtzite nitrides. For example, spontaneous polarization is significant in AlGaN/GaN due to a large spontaneous polarization of AlN, and piezoelectric polarization is significant in InGaN/GaN due differences in the lattice constant of InN and GaN <sup>63</sup>.

Figure 1.15 GaN wurtzite structure showing Ga-face and N-face polarity <sup>64</sup>

Figure 1.16 GaN planes: (a) polar c-plane and (b) nonpolar m-plane  $^{38}$

Nonpolar planes do not form polarization discontinuities in heterostructures; this has motivated great interest in *m*-plane GaN for devices with normally-off operation (Figure 1.16). For power and consumer applications, a normally off operation is preferred for the safety of the switching systems. GaN based MOSFETs on *c*-plane substrates show poor threshold voltage stability with temperature due to the strong pyroelectric polarization (polarization change due to temperature) present in polar GaN. Non-polar GaN leads to better temperature stability and normally-off transistor operation; polar GaN based devices do not. High quality and large sizes of *m*-plane GaN substrates are also useful for green lasers and miscut *m*-planes showed improvement in laser performance <sup>65</sup>.

# 1.2.8.2.2 Properties of GaN

Si, GaAs, SiC and GaN are the main semiconductors used commercially for high-power/high-temperature switching applications. GaN transistors promise to deliver better linear power and efficiency than is possible with silicon.