# DESIGN OF AN EASY-TO-USE, HOST-INDEPENDENT DATA ACQUISITION SYSTEM

by

## DURWIN DUANE NIGUS

B.S., Kansas State University, 1987

#### A THESIS

submitted in partial fulfillment of the requirements for the degree

MASTER OF SCIENCE

ELECTRICAL AND COMPUTER ENGINEERING

KANSAS STATE UNIVERSITY Manhattan, Kansas

1989

Approved by:

Major Professor

LD 2668 .74 EECE 1989 N54 c.2

# TABLE OF CONTENTS

| CHAPTER | PAGE                                                                  |

|---------|-----------------------------------------------------------------------|

| ONE     | INTRODUCTION 1-1                                                      |

| TWO     | THE DEVELOPMENT OF THE DAS                                            |

| 2.1     | Introduction 2-1                                                      |

| 2.2     | Host-to-DAS Interface Development 2-1                                 |

| 2.3     | Development of the DAS's Internal Structure 2-3                       |

| 2.4     | Communication with the System 2-10                                    |

| 2.5     | Conclusion                                                            |

| THREE   | THE SYSTEM FRONT-END AND SYSTEM BUS                                   |

| 3.1     | Introduction                                                          |

| 3.2     | The System Front-end: A User's Perspective                            |

| 3.3     | The System Bus and Bus Drivers 3-7                                    |

| 3.4     | Algorithms for System Bus Control 3-13                                |

| 3.5     | The Circuits of the System Front-end: A Technician's Perspective 3-19 |

| FOUR    | THE ANALOG-TO-DIGITAL BOARD                                           |

| 4.1     | Introduction 4-1                                                      |

| 4.2     | The User's Perspective of the A/D Board                               |

| 4.3     | The A/D from a Programmer's Perspective                               |

# TABLE OF CONTENTS (cont.)

| CHAPTER |                        |                                                                           | PAGI |

|---------|------------------------|---------------------------------------------------------------------------|------|

|         | 4.3.1                  | The A/D Board<br>Register Set                                             | 4-9  |

|         | 4.3.2                  | Algorithmic Control of the A/D Board                                      | 4-25 |

| 4.4     | The Circu              | itry for the A/D Board                                                    | 4-34 |

|         | 4.4.1                  | The Analog Signal Circuits                                                | 4-36 |

|         | 4.4.2                  | Timing Considerations and the Controlling Sequence for the Analog Circuit | 4-52 |

|         | 4.4.3                  | The Digital Controller Section                                            | 4-58 |

|         | 4.4.4                  | A/D Board Circuit Schematics and Parts List                               | 4-82 |

| FIVE    | SUGGESTED              | SYSTEM CONTROLLER ALGORITHMS                                              |      |

| 5.1     | Introduct              | ion                                                                       | 5-1  |

| 5.2     | Algorithm<br>Controlle | Format for the System                                                     | 5-3  |

| 5.3     | I/O-Board              | Command Implementation                                                    | 5-16 |

| SIX     | SUMMARY .              |                                                                           | 6-1  |

# TABLE OF CONTENTS (cont.)

| APPE | NDIX                                                                   | PAGE |

|------|------------------------------------------------------------------------|------|

| A    | USING THE DAS WITH SYSTEM CONTROLLER SIMULATOR                         |      |

|      | A.1 Introduction                                                       | A-1  |

|      | A.2 Simulating the System Controller                                   | A-2  |

|      | A.3 Using the System with the PC Controller                            | A-5  |

|      | A.4 Calibrating the A/D board                                          | A-15 |

| В    | THE PROPOSED COMMAND SET FOR THE DAS                                   | B-1  |

| С    | DESIGN OF ADDITIONAL BOARDS                                            |      |

|      | C.1 Introduction                                                       | C-1  |

|      | C.2 The Board Design Procedures                                        | C-1  |

| D    | CIRCUIT CONSTRUCTION CONSIDERATIONS AND COMPONENT LAYOUT               |      |

|      | D.1 Construction of the system front-end                               | D-1  |

|      | D.2 Construction of the A/D board                                      | D-3  |

| E    | HARDWARE MODIFICATIONS FOR THE 68HC11EVB                               | E-1  |

| F    | ALGORITHMS FOR SYSTEM TESTING AND MAINTAINENCE<br>OF PC-BASED SOFTWARE | F-1  |

# LIST OF FIGURES

| FIGURE  |                                                                                                     | PAGE |

|---------|-----------------------------------------------------------------------------------------------------|------|

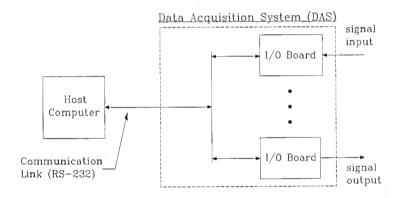

| 2.3.1   | The block diagram of a DAS consisting of removable I/O boards                                       | 2-4  |

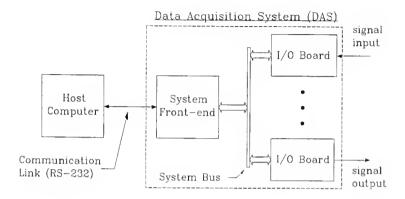

| 2.3.2   | The DAS including the system front-end and system bus                                               | 2-6  |

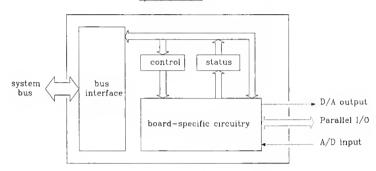

| 2.3.3   | Block representation of the I/O board $$                                                            | 2-7  |

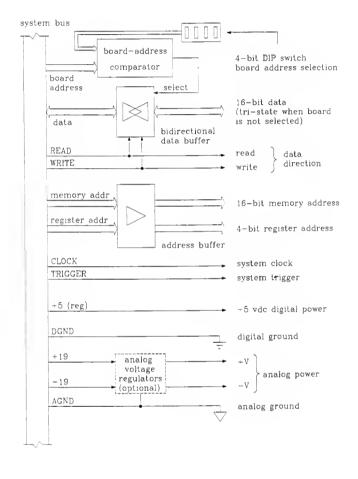

| 2.3.4   | A block representation of the I/O-board bus interface                                               | 2-9  |

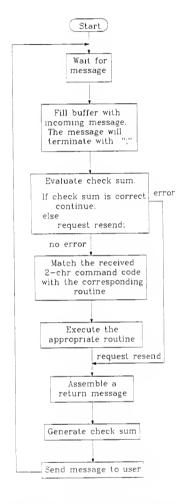

| 2.4.1   | Operations performed by system controller software                                                  | 2-12 |

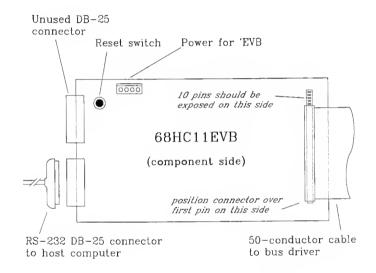

| 3.2.1   | The connections to the system controller board: the 68HC11EVB                                       | 3-3  |

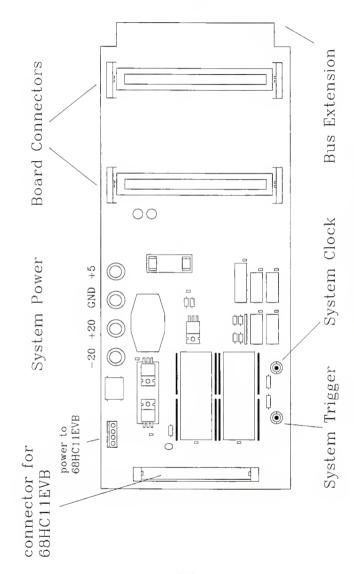

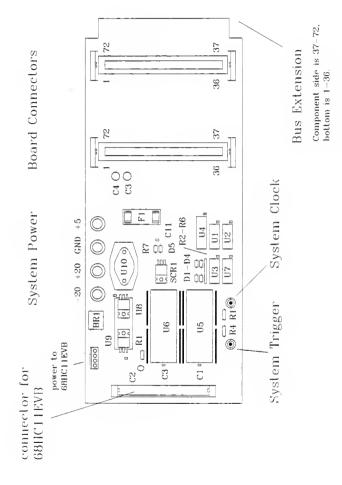

| 3.2.2   | Top-view of the bus-driver board                                                                    | 3-5  |

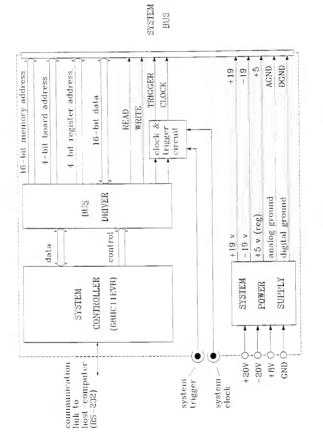

| 3.5.1   | The components of the DAS front-end                                                                 | 3-20 |

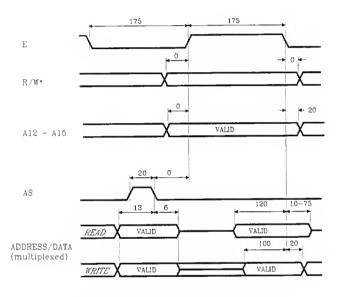

| 3.5.2   | Timing associated with the bus driver circuit when used with the 68HCllEVB as the system controller | 3-22 |

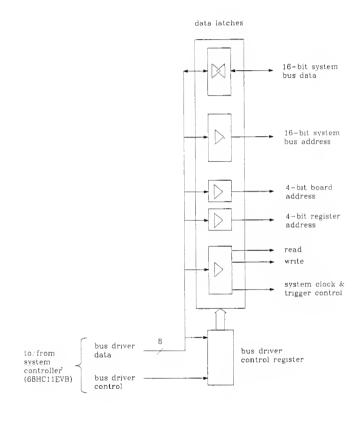

| 3.5.3   | A block representation of the bus driver                                                            | 3-24 |

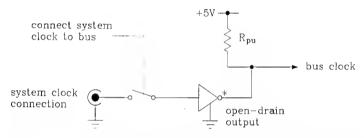

| 3.5.4   | A block representation of the system clock controller                                               | 3-25 |

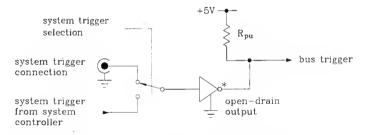

| 3.5.5   | A block representation of the system bus trigger control and interface                              | 3-26 |

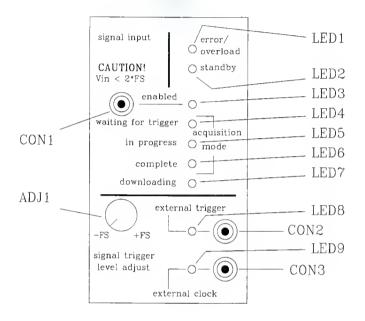

| 4.2.1   | The front panel of the A/D board                                                                    | 4-5  |

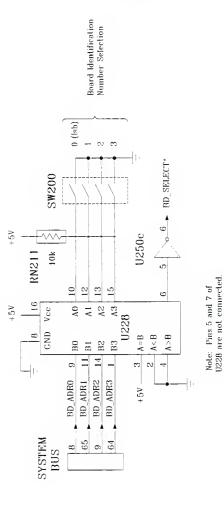

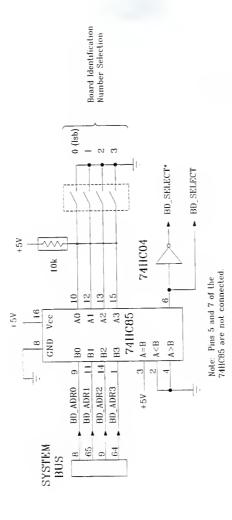

| 4.2.2   | The A/D board address selection switch                                                              | 4-8  |

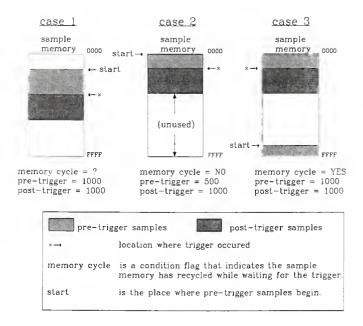

| 4.3.2.1 |                                                                                                     | 4-30 |

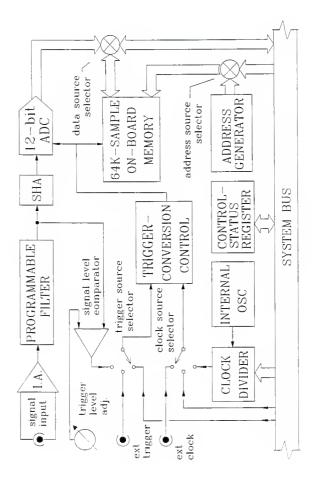

| 4.4.1   | Block diagram of the A/D board                                                                      | 4-35 |

# LIST OF FIGURES (cont)

| FIGURE  |                                                                                              | PAGI |

|---------|----------------------------------------------------------------------------------------------|------|

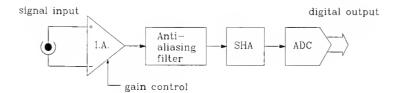

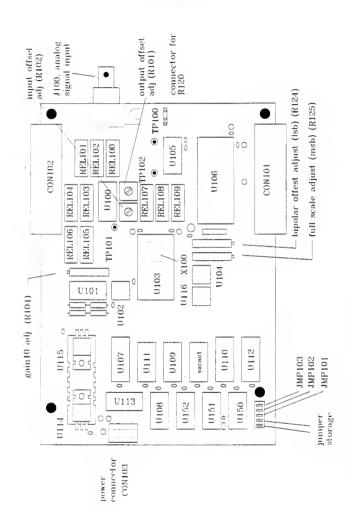

| 4.4.1.1 | The arrangement of the analog signal components                                              | 4-37 |

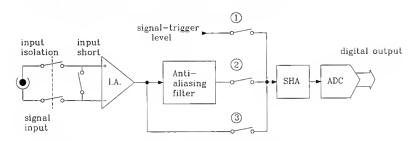

| 4.4.1.2 | The arrangement of signal routing relays between the analog signal components                | 4-39 |

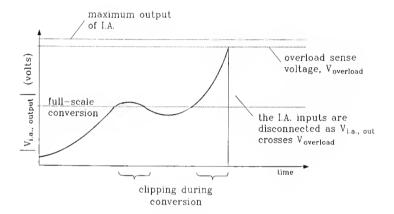

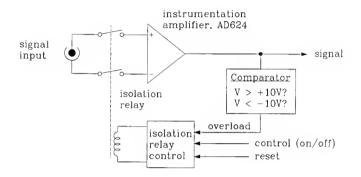

| 4.4.1.3 | The operation of the protection circuit with an overloading signal                           | 4-42 |

| 4.4.1.4 | A block representation of the non-intrusive protection system used on the A/D board          | 4-43 |

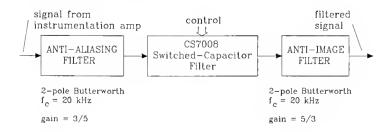

| 4.4.1.5 | A block representation of the on-board anti-aliasing filter and its associated circuitry     | 4-48 |

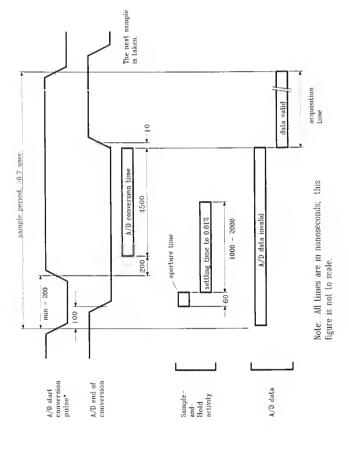

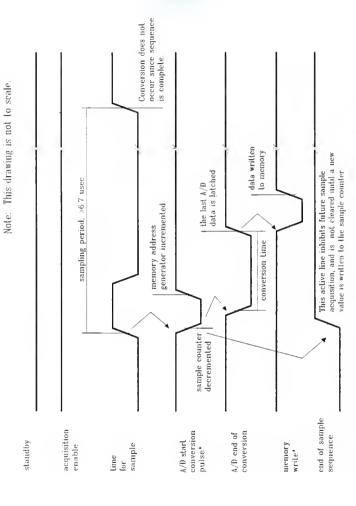

| 4.4.2.1 | Timing diagram for single sample conversion                                                  | 4-53 |

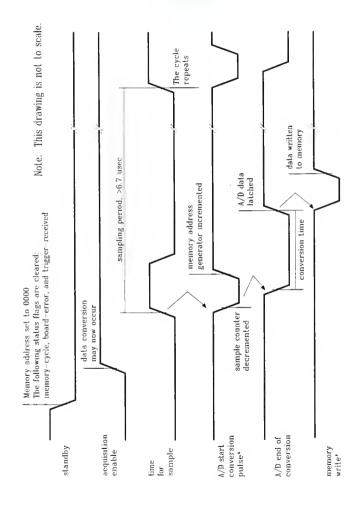

| 4.4.2.2 | Timing diagram for beginning of acquisition sequence                                         | 4-55 |

| 4.4.2.3 | Timing diagram for the end of an acquisition sequence                                        | 4-57 |

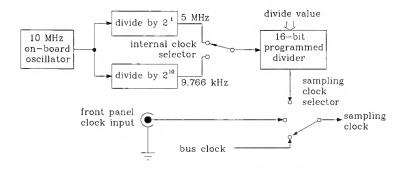

| 4.4.3.1 | A block representation of the on-board sample period generator and the sample clock selector | 4-59 |

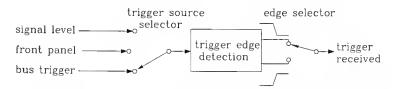

| 4.4.3.2 | Block representation of the A/D board's trigger circuit                                      | 4-62 |

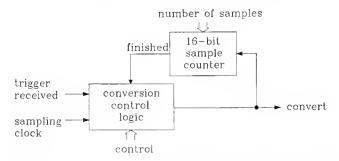

| 4.4.3.3 | A block representation of the conversion control logic circuit                               | 4-65 |

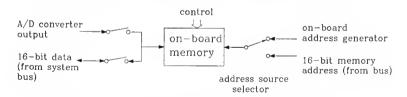

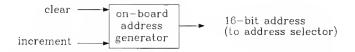

| 4.4.3.4 | A block representation of the A/D board's on-board memory                                    | 4-66 |

| 4.4.3.5 | A block representation of the on-board address generator                                     | 4-67 |

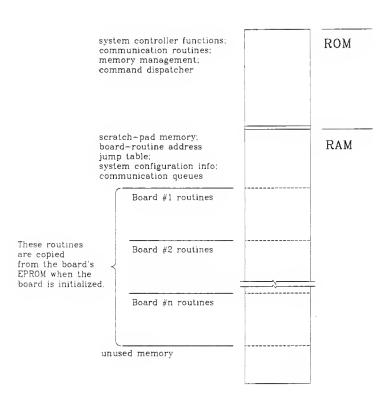

| 5.2.1   | The allocation of system controller ROM and RAM                                              | 5-7  |

# LIST OF FIGURES (cont)

| FIGURE |                                                                                                                                                                                  | PAGE |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.2.2  | The software modules which comprise the system controller                                                                                                                        | 5-9  |

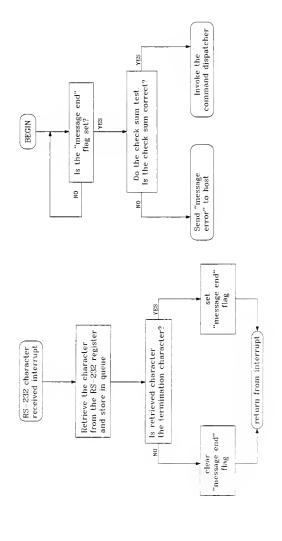

| 5.2.3  | Operations performed by the system controller: (a) the interrupt routine which handles a character when it is received, and (b) waiting for a character to be sent from the host | 5-11 |

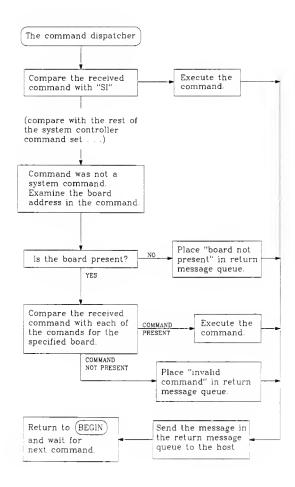

| 5.2.4  | The sequence of operations performed by the command dispatcher                                                                                                                   | 5-13 |

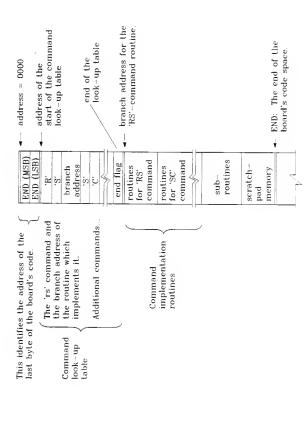

| 5.3.1  | The code space for an I/O-board, as it is arranged on the board's EPROM                                                                                                          | 5-19 |

| A.2.1  | The necessary timing when the bus driver circuit is used with the PCPI and the interface circuit shown in Fig. A.1                                                               | A-4  |

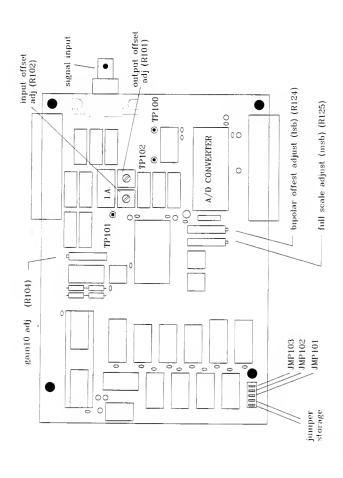

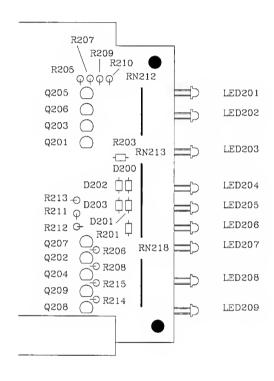

| A.4.1  | View of the A/D board for location of calibration components                                                                                                                     | A-19 |

| D.1.1  | Top view of the system front-end                                                                                                                                                 | D-2  |

| D.2.1  | Top view of the analog circuit board of the A/D board                                                                                                                            | D-5  |

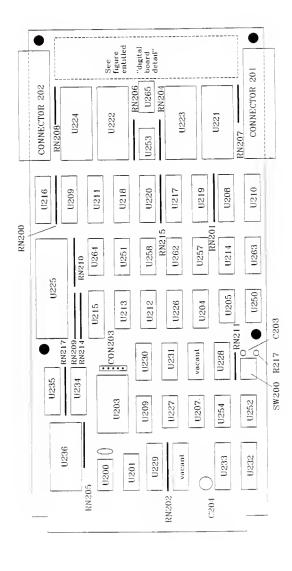

| D.2.2  | Top view of the digital control board of the A/D board                                                                                                                           | D-8  |

| D.2.3  | Component placement details for the A/D digital board                                                                                                                            | D-10 |

| E.1    | The wiring modification necessary at the 68HC24 PRU socket aboard the 68HC11EVB (the 68HC24 is removed)                                                                          | E-2  |

# LIST OF TABLES

| TABLE   |                                                                                   | PAGE |

|---------|-----------------------------------------------------------------------------------|------|

| 3.1.1   | Specifications for the DAS system frontend                                        | 3-2  |

| 3.3.1   | The lines available on the system bus $\ \ .$                                     | 3-7  |

| 3.3.2   | A summary of the bus driver ports and their address with respect to the 68HC11EVB | 3-9  |

| 3.3.3   | The assignments for the address and data bus driver ports                         | 3-10 |

| 3.3.4   | The bit-wise assignment of bus driver port A002                                   | 3-11 |

| 3.3.5   | The bit-wise assignment of bus driver port A004                                   | 3-11 |

| 3.3.6   | Configuration values for bus ports A003 and A007                                  | 3-12 |

| 3.5.1   | The pin out of the system bus, as viewed from the connecter edge                  | 3-34 |

| 4.1.1   | Specifications for the A/D board                                                  | 4-2  |

| 4.3.1.1 | Register assignments for the A/D board                                            | 4-10 |

| 4.3.1.2 | Bit-wise assignment of register 0 $\dots$                                         | 4-11 |

| 4.3.1.3 | Bit-wise assignment of register 1 $\dots$                                         | 4-12 |

| 4.3.1.4 | Bit-wise assignment of register 2                                                 | 4-13 |

| 4.3.1.5 | Assignments for the A/D board status register                                     | 4-16 |

| 4.3.1.6 | Bit-wise assignment of register 4                                                 | 4-18 |

| 4.3.1.7 | Bit-wise assignment of register 6                                                 | 4-21 |

| 4.3.1.8 | Bit-wise assignment for register 11                                               | 4-23 |

# LIST OF TABLES (cont.)

| TABLE   |                                                                                                               | PAGI |

|---------|---------------------------------------------------------------------------------------------------------------|------|

| 4.3.1.9 | Bit-wise assignment for register 12                                                                           | 4-23 |

| 4.3.2.1 | A summary of pre-acquisition controls $$ . $$                                                                 | 4-27 |

| 4.3.2.2 | The data acquisition modes for the A/D board                                                                  | 4-27 |

| 4.3.2.3 | Signal sources appropriate for single conversions                                                             | 4-33 |

| 4.4.1.1 | Signal routing logic for the analog signal                                                                    | 4-40 |

| 4.4.1.2 | Procedure for nulling I.A. (AD624) offset errors                                                              | 4-47 |

| 4.4.3.1 | The two on-board oscillators and their respective range of sampling frequencies                               | 4-61 |

| 4.4.3.2 | Truth table for sample counter controller                                                                     | 4-64 |

| 4.4.3.3 | The conversion control logic truth table                                                                      | 4-66 |

| 4.4.3.4 | A/D board register mapping of the control/status port                                                         | 4-71 |

| 4.4.3.5 | The 82C54-2 internal register summary                                                                         | 4-75 |

| 4.4.3.6 | Comparison of sampling frequency, $f_{\S}$ , with respect to various crystal frequencies                      | 4-77 |

| 4.4.3.7 | Available sampling frequencies, $f_s$ , for the CS7008 with the 2.4576 MHz crystal installed on the prototype | 4-77 |

| 5.2.1   | Memory allocation for the 68HC11EVB (following modifications listed in Appendix E)                            | 5-5  |

| A.1     | PCPI/DAS: Routines exclusive to the DAS/PCPI test routine                                                     | A-7  |

# LIST OF TABLES (cont.)

| TABLE |                                                                            | PAGE |

|-------|----------------------------------------------------------------------------|------|

| A.2   | PCPI/DAS commands: System controller                                       | A-8  |

| A.3   | PCPI/DAS commands: A/D Board commands for conversion control configuration | A-8  |

| A.4   | PCPI/DAS commands: A/D Board commands for conversion control               | A-9  |

| A.5   | PCPI/DAS commands: A/D board status query and data retrieval               | A-9  |

| A.6   | PCPI/DAS commands: auxiliary commands for test program                     | A-10 |

| B.1   | Data acquisition system command summary .                                  | B-2  |

| C.1   | The pin out of the system bus, as viewed from the connecter edge           | C-5  |

| D.2.1 | Digital board to analog board connector pin assignments                    | D-11 |

# LIST OF SCHEMATICS

| SCHEMA | ATIC                                                                                         | PAGE |

|--------|----------------------------------------------------------------------------------------------|------|

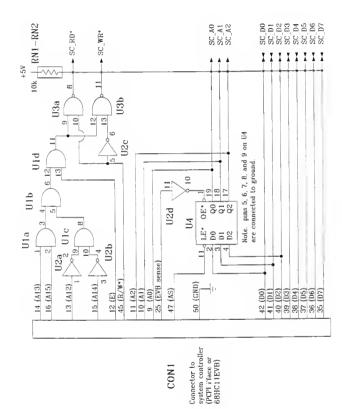

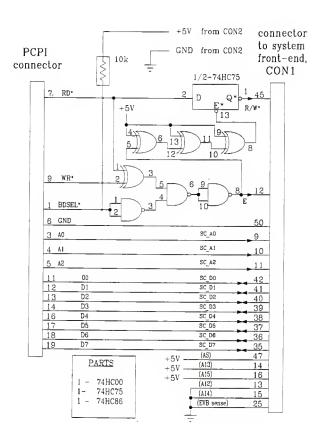

| 3.1    | The system controller interface circuit                                                      | 3-29 |

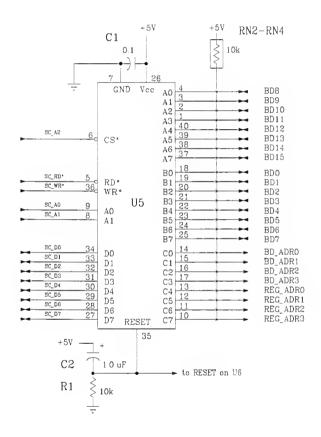

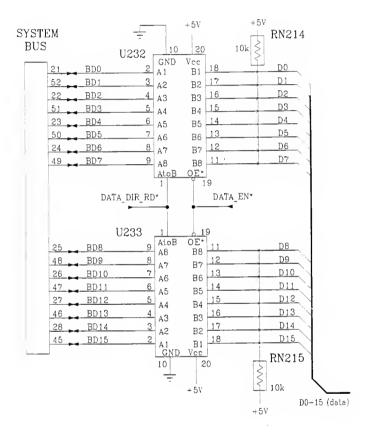

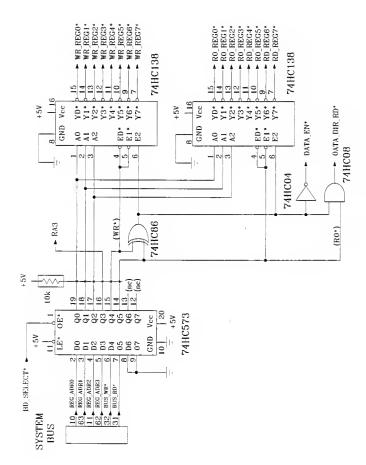

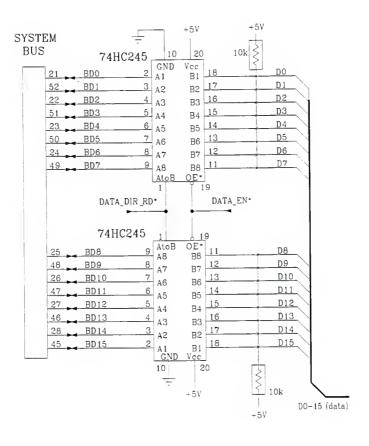

| 3.2    | The bus driver for data and register/board addresses                                         | 3-30 |

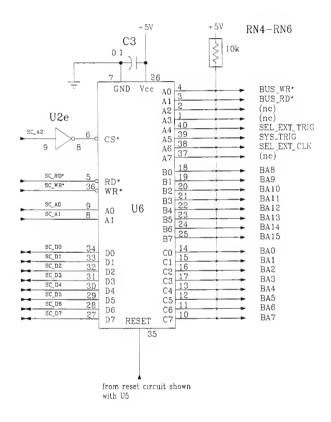

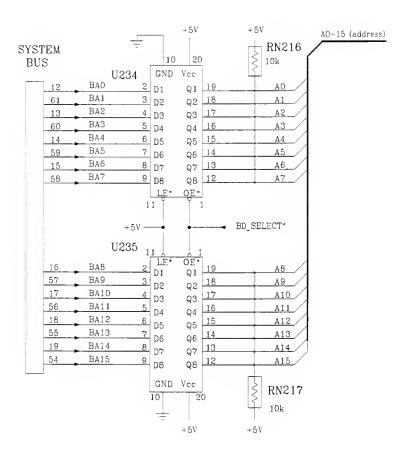

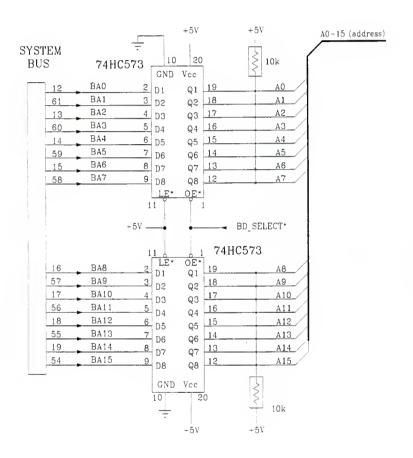

| 3.3    | The bus driver for 16-bit memory addresses and bus control                                   | 3-31 |

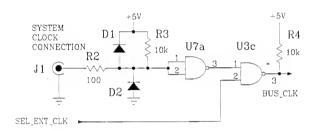

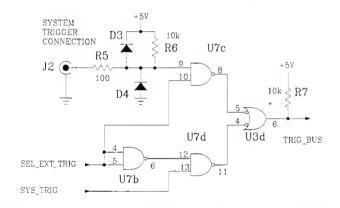

| 3.4    | Interface and control for (a) the system bus clock, and (b) the system bus trigger $\dots$   | 3-32 |

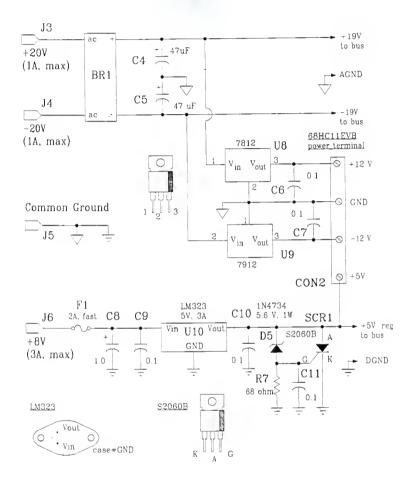

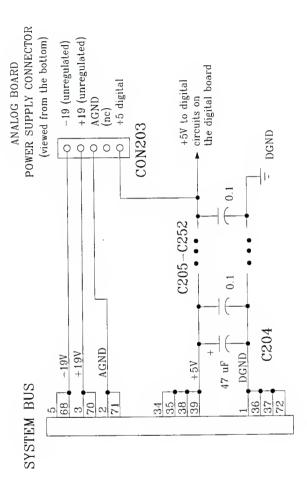

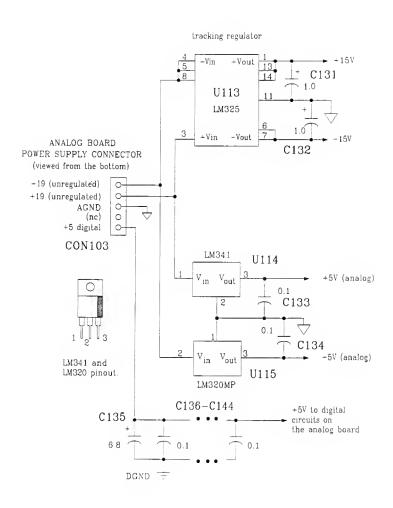

| 3.5    | System power supply conditioning and regulation                                              | 3-33 |

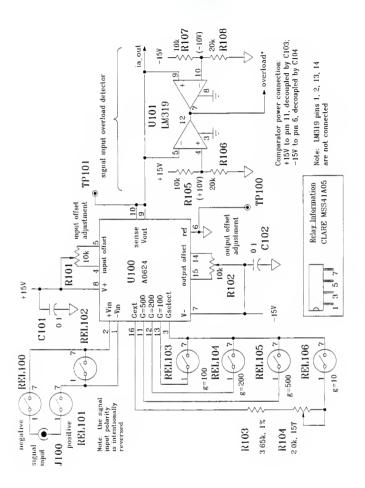

| 4.1    | The instrumentation amplifier and the overload detector                                      | 4-84 |

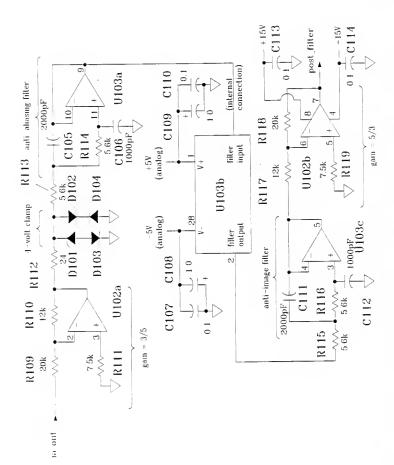

| 4.2    | The on-board anti-aliasing filter and its associated circuitry                               | 4-85 |

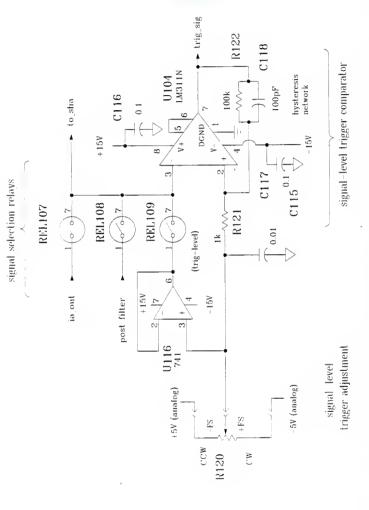

| 4.3    | The signal selection relays and the signal level trigger detector                            | 4-86 |

| 4.4    | The sample-and-hold amplifier and the analog-to-digital converter                            | 4-87 |

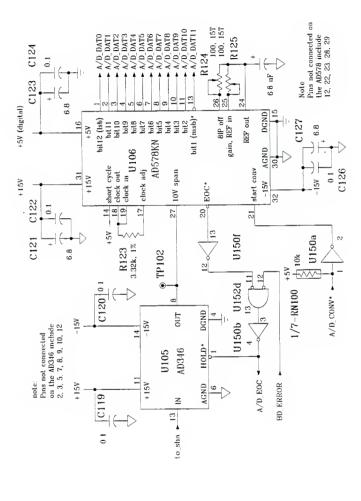

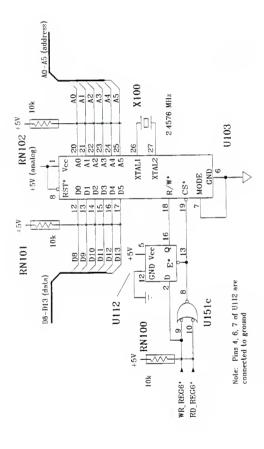

| 4.5    | The on-board sampling period generator, and the sampling clock selector                      | 4-88 |

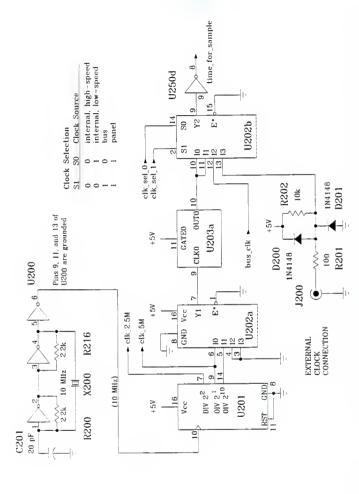

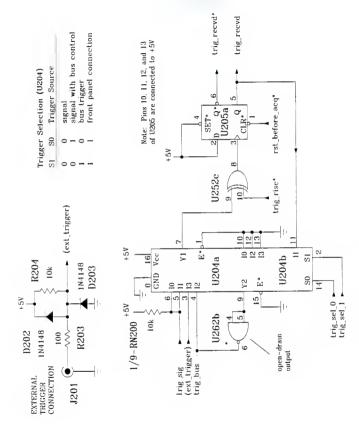

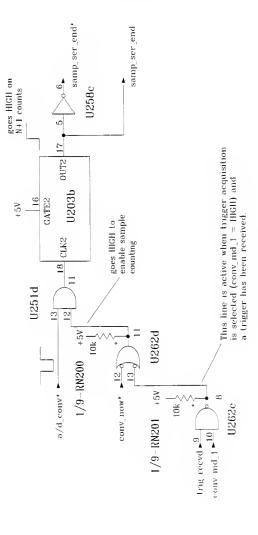

| 4.6    | The trigger source selector and trigger detection circuit                                    | 4-89 |

| 4.7    | The sample counter for the conversion controller                                             | 4-90 |

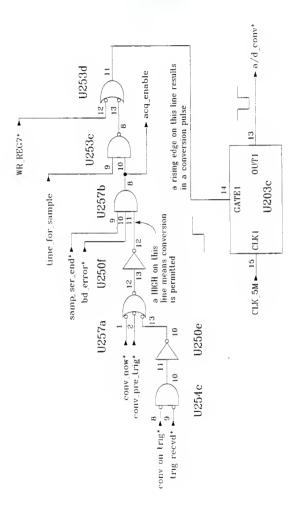

| 4.8    | The convert-enable circuit and the conversion pulse generator                                | 4-91 |

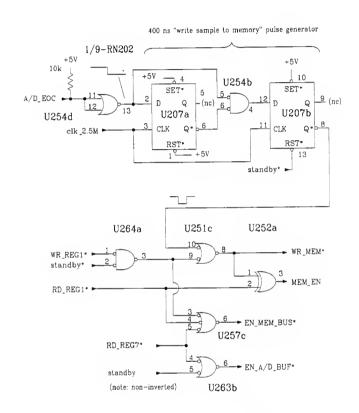

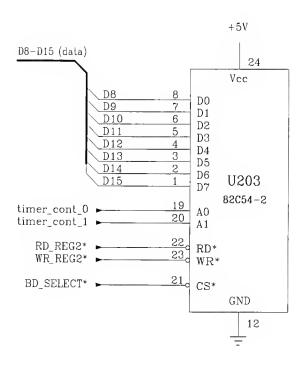

| 4.9    | The on-board memory control, including the data buffer controllers and write-pulse generator | 4-92 |

# LIST OF SCHEMATICS (cont.)

| SCHEMA | ATIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PAGE  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

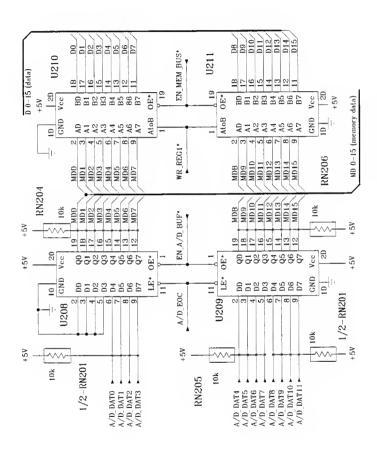

| 4.10   | The on-board memory data source selection circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-93  |

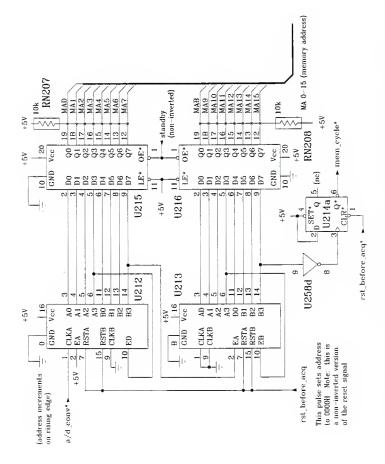

| 4.11   | The on-board memory address generator circut                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-94  |

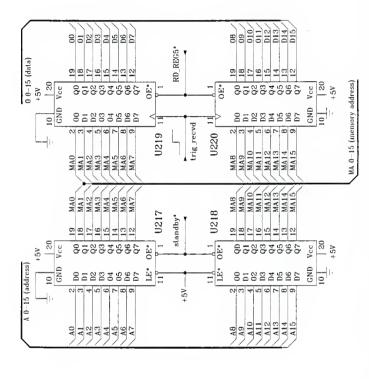

| 4.12   | The on-board memory address source selector and trigger-address capture latches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-95  |

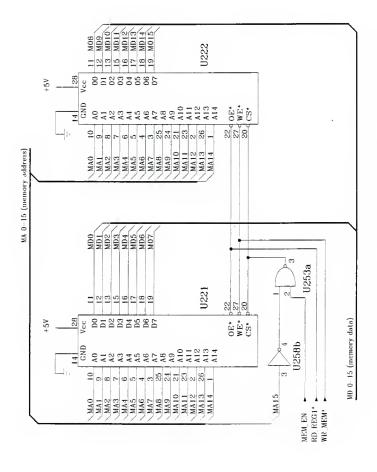

| 4.13   | The on-board memory devices: addresses \$0000 -\$7FFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-96  |

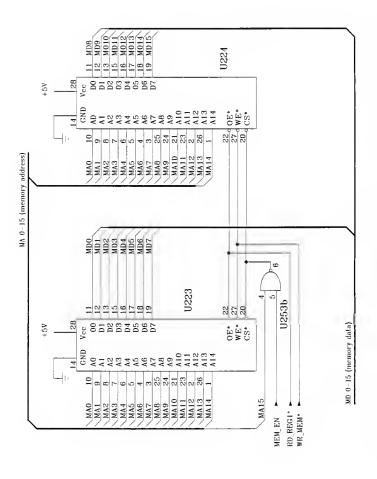

| 4.14   | The on-board memory devices: addresses \$8000 -\$FFFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-97  |

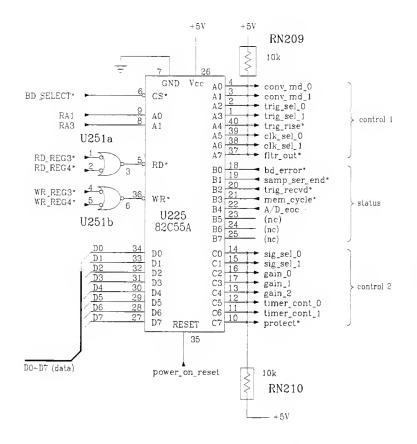

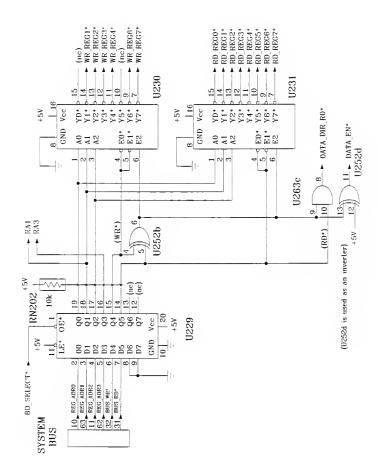

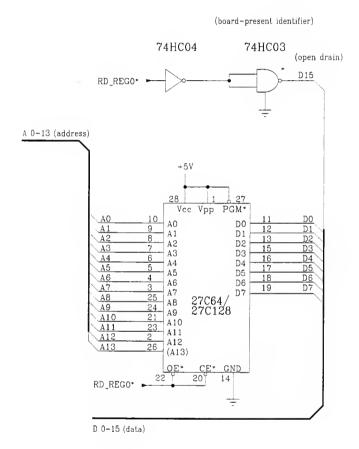

| 4.15   | The A/D board status and control registers $% \left( 1\right) =\left( 1\right) \left( $ | 4-98  |

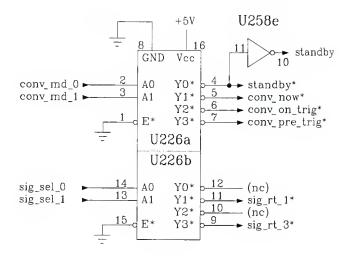

| 4.16   | The conversion mode decoder and the signal route decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-99  |

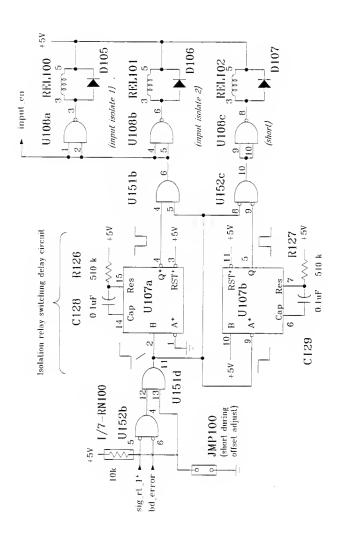

| 4.17   | The input signal isolation relay control circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-100 |

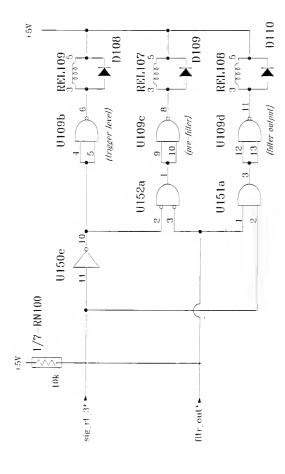

| 4.18   | The logic circuitry and drivers associated with the signal routing relays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-101 |

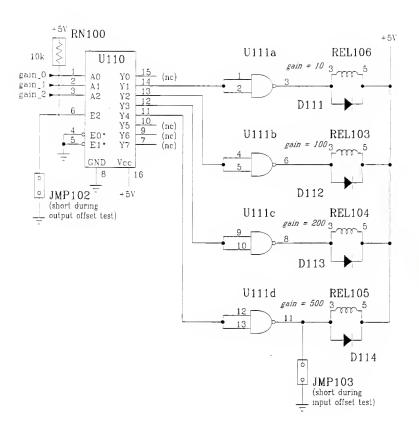

| 4.19   | The gain decoder and drivers associated the gain control relays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-102 |

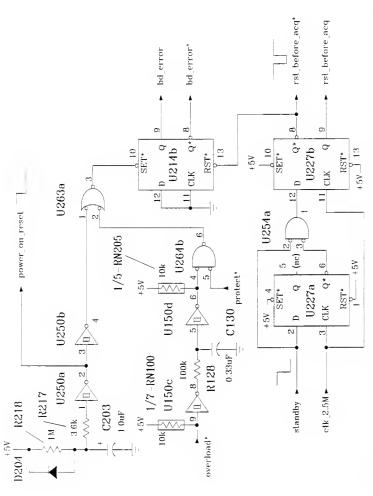

| 4.20   | The board-error status register and the reset-<br>pulse generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-103 |