# VHF & UHF ENERGY HARVESTING RADIO SYSTEM PHYSICAL AND MAC LAYER CONSIDERATIONS

by

### XIAOHU ZHANG

B.S., Xi'an Jiaotong University, 2001

### A THESIS

submitted in partial fulfillment of the requirements for the degree

### MASTER OF SCIENCE

Department of Electrical and Computer Engineering College of Engineering

> KANSAS STATE UNIVERSITY Manhattan, Kansas

> > 2009

Approved by:

Major Professor William B. Kuhn

# **Abstract**

Wireless Sensor Network industrial and civilian applications have been moved closer to us since they were originally developed for defense applications. They have been or will be widely used in industrial process monitoring and control, earth quake monitoring, healthcare applications, construction health monitoring, home automation, traffic control, and space exploration. The IEEE802.15.4 standard defines the PHY and MAC layers for low power wireless sensor networks. However, applications and research of wireless sensor networking are centered on battery powered devices. To remove the battery from the system is the ultimate goal of this research by using Energy Harvesting technology, which will largely reduce the wireless sensor network maintenance cost, increase the option open to application environments and push the speed of wireless sensor network industrialization.

This thesis tackles the problem of RF link budget and PHY layer design for Energy Harvesting Wireless Sensor Network Nodes, through a *modification to PHY/MAC layers*. To this end, a prototype of energy harvesting radio is developed that hinges on burst-communication and solar cell energy harvesting techniques. The choice of operating frequency is considered relative to transmission range, antenna technology and RF link budget, and quantified by propagation measurements at four unlicensed frequencies in the VHF through UHF spectrums. A short preamble, PHY payload protocol frame structure and synchronization method are also proposed in order to support long sleep period duty cycle necessary in Energy Harvesting Radio systems. Some related work has recently begun under a standardization effort known as 802.15.4f. It is hoped that this thesis will contribute to this effort.

# **Table of Contents**

| List of Figures                                             | vii         |

|-------------------------------------------------------------|-------------|

| List of Tables                                              | X           |

| Acknowledgements                                            | xi          |

| CHAPTER 1 Introduction                                      | 1           |

| 1.1 The Future of Wireless Sensor Networks                  | 1           |

| 1.2 Current Research on Wireless Sensor Nodes               | 1           |

| 1.3 Challenges for Energy Harvesting Wireless Sensor Nodes  | 2           |

| 1.4 Thesis Organization                                     | 2           |

| CHAPTER 2 K-State Energy Harvesting Radio (EHR) Prototype I | Demo Board4 |

| 2.1 RF transmission mode Versus Power Consumption           | 5           |

| 2.2 Design Principle                                        | 6           |

| 2.3 Hardware Design                                         | 7           |

| 2.4 Software Design                                         | 11          |

| 2.4.1 RFIC Programming                                      | 11          |

| 2.4.2 Duty Cycle Design                                     | 13          |

| 2.4.2.1 High CPU Clock, Software Control TX                 | 14          |

| 2.4.2.2 Low CPU Clock, Hardware Control TX                  | 15          |

| 2.4.2.3 Computing Active and Sleep Time                     | 16          |

| 2.5 Test Results                                            | 17          |

| 2.5.1 Lab Test                                              | 17          |

| 2.5.1.1 Current Consumption Test                            | 17          |

| 2.5.1.2 The Burst Communication Test                        | 18          |

| 2.5.1.3 The System Reliability Test                         | 21          |

| 2.5.2 Outdoor Test                                          | 21          |

| 2.6 Conclusions                                             | 22          |

| CHAPTER 3 RF Link Budgets of EHR Systems                    | 23          |

| 3.1 RF Link Budget Factors                                  | 23          |

| 3.1.1 Propagation                                           | 24          |

| 3.1.2 Ante | ennas                                                       | 25 |

|------------|-------------------------------------------------------------|----|

| 3.1.2.1    | Reciprocity                                                 | 25 |

| 3.1.2.2    | Antenna Directivity                                         | 25 |

| 3.1.2.3    | Gain                                                        | 26 |

| 3.1.2.4    | Effective Area                                              | 26 |

| 3.1.2.5    | Antenna Size                                                | 26 |

| 3.1.3 Link | Budget                                                      | 27 |

| 3.1.3.1    | Antenna Gain Effects on Link Budget                         | 27 |

| 3.1.3.2    | Link Budget Examples                                        | 28 |

| 3.1.4 RF I | Link Budget and The System Design of EHR                    | 30 |

| 3.2 UHF/\  | /HF Propagation Comparisons                                 | 30 |

| 3.2.1 Exp  | erimental Setup                                             | 31 |

| 3.2.1.1    | Propagation Links                                           | 31 |

| 3.2.1.2    | Experiment Environment                                      | 31 |

| 3.2.1.3    | Antennas                                                    | 34 |

| 3.2.1.4    | Transmitter and Receiver                                    | 37 |

| 3.2.2 Exp  | eriment Results                                             | 39 |

| 3.2.2.1    | Received Signal Strength Measurements at Each Frequency     | 39 |

| 3.2.2.2    | Directional Antennas versus Monopole Antenna Results        | 42 |

| 3.2.2.3    | Path Loss Exponent Comparison                               | 46 |

| 3.2.2.4    | Comparison of Four Frequency's Propagation                  | 47 |

| CHAPTER 4  | Energy Harvesting Radio System PHY/MAC layer Considerations | 49 |

| 4.1 IEEE8  | 02.15.4 & ZigBee Overview                                   | 50 |

| 4.1.1 PHY  | General Definition                                          | 50 |

| 4.1.2 MA   | C Layer Synchronization                                     | 51 |

| 4.2 Propos | ed EHR System PHY Layer                                     | 54 |

| 4.2.1 PHY  | General Definition                                          | 55 |

| 4.2.2 PHY  | Frame Structure                                             | 56 |

| 4.2.3 Prea | mble Design                                                 | 57 |

| 4.2.3.1    | Preamble Length versus Start of Frame Detecting Error       | 57 |

| 4.2.3.2    | Method for Improving Short Preamble Frame Performance       | 60 |

| 4.2.3.3 Preamble Length versus Energy Comsumption                                 | 61 |

|-----------------------------------------------------------------------------------|----|

| 4.3 Proposed EHR MAC Layer Synchronization                                        | 62 |

| 4.3.1 Pure-EHR Network Obtaining Synchronization                                  | 63 |

| 4.3.2 Hybrid-EHR Networks for Obtaining Synchronization                           | 66 |

| 4.3.3 Keeping Synchronization                                                     | 69 |

| 4.4 Conclusions                                                                   | 69 |

| CHAPTER 5 Conclusions                                                             | 71 |

| 5.1 Summary                                                                       | 71 |

| 5.2 Challenges and Future Directions                                              | 72 |

| Bibliography                                                                      | 73 |

| Appedix A - PHY Layer implementation of K-State Energy Harvesting Receiver System | 1  |

| A.1 RFIC Front-end                                                                | 1  |

| A.2 DSP Baseband Design                                                           | 4  |

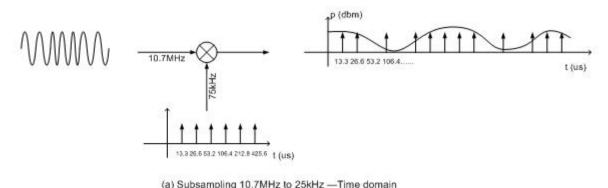

| A.2.1 Subsampling                                                                 | 4  |

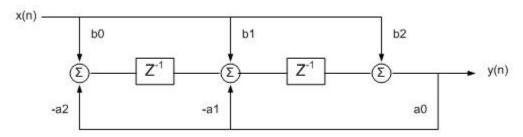

| A.2.2 Digital Low Pass Matched Filter                                             | 6  |

| A.2.3 Bit-sync                                                                    | 9  |

| A.3 DSP Software Implementation                                                   | 12 |

| A.3.1 Microcontroller Configurations                                              | 12 |

| A.3.2 Software Architecture                                                       | 14 |

| A.3.3 Test Result                                                                 | 21 |

| A.4 EHR DSP Code                                                                  | 25 |

| A.4.1 ADC, LPF, and Bit-Sync File                                                 | 25 |

| A.4.2 PIC Initialization file                                                     | 30 |

| A.4.3 ISR Interrupt Process file                                                  | 35 |

| Appedix B - K-State Energy Harvesting Demo Board Schematic                        | 37 |

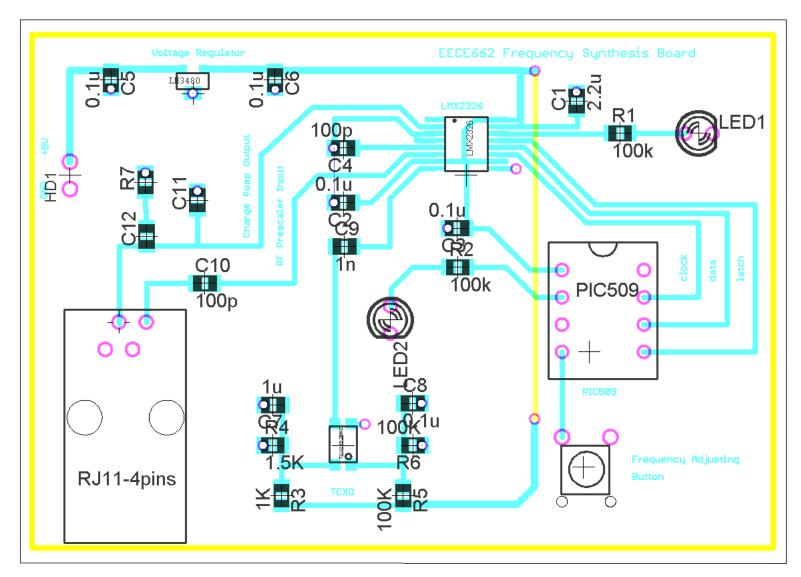

| Appedix C - Frequency Synthesis Board Schematic and Layout                        | 39 |

| Appedix D - K-State EHR Demo Board Code for 4MHz CPU Clock                        | 41 |

| Appedix E - K-State EHR Demo Board Code for 400kHz CPU Clock                      | 51 |

| Appedix F - Frequency Synthesizer PIC12F509 Code                                  | 61 |

| F.1 151MHz Board                                                                  | 61 |

| F 2 433MHz Board                                                                  | 66 |

| F.3 902MHz Board  | 71 |

|-------------------|----|

| F.4 2400MHz Board | 76 |

# **List of Figures**

| Figure 2-1 K-State Energy Harvesting Radio prototype board                              | 5        |

|-----------------------------------------------------------------------------------------|----------|

| Figure 2-2 RF operation mode (a) Continuous operation mode (b) Burst operation mode.    | 6        |

| Figure 2-3 K-State EHR demo board schematic                                             | 9        |

| Figure 2-4 CASIO SA5511S4 solar cells and CASIO fx-260SLOAR Calculators                 | 9        |

| Figure 2-5 PIC16F676 Pin Diagrams                                                       | 10       |

| Figure 2-6 K-State Transceiver RFIC block diagram [10]                                  | 11       |

| Figure 2-7 K-State RFIC programming register fields [10]                                | 12       |

| Figure 2-8 RFIC SPI Programming Timing sequence.                                        | 13       |

| Figure 2-9 1.1% Duty cycle with 4MHz CPU clock (above) times diagram (below)screen      | n        |

| captures of RF output on scope                                                          | 15       |

| Figure 2-10 1.3% Duty Cycle with 400kHz CPU clock                                       | 16       |

| Figure 2-11 1% duty cycly capacitor charge-discharge process                            | 17       |

| Figure 2-12 Microcontroller PIC16F676 Current consumption measurement with 4MHz         | clock    |

| (a) ACTIVE mode current (b) SLEEP mode current                                          | 18       |

| Figure 2-13 Four burst clusters with 1% duty cycle                                      | 19       |

| Figure 2-14 One Active period command signal and burst signal of 400kHz Clock Speed     | d design |

|                                                                                         | 19       |

| Figure 2-15 Five burst period                                                           | 20       |

| Figure 2-16 433.92MHz modulation signal                                                 | 21       |

| Figure 2-17 Yaesu VR-120 Receiver                                                       | 21       |

| Figure 2-18 EH demo board transmitting range test (a) Satellite view of 0.2km transmiss | ion      |

| range (b) view look back from parking lot (c) view looking inside hallway of RA20       | 97 [11]  |

|                                                                                         | 22       |

| Figure 3-1 Calculated range at 433 MHz with dipole antennas and 1 kbps data rate        | 29       |

| Figure 3-2 Calculated range at 2.4 GHz with dipole antennas and 1 kbps data rate        | 29       |

| Figure 3-3 Two type of experimental Propagation Links                                   | 31       |

| Figure 3-4 Rathbone Hall Engineering Building constructions                             | 32       |

| Figure 3-5 Measurements location marked on the indoor floor plan and outdoor map: Left    | is 2 <sup>nd</sup> |

|-------------------------------------------------------------------------------------------|--------------------|

| floor plan of Rathbone Hall; Right is the Google earth map of Rathbone Hall               | 33                 |

| Figure 3-6 Two path used for lower frequency transmitting range measurement               | 33                 |

| Figure 3-7 Antennas used in measurement                                                   | 34                 |

| Figure 3-8 Monopole antenna, Ground plane and antenna reflection coefficients measurement | ents35             |

| Figure 3-9 151MHz directional antenna S11=-14.9dB, monopole antenna S11=-12.7dB           | 36                 |

| Figure 3-10 433MHz directional antenna S11=-28dB, monopole antenna S11=-12.9dB            | 36                 |

| Figure 3-11 902MHz directional antenna S11=-12.5dB, monopole antenna S11=-10dB            | 36                 |

| Figure 3-12 2400MHz directional antenna S11=-31dB, monopole antenna S11=-13.3dB           | 37                 |

| Figure 3-13 Portable 10mW Transmitter photo                                               | 37                 |

| Figure 3-14 Receiver—Spectrum and monopole antenna                                        | 39                 |

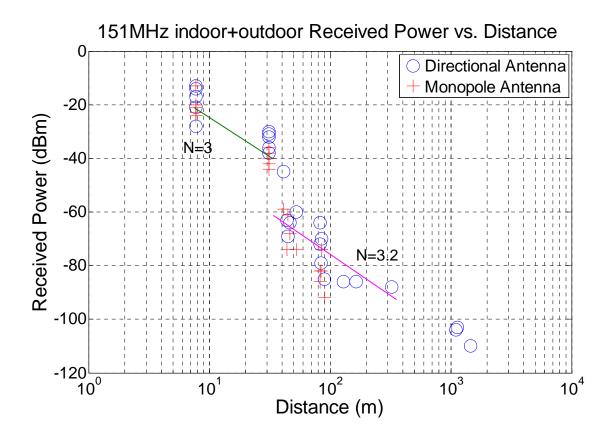

| Figure 3-15 151MHz two different link propagation with Path loss Exponent                 | 43                 |

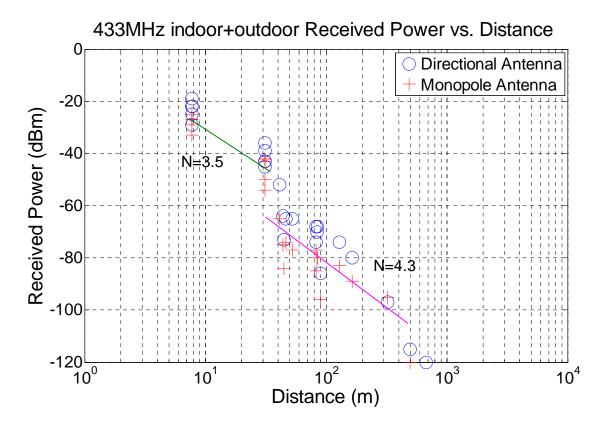

| Figure 3-16 433MHz two different link propagation with Path loss Exponent                 | 44                 |

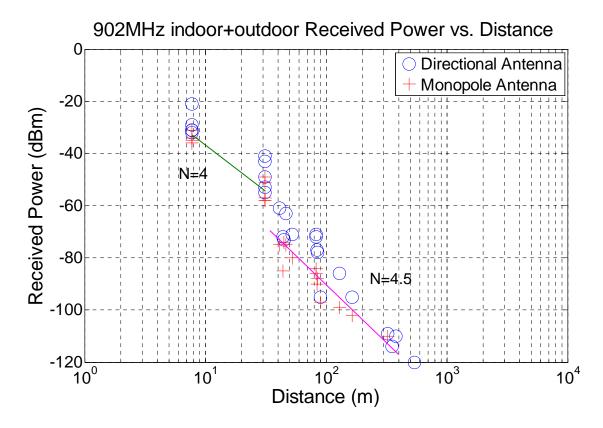

| Figure 3-17 902MHz two different link propagation with Path loss Exponent                 | 45                 |

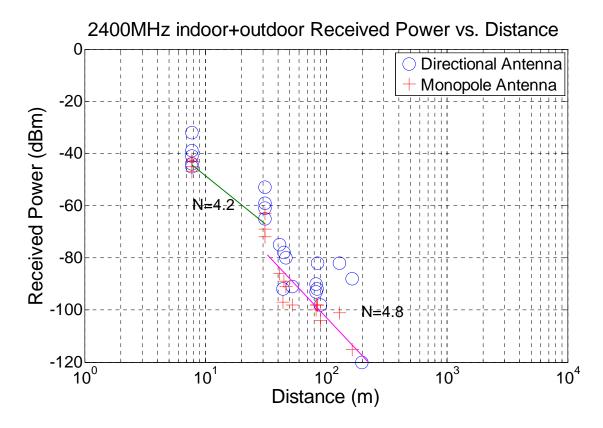

| Figure 3-18 2400MHz two different link propagation with Path loss Exponent                | 46                 |

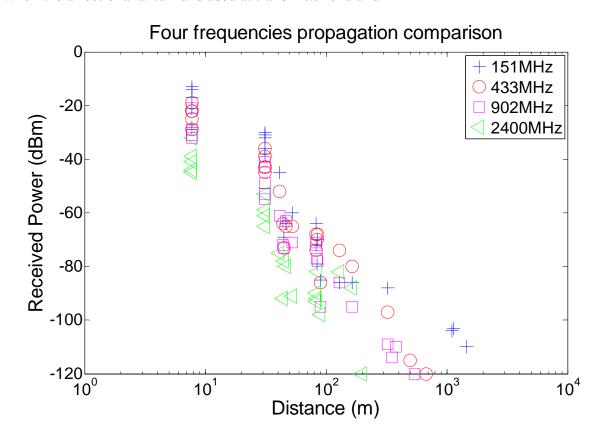

| Figure 3-19 Four frequencies propagation comparison                                       | 47                 |

| Figure 4-1 K-State Micro-Transceiver Demo Board                                           | 50                 |

| Figure 4-2 Frequency band and Data rate of IEEE802.15.4 (IEEE802.15.4 2006)               | 51                 |

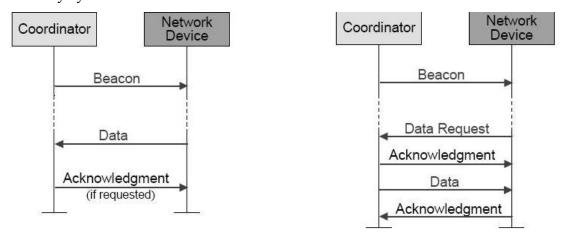

| Figure 4-3 ZigBee beacon-enabled TX / RX mode [1]                                         | 51                 |

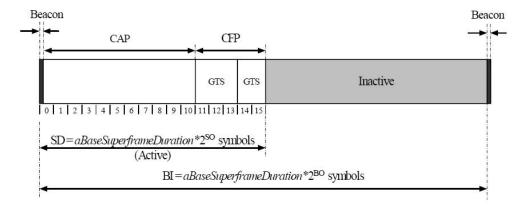

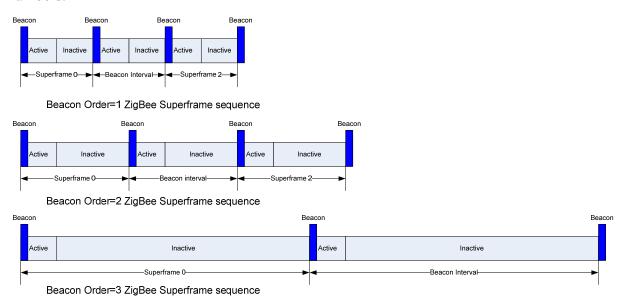

| Figure 4-4 IEEE 802.15.4 Superframe structure [1]                                         | 52                 |

| Figure 4-5 IEEE802.15.4 super frame sequence with different Beacon Oder                   | 52                 |

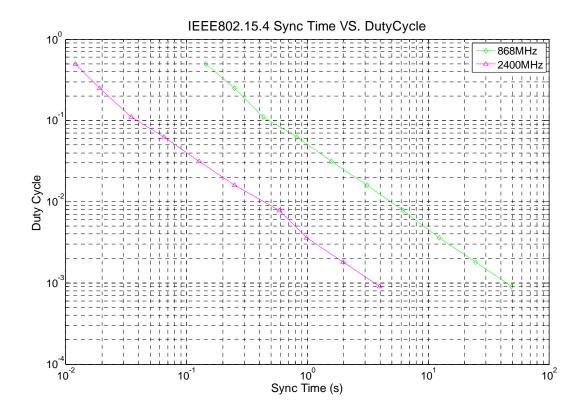

| Figure 4-6 IEEE802.15.4 Sync Time Vs. Duty Cycle                                          | 54                 |

| Figure 4-7 PHY Frame Format                                                               | 56                 |

| Figure 4-8 Preamble test experiment environment                                           | 58                 |

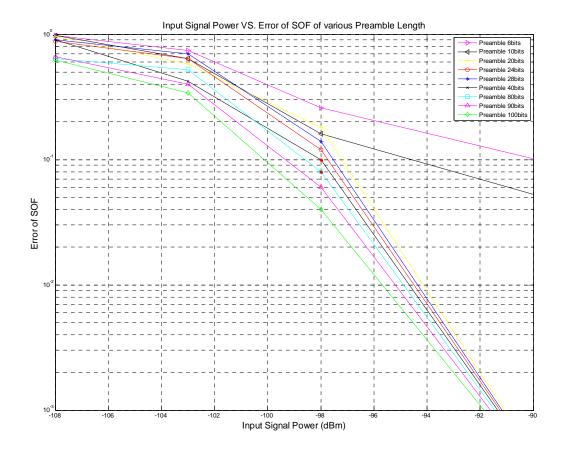

| Figure 4-9 Error Probability of SOF versus Input Signal Power of varied preamble length   | 59                 |

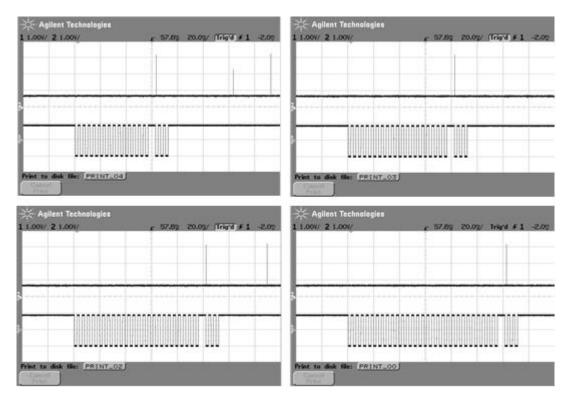

| Figure 4-10 SOF detection with various preamble length                                    | 60                 |

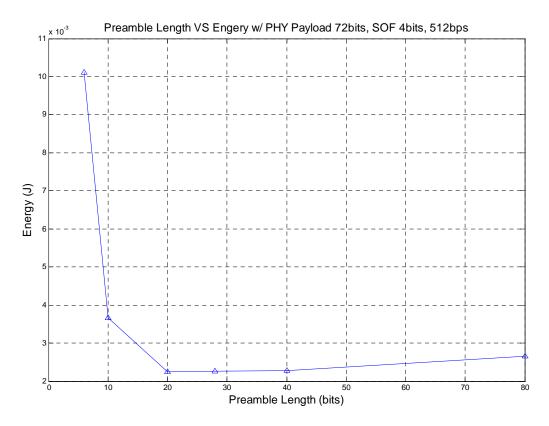

| Figure 4-11 Energy Consumption VS. Preamble Length                                        | 62                 |

| Figure 4-12 Beacon Frame format                                                           | 63                 |

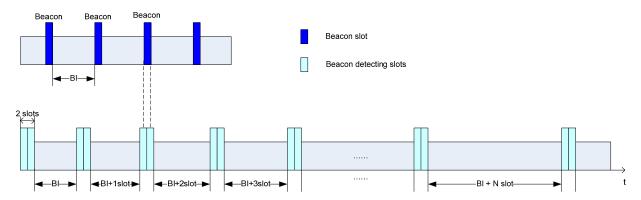

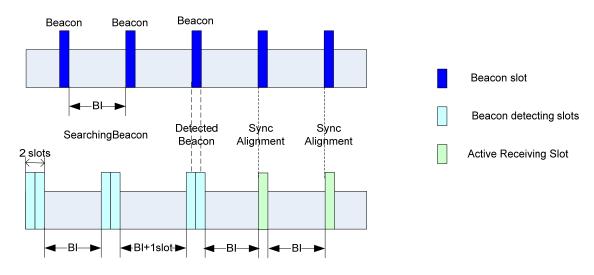

| Figure 4-13 Beacon searching process                                                      | 64                 |

| Figure 4-14 Beacon detected process                                                       | 64                 |

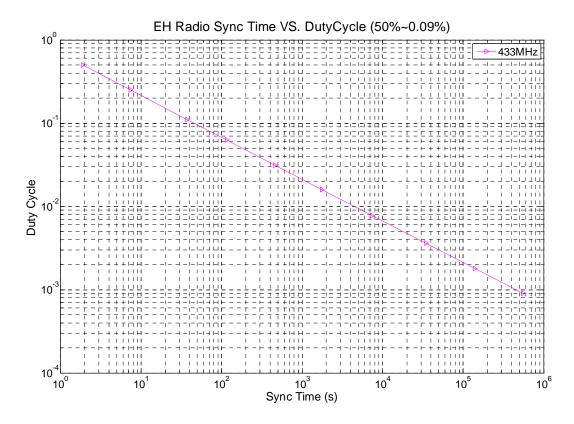

| Figure 4-15 Energy Harvesting Radio Sync time versus Duty cycle                           | 66                 |

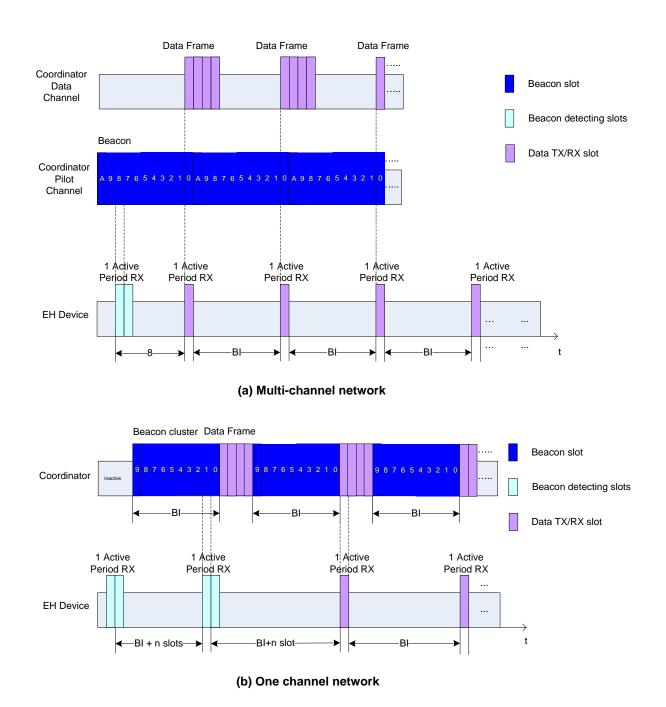

| Figure 4-16 Hybrid-EHR System Synchronization                                      | 68       |

|------------------------------------------------------------------------------------|----------|

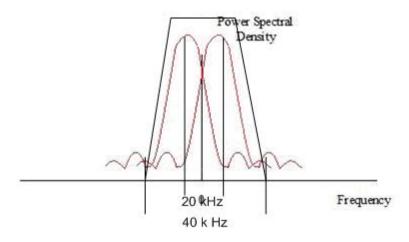

| Figure 5-1 IF filter and wideband FM modulation                                    | 2        |

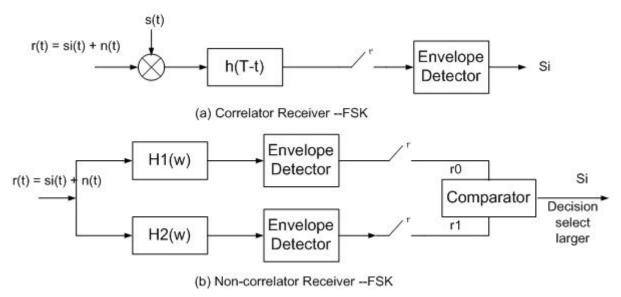

| Figure 5-2 FSK demodulation (a) Correlator Receiver (b) Non-correlator Receiver    | 2        |

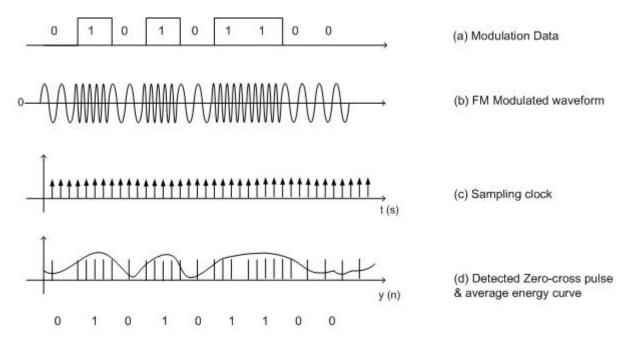

| Figure 5-3 One-shot FSK demodulation: (a) Modulation Data, (b) FM Modulated wavef  | orm, (c) |

| Zero cross Sampling clock, (d) Zero cross pulse & average energy curve             | 3        |

| Figure 5-4 Subsampling 10.7 MHz with 75kHz sampling rate                           | 5        |

| Figure 5-5 Two pole IIR digital low pass filter                                    | 6        |

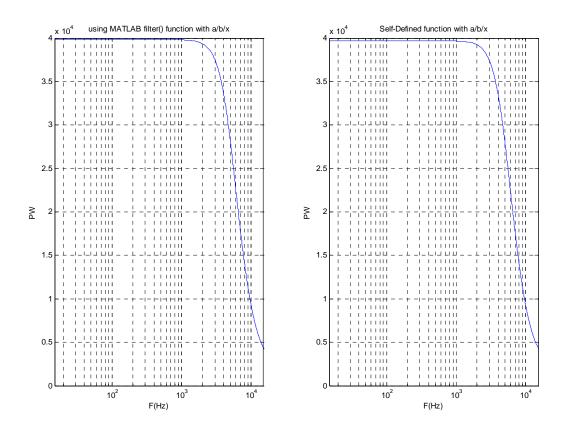

| Figure 5-6 Frequency response comparison of designed 1 kHz Low Pass Matched Filter | with     |

| MATLAB function plot                                                               | 8        |

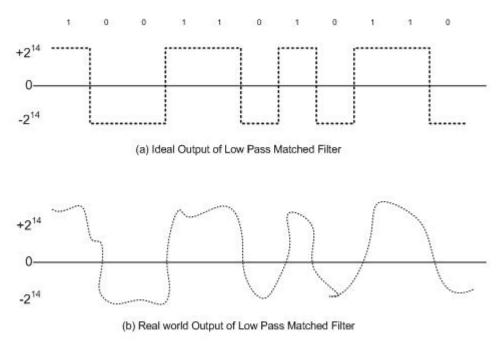

| Figure 5-7 output of LPMF (a) Ideal output (b) real output                         | 9        |

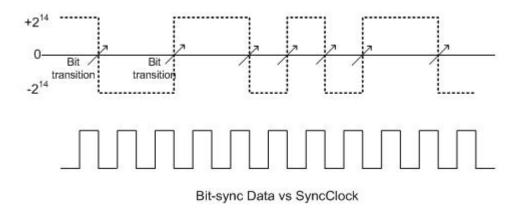

| Figure 5-8 Bit-sync data versus clock                                              | 10       |

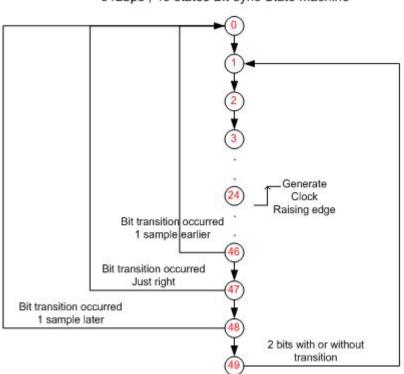

| Figure 5-9 Bit-sync Finite State Machine (FSM)                                     | 11       |

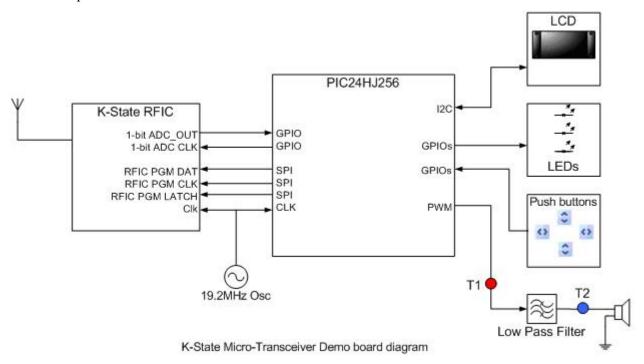

| Figure 5-10 K-State Micro-Transceiver Demo board block diagram                     | 12       |

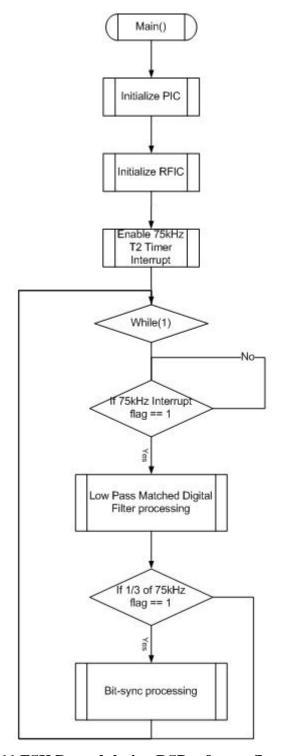

| Figure 5-11 FSK Demodulation DSP software flow                                     | 15       |

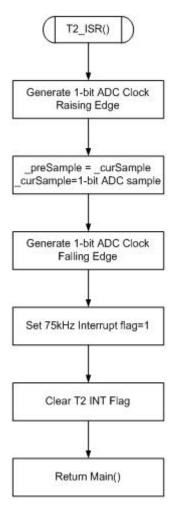

| Figure 5-12 Timer2 ISR                                                             | 16       |

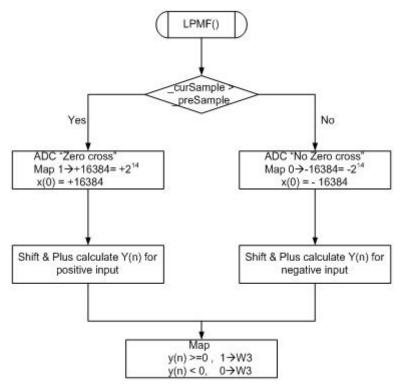

| Figure 5-13 LPMF procedure                                                         | 17       |

| Figure 5-14 LPF calculation coefficient b products                                 | 19       |

| Figure 5-15 LPF calculation coefficients a products                                | 20       |

| Figure 5-16 Calculated X shifts                                                    | 21       |

| Figure 5-17 PHY Layer DSP test environment                                         | 21       |

| Figure 5-18 10kHz Bandwith FSK modulation                                          | 22       |

| Figure 5-19 "Zero-cross" detection                                                 | 22       |

| Figure 5-20 512bps Bit-sync Test restults                                          | 23       |

| Figure 5-21 512bps Bit-sync Test restults                                          | 24       |

| Figure 5-22 Schematic                                                              | 37       |

| Figure 5-23 Layout                                                                 | 38       |

| Figure 5-24 Schematic                                                              | 39       |

| Figure 5-25 Layout                                                                 | 40       |

# **List of Tables**

| Table 2-1 Demo board Electrical Specification                                         | 7    |

|---------------------------------------------------------------------------------------|------|

| Table 3-1 quarter-wave antenna size and effective aperture of dipole antenna          | 34   |

| Table 3-2 Components list of 10mW un-modulated transmitter                            | 38   |

| Table 3-3 151MHz Propagation measurement results                                      | 39   |

| Table 3-4 433MHz Propagation measurement results                                      | 40   |

| Table 3-5 902MHz Propagation measurement results                                      | 41   |

| Table 3-6 2400MHz Propagation measurement results                                     | 41   |

| Table 3-7 Path Loss Exponents comparison                                              | . 46 |

| Table 4-1 IEEE802.15.4 Synchronization time calculation                               | 53   |

| Table 4-2 Barker code                                                                 | 56   |

| Table 4-3 Preamble Length VS. Energy when data rate is 512bps                         | 61   |

| Table 4-4 Sync time and power consumption comparison of EHR and IEEE802.15.4 standard | ļ    |

| radio                                                                                 | 65   |

| Table A-1 Two pole LPF coefficients                                                   | 7    |

| Table A-2 Bit shift and product factor                                                | 18   |

| Table A-3 LPF coefficients 2 <sup>n</sup> expression                                  | 18   |

# Acknowledgements

This thesis is obviously not the product of my own individual efforts, but the fruit of intense collaboration. First and the foremost, I would like to thank my major advisor, Professor Bill Kuhn for his excellent guidance, above and beyond the mere technical research. He has truly given meaning to the word "advisor", helping me every step of the academic way. In addition, I would also like to express my gratitude towards the other members of my committee, Dr. Don Gruenbacher and Dr. Bala Natarajan, for their support and feedback, and my colleagues in Wireless Communication Hardware design group.

I also gratefully acknowledge our research sponsor – Peregrine Semiconductor for their support.

# **CHAPTER 1** Introduction

#### 1.1 The Future of Wireless Sensor Networks

Wireless sensor networks (WSN) and associated wireless sensor node devices in industrial and civilian applications have seen rapid growth since they were originally motivated by military applications. They have been or will be widely used in industrial process monitoring and controls, earthquake monitoring, healthcare applications, construction health monitoring, and home automation and traffic control. Additionally, they will help humans to explore outer space, planets, and moons. For example, future Mars rovers could plant hundreds of WSN nodes on the planet during exploration and then collect data from all nodes over time. They will help humans to inspect and monitor the south and north poles, deserts, virgin forests, unfathomable depths of the oceans and no man's lands on the earth. To implement all these applications, *battery-free* and *Energy Harvesting Radio(EHR)* nodes are preferred. Energy harvesting nodes use energy captured from natural or human environments, such as solar, thermal, wind, biological and kinetic processes. Unlike traditional battery powered systems, the advantages of energy harvesting devices reduce or eliminated the need for manual intervention. Moreover, waste from depleted batteries is eliminated, many application environment restrictions are removed, and the WSN lifecycle is extended from months or years, to decades or centuries.

#### 1.2 Current Research on Wireless Sensor Nodes

The wireless sensor node is an important part of a wireless sensor network. It must handle the tasks of gathering sensory information, processing data, and communicating with the network. For designing current wireless sensor nodes, IEEE802.15.4 is a main standard to interface with.

IEEE Std 802.15.4 defines the physical layer (PHY) and medium access control (MAC) sublayer specifications for low-data-rate wireless connectivity with fixed, portable, and moving devices with limited battery consumption, typically operating in the personal operating space (POS) of 10m [1]. In the definition, three main frequency bands are used, 2.4GHz for global, 915MHz in America and 868MHz in Europe. The bit rate ranges from 20kbps to 250kbps. BPSK, ASK, and O-QPSK may be used, with DSSS, OCDM (Orthogonal Code Division

Multiplexing) spreading methods at the physical layer. CSMA-CA (Carrier Sense Multiple Access with Collision Avoidance) channel access method is used at the MAC layer.

Most current wireless sensor nodes research is focused on battery consumption improvements [2] [3] [4], energy/power management [5], application of wireless sensor nodes [6], and energy harvesting methods [7]. Few are proposing a PHY or MAC layer. Research of narrow-band, spread spectrum, and ultra-wideband (UWB) technologies of PHY layer has been evaluated [8]. Research of MAC layer has resulted in talk of the mobility of WSN [9]. Few self-powered wireless radio commercial products were developed [24]. However, almost all of them assume using IEEE802.15.4, Blutooth, or UWB as PHY layer construction and *few* have proposed approaches to *optimize PHY and MAC sublayer on a system level* (although very recently a new 802.15.4f standards proposal has been launched [25]).

## 1.3 Challenges for Energy Harvesting Wireless Sensor Nodes

The challenges of energy harvesting wireless sensor nodes include several aspects: developing an efficient energy harvester, implementing suitable radio systems, and providing high energy storage capability. The focus of this thesis is on the radio systems challenges and associated solutions. The radio system design challenge includes:

- 1. RF transmitting mode versus power consumption

- 2. Low power circuit design

- 3. Frequency selection versus transmitting performance

- 4. Antenna technology versus RF link budget

- 5. PHY layer frame construction versus energy consumptions

- 6. Ultra-low duty cycle communication synchronizations

# 1.4 Thesis Organization

In this thesis, three chapters address the energy harvesting wireless sensor nodes design challenges listed above. Chapter two addresses points 1 and 2. An EHR prototype demo experiment shows a burst communication system employing common indoor solar energy harvester panels and capacitor energy storage, and discusses methods for low power circuit design. Chapter three is focused on points 3 and 4, addressing *frequency selection versus* transmitting performance and antenna technology versus RF link budget considerations. Four

frequencies' propagation performance were measured in the VHF/UHF frequency band including both indoor and outdoor environments. Chapter four focuses on points 5 and 6 and investigates the PHY frame construction, and synchronization problems. Finally chapter five (Conclusions) summarizes overall recommendations and possible future directions for the research area.

# CHAPTER 2 K-State Energy Harvesting Radio (EHR) Prototype Demo Board

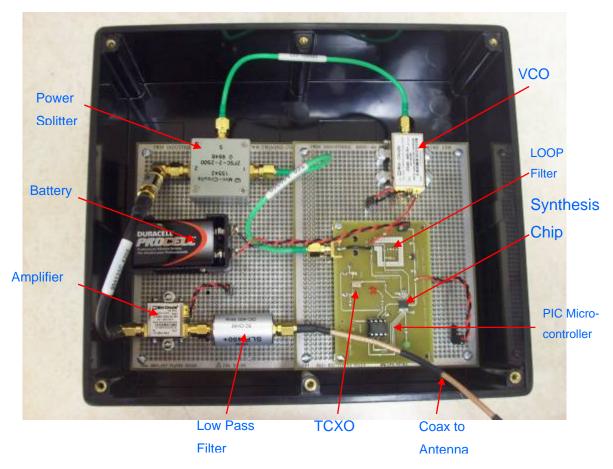

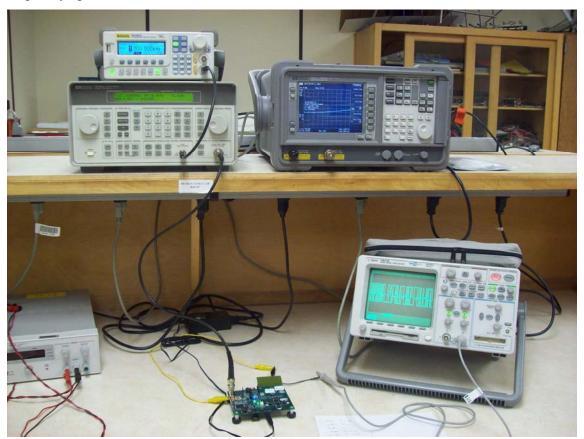

In this chapter, the design and testing of K-State's EHR prototype demo board (Figure2-1) are discussed. The *purpose of this part is to prove feasibility of an energy harvesting radio system* by using burst communication mode techniques at 433MHz operation frequency and currently available radio technology. The motivation of this is that most current research and industrial products of wireless sensor nodes are still using batteries as power supply. They are focused on ways to improve energy management methods, energy efficient wireless sensor network protocols, or low power SoC (System on Chip) technologies for short-range use. Unlike these efforts, K-State's EHR prototype is a battery-less wireless sensor node demonstration. The demo shows that the energy harvested by four 5cm² solar panels from indoor lighting is enough to support 433MHz bust mode wireless communication with range approaching 0.2km or more. In this system, the K-State microtransceiver RFIC [10] is used as the RF front end, and solar cells from low-cost calculator products are used as the energy source. A 16F series PIC microcontroller serves as the data source and timing subsystem.

Figure 2-1 K-State Energy Harvesting Radio prototype board

# 2.1 RF transmission mode Versus Power Consumption

For an EHR system, to keep the average power consumption at the micro-watt levels available with indoor solar-cell harvesters, we must reduce both the average digital baseband power consumption and the average RF transceiver power consumption. For a digital baseband circuit, the power consumption scales down when processing clock speed reduces, such as the DSP chip operation clock. Thus, low power systems can be implemented when processor clocks down to the *kHz* range and continuous operation is possible. Taking notice, the data rate will be reduced respectively. Unfortunately, RF circuit power consumption does not reduce when the data rate goes lower. The analog parts in RF circuits, such as LNA and VCO must still consume the same current even if data rate is lowered. Many techniques are being researched to design low power RF circuits, such as using very high quality passive elements, Q-enhanced LC

resonant or MEMs circuits to replace the preselect filter and LNA, and using lower power IC processes, etc [11], but to-date, none of these techniques offers the possibility of micro-watt RF transceiver functions.

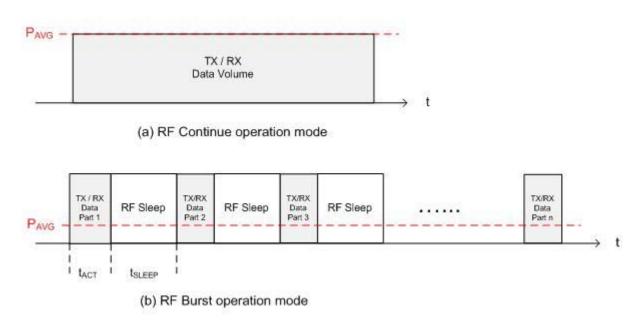

Fortunately, *burst mode* operation is an effective way to reduce overall average power consumption. In burst mode, the active operation period T is broken down into several pieces or time slots,  $t_1$ ,  $t_2$ , ... $t_n$  including *active subperiods* and *sleep subperiods* where  $T = t_1 + t_2 + ... + t_n$ . Thus the whole transmission data volume is broken down into several parts,  $d_1$ ,  $d_2$ , ... $d_n$ , . Figure 2-2 shows the comparison of continuous and burst modes. The red symbol  $P_{AVG}$  and the dash lines are indicating the average power consumption of operating period. Obviously, using burst mode saves power more than using continuous mode.

Figure 2-2 RF operation mode (a) Continuous operation mode (b) Burst operation mode

Therefore, the burst mode has significant advantage for EHR systems since there *active* and sleep alternated processes allow the energy to be re-charged during the SLEEP periods and discharged during the ACTIVE periods.

# 2.2 Design Principle

The burst communication mode is the fundamental design idea of the EHR demo board. To simulate a data burst, we modulated a 433.92MHz sine-wave signal by a 1kHz square wave

burst. Using 1kHz square burst is the same as 1kHz amplitude-shift-keying (ASK) modulated RF signal. With the simulated 1010 pattern created with a 0.5ms square wave burst, a human ear recognizable "beep" tone can easily be detected by a commercial receiver for demonstration and range testing purposes.

The AM square wave burst envelope was generated in two ways: (1) Hardware control method: turn on and off the radio frequency chip's RFIC\_PW\_DN pin directly at 1kHz frequency; (2) Software control method: program "LPAena" bit of the RFIC control register to switch radio frequency chip between transmitting and standby modes. These two ways were designed for different system configurations of CPU operating clock speed and energy storage capacitor's value. The first method, by controlling RFIC hardware pin, requires less CPU instruction cycles because of small code size. By contrast, the second method, by programming the RFIC register for each pulsing, requires more CPU instruction cycle resources since code size is bigger.

In the design of the whole system, these two methods could be integrated to exploit the tradeoffs between the energy consumption and timing consumption. In later parts of this chapter, these two different design and measurement results are discussed and compared.

# 2.3 Hardware Design

The main components of the EHR demo board hardware included a K-State RFIC, a commercial 5 mW TCXO, a Microchip PIC16F676, a voltage regulator, and SMT Capacitors. Table 2-1 is the EHR board's electrical specification.

**Table 2-1 Demo board Electrical Specification**

| Duty cycle                                                                   | ≤ 1.3%    |

|------------------------------------------------------------------------------|-----------|

| solar cell output Voltage (two in series)                                    | 5.4v      |

| Solar cell output Current (indoor fluorescent lights)                        | 0.02mA    |

| Solar cell output Current (40-Watt incandescent bulb with 6 inches distance) | 0.32mA    |

| RFIC supply Voltage range                                                    | 3.0v~3.3v |

| RFIC TX mode Current                                                         | ≤20mA     |

| RFIC Sleep mode Current                                                      | ≤0.01mA   |

| RFIC TX Frequency                           | 433.92MHz  |

|---------------------------------------------|------------|

| PIC16F676 Operating mode Voltage            | 1.2v~3.0v  |

| PIC16F676 Operating mode Current (4kHz)     | ≤0.5mA     |

| PIC16F676 Operating mode Current (4MHz)     | ≤0.74mA    |

| PIC16F676 Sleeping mode Current(4kHz)       | ≤0.05mA    |

| PIC16F676 Sleeping mode Current(4MHz)       | ≤0.17mA    |

| 3.3v Voltage Regulator Input Voltage range  | 3.7v~12v   |

| 3.3v Voltage Regulator Output Voltage range | 3.3v +/-5% |

| 3.3v Voltage Regulator Gnd current          | ≤0.5mA     |

$$I_{avg} = \frac{(I_{PIC\_act} + I_{RF\_act}) \times T_{act} + (I_{PIC\_sleep} + I_{RF\_sleep}) \times T_{sleep}}{T_{act} + T_{sleep}}$$

(2-1)

Depends on the electrical specification, we can get the average current of the system using the equation (2-1). In the equation (2-1),  $I_{avg}$  is average current of system,  $I_{PIC\_act}$  is the current of the Microcontroller consumed during the active period,  $I_{RF\_act}$  is the current of the RFIC consumed during the active operation period,  $I_{PIC\_sleep}$  is the current of the Microcontroller consumed during the sleep mode,  $I_{RF\_sleep}$  is the current of the RFIC consumes during the sleep mode,  $T_{act}$  is total active time slots and  $T_{sleep}$  is total sleep time slots. The duty cycle, which is the ratio of  $\frac{T_{act}}{T_{act} + T_{sleep}}$ , can be designed depending on the system requirements, system power consumption, energy harvesting capability, and energy storage capability. In section 2, 4, example calculations show the relationship of the duty cycle, average current and voltage variation.

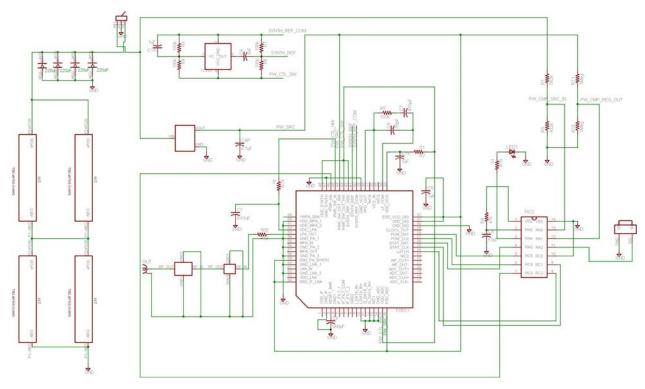

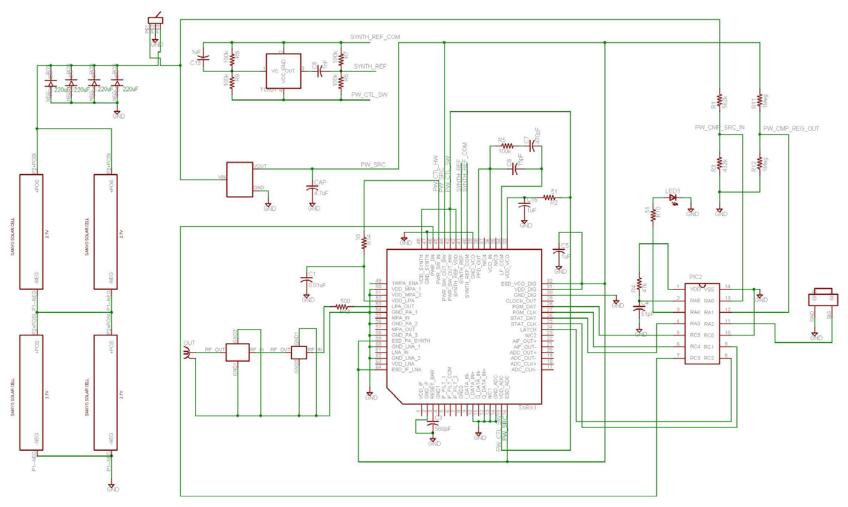

Figure 2-3 K-State EHR demo board schematic

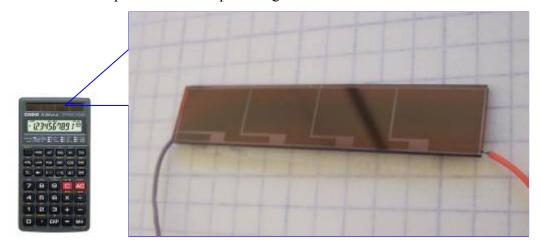

Figure 2-3 is the K-State EHR demo board schematics. The layout is in Figure A-2. The energy is harvested by using four CASIO SA5511S4 solar cells (Figure 2-4). Each can provide 2.7v dc-voltage, 0.16mA dc-current under a 40-Watt incandescent bulb with 6 inches distance. Otherwise, each can provide 2.7v dc-voltage, 0.033mA dc-current under indoor fluorescent lights. These solar cells were salvaged from CASIO fx-260SLOAR commercial Calculators. To maximize energy harvesting capability, two of them were attached in series and then parallel led with another series two to provide 5.4v output at higher current.

Figure 2-4 CASIO SA5511S4 solar cells and CASIO fx-260SLOAR Calculators

The energy storage is using four 220uF SMT capacitors, which are connected in shunt between solar cells and power switch. A TPS76130-100MA voltage regulator is put after the power switch to provide stable 3.3v dc-voltage for the RFIC and the Microchip PIC.

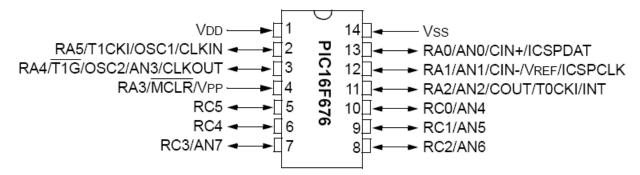

The 14 pins chip in the schematic is a Microchip PIC16F676, which is a Flash-Based 8-bit CMOS, high performance, low power, and wide operating voltage range (2.0v~5.5v) RISC CPU. Figure 2-5 shows PIC16F676 pin diagram. This microcontroller can be configured to work with several different clock speeds, either an external or an internal clock oscillator.

Figure 2-5 PIC16F676 Pin Diagrams

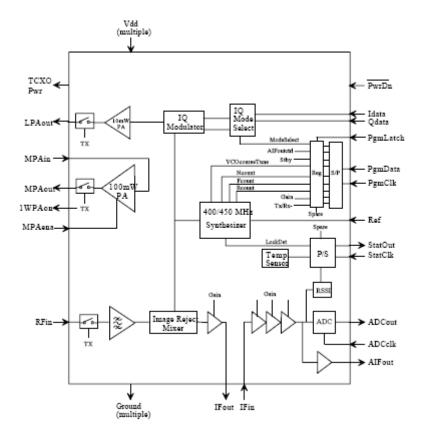

The biggest chip in the schematic is K-State RFIC. Figure 2-6 shows the RFIC block diagram. The PgmClk, PgmData and PgmLatch are serial port interface signals defined by the RFIC. The  $IF_{out}$  and  $IF_{in}$  are the 10.7MHz Intermediate Frequency output and input, which connect with an off-chip IF filter. The ADCclk is 1bit ADC sampling clock input pin. The ADCout is the 1bit ADC sampling data output pin. The Ref is a 19.2MHz TCXO reference clock input pin.

Figure 2-6 K-State Transceiver RFIC block diagram [10]

A 19.2MHz TCXO oscillator is used as RF reference clock, which consume 5mW (1.5mA at 3.3v). A DC-490MHz low pass filter is put between the attenuator and the antenna for transmitter harmonic attenuation in and receiver preselection/protection from cell phone and other strong nearby emitters.

# 2.4 Software Design

## 2.4.1 RFIC Programming

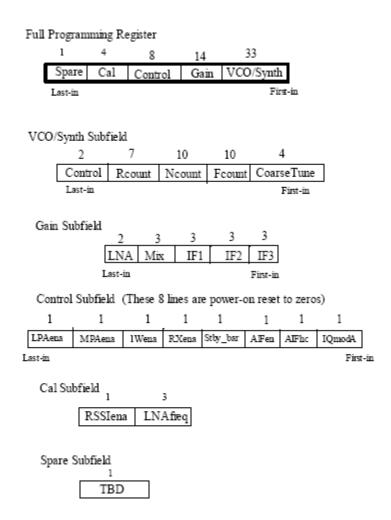

The first function of the software is programming the RFIC. The RFIC can be programmed to work in TX, RX, or SLEEP modes through a serial port interface (SPI). The Microcontroller programs the registers, which are inside the RFIC, through the SPI. Figure 2-7 shows the RFIC programmable register fields [10].

Figure 2-7 K-State RFIC programming register fields [10]

There are 60 bits in the programmable register, which are divided into four main function subfields. The VCO/Synth subfield is used to set the synthesizer. The Gain subfield is used to control low noise amplifier and IF amplifier. The Control subfield is used to control the chips working mode. This includes enable and disable power amplifier, RX/TX mode switch, Sleep/ Standby mode switch, etc. The Cal subfield is used to configure RSSI and set the LNA frequency. To configure the VCO/Synth, equation (2-2) is used to calculate N and R. Here  $f_{ref}$  is the reference frequency, which is 19.2MHz, and  $f_{vco}$  is the frequency of the signal generated by

$$\frac{f_{ref}}{R} = \frac{f_{vco}}{N} \tag{2-2}$$

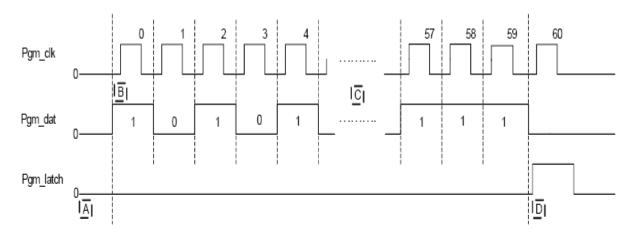

VCO. In "A Low-Power, Radiation-tolerant, RFIC Micro-Transceiver Chipset for Space Application" [10], detailed programming steps for the RFIC are provided. Programming should begin with *Pgm dat*, *Pgm clk*, and *Latch* input pins at zero. Place first bit onto *Pgm dat* input

pin. Then bring  $Pgm\_clk$  high and return it to low. Repeat with subsequent bits until all 60 bits are entered. Finally, raise Latch line to high state and then issue one more clock to latch data into the chip. No changes occur in the RFIC chip's operation until this final clock rising edge with Latch is asserted [10]. Using this description, the programming time sequence is designed as shown in Figure 2-8.

· Programming Register Data writing from PIC to RFIC

- Programming should begin with Pgm\_dat, Pgm\_clk, and Latch input pins at zero.

- Place first bit onto Pgm\_dat input pin. Then bring Pgm\_clk high and return it to low.

- | C | Repeat with subsequent bits until all 60 are entered.

- Finally, raise Latch line to high state and issue one more clock to latch data into chip.

Figure 2-8 RFIC SPI Programming Timing sequence

## 2.4.2 Duty Cycle Design

The second main function of the software is the duty cycle timing control. The software controls the time period switching of the RFIC transmission, sleeping, and energy recharging. Timing is critical to keep the system working in a low energy environment. To design the critical timing, we should know the accurate CPU instruction operation cycle time. For the PIC16F676, one instructions cycle consists of four oscillator periods. As mentioned in the previous design principle part, there are two different ways used to implement the RFIC control: one is software

controlled and the other one is hardware controlled. Using the software controlled method; the CPU oscillator clock is configured with 4 MHz internal high CPU oscillator speeds, which has a 1 us instruction cycle. Using the hardware controlled method; the clock speed can be reduced to conserve energy. In this case, the CPU oscillator clock was configured with 400kHz external RC low CPU oscillator speeds, which has a 10 us instruction cycle. These two different configurations implementations are discussed and compared below.

## 2.4.2.1 High CPU Clock, Software Control TX

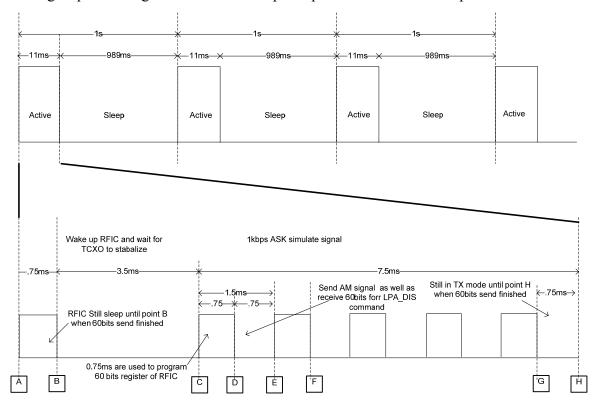

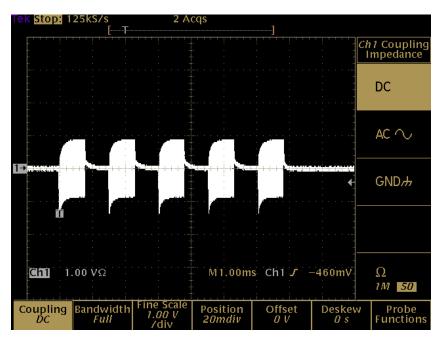

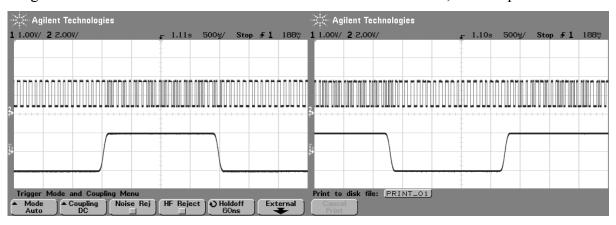

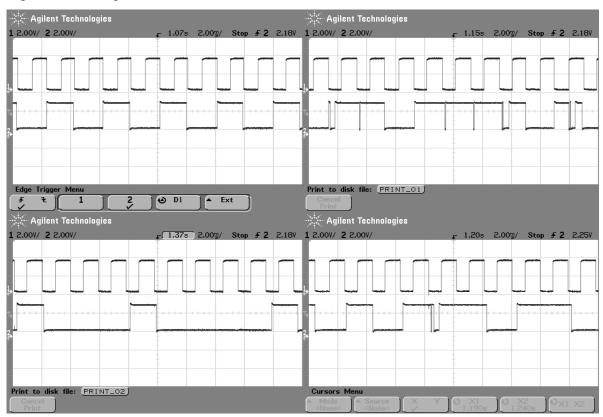

In this design, the microcontroller PIC uses a 4MHz system clock configured by using the internal oscillator. The high clock speed is needed in the software controlled case to allow repeated program of the 60 bits control register to modulate the bits. The code was written in assemble language and the total programming time of writing 60 bits RFIC registers is 0.75ms. The code is in Appendix-D. Figure 2-9 shows the resulting 1.1% duty cycle design software processing sequence diagram and the RF output captured on an oscilloscope.

Figure 2-9 1.1% Duty cycle with 4MHz CPU clock (above) times diagram (below)screen captures of RF output on scope

According to equation (2-1), the average current of this design is 0.41mA.

$$I_{avg} = \frac{(0.74mA + 20mA) \times 11ms + (0.17mA + 0.01mA) \times 989ms}{1000ms} = 0.4062mA$$

From above calculated result, it is easy to estimate approximate average power consumption of the EHR demo board, which is 0.4062mA\*3.3v=1.34mW. To compare the result with using batteries instead of the solar cells for this radio, assume we are using a 2.7Ah AA batterie. This battery could support the radio board for about 6650 hours (about 277 days). In other words, the battery needs to be changed in under a year, whereas the HER radio could function indefinitely.

#### 2.4.2.2 Low CPU Clock, Hardware Control TX

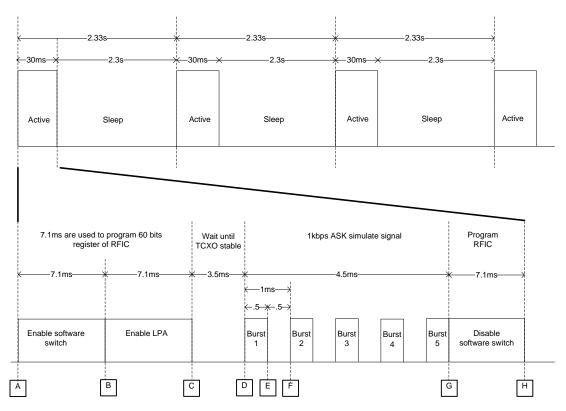

The second configuration uses a lower CPU clock. The duty cycle is designed as 1.3% and the PIC operating clock is using an external RC 400kHz oscillator. Figure 2-10 shows the software processing diagram.

Figure 2-10 1.3% Duty Cycle with 400kHz CPU clock

## 2.4.2.3 Computing Active and Sleep Time

From Figure 2-10, we can find the active time to be 30ms and the sleep time is 2.3s. To determine this duty cycle, we must determine the charging and discharging time of the capacitors. The equation (2-3) describes the relationship of the voltage, current, and the capacitor values where dv/dt is the voltage changing or discharging rate, i is the current, and C is the capacitor value.

$$i = \frac{dv}{dt}C\tag{2-3}$$

From section 2.3, we note that the EHR demo system has four parallel 220uF capacitors, the microcontroller PIC active current is 0.5mA, and the RFIC transmitting current is 20mA. Thus the voltage dischargs from capacitor during the 30ms active period is given:

$$dv = \frac{i \times dt}{C} = \frac{(0.5 + 20)mA \times 30ms}{4 \times 220uF} = 0.7v$$

The time to recharge this 0.7v voltage back using four solar cells, which provides 2x0.13mA current, is:

$$dt = \frac{dv}{i}C = \frac{0.7v}{2 \times 0.13mA} \times 4 \times 220uF = 2.3s$$

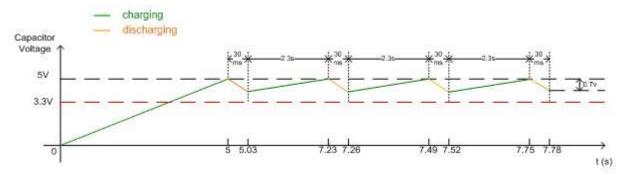

This is why the sleep time was designed as 2.3s when the active time is 30ms. Figure 2-11 shows the capacitors charging and discharging process.

Figure 2-11 1% duty cycly capacitor charge-discharge process

The average current of this design can be calculated from equation (2-1) as:

$$I_{avg} = \frac{(0.5mA + 20mA) \times 30ms + (0.05mA + 0.01mA) \times 2300ms}{30ms + 2300ms} = 0.323mA$$

If 2.7Ah AA batteries were used to drive this demo board instead of the solar cells. This device could continue work about 8400 hours, approximately 348 days. Although the life time is extended compared with the 4 MHz CPU configurations, the total data volume is significantly reduced due to the longer cycle time mode necessary by repeated programming of the 60 bit RFIC register.

In the following part of this chapter, the test in the lab tests and outdoor environment tests will show the performance of 400kHz CPU clock EHR board.

#### 2.5 Test Results

The measurements of this EHR demo board include Lab and outdoor performance tests. In the Lab test, we focused on the center frequency, duty cycle, board power consumption, and system reliability. The outdoor performance test was focused on the transmitting distance, and propagation issues inside and outside of the building.

#### 2.5.1 Lab Test

#### 2.5.1.1 Current Consumption Test

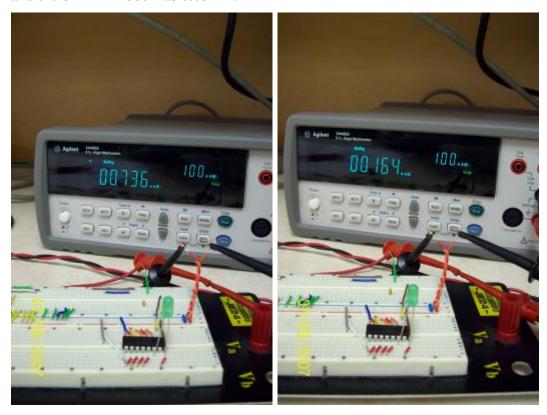

The Microcontroller and the RFIC are the two main power consumption components of this demo board. We already knew the RFIC's action currents was less than 20mA and the SLEEP mode currents was less than 0.01mA. The Microcontroller PIC power consumption was measured by using the photo board shown in Figure 2-12. This picture shows 4MHz clock configurations current consumption. The ACTIVE mode current was 0.74mA and SLEEP mode was 0.16mA (higher than expected from the datasheet). Use the same technique, we measured the 400kHz CPU clock configurations current consumption. The ACTIVE mode current was 0.5mA and the SLEEP mode was 0.05mA.

Figure 2-12 Microcontroller PIC16F676 Current consumption measurement with 4MHz clock (a) ACTIVE mode current (b) SLEEP mode current

#### 2.5.1.2 The Burst Communication Test

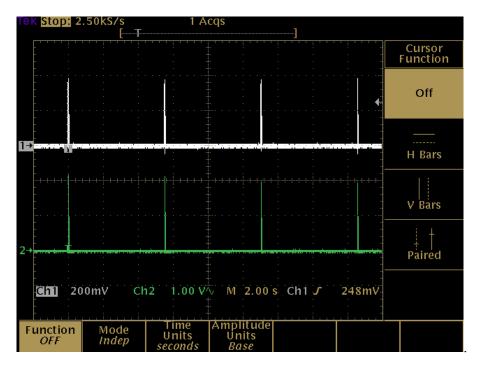

The Burst communication was measured by using a Tektronix TDS 724D Oscilloscope, which is a two channel digital phosphor 500MHz~2GS/s oscilloscope. Figure 2-10 previously showed the duty cycle design of using a 400kHz CPU operating clock configuration. Figure 2-13 is 4 burst signal capture. The channel 1 signal is microcontroller control signal (Command signal). The channel 2 signal is the RF output burst signal.

Figure 2-13 Four burst clusters with 1% duty cycle

Figure 2-14 is the zoomed in picture of one burst of the four in Figure 2-13. Channel 1 is the Microcontroller programming signal (Command signal) and the channel 2 is the RF output burst signal. Compared with Figure 2-10, it matches its design. The whole active period is 30ms.

Figure 2-14 One Active period command signal and burst signal of 400kHz Clock Speed design

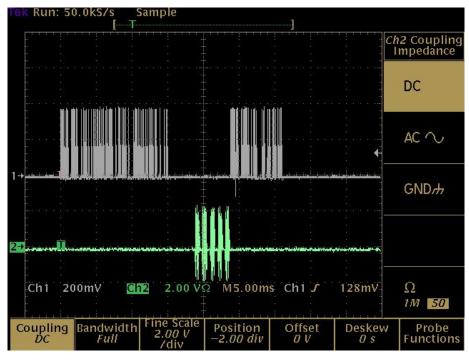

Figure 2-15 is the zoomed in burst period. Five bursts plus the time period of waiting TCXO standby, which last 8.68ms. The design time was 8ms. The difference was due to delay caused by software and oscilloscope measurement.

Figure 2-15 Five burst period

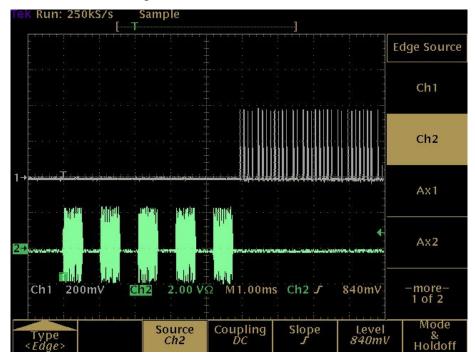

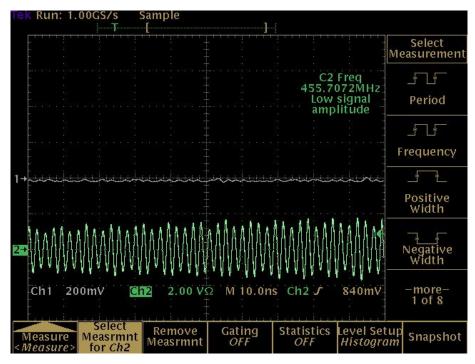

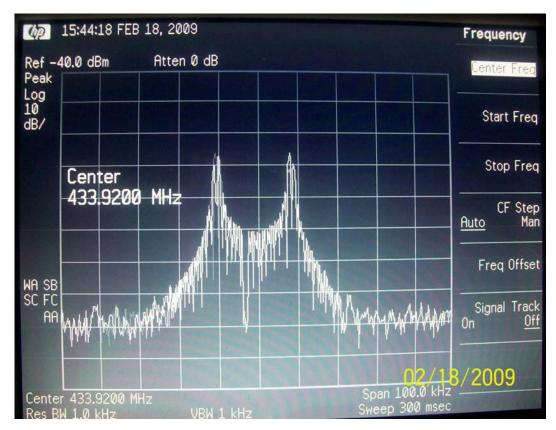

Figure 2-16 is the zoomed in picture of one burst signal. It is a 433MHz modulated sinwave.

#### Figure 2-16 433.92MHz modulation signal

#### 2.5.1.3 The System Reliability Test

For EHR systems, one important capability is that the system re-starts when energy satisfies the requirement after it was off. To test this, we moved the demo board away from the lights for about 5 minutes, thus the transmitting was stopped. When we move it back under to the lights, it successfully transmitted with expected duty cycle after the capacitor reached full charge.

#### 2.5.2 Outdoor Test

The purpose of outdoor test was to estimate the transmitting range of the EHR prototype board. To test the range, we used a Yaesu VR-120D handheld radio shown in Figure 2-16. The VR-120D specifies a sensitivity of 0.6uV, which equates to -111dBm [11]. Since the burst clusters are actually are AM modulated signals we could hear a 'beep' when we use an AM receiver.

Figure 2-17 Yaesu VR-120 Receiver

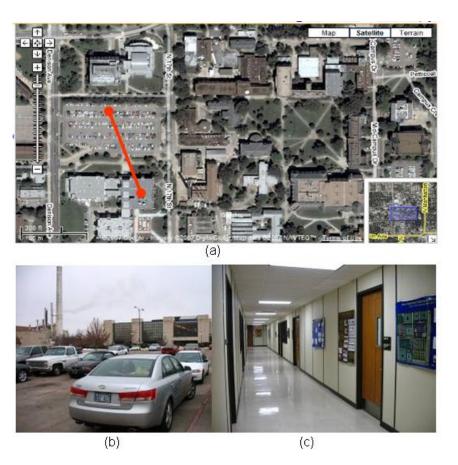

Figure 2-18 are google maps with a mark to show the furthest point that the 'beep' could be heard. The signal was transmitted from within room RA2097 of Rathbone Hall at Kansas State University and received in the North parking lot up to approximately 0.2km away.

Figure 2-18 EH demo board transmitting range test (a) Satellite view of 0.2km transmission range (b) view look back from parking lot (c) view looking inside hallway of RA2097 [11]

#### 2.6 Conclusions

This demo board has shown the feasibility of a simple energy harvesting wireless node with solar energy harvesting, which uses burst communication mode with very low duty cycle. This prototype board has shown the basic hardware skeleton of an energy harvesting wireless node including solar cell energy harvester, energy storage, radio and control unit. This chapter also has shown the software skeleton of an EHR node, which includes energy storage and management, burst communication and duty cycle management. The software allowed the system to self-recover after the power was re-satisfied. This demo board also proved that the K-State 400MHz RFIC is a very good RF front-end working in the energy harvesting applications as it has low active and sleep mode power, easy control to implement burst mode, and reliable performance.

# **CHAPTER 3 RF Link Budgets of EHR Systems**

In the previous chapter, we demonstrated basic transmission performance by using ordinary ASK modulation techniques at 433.92MHz. However, the current IEEE802.15.4 standard defines 806MHz, 902MHz, and 2.4GHz as allocations for wireless sensor networks. Therefore, we investigated which frequency band is most applicable for EHR systems. To answer this question, we must understand the properties of electromagnetic waves and their propagation in an urban environment, in other words the RF Link budget in an urban environment must be understood. For RF communication, electromagnetic wave propagation considerations in the presence of natural and man-made structures heavily affects system performance, such as transmission range, and power consumption. Additionally, antenna technology will need to be considered.

There are many radio propagation models for digital wireless communication, such as Longley-Rice model for outdoor, Partition Losses (same floor) for indoor, etct, which provide a link model based on random variables and random processes. Such models allow people to simulate the RF signals on computers to improve the real world network deployments. But this is outside of our research. We are not designing a channel model here and will not discuss it. Instead, we take a measurements-based approach.

In this chapter, four unlicensed-band frequencies were picked in the VHF/UHF spectrum band, 151MHz, 433MHz, 902MHz and 2.4GHz and measured propagation data are reported and compared under two different RF link conditions. A custom 10mW signal source was used as the transmitter, and a spectrum analyzer as the receiver to provide accuracy to within 1dB and sensitivity to better than -120dBm. Both monopole and low-gain directional antennas were employed to represent expected use in an energy harvesting application and the measurement environment included both indoor and outdoor features.

## 3.1 RF Link Budget Factors

The choice of frequency spectrum is a fundamental factor for any radio communication link. Theoretically, an RF communication system can use any ISM (Industrial, Scientific and Medical) frequency for unlicensed applications such as EHR in wireless sensor networks.

However, picking a frequency for a radio system is not merely dependant on the frequency spectrum allocations available. There are several factors that we should consider, which include frequency propagation environment versus transmitting range, antenna size, energy efficiency versus spectrum efficiency, and system complexity. In this section, these factors are considered through an examination of propagation and antenna technology first, then evaluating a RF link budget, and finally considering a radio system's complexity.

### 3.1.1 Propagation

Transmitting range is always a key performance consideration of a wireless communication system. Electromagnetic wave propagation is one of the significant factors affecting transmitting range. An electromagnetic wave has a much more complex structure than many other waves (ex. sound waves) [13], and is described by Maxwell's equations. Maxwell's equations state that a changing magnetic field produces an electric field and a changing electric field produces a magnetic field, which indicates that electromagnetic waves are able to self-propagate [12]. However, the detailed interaction of these waves with the environment, radiation path, and antenna techniques used will all affect the transmitting range.

In free space, the electromagnetic waves are described as spherically propagating outward from the source in all directions. The instantaneous rate of energy flow across a area is P which is represented by Poynting's vector equation (3-1) where E is electric intensity and H is the

$$P = E \times H \tag{3-1}$$

magnetic intensity [13]. Ideally, the power density on the surface of an imaginary sphere can be expressed as equation (3-2) where S is the power density on the surface of the sphere in

$$S = \frac{P}{4\pi d^2} \tag{3-2}$$

watts/m<sup>2</sup>, d is the diameter of sphere in meters, and P is the total transmitted power. Thus the Equ(3-2) shows the power density of the electromagnetic wave is inversely proportional to  $d^2$ . But, in the real world, the electromagnetic waves are not radiating in an ideal free space environment, many different propagation issues occur, such as line-of-sight (LOS) propagation, obstructions, diffraction, refraction, tropospheric and ionospheric propagation. To analyze all those propagation models is beyond the scope of this research. We only consider the simple model of (3-2), and its varients where the propagation exponent is replaced by values up to 3 or 4

to capture such effects. The power at the receiver end may be expressed by equation (3-3), which indicates that the path loss equals the ratio of transmitted power to received power ratio.

$$L_P = \frac{P_T}{P_R} \tag{3-3}$$

The free space path loss (FSPL) is the signal strength loss when the electromagnetic wave radiates in free space. Equation (3-4) shows FSPL with frequency f.

$$L_{FS} = (\frac{4\pi d}{\lambda})^2 = (\frac{4\pi df}{c})^2$$

(3-4)

Here, d is distance between transmitter and receiver,  $\lambda$  is the signal's wave length, f is frequency of operation, and c is speed of light in vacuum (3.0E8 m/sec). This formula indicates the relationship between operation frequency and transmitting range. From (3-4) we see that FSPL is proportional to the square of the operation frequency. In other words, higher operation frequency leads to bigger free space loss, which leads to requirements for higher transmitting power and energy.

#### 3.1.2 Antennas

Antennas are another important factor affecting transmitting range and link budget. It is the interface between air and physical radio systems. For every wireless communication system, antennas must be employed to radiate and receive electromagnetic energy. There are several fundamental concepts of antennas that should be explained so that a RF link budget can be evaluated.

#### 3.1.2.1 Reciprocity

A fundamental principle of antennas, called *reciprocity*, states that antenna performance is the same whether radiation or reception is considered [14]. This principle states that the measurement of antenna parameters, such as gain, and beamwidth, are the same for both transmit and receive.

### 3.1.2.2 Antenna Directivity

In equation (3-2), the assumed radiation of electromagnetic wave has the same power density on all parts of the surface of a sphere. This would be called an isotropic radiator. The

corresponding antenna is called Isotropic Antenna. Real world antennas are not isotropic. They concentrate energy in certain directions. This effect is capture by the concept of antenna gain.

#### 3.1.2.3 Gain

The antenna gain, usually called directivity gain, is defined as the ratio of the radiated power density at distance, d in the direction of maximum intensity, to the average power density over all angles at distance, d [12]. This is expressed by equation (3-5).

$$G = \eta \frac{P_{dirc}}{\frac{P_T}{4\pi d^2}} \tag{3-5}$$

Where  $P_{dirc}$  is the power density at d in maximum direction,  $P_T$  is the power applied to the antenna terminals,  $\eta$  is the total antenna efficiency which accounts for all losses in the antenna (which includes mismatch losses, conduction losses, and dielectric losses [15]). The denominator part is the average power density factor, which is calculated by using ideal isotropic antenna power density equation (3-2).

# 3.1.2.4 Effective Area

The effective area  $A_e$  or is introduced to determine the amount of power  $P_r$  that a receiver intercepts from a signal with power density  $P_{dirc}$  passing its location. Effective area can be defined by (3-6).

$$P_r = P_{dirc} A_e \tag{3-6}$$

where The relationship of effective area and antenna gain is expressed by equation (3-7) where G is antenna gain (not in decibel) and  $\lambda$  is wavelength.

$$A_e = \frac{\lambda^2}{4\pi}G\tag{3-7}$$

#### 3.1.2.5 Antenna Size

The electrical length of a monopole antenna can be determined from basic antenna theory, which says the antenna's length  $\lambda/4$  is inversely proportional to its operating frequency f according to equation (3-8) where c is the speed of light,  $\lambda$  is wavelength and f is the operation frequency.

$$\lambda = \frac{c}{f} \tag{3-8}$$

Obviously, the antenna size is inversely proportional to the operation frequency also.

## 3.1.3 Link Budget

We have explained and reviewed free space RF propagation and basic antenna techniques. It is time to move on into a link budget evaluation. The link planning is an essential part of a wireless communication network deployment, which will help to avoid resource waste, overdesign and poor system performance. A RF link budget is prepared in such a way that accounts for the transmitter radiated power and all of the losses in the link prior to the receiver [16]. It is not including any components of the noise figure, or digital link loss. A simple RF link budget can be expressed as equation (3-9),

$$P_{RX}(dBm) = P_{TX}(dBm) + G(dB) - L(dB)$$

(3-9)

where  $P_{RX}$  is the received power in dBm,  $P_{TX}$  is the transmitted power, G is product of TX and RX gains in the system (antenna gain, etc.), and L is loss (path loss, cable loss, etc.). In the RF link budget, the link margin reflects the robustness of a link, which is expressed by equation (3-10):

$$LinkM \arg in = EIRP - L_{Path} + G_{RX} - TH_{RX}$$

(3-10)

$L_{Path}$  is free space path loss in dB,  $G_{RX}$  is the receive gain in dB,  $TH_{RX}$  is the receiver threshold or the minimum received signal level in dBm. The EIRP is the transmit power plus the transmitter antenna gain, minus any waveguide and random losses [12]. We do not consider any modulation and digitization effects in this RF link margin calculation.

#### 3.1.3.1 Antenna Gain Effects on Link Budget

The free-space path loss is already known from equation (3-4). In RF link budgets, since antenna technology is involved, the Friis transmission equation can be modified to express the path loss with antenna gain in equation (3-11) where  $G_T$  is transmitter antenna gain,  $G_R$  is receiver antenna gain (not in dB).

$$L = \frac{P_T}{P_R} = \frac{1}{G_T G_R} \left(\frac{4\pi d}{\lambda}\right)^2 \tag{3-11}$$

Thus, considering the discussion above about antenna effective area, combining equation (3-6), (3-7) and (3-11), we could rewrite the free space loss as equation (3-12)

$$L = \frac{P_T}{P_R} = \frac{(4\pi d)^2}{G_R G_T \lambda^2} = \frac{(4\pi)^2 d^2 f^2}{G_R G_T c^2}$$

(3-12)

## 3.1.3.2 Link Budget Examples

From the analysis above, we can obtain the following results:

*First*, for a set distance between the transmitter and receiver, since the gains and effective areas are constant, *the path loss is inversely proportional to the operation frequency f*.

Second, from previous antenna parts, we know that *the antenna size will increase with lower operation frequencies*. For example, a half-wave dipole antenna at 3GHz is a manageable 5cm in length, whereas at 300MHz it is 50cm in length. Fortunately, the antenna physical size could be shrunk by using special material [17] or some technique like non-planar rings [18].

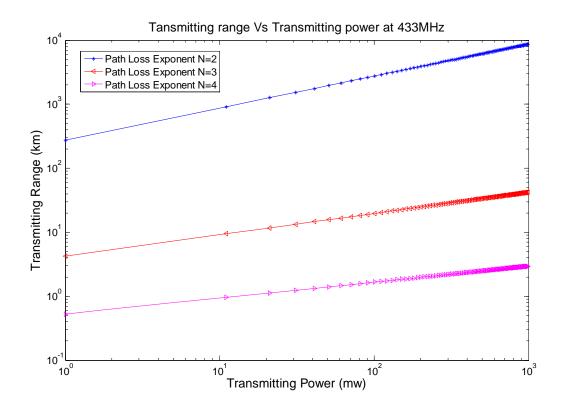

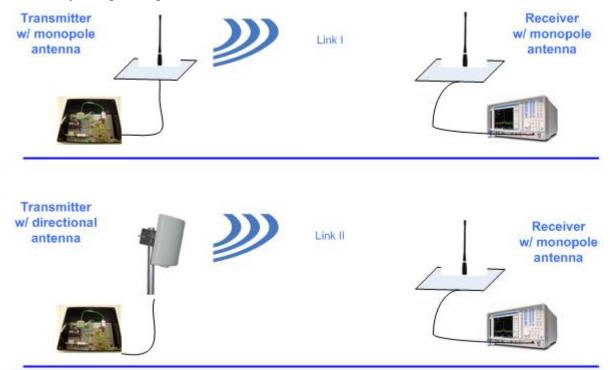

Third, is equation (3-12),  $\mathbf{d}^{\mathbf{N}}$  where  $\mathbf{N}=2$ ,  $\mathbf{N}$  is called the path loss exponent, which is for RF propagation in free space. However, in the real world, there are lots of reflections, diffractions or multipath, and this exponent will vary from 1 to 6 depending on different environments. By using equation (3-11), we can easy calculate the transmitted power versus transmitting range. Assume  $P_R=10P_n$  while  $P_n=kTB$  and the ideal antenna gain  $G_T$  and  $G_R$  are 1, k is 1.38E-23 and T is 290k, T is 1kHz. Figure 3-1 and 3-2 are 433MHz and 2.4GHz plots of transmitting range versus transmit power with 2 to 4 path loss exponents.

Figure 3-1 Calculated range at 433 MHz with dipole antennas and 1 kbps data rate

Figure 3-2 Calculated range at 2.4 GHz with dipole antennas and 1 kbps data rate

## 3.1.4 RF Link Budget and The System Design of EHR

So far, we have shown that lower frequency can transmit further than higher frequency under same power level, when at least one of the antennas used is low-gain. Unfortunately, most commercial WSN products are using the crowed high frequency bands of 800-900MHz, 902-928MHz (Europe), or 2.4-2.5GHz. The main reasons are because these bands are world wide allocation where inexpensive radio transceivers are commercially available and higher data rate can be provided [19]. But the negative aspect of using these frequencies is that the range is fundamentally limited and interference is very serious from higher power transmitting systems, such as WLAN and other fixed transmitters. This is potentially harmful for the power-constrained EHR systems since the lower power sensor nodes are easily affected by stronger signals.

Obviously, there are many techniques which can be used to detect and recover signals within low SNR environment in such crowed frequency bands, such as using MIMO (multiple input and multiple output) antenna systems, using CDMA, FDMA or OFDMA multi-access techniques, or using convolutional codec etc. But, at the same time, these techniques are increasing the complexity, and therefore power consumption of system design. Typically, the complex PHY and MAC layer protocol standards are defined assuming battery powered operation. On the hardware side, to implement these standards, a wide-band RF front-end, a high clock rate FPGA and DSP baseband processor are required. On the software side, a real-time operating system, complex codec algorithms and multi-tasking protocol stacks must be implemented that need be run at higher CPU clock rates to guarantee the wireless communication real-time capabilities.

Thus, EHR system designs must consider the system complexity. We propose to use low data rates along with low RF operation frequency because it leads simple, low complexity implementations, which includes lower power hardware and lower MIPS DSP software design. In the following subsections, four unlicensed VHF/UHF frequencies propagation are measured and compared by using practical equipments and methods. It will give a practical proof of lower frequency's benefit for energy constrained radio systems. In the subsequent chapter, the issues of low-complexity PHY and MAC layer techniques are considered.

# 3.2 UHF/VHF Propagation Comparisons

For this research, we selected frequencies of 151MHz, 433MHz, 902MHz and 2400MHz for several reasons: First, in 2009 significant new spectrum resources will be freed-up in the UHF frequency range in the United States. Around the world, similar and even more dramatic changes are occurring [20]. Second, the 2400MHz and 902MHz are ISM frequency band allocated to IEEE802.15.4 standard, which is widely used standard of wireless sensor networks. 433.92MHz is in an unlicensed band widely used for remote-sensing and RFID applications. In light of these issues and the previous analysis of the relationship between frequency and energy harvesting radio system, we have undertaken a fresh look at which frequencies are most appropriate for energy constrained radio systems.

## 3.2.1 Experimental Setup

## 3.2.1.1 Propagation Links

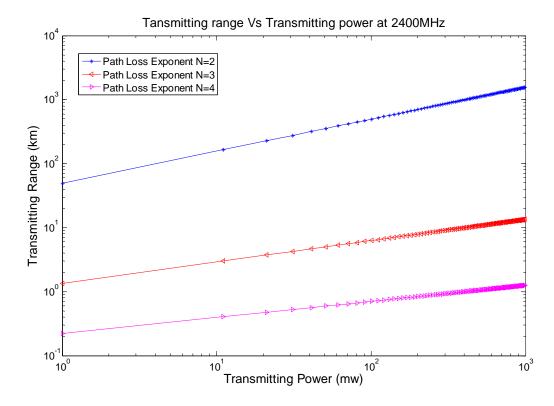

Two different links were measured and compared as shown in Figure 3-3. One link was measured by using monopole antennas at both transmitter and receiver end. The second link was measured by using monopole antenna at receiver end and directional antenna at transmitter end.

Figure 3-3 Two type of experimental Propagation Links

## 3.2.1.2 Experiment Environment

The testing locations were based at Kansas State University and included both indoor and outdoor propagation features. The receiving station was sited indoors, in room RA2097 (2,5 of Figure 3-4), on the 2<sup>nd</sup> floor of the engineering building This building contains four floors and consists of a concrete foundation, concrete wall supports, concrete slab floors with metal supports (3, 6, 7 of Figure 3-4) and dry wall partitions (4 of Figure 3-4). The spaces between floors and walls contain power and cable lines, air conditioning ducts, fire protection sprinklers, and steel piping (3,6,7 of Figure 3-4). Due to its structural makeup, this building serves as a good representative testing environment for construction monitoring applications.

Figure 3-4 Rathbone Hall Engineering Building constructions

For indoor and outdoor measurements, several points at varying transmission radii away from the receiver were selected. Figure 3-5 shows the receiver measurement location mark on the Rathbone Hall  $2^{nd}$  floor plan and the outdoor map.

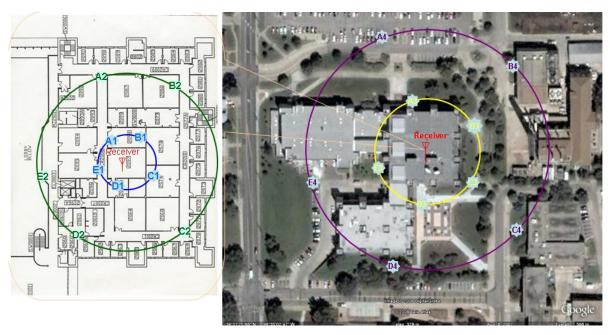

Figure 3-5 Measurements location marked on the indoor floor plan and outdoor map: Left is  $2^{nd}$  floor plan of Rathbone Hall; Right is the Google earth map of Rathbone Hall

The points A to E, five group points, were marked on the map. Each group has 4 points kept in line, to represent a propagation path, for example A1, A2, A3, A4, and A5.

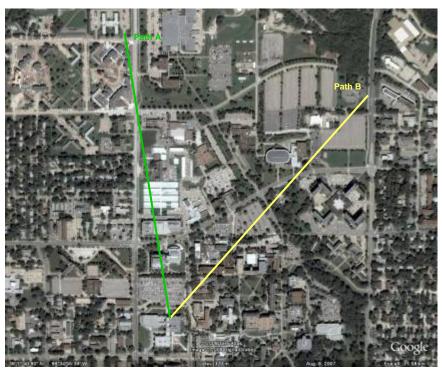

Figure 3-6 Two path used for lower frequency transmitting range measurement

The outdoor measurement paths were located north and northeast of the Ratbone Hall (Figure 3-6) due to the fairly open terrain, but included several obstructions such as buildings and trees. Two similar sized buildings are located north at distances of 0.16km and 0.27km while a taller building is located 0.21km north east.

The area is relatively flat with maximum elevation variations of approximately 10 meters. The path B is higher elevation than path B. Located east of the engineering building is the main campus whose buildings are far more congested.

## 3.2.1.3 Antennas

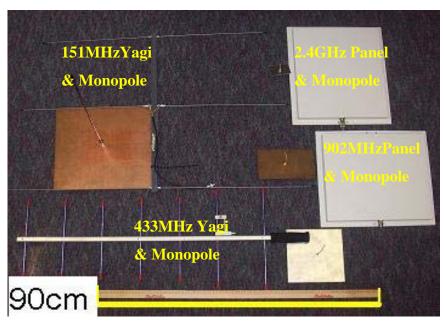

Both directional and non-directional antennas are used for this measurement. For the omni-directional tests, monopole antennas were constructed and used at both ends of the link. The antennas used as directional antennas were commercial panels and Yagis. Figure 3-7 shows antennas pictures used in measurements.

Figure 3-7 Antennas used in measurement

Table 3-1 shows the relationship between the measured frequency, quarter-wave length and the effective aperture of the antennas. For a half-wave length dipole antenna, the effective aperture is calculated by equation (3-6) when G = 1.6 [15].

Table 3-1 quarter-wave antenna size and effective aperture of dipole antenna

| Frequency | Quarter-wave            | Effective Aperture of             |

|-----------|-------------------------|-----------------------------------|

| (MHz)     | Length $\lambda/4$ (cm) | Dipole Antenna (cm <sup>2</sup> ) |

| 151.94 | 49.36 | 3102  |

|--------|-------|-------|

| 433.92 | 17.28 | 380   |

| 902    | 8.31  | 97.92 |

| 2400   | 3.12  | 12.39 |

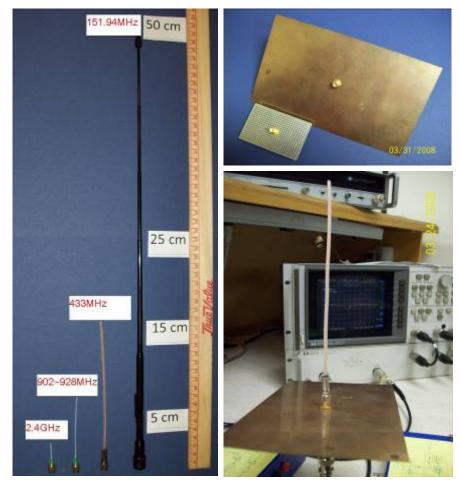

For monopole antenna, truncated ground planes were used. To validate the antenna constructions, reflection coefficients of all antennas were measured prior to use. Figure 3-8 shows the monopole antenna and the ground planes.

Figure 3-8 Monopole antenna, Ground plane and antenna reflection coefficients measurements

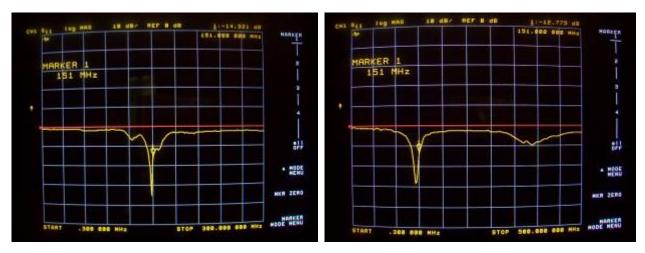

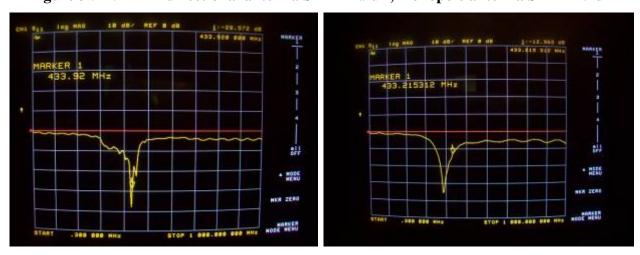

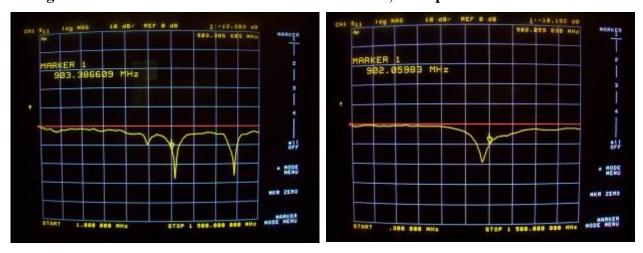

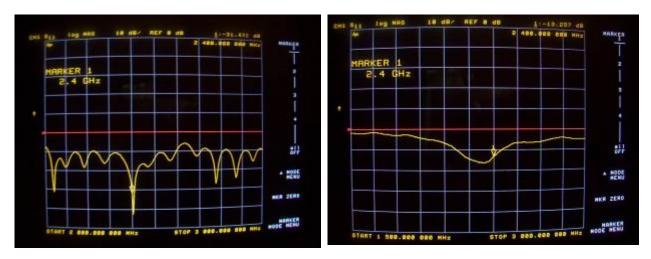

Figures 3-9, 3-10, 3-11 and 3-12 show 151MHz, 433MHz, 902MHz and 2.4GHz directional and monopole antenna reflection coefficient S11 measurement results. The S11 ranged from -15dB to -35dB.

Figure 3-9 151MHz directional antenna S11=-14.9dB, monopole antenna S11=-12.7dB

Figure 3-10 433MHz directional antenna S11=-28dB, monopole antenna S11=-12.9dB

Figure 3-11 902MHz directional antenna S11=-12.5dB, monopole antenna S11=-10dB

Figure 3-12 2400MHz directional antenna S11=-31dB, monopole antenna S11=-13.3dB

# 3.2.1.4 Transmitter and Receiver

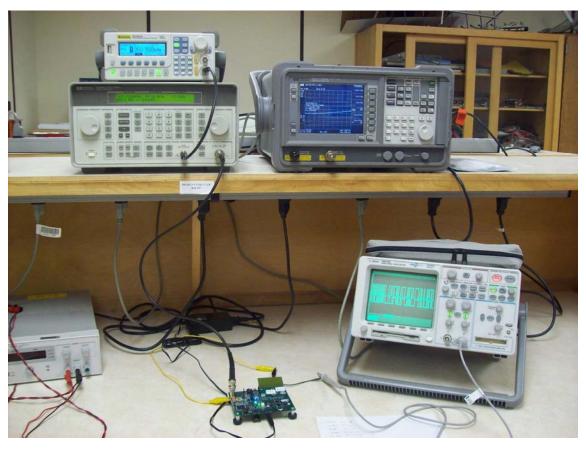

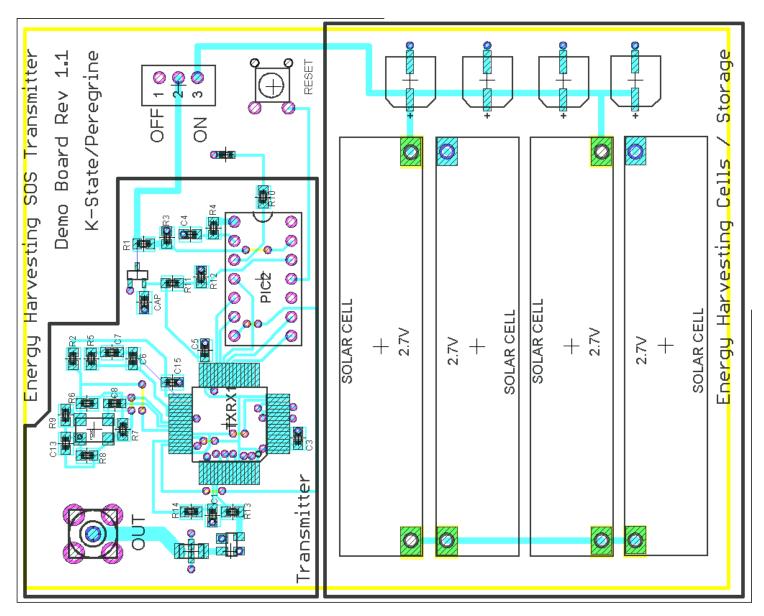

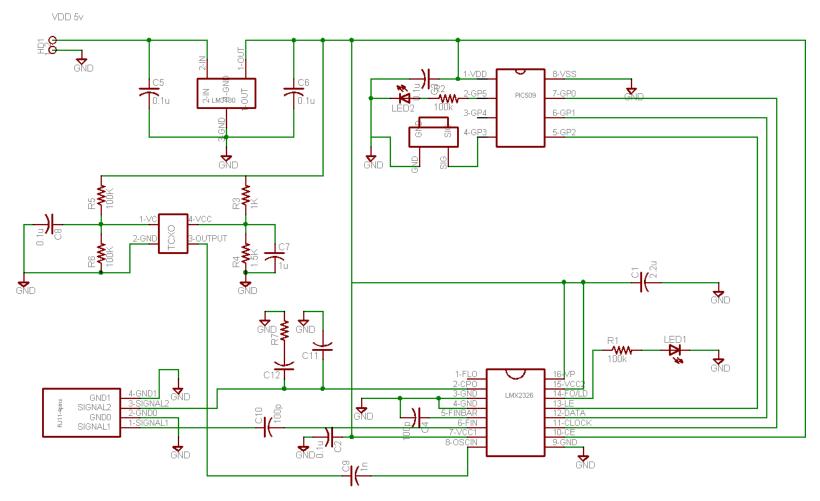

Figure 3-13 Portable 10mW Transmitter photo

The transmitters were designed to output 10mW un-modulated signals and were placed in boxes to make them more potable. The transmitter circuit includes a power supply, frequency

synthesizer board, amplifier, and an output harmonic filter. Figure 3-13 is the transmitter photo. They shared an LMX 2326-based frequency synthesis board, Mini- circuits 15542 power splitter, Mini-Circuit ZX60-33LN-S+ power amplifier, and PIC 12F509 microcontroller hardware. The VCO, Low Pass Filter and Microcontroller software are selected individually for each frequency. **Appendix C** shows the schematic and layout of frequency synthesis board. **Appendix F** provides the software code for the different frequency synthesizer boards. Table3-2 is the components list used to build four frequencies transmitter.

Table 3-2 Components list of 10mW un-modulated transmitter

|                  | VCO                      | LPF                    | AMP     | PW<br>Splitter | Synthesis<br>Chip | TCXO               |

|------------------|--------------------------|------------------------|---------|----------------|-------------------|--------------------|

| 151MHz<br>433MHz | ZX95-148+<br>ZX95-445+   | SLP-200+<br>SLP-450+   | ZX60-   | ZFSC-2-        | LMX2326           | 19.2MHz<br>crystal |

| 902MHz<br>2.4GHz | ZX95-930C+<br>ZX95-2550+ | SLP-1000+<br>SLP-2950+ | 33LN-S+ | 1W-S+          | ENT/X2320         | oscillator         |

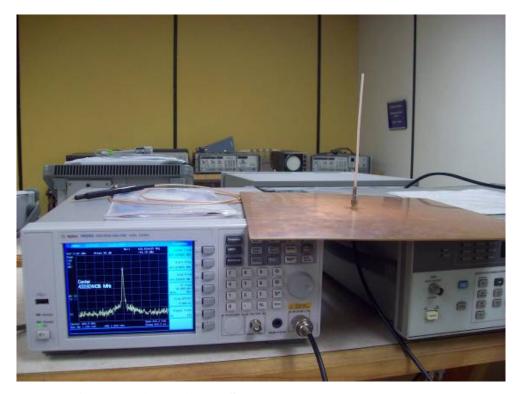

The receiver was an Agilent N9320 spectrum analyzer. The minimum receiver power of this equipment, with the preamp enabled, is lower than -130dBm so that it is adequate. Figure 3-14 is a photo of the receiver with a 433MHz monopole antenna attached. The other frequencies have similar receiver architecture except antenna length.

Figure 3-14 Receiver—Spectrum and monopole antenna

# 3.2.2 Experiment Results

The experiment covered indoor and outdoor environments up to a range of 1.5km. Using room RA2097 as the center location, four circles were scribed with two indoor (7m and 30m) and two outdoor (40m and 90m) radii. Each circle contains five measurement locations (Figure 3-5). Beyond 90 meters, the measurement locations were not fixed.

## 3.2.2.1 Received Signal Strength Measurements at Each Frequency

The propagation measurements for the four frequencies are recorded in Table 3-3, Table 3-4, Table 3-5 and Table 3-6 with both monopole and directional antennas. In the tables, the item Environment indicates indoor or outdoor depending on the location of the transmitter. Item Mark is used to mark the location on the map (Figure 3-5). Item Distance in meters is the range between transmitter and receiver. Item Power(dBm)\_Drc is the received power when the directional antenna is used at the transmitter end. Item Power(dBm)\_Mon is the received power when the monopole antenna is used at the transmitter end.

Table 3-3 151MHz Propagation measurement results

| 151MHz      |                                            |  |  |  |  |

|-------------|--------------------------------------------|--|--|--|--|

| Environment | Environment Mark Distance(m) Power(dBm)_Dr |  |  |  |  |

|         | C2  | 7.74  | 4.4  | 40  |

|---------|-----|-------|------|-----|

|         |     |       | -14  | -13 |

|         | D2  | 7.74  | -13  | -20 |

|         | E2  | 7.74  | -21  | -23 |

|         | A2  | 7.74  | -28  | -24 |

| Indoor  | B2  | 7.74  | -17  | -21 |

| muoor   | С   | 31.3  | -30  | -38 |

|         | D   | 31.3  | -36  | -42 |

|         | E   | 31.3  | -31  | -36 |

|         | Α   | 31.3  | -38  | -44 |

|         | В   | 31.3  | -32  | -40 |

|         | А3  | 43.86 | -63  | -74 |

|         | В3  | 46.36 | -64  | -68 |

|         | C3  | 52.65 | -60  | -74 |

|         | D3  | 41.36 | -45  | -59 |

|         | E3  | 45    | -69  | -61 |

|         | A4  | 85    | -70  | -74 |

|         | B4  | 84    | -79  | -82 |

| Outdoor | C4  | 83    | -72  | -86 |

| Outdoor | D4  | 90    | -85  | -92 |

|         | E4  | 83    | -64  | -82 |

|         | A5  | 129   | -86  | N/A |

|         | A6  | 165   | -86  | N/A |

|         | A7  | 323   | -88  | N/A |

|         | A9  | 1100  | -104 | N/A |

|         | A10 | 1130  | -103 | N/A |

|         | A8  | 1460  | -110 | N/A |

Table 3-4 433MHz Propagation measurement results

|             | 433MHz |             |                |                |  |  |  |  |

|-------------|--------|-------------|----------------|----------------|--|--|--|--|

| Environment | Mark   | Distance(m) | Power(dBm)_Drc | Power(dBm)_Mon |  |  |  |  |

|             | C2     | 7.74        | -19            | -27            |  |  |  |  |

|             | D2     | 7.74        | -22            | -25            |  |  |  |  |

|             | E2     | 7.74        | -29            | -27            |  |  |  |  |

|             | A2     | 7.74        | -22            | -33            |  |  |  |  |

| Indoor      | B2     | 7.74        | -25            | -29            |  |  |  |  |

| ilidool     | С      | 31.3        | -36            | -42            |  |  |  |  |

|             | D      | 31.3        | -43            | -50            |  |  |  |  |

|             | E      | 31.3        | -39            | -42            |  |  |  |  |

|             | Α      | 31.3        | -45            | -54            |  |  |  |  |

|             | В      | 31.3        | -43            | -43            |  |  |  |  |

| Outdoor     | А3     | 43.86       | -64            | -75            |  |  |  |  |

|             | B3     | 46.36       | -65            | -74            |  |  |  |  |

|             | C3     | 52.65       | -65            | -77            |  |  |  |  |

|             | D3     | 41.36       | -52            | -65            |  |  |  |  |

|             | E3     | 45          | -73            | -84            |  |  |  |  |

|             | A4     | 85          | -68            | -80            |  |  |  |  |

|             | B4     | 84          | -70            | -80            |  |  |  |  |

| C4    | 83  | -68  | -77  |

|-------|-----|------|------|

| D4    | 90  | -86  | -96  |

| E4    | 83  | -74  | -85  |

| A5    | 129 | -74  | -83  |

| A6    | 165 | -80  | -89  |

| A7    | 323 | -97  | -95  |

| A433- |     |      |      |

| 8     | 496 | -115 | -120 |

| A433- |     |      |      |

| 9     | 672 | -120 | -122 |

**Table 3-5 902MHz Propagation measurement results**

|             | 900MHz     |             |                |                |  |  |  |

|-------------|------------|-------------|----------------|----------------|--|--|--|

| Environment | Mark       | Distance(m) | Power(dBm)_Drc | Power(dBm)_Mon |  |  |  |

| Indoor      | C2         | 7.74        | -21            | -31            |  |  |  |

|             | D2         | 7.74        | -31            | -35            |  |  |  |

|             | E2         | 7.74        | -29            | -34            |  |  |  |

|             | A2         | 7.74        | -32            | -34            |  |  |  |

|             | B2         | 7.74        | -31            | -36            |  |  |  |

| maddi       | С          | 31.3        | -43            | -49            |  |  |  |

|             | D          | 31.3        | -55            | -58            |  |  |  |

|             | Е          | 31.3        | -41            | -51            |  |  |  |

|             | Α          | 31.3        | -53            | -58            |  |  |  |

|             | В          | 31.3        | -49            | -57            |  |  |  |

|             | A3         | 43.86       | -72            | -85            |  |  |  |

|             | B3         | 46.36       | -63            | -75            |  |  |  |

|             | C3         | 52.65       | -71            | -80            |  |  |  |

|             | D3         | 41.36       | -61            | -75            |  |  |  |

|             | E3         | 45          | -73            | -74            |  |  |  |

|             | A4         | 85          | -78            | -88            |  |  |  |

|             | B4         | 84          | -77            | -90            |  |  |  |

|             | C4         | 83          | -72            | -84            |  |  |  |

| Outdoon     | D4         | 90          | -95            | -97            |  |  |  |

| Outdoor     | E4         | 83          | -71            | -86            |  |  |  |

|             | A5         | 129         | -86            | -99            |  |  |  |

|             | A6         | 165         | -95            | -102           |  |  |  |

|             | A7         | 323         | -109           | -110           |  |  |  |

|             | A900-<br>8 | 353         | -114           | N/A            |  |  |  |

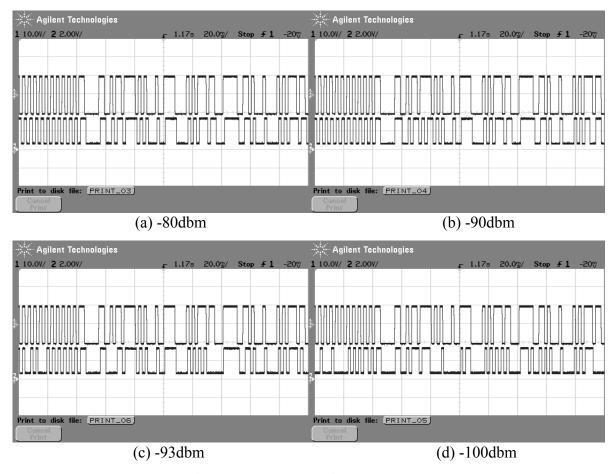

|             | A900-<br>9 | 379         | -110           | N/A            |  |  |  |