# STUDY OF HIGH DIELECTRIC CONSTANT OXIDES ON GAN FOR METAL OXIDE SEMICONDUCTOR DEVICES

by

### **DAMING WEI**

B.S., Dalian University of Technology, 2009

### AN ABSTRACT OF A DISSERTATION

submitted in partial fulfillment of the requirements for the degree

DOCTOR OF PHILOSOPHY

Department of Chemical Engineering College of Engineering

KANSAS STATE UNIVERSITY Manhattan, Kansas

2014

### **Abstract**

Gallium nitride is a promising semiconductor for fabricating field effect transistors for power electronics because of its unique physical properties of wide energy band gap, high electron saturation velocity, high breakdown field and high thermal conductivity. However, these devices are extremely sensitive to the gate leakage current which reduces the breakdown voltage and the power-added efficiency and increases the noise figures. To solve this problem, employing a gate dielectric is crucial to the fabrication of metal insulator semiconductor high electron mobility transistors (MISHEMTs), to reduce the leakage current and increase the magnitude of voltage swings possible. For this device to be successful, imperfections at the oxide-semiconductor interface must be suppressed to maintain the high electron mobility of the device.

This research explored multiple high dielectric constant gate oxides (Al<sub>2</sub>O<sub>3</sub>, TiO<sub>2</sub>, and Ga<sub>2</sub>O<sub>3</sub>), deposited on different crystalline orientations and polarities of GaN by atomic layer deposition (ALD) to form metal oxide semiconductor capacitors, including effects of pretreatment on N-polar GaN, ALD TiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> nano-laminate on thermal oxidized Ga-polar GaN and ALD Al<sub>2</sub>O<sub>3</sub> on *c*- and *m*-plane GaN Surface pretreatments were shown to greatly alter the morphology of reactive N-polar GaN which is detrimental to the electrical properties. 14 nm thick ALD Al<sub>2</sub>O<sub>3</sub> films were directly deposited on N-polar GaN without thermal or chemical pretreatments which yield a smooth surface (RMS=0.23 nm), low leakage current (2.09 x 10<sup>-8</sup> A/cm<sup>2</sup>) and good Al<sub>2</sub>O<sub>3</sub>/GaN interface quality, as indicated by the low electron trap density (2.47 x 10<sup>10</sup> cm<sup>-2</sup>eV<sup>-1</sup>). In the nano-laminate study, a high dielectric constant of 12.5 was achieved by integrating a TiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> oxide stack layer, while maintaining a low interface trap density and low leakage current. There was a strong correlation between the surface morphology and electrical properties of the device discovered from comparing the ALD Al<sub>2</sub>O<sub>3</sub> on *c*- and *m*-plane GaN, namely smooth surface lead to small hysteresis. These results indicate the promising potential of incorporation gate dielectric for future GaN devices.

# STUDY OF HIGH DIELECTRIC CONSTANT OXIDES ON GAN FOR METAL OXIDE SEMICONDUCTOR DEVICES

by

### **DAMING WEI**

B.S., Dalian University of Technology, 2009

### A DISSERTATION

submitted in partial fulfillment of the requirements for the degree

### DOCTOR OF PHILOSOPHY

Department of Chemical Engineering College of Engineering

KANSAS STATE UNIVERSITY Manhattan, Kansas

2014

Approved by:

Major Professor Dr. James H. Edgar

# Copyright

DAMING WEI 2014

### **Abstract**

Gallium nitride is a promising semiconductor for fabricating field effect transistors for power electronics because of its unique physical properties of wide energy band gap, high electron saturation velocity, high breakdown field and high thermal conductivity. However, these devices are extremely sensitive to the gate leakage current which reduces the breakdown voltage and the power-added efficiency and increases the noise figures. To solve this problem, employing a gate dielectric is crucial to the fabrication of metal insulator semiconductor high electron mobility transistors (MISHEMTs), to reduce the leakage current and increase the magnitude of voltage swings possible. For this device to be successful, imperfections at the oxide-semiconductor interface must be suppressed to maintain the high electron mobility of the device.

This research explored multiple high dielectric constant gate oxides (Al<sub>2</sub>O<sub>3</sub>, TiO<sub>2</sub>, and Ga<sub>2</sub>O<sub>3</sub>), deposited on different crystalline orientations and polarities of GaN by atomic layer deposition (ALD) to form metal oxide semiconductor capacitors, including effects of pretreatment on N-polar GaN, ALD TiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> nano-laminate on thermal oxidized Ga-polar GaN and ALD Al<sub>2</sub>O<sub>3</sub> on *c*- and *m*-plane GaN Surface pretreatments were shown to greatly alter the morphology of reactive N-polar GaN which is detrimental to the electrical properties. 14 nm thick ALD Al<sub>2</sub>O<sub>3</sub> films were directly deposited on N-polar GaN without thermal or chemical pretreatments which yield a smooth surface (RMS=0.23 nm), low leakage current (2.09 x 10<sup>-8</sup> A/cm<sup>2</sup>) and good Al<sub>2</sub>O<sub>3</sub>/GaN interface quality, as indicated by the low electron trap density (2.47 x 10<sup>10</sup> cm<sup>-2</sup>eV<sup>-1</sup>). In the nano-laminate study, a high dielectric constant of 12.5 was achieved by integrating a TiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> oxide stack layer, while maintaining a low interface trap density and low leakage current. There was a strong correlation between the surface morphology and electrical properties of the device discovered from comparing the ALD Al<sub>2</sub>O<sub>3</sub> on *c*- and *m*-plane GaN, namely smooth surface lead to small hysteresis. These results indicate the promising potential of incorporation gate dielectric for future GaN devices.

# **Table of Contents**

| List of Figures                                                           | ix  |

|---------------------------------------------------------------------------|-----|

| List of Tables                                                            | xiv |

| Acknowledgements                                                          | XV  |

| Dedication                                                                | xvi |

| Chapter 1 - Introduction                                                  | 1   |

| Prologue to the thesis                                                    | 1   |

| Introduction of power electronics:                                        | 1   |

| Reference                                                                 | 7   |

| Chapter 2 - Review of High-k Dielectrics on GaN                           | 9   |

| Introduction of high-k oxides                                             | 9   |

| Al <sub>2</sub> O <sub>3</sub> as gate dielectric on GaN based transistor | 9   |

| HfO <sub>2</sub> as gate dielectric on GaN transistor                     | 10  |

| Ga <sub>2</sub> O <sub>3</sub> as gate dielectric on GaN transistor       | 11  |

| Other oxides as Gate dielectric                                           | 14  |

| Summary                                                                   | 16  |

| Reference                                                                 |     |

| Chapter 3 - Device Fabrication                                            | 22  |

| Growth of bulk GaN                                                        | 22  |

| GaN thin film growth                                                      | 23  |

| MOCVD                                                                     | 24  |

| MBE                                                                       | 25  |

| Gate dielectric deposition                                                | 26  |

| ALD                                                                       | 27  |

| Thermal ALD                                                               | 28  |

| Plasma assisted ALD (PA-ALD)                                              | 28  |

| Metal contacts                                                            | 28  |

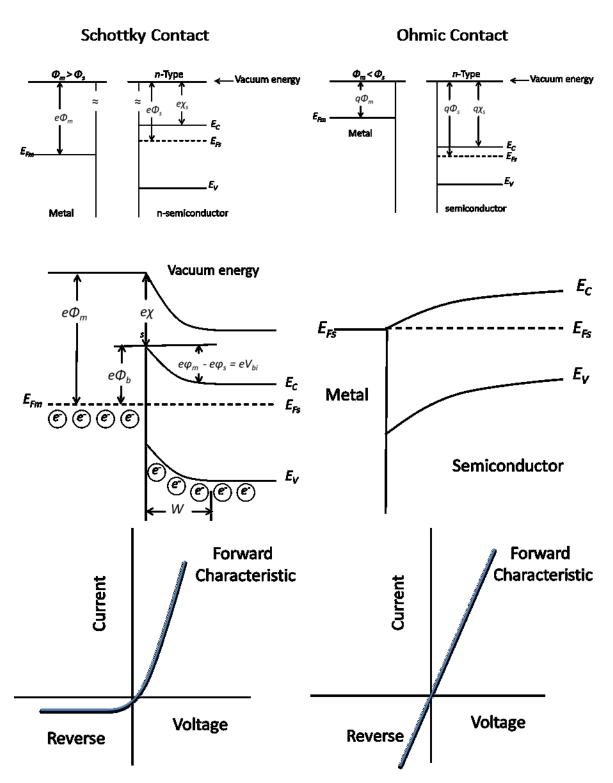

| Schottky contact                                                          | 28  |

| Ohmic contact                                                             | 29  |

| Metal contacts deposition                                                       | 31               |

|---------------------------------------------------------------------------------|------------------|

| Lithography                                                                     | 32               |

| Etching                                                                         | 32               |

| References                                                                      | 34               |

| Chapter 4 - Device Characterization                                             | 37               |

| Microscopy                                                                      | 37               |

| Optical Microscopy                                                              | 37               |

| Scanning Electron Microscopy (SEM)                                              | 38               |

| Atomic Force Microscopy (AFM)                                                   | 39               |

| X-ray Diffraction (XRD)                                                         | 40               |

| X-ray photoelectron spectroscopy (XPS)                                          | 40               |

| Electrical characterization.                                                    | 41               |

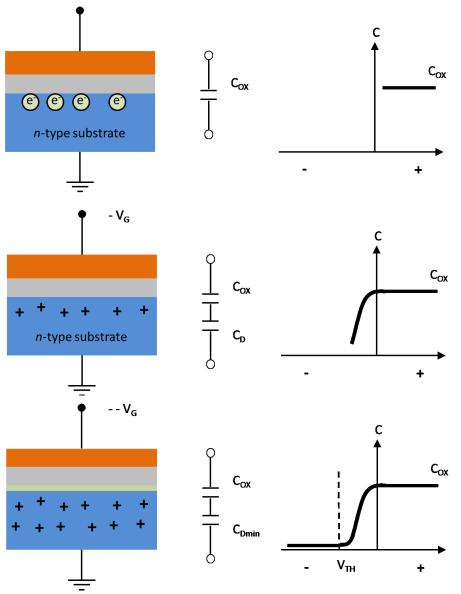

| Capacitance voltage (CV)                                                        | 41               |

| References                                                                      | 45               |

| Chapter 5 - Influence of Atomic Layer Deposition Temperatures on $TiO_2/n$ -Si  | MOS Capacitor 46 |

| Abstract                                                                        | 46               |

| Introduction                                                                    | 47               |

| Experimental Procedure                                                          | 47               |

| A. TiO <sub>2</sub> ALD Film Growth and Metal Contact Deposition                | 47               |

| B. TiO <sub>2</sub> Film Characterization                                       | 48               |

| Results and Discussion                                                          | 49               |

| Conclusion                                                                      | 58               |

| Acknowledgements                                                                | 59               |

| References                                                                      | 60               |

| Chapter 6 - Effects of surface pretreatments on N-polar GaN for atomic layer of | deposition of    |

| $Al_2O_3$                                                                       | 62               |

| Abstract                                                                        | 62               |

| Introduction                                                                    | 63               |

| Experimental procedures                                                         | 64               |

| MOS capacitor fabrication                                                       | 64               |

| High-k film and device characterization                                         | 65               |

| Results and discussion                                                                                                  | 66                |

|-------------------------------------------------------------------------------------------------------------------------|-------------------|

| Transformation of surface morphology by AFM Observation                                                                 | 66                |

| C-V and I-V measurements for Al <sub>2</sub> O <sub>3</sub> on GaN MOSCAPs                                              | 70                |

| Conclusion                                                                                                              | 75                |

| Acknowledgement                                                                                                         | 76                |

| References                                                                                                              | 77                |

| Chapter 7 - Characterization of ALD TiO <sub>2</sub> -Al <sub>2</sub> O <sub>3</sub> Laminated Gate Dielectrics on Ga-p | oolar GaN         |

| MOSCAPs                                                                                                                 | 80                |

| Abstract                                                                                                                | 80                |

| Introduction                                                                                                            | 81                |

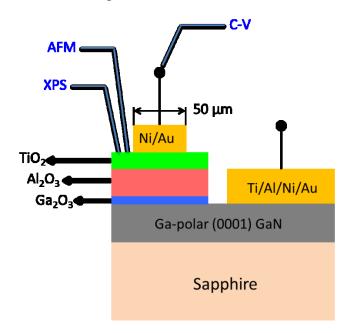

| Experiment                                                                                                              | 81                |

| Results and Discussion                                                                                                  | 83                |

| Conclusion                                                                                                              | 88                |

| Acknowledgement                                                                                                         | 88                |

| References                                                                                                              | 89                |

| Chapter 8 - Comparison of the physical, chemical and electrical properties of ALD A                                     | $l_2O_3$ on $c$ - |

| and m-plane GaN                                                                                                         | 91                |

| Abstract                                                                                                                | 91                |

| Introduction                                                                                                            | 92                |

| Experiments                                                                                                             | 92                |

| Results and discussion                                                                                                  | 93                |

| Conclusion                                                                                                              | 97                |

| Acknowledgements                                                                                                        | 97                |

| References                                                                                                              | 98                |

| Chapter 9 - Conclusions and Future work                                                                                 | 99                |

| Conclusions                                                                                                             | 99                |

| Future work                                                                                                             | 100               |

| Appendix A - Process flow of GaN MOS capacitor with top to bottom contact                                               | 101               |

# **List of Figures**

| Figure 1.1 Schematic picture of power electronic system <sup>2</sup> . The source energy is converted to              |     |

|-----------------------------------------------------------------------------------------------------------------------|-----|

| serve an electrical load.                                                                                             | . 1 |

| Figure 1.2 Schematic picture of a generic MOSFET                                                                      | . 3 |

| Figure 1.3 Crystal structure of wurtzite GaN. <sup>24</sup>                                                           | 4   |

| Figure 1.4 Structure of AlGaN/GaN HEMT (left) and MOSHEMT (right)                                                     | 5   |

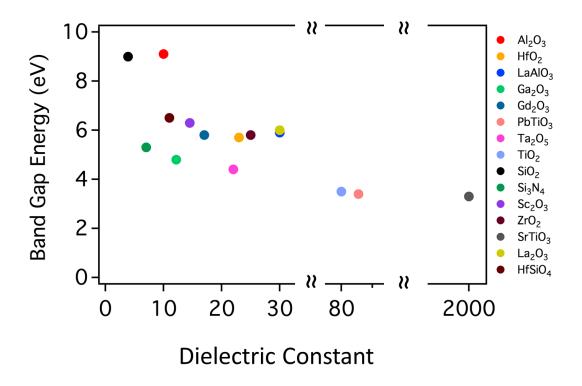

| Figure 2.1 SEM images of Ga <sub>2</sub> O <sub>3</sub> surfaces form at different temperatures (a) 850°C, (b) 900°C, |     |

| (c) 950°C, (d) 1000°C. 46                                                                                             | 13  |

| Figure 2.2 SEM images of the underlying GaN surface after the Ga <sub>2</sub> O <sub>3</sub> layer was removed. The   |     |

| original oxidation temperatures were: (a) 850°C, (b) 900°C, (c) 950°C (d) 1000°C all for 6 h                          | ır. |

| 46                                                                                                                    | 13  |

| Figure 2.3 The unit cell of BaTiO <sub>4</sub> . The displacement of the cation lattice with respect to the           |     |

| anion lattice induces a static dipole moment and thus, a spontaneous polarization in the                              |     |

| perovskite crystal.                                                                                                   | 15  |

| Figure 2.4 Distribution of the high-k dielectrics and their band gap.                                                 | 16  |

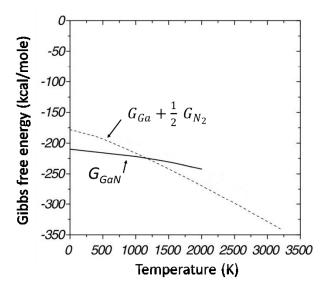

| Figure 3.1 Gibbs free energy of 1 mole GaN and the (Ga + 12 N <sub>2</sub> ) system as a function of the              |     |

| temperature at the pressure of 1 bar. <sup>7</sup>                                                                    | 23  |

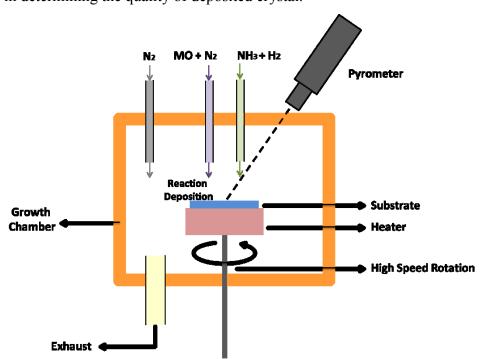

| Figure 3.2 Schematic diagram of a MOCVD reaction system.                                                              | 24  |

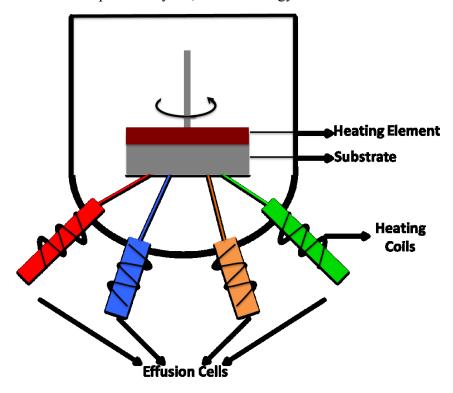

| Figure 3.3 Schematic picture of MEB reaction system                                                                   | 26  |

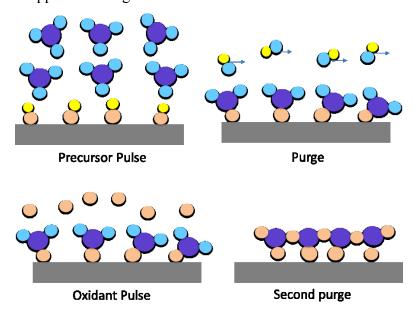

| Figure 3.4 Schematic picture of one cycle ALD processing                                                              | 27  |

| Figure 3.5 (a) Schottky contact of metal and n-type semiconductor junction (b) Ohmic contact of                       | of  |

| metal and n-type semiconductor junction. <sup>51</sup>                                                                | 30  |

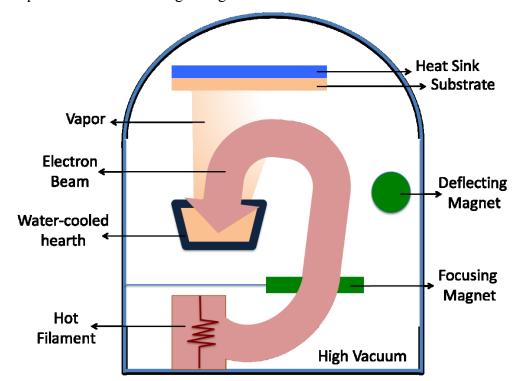

| Figure 3.6 Schematic diagram of an e-beam evaporation system.                                                         | 31  |

| Figure 4.1 MOS capacitor structure with the equivalent circuit and its operation at (a)                               |     |

| accumulation region, (b) depletion region, (c) inversion region. 10                                                   | 12  |

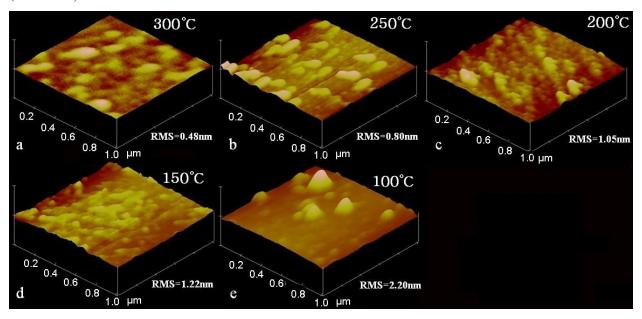

| Figure 5.1 Three-dimensional AFM images of TiO <sub>2</sub> on Si deposited at different ALD                          |     |

| temperatures. The Z height is 30nm for all images. (a) 300°C (RMS=0.48 nm), (b) 250°C                                 |     |

| (RMS=0.80 nm), (c) 200°C (RMS=1.05 nm), (d) 150°C (RMS=1.22 nm), and (e) 100°C                                        |     |

| (RMS=2.202 nm).                                                                                                       | 19  |

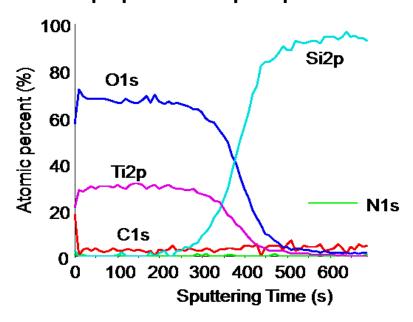

| Figure 5.2 (a) XPS depth profile of sample deposited at 300°C. (The shape of the depth profiles            |

|------------------------------------------------------------------------------------------------------------|

| is similar for all the samples. Only one is demonstrated.) (b) XPS depth profile of Ti2p at                |

| different sputtering times. The 2p3 of Ti <sup>4+</sup> and metallic Ti peaks are 458.5eV at 0 seconds     |

| and 454.2eV at 510 seconds.                                                                                |

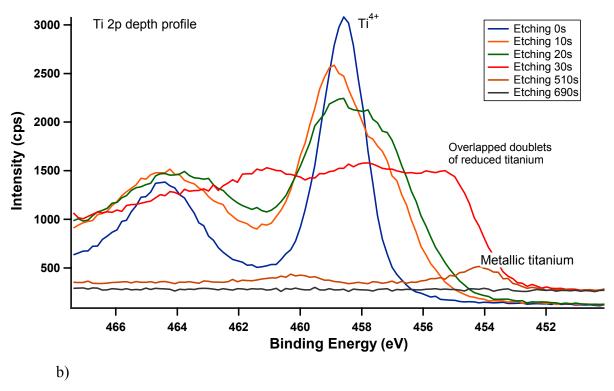

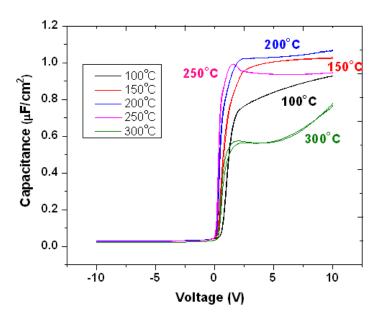

| Figure 5.3 (Left axis) Average atomic carbon concentration in the TiO <sub>2</sub> layers versus ALD       |

| temperature. (Right axis) Sputtering time to remove the oxide layer and expose the Si                      |

| substrate versus ALD deposition temperature.                                                               |

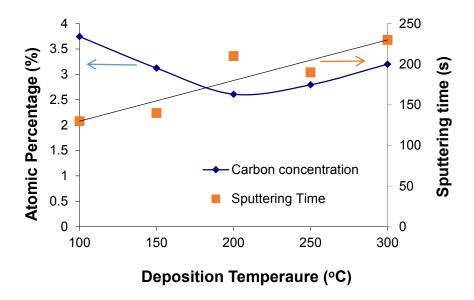

| Figure 5.4 C-V measurement for TiO <sub>2</sub> /Si MOS capacitors at different ALD temperatures           |

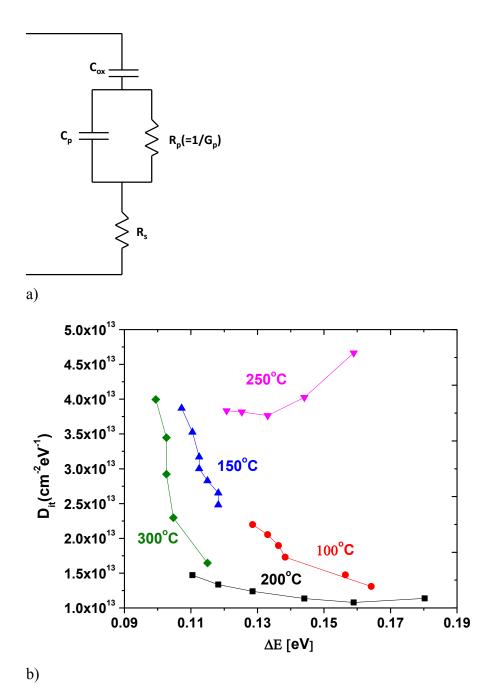

| Figure 5.5 (a) Simplified circuit of MOS capacitor including series resistance. (b) Interface trap         |

| density distributions of ALD samples at different deposition temperatures                                  |

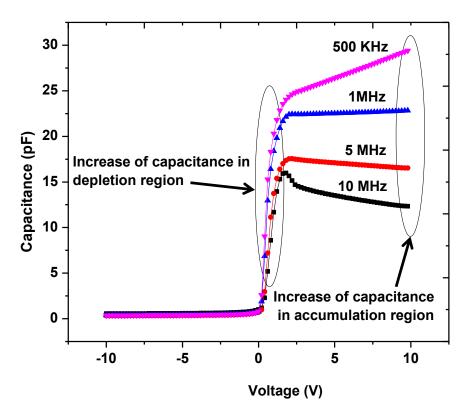

| Figure 5.6 Measured capacitance vs gate voltage as a function of frequency for the TiO <sub>2</sub> /Si at |

| 200°C deposition temperature.                                                                              |

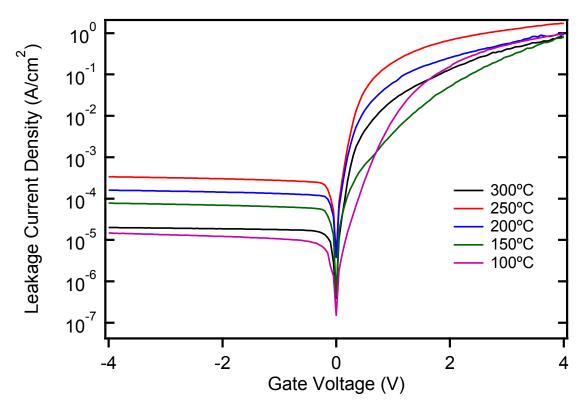

| Figure 5.7 I–V characteristics of TiO <sub>2</sub> /Si MOS capacitor at different ALD temperatures         |

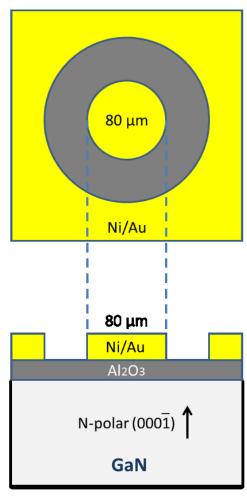

| Figure 6.1 Schematic illustration of the N-polar GaN MOS capacitor with a top view (upper) an              |

| a side view (lower)6                                                                                       |

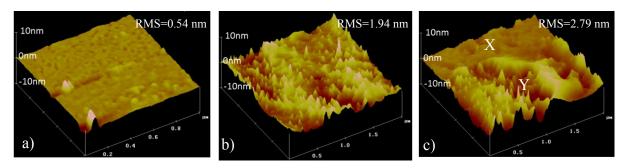

| Figure 6.2 Three dimensional AFM pictures of the N-polar GaN surface morphologies of sample                |

| with a) no etching b) 30 min etching c) 5 min etching. The examined area was 1 x 1 μm² fo                  |

| the not etched sample and 2 x 2 $\mu m^2$ for two etched samples all with the Z-height of 20nm.            |

| The RMS roughness of surfaces were 0.54, 1.94 and 2.79 nm respectively                                     |

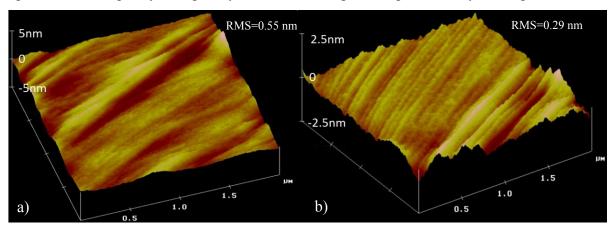

| Figure 6.3 Three dimensional AFM picture of a) 30 min etched sample; b) 5 min etched sample                |

| after epitaxial growth of 100nm GaN.                                                                       |

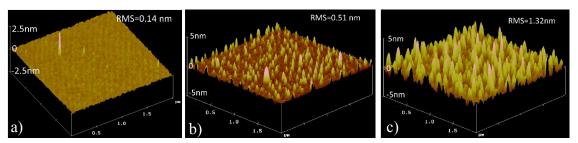

| Figure 6.4 Three dimensional AFM pictures of sample (a) before oxidation, (b) oxidized at                  |

| 800°C and (c) oxidized at 850°C                                                                            |

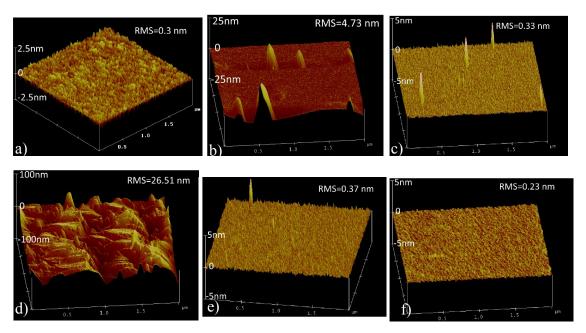

| Figure 6.5 Three dimensional AFM images of N-polar GaN a) before ALD and after ALD                         |

| pretreated with b) HCl, c) HF, d) Base piranha, e) H2 plasma, f) No pretreatment                           |

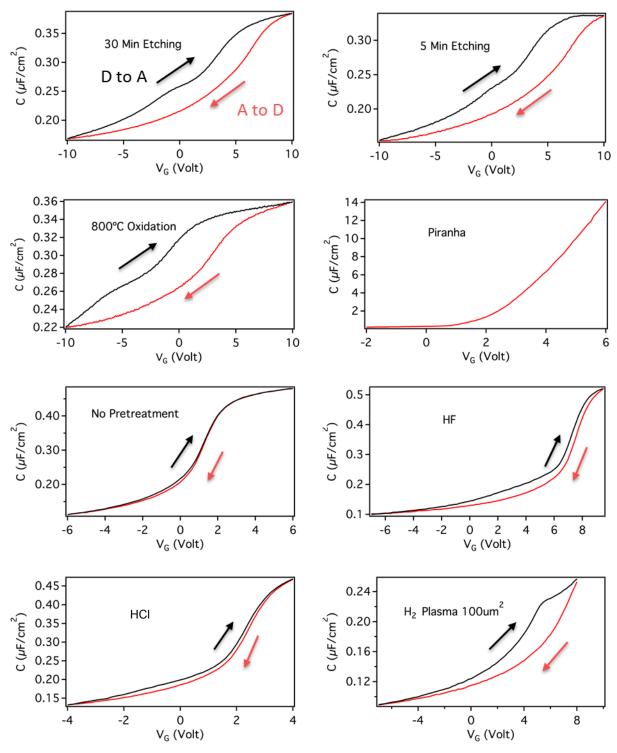

| Figure 6.6 C-V sweeps from accumulation to depletion (red) and from depletion to accumulatio               |

| (black) for samples with different pretreatment methods.                                                   |

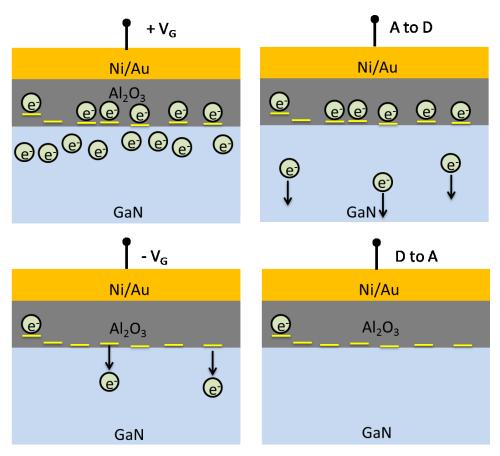

| Figure 6.7 Schematic picture of electron motion in a single loop of C-V sweeps with the respect            |

| of oxide traps. <sup>19</sup>                                                                              |

| Figure 7.1 Schematic picture of GaN MOSCAP with nano-laminate gate dielectrics                             |

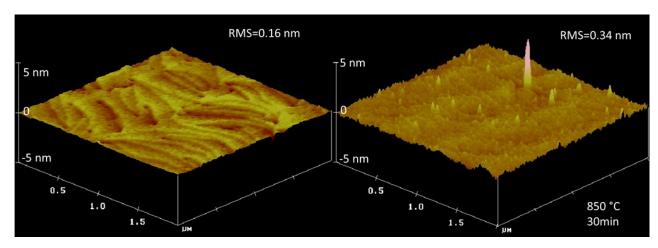

| Figure 7.2 Three dimensional AFM image of (a) Ga-polar GaN surface; (b) Ga <sub>2</sub> O <sub>3</sub> after thermal |

|----------------------------------------------------------------------------------------------------------------------|

| oxidation of 850°C for 30 min. The scanned areas were 2 $\times$ 2 $\mu$ ms with the Z scale of 10nm.                |

| 84                                                                                                                   |

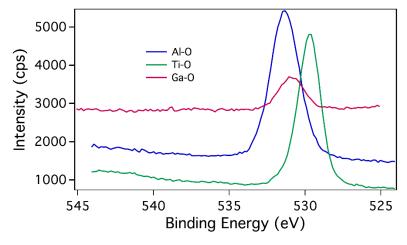

| Figure 7.3 XPS spectrum of O 1s binding with Ti, Al and Ga                                                           |

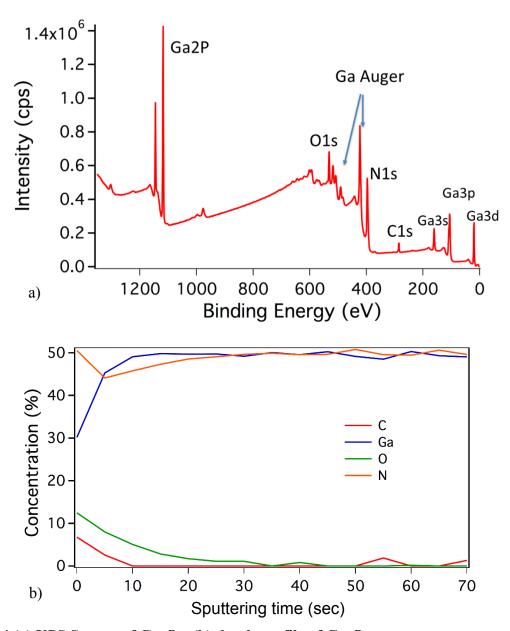

| Figure 7.4 (a) XPS Survey of Ga <sub>2</sub> O <sub>3</sub> ; (b) depth profile of Ga <sub>2</sub> O <sub>3</sub>    |

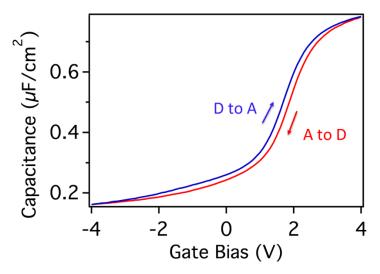

| Figure 7.5 Hysteresis sweep of the GaN MOSCAP at room temperature                                                    |

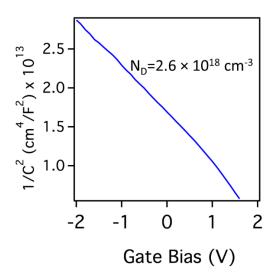

| Figure 7.6 $1/C^2$ curve vs. the applied gate voltage in the depletion and depletion region. The GaN                 |

| electron concentration was calculated to be $2.6 \times 10^{18}$ cm <sup>-3</sup>                                    |

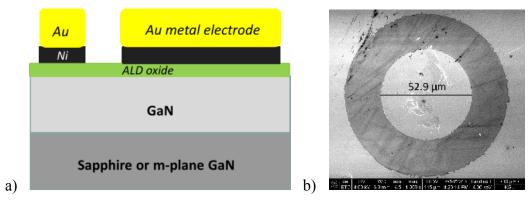

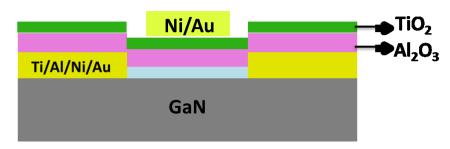

| Figure 8.1 a) Schematic structure of the side view of the MOSCAP. b) Scanning electron                               |

| microscopy (SEM) top view of the MOSCAP with the diameter of 52.9 μm                                                 |

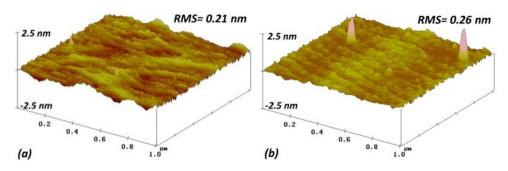

| Figure 8.2 Three-dimensional AFM images of $Al_2O_3$ on (a) $c$ -plane and (b) $m$ -plane GaN. The $Z$               |

| height is 5 nm and scan area is $1 \times 1$ square micron for both images                                           |

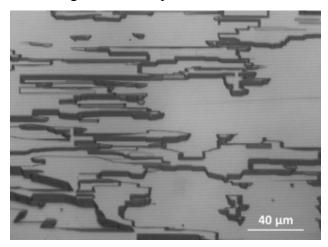

| Figure 8.3 Optical microscopic image of the m-plane GaN surface. The morphology is a                                 |

| consequence of the epitaxial growth                                                                                  |

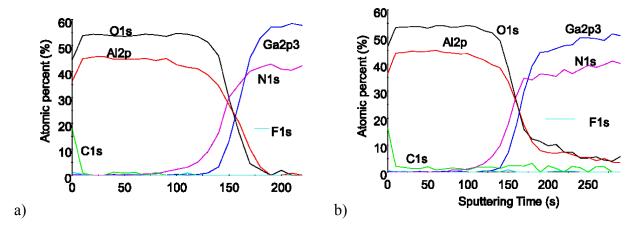

| Figure 8.4 XPS depth profile of Al <sub>2</sub> O <sub>3</sub> on a) <i>c</i> - and b) <i>m</i> -plane GaN           |

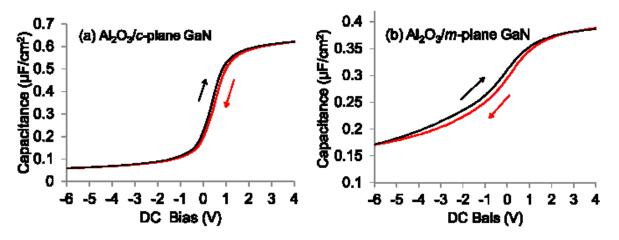

| Figure 8.5 C-V measurements of the MOSCAPs on (a) $c$ - and (b) $m$ -plane GaN at 20 $^{\circ}$ C 95                 |

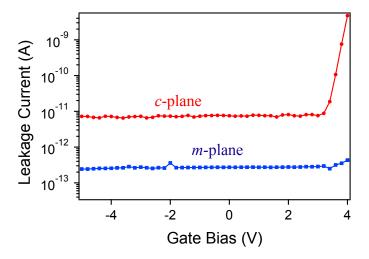

| Figure 8.6 I-V measurement of the MOSCAPs on <i>c</i> - and <i>m</i> -plane GaN                                      |

| Figure A.1 Photoresist (PR) spin coating on Ga <sub>2</sub> O <sub>3</sub> /GaN/Sapphire 2-inch wafer. P20 was spin  |

| coated first as a primer which improves the adhesion of the PR to the surface, followed by                           |

| the 955-2 $\mu m$ positive photoresist. 3000 rpm spin rate was applied to both chemicals, and a                      |

| pre-exposure baking of 90 °C for 90 sec was conducted to reduce the solvent concentration                            |

| in the PR. This prevents the PR sticking to the mask and improves the resist adhesion 101                            |

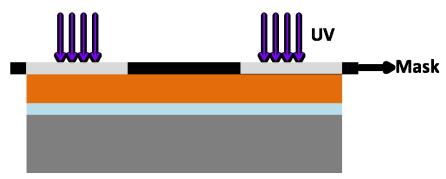

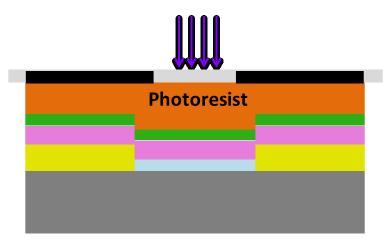

| Figure A.2 Ultra-violet light exposure for 3 sec. A post exposure bake at 115°C for 90 sec was                       |

| applied to further harden the PR and improving the adhesion                                                          |

| Figure A.3 Develop the exposed PR in CD-26 for 75 sec. The exposed PR turns into clouds in                           |

| CD-26. Rule of thumb of a good development is visually observe the disappearance of                                  |

| clouds and wait for additional 10 sec. Wafer will subsequently rinsed by DI water and                                |

| characterized under optical microscope for the quality of development. Surface profilometer                          |

| was used to monitor the thickness of PR                                                                              |

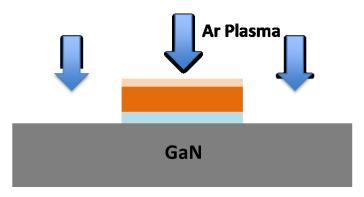

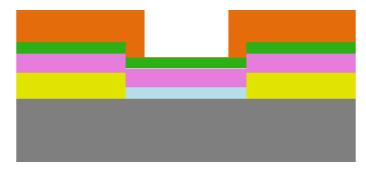

| Figure A.4 Reactive ion etching (RIE). Etching process is very sensitive to the chamber                              |

| condition. A 10 min pre-clean of RIE chamber was applied before loading the wafer. The                               |

| exposed Ga <sub>2</sub> O <sub>3</sub> on the surface of the water was etched by Ar ion with an RF generation    |

|------------------------------------------------------------------------------------------------------------------|

| power of 2500 W and DC bias of 50 W. This is a combination of descum PR and device                               |

| feature developing. A 20 sec sputtering removes surface contamination, and improves the                          |

| adhesion for Ohmic contact metal deposition                                                                      |

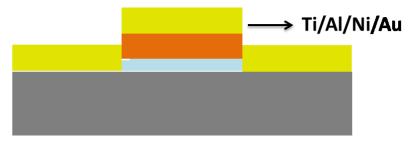

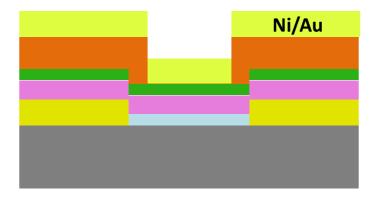

| Figure A.5 Metal deposition to form Ohmic contact. Metal stack of Ti/Al/Ni/Au was evaporated                     |

| in order by electron beam evaporation. The thickness of each layer is 25/20/40/50 nm. The                        |

| first Ti layer reacts with N in GaN forming TiN which has low band offset with GaN.                              |

| Meanwhile the N vacancy increase the conductivity of GaN. Al and Ni prevent the diffusion                        |

| of Ti and Au respectively. Also, 40 nm of Ni provide better adhesion for Au layer 102                            |

| Figure A.6 Liftoff. Wafer was immersed in an acetone and sonicated for 5mins in the dirty                        |

| slurry, followed by another 5mins sonication in the clean bath                                                   |

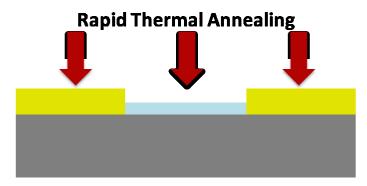

| Figure A.7 Rapid thermal processing (RTP). The metal stack needs to be annealed to decrease                      |

| the resistivity. RTP was ramped to 400°C within 20 sec and wafer was soaked for 3 min to                         |

| let the heat evenly distribute across the wafer. Then, the system temperature was increased                      |

| to 800°C within 40 sec and maintain 800°C for 25 sec. The whole thermal process was                              |

| under N <sub>2</sub> atmosphere. 103                                                                             |

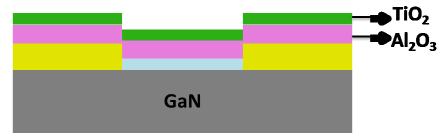

| Figure A.8 ALD of high-k oxides. The cycle of Al <sub>2</sub> O <sub>3</sub> includes 30 ms TMA dose followed by |

| 1500 ms Ar purge; and 2000ms O2 plasma dose followed by 800 ms post plasma. This                                 |

| yields 1.35 Å per cycle. Then TiO2 was deposited on top of Al2O3 with the recipe of 1000                         |

| TTIP dose followed by 3000ms Ar purge and 3000ms $\mathrm{O}_2$ plasma dose followed by 2000 ms                  |

| Ar purge. This yields of 0.43 Å per cycle. The thickness of both oxide was characterized to                      |

| be 7.1 nm and 5.1 nm on Si witness wafer under ellipsometry                                                      |

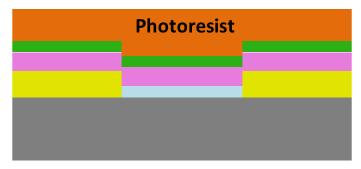

| Figure A.9 PR spin coating. The thickness of PR is $0.7~\mu m$ with a recipe of P20 as the primer and            |

| 955-0.7 at the PR. The spin rate was 4000rpm for 45 sec                                                          |

| Figure A.10 Mask alignment and Exposure. The alignment mark was adjusted under microscope                        |

| before a 5-seconds exposure. 104                                                                                 |

| Figure A.11 Develop the pattern in CD-26 for 1 min. The quality of the photolithography was                      |

| monitor under the microscope and the thickness of PR was measured by surface                                     |

| profilometer 104                                                                                                 |

| Figure A.12 Ni/Au (20/40 nm) was evaporated in order to form the gate contact                                    |

| Figure A.13 Liftoff. Wafer was immersed in the acetone bath and sonicated for 5 min then  |     |

|-------------------------------------------------------------------------------------------|-----|

| transferred to clean acetone bath for another 5 min sonication. Finally, wafer was rinsed | by  |

| IPA, DI water and air dry to get rid of the liftoff metal particles on the surface        | 105 |

# **List of Tables**

| Table 1.1 Physical properties of common semiconductor materials. GaN has superior saturated                    |

|----------------------------------------------------------------------------------------------------------------|

| electron velocity and breakdown field comparing to other semiconductors. 18                                    |

| Table 2.1 Summary of the reviewed oxides and their properties including band gap, dielectric                   |

| constant and band offset with GaN                                                                              |

| Table 5.1 Oxygen and titanium ratio, average carbon concentration, thickness, dielectric constant              |

| of TiO2 and calculated values of Dit for TiO2/Si samples prepared at different ALD                             |

| temperatures. 53                                                                                               |

| Table 6.1 Surface roughness of N-polar GaN before and after ALD of Al <sub>2</sub> O <sub>3</sub>              |

| Table 6.2 Summary of electrical properties of ALD Al <sub>2</sub> O <sub>3</sub> on N-polar GaN with different |

| pretreatments. 73                                                                                              |

| Table 8.1 Calculated oxide capacitance, flat band capacitance, hysteresis and total trapped charge             |

| density of Al <sub>2</sub> O <sub>3</sub> on <i>c</i> - and <i>m</i> -plane GaN                                |

## **Acknowledgements**

I would like to thank my committee members who spent their precious time to train me on equipment and teach me knowledge during my doctoral research. Special thanks to Professor James Edgar, my major advisor and my role model for continuous supporting and inspiring me throughout the entire process. He also encourages me to continually explore the unknown and provide me valuable opportunities to lean in national laboratories. I feel very fortunate to work under his supervision. I also want to thank Professor Andrew Rys for guiding me into the electrical characterization of semiconductors and letting me use the oxidation furnace; Thank you Professor Vikas Berry for teaching me AFM and thank you Professor Keith Hohn for teaching me XPS.

I am grateful for numerous CV and IV measurements done by my co-worker and my friend Dr. Tashfin Hossain which is very important to this research. I also want to acknowledge Professor Daniel Higgins, Professor Takashi Ito for training me on the AFM, Dr. William Kuhn for trouble shooting electrical problems and Dr. Dan Boyle for teaching me SEM. I also want to thank all the professors, staffs and graduate students in chemical engineering who are always willing to help me out whenever I need them.

I would like to acknowledge Naval Research Laboratory for the collaborated work in this dissertation and Oak Ridge National Laboratory for providing user facilities to make partial of the device fabrication and characterization possible. Special thanks to Dr. Harry Meyer for training me operating the state-of-the-art XPS and Dr. Andrew Payzant, Dr. Melanie Kirkham for training me on XRD. I am also grateful for Dayrl Briggs who spends countless time writing recipes for processing my samples and training me on several semiconductor fabrication tools.

# **Dedication**

This dissertation is dedicated to my family and friends. Especially to my parents Bai Wei and Hongna Shen and grandparent Guichun Zhou.

## **Chapter 1 - Introduction**

### **Prologue to the thesis**

GaN based devices have successfully demonstrates its superior performance of high frequency, high power handling capability and high device efficiency in power electronic applications such as hybrid electric vehicles, controllers for electric grids, wireless networks and compact radars. This is owing to the unique physical properties of GaN for a wide band gap energy and high saturation electron mobility. In the past decade, the dimension of GaN based devices have been scaled down to achieve higher frequency performance which bring some drawbacks such as the increasing gate leakage current.

In this dissertation work, multiple high dielectric constant oxides has been deposited on GaN substrates forming metal oxide semiconductor capacitors to reduce the leakage current and increase the magnitude of voltage swing possible. These devices were tested by correlating the composition, chemical bonding states, impurity concentrations, structure and morphology of gate oxides, to the electrical properties of the device such as leakage current density, interface states and breakdown strength. These were also related to the process conditions under which the oxide was prepared to better control the performance of the device

### **Introduction of power electronics:**

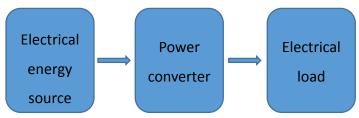

To manipulate electrical energy itself, power electronics are the vital components to convert and control the flow of electrical energy. A more complete illustration of power electronic system includes an energy source, an electrical load, and a power converter. A power converter consists switches, energy storage elements and transformers, which is used to change the characteristics including current, voltage and/or frequency of electrical power to serve certain application (electrical load).

Figure 1.1 Schematic picture of power electronic system<sup>2</sup>. The source energy is converted to serve an electrical load.

Ever since the invention of the transistor at Bell Laboratory in 1947,<sup>4</sup> this invention can be found in most modern electronic technologies as well as the power electronic circuit. The development of a commercial thyristor by General Electric Company in 1958 opened a new era of power electronics. Since then, many different types of power semiconductor devices have been developed such as power metal oxide semiconductor field effect transistor (IR 400V 25A) and insulated gate bipolar transistor (IGBT).

The unique property of semiconductors is that its electrical conductivity can be controlled over a wide range by introducing impurities which are atoms contain either one more (electrons) or one fewer (holes) electrons in their outermost shell than the host semiconductor atoms. This process is called doping by which different regions of the semiconductor with excessive electrons or holes could be formed, subsequently, those regions can be either positive (*p*-type) or negative (*n*-type). Solid state devices such as transistors are fabricated by forming junctions of these regions.

The function of a transistor is to control a large output with a small input. Based on how the electron flow is controlled when a bias voltage is applied between the terminals, transistors can be divided into two groups: bipolar (junction) transistors (BJT) and field effect transistors (FET). In a BJT, a potential profile controls the electron flow, while in a FET gate bias is used to control the flow. There are many kinds of FETs such as Metal Semiconductor Field effect transistor (MESFET), Heterojunction Field Effect Transistor (HFET), and Metal Oxide Semiconductor Field effect transistor (MOSFET) or Metal Insulator Semiconductor Field effect transistor (MISFET). Since the first introduction of commercial MOSFETs, they have replaced BJTs and became the most extensively used solid-state device, due to its simple fabrication technologies, excellent thermal stability and no secondary breakdown. These properties are favorable in high power applications.

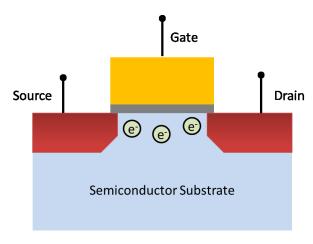

The MOSFET is a three terminal device with a source as an input, the drain as an output and the gate as a control terminal.<sup>5</sup> A MOSFET has a conducting semiconductor channel with two ohmic contacts (the source and the drain) on the end of each side of the channel as illustrates in Fig. 1.2. The number of charge carriers in the channel is controlled by the gate terminal through capacitive coupling (field effect),<sup>9</sup> and the insulator under the gate plays an important role of electrically separating the gate to the channel in order to minimize leakage current.

Figure 1.2 Schematic picture of a generic MOSFET

MOSFETs can be made from a wide variety of semiconductors including Si, GaAs, InP, InGaAs, GaN, SiC, etc., <sup>10–15</sup> among which GaN are prevalent for power electronic devices for high frequency, high temperature and high power applications <sup>16,17</sup> due to its advantageous physical properties shown in table 1.1.

Table 1.1 Physical properties of common semiconductor materials. GaN has superior saturated electron velocity and breakdown field comparing to other semiconductors. 18

| Semiconduc           | tor                   | silicon        | Gallium  | Indium    | Silicon | Gallium |

|----------------------|-----------------------|----------------|----------|-----------|---------|---------|

| Characteristic       | Unit                  | 56511          | arsenide | phosphide | carbide | nitride |

| Bandgap              | eV                    | 1.1            | 1.42     | 1.35      | 3.26    | 3.49    |

| Electron mobility at | cm²/Vs                | 1500           | 9500     | E400      | 700     | 1000-   |

| 300 K                | CIII / VS             | 1500 8500 5400 |          | 3400      | 700     | 2000    |

| Saturated (peak)     | ×10 <sup>7</sup> cm/s | 1.0            | 2.1      | 2.3       | 2.0     | 2.5     |

| electron velocity    | ~10 cm/3              | 1.0            | 2.1      | 2.3       | 2.0     | 2.5     |

| Critical breakdown   | MW/cm                 | 0.3            | 0.4      | 0.5       | 3.0     | 3.0     |

| field                | ivivv/ciii            | 0.5            | 0.4      | 0.5       | 3.0     | 3.0     |

| Thermal              | W/cm·K                | 1.5            | 0.5      | 0.7       | 4.5     | > 1.5   |

| conductivity         | VV/CIII·K             | 1.5            | 0.5      | 0.7       | 4.5     | 7 1.3   |

Although silicon has dominated electronic device since the 1950s because of its purity and the superior interface quality of Si/SiO<sub>2</sub>, <sup>19</sup> the increasing need of higher frequency and lower cost per device has pushed silicon to its limits. Also, the dimensions of the transistor has been dramatically reduced. Imagine the size of a 1960s transistor was as big as a three-bedroom house, and it shrank by the same factor that the transistor has over 50 years. Today, the house could be held on people's hand. <sup>20</sup> With the reduction in device size, there are several problems that need to be addressed including larger power density per chip, increasing heat dissipation, and shrinking thickness of gate oxide. <sup>21</sup> All these factors make GaN an important alternative to high speed Si electronics.

At high temperature, Si devices stop working at about 140°C due to its small bandgap (1.1 eV), which nullifies the effect of external dopant.<sup>22</sup> In contrast, with a larger bandgap of 3.4 eV GaN devices have been tested up to 300°C and worked very well.<sup>18</sup> In addition to bandgap, another crucial properties affecting the performance of the device is the carrier drift velocity which determines how fast a transistor can switch.<sup>23</sup> The maximum drift velocity of an electron in a semiconductor when an electrical field is applied is the saturation drift velocity.<sup>22</sup> GaN can achieve a very high saturation velocity due to the polarization generated from its unique crystalline structure.

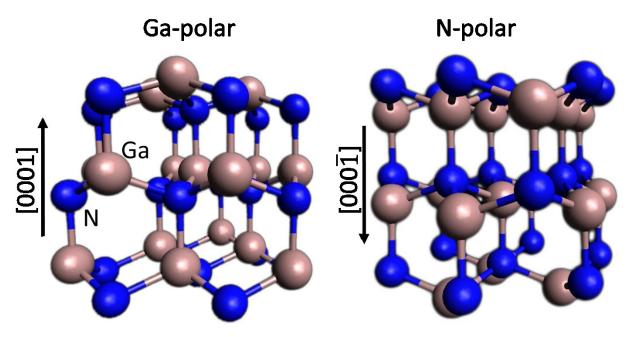

Figure 1.3 Crystal structure of wurtzite GaN.<sup>24</sup>

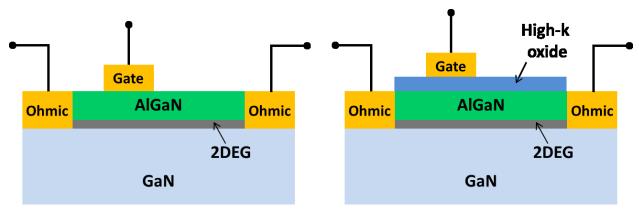

GaN exists in two crystal structures: wurtzite and zinc-blende. The most stable and commonly used phase is wurtzite. Due to the inversion asymmetry along the c-axis in the wurtzite phase, its structures along the (0001) [Ga-polar] and (000 $\overline{1}$ ) [N-polar] have distinctive properties (Fig 1.3).<sup>25</sup> This makes possible the fabrication of the GaN-based High electron mobility transistors (HEMTs) which are a derivation of a FET. Take the AlGaN on Ga-polar GaN HEMT as an example (Fig 1.4). In GaN crystal, the ionized gallium and nitrogen atoms greatly differ in size and settled irregularly with respect to each other, which naturally generates electrical polarization within the crystal. Due to the neutralization of opposite charged regions, this polarization does not accumulate until it reaches the boundary with another crystal (AlGaN). Furthermore, the lattices mismatch of the two crystals at this AlGaN/GaN heterojunction can generate piezoelectric polarization. <sup>26</sup> This combination of two polarizations produces a high concentration of free charge carriers in a narrow region parallel to the interface in GaN. commonly known as two dimensional electron gas (2DEG), which is the critical part of HEMTs. Unlike most other semiconductors, the GaN HEMTs can form the mobile electron gases without doping with impurities. 18 This is advantageous because the electron mobility is reduced as the impurity concentration increases due to scattering. Until recently, all AlGaN-GaN HEMTs were made on Ga-polar GaN rather than N-polar semiconductors. 27-29

Figure 1.4 Structure of AlGaN/GaN HEMT (left) and MOSHEMT (right)

In contrast to an ordinary silicon based FET, which requires a gate bias to turn on the transistor (enhancement-mode operation), the source and drain of a GaN HEMT is always connected by the 2DEG. This is specifically true for a Ga-polar GaN-based HEMT. So when a voltage is applied to the drain, it can instantly draw electrons from the source. A negative gate voltage is required to adjust the amplitude of the current and even cut it off. This type of device is called normally-on transistor or depletion-mode transistor.<sup>30</sup> However, in the field of power

electronic applications, a normally-off type transistor is preferred for fail-safe operation and to minimize energy consumption.<sup>31</sup> For the normally-off transistor, a positive gate voltage is necessary to create a region of mobile electrons which connects the source and drain, and when the voltage is retrieved, the transistor is open (off). This is also called enhancement mode transistor.<sup>30</sup>

There are several ways of making a GaN enhancement transistor. First of all, is to use N-polar GaN as the substrate.<sup>29</sup> The switch of polarity of GaN crystal could adjust the amount of electrons in the 2DEG, and complete depletion of the electron turns it into an enhancement transistor. Secondly, 2DEG could also be controlled by fluoride-based plasma treatment,<sup>32</sup> in which fluorine ions act as immobile negative charges that deplete the 2DEG.<sup>33</sup> But implantation of the highly energetic fluorine ions leads to a defect formation in the 2DEG region, and consequently scarifies the electron velocity. An alternative structure to achieve the normally-off condition is to employ a GaN MOSFETs, but this structure also compromise the enhanced electron mobility.<sup>34</sup>

Another important factor in GaN transistor is a good insulation between the gate and channel, because the maximum forward voltage that can be applied to the gate is restricted by the Schottky barrier height. This would be the bottleneck if high positive gate voltage is required to generate significant drain current flow for the enhancement mode transistor. Adding a high dielectric constant [high-k] oxide (k > 3.9)insulator between the transistor gate and substrate helps to address the problems. It can significantly lower the leakage currents through the gate and increase the magnitude of voltage swings possible, thereby greatly increasing the device efficiency.  $^{35,36}$

### Reference

- <sup>1</sup> M.H. Rashid, *Power Electronic Handbook* (Academic Press, San Diego, 2001).

- <sup>2</sup> P.T. Krein, *Elements of Power Electronics* (Oxford University Press, USA, 1997), p. 784.

- <sup>3</sup> B. Ozpineci, Http://edoqs.com/pdf/introduction-to-Bpowerb-Belectronicsb-a-Tutorial 1c71e17d0c902a8aebbaf10d4ba45ac2 (n.d.).

- <sup>4</sup> W.F. Brinkman, D.E. Haggan, and W.W. Troutman, IEEE J. Solid-State Circuits **32**, 1858 (1997).

- <sup>5</sup> J.D. Plummer, M. Deal, and P.D. Griffin, *Silicon VLSI Technology: Fundamentals, Practice, and Modeling* (Prentice Hall, Upper Saddle River, 2000), p. 817.

- <sup>6</sup> U.K. Mishra and J. Singh, *Semiconductor Device Physics and Design* (Springer Netherlands, Dordrecht, 2008).

- <sup>7</sup> R.S. Muller, T.I. Kamins, and M. Chan, in (Wiley, 2002), p. 560.

- <sup>8</sup> I. Yoshida, T. Okabe, M. Katsueda, S. Ochi, and M. Nagata, IEEE Trans. Electron Devices **27**, 395 (1980).

- <sup>9</sup> T. Ytterda, Y. Cheng, and T.A. Fjeldly, MOSFET Device Physics and Operation (2003).

- <sup>10</sup> J.L. Hoyt, H.M. Nayfeh, S. Eguchi, I. Aberg, G. Xia, T. Drake, E.A. Fitzgerald, and D.A. Antoniadis, in *Dig. Int. Electron Devices Meet.* (IEEE, 2002), pp. 23–26.

- <sup>11</sup> P.D. Ye, G.D. Wilk, J. Kwo, B. Yang, H.-J.L. Gossmann, M. Frei, S.N.G. Chu, J.P. Mannaerts, M. Sergent, M. Hong, K.K. Ng, and J. Bude, IEEE Electron Device Lett. **24**, 209 (2003).

- <sup>12</sup> Y. Xuan, Y.Q. Wu, and P.D. Ye, **29**, 294 (2008).

- <sup>13</sup> Y.Q. Wu, Y. Xuan, T. Shen, P.D. Ye, Z. Cheng, and A. Lochtefeld, Appl. Phys. Lett. **91**, (2007).

- <sup>14</sup> W. Huang, T. Khan, and T.P. Chow, in 2006 IEEE Int. Symp. Power Semicond. Devices IC's (IEEE, 2006), pp. 1–4.

- <sup>15</sup> J. Senzaki, K. Kojima, S. Harada, R. Kosugi, S. Suzuki, T. Suzuki, and K. Fukuda, IEEE Electron Device Lett. **23**, 13 (2002).

- <sup>16</sup> M.S. Shur and R.F. Davis, *GaN-Based Electronic Devices* (World Scientifie Publishing Co., Singapore, 2004).

- <sup>17</sup> T.D. Steiner, *Semiconductor Nanostructures for Optoelectronic Applications* (Artech House, 2004), p. 412.

- <sup>18</sup> L.F. Eastman and U.K. Mishra, IEEE Spectr. (2002).

- <sup>19</sup> M. Riordan and L. Hoddeson, *Crystal Fire: The Birth of the Information Age* (Blackstone Audiobooks, 1998).

- <sup>20</sup> M. Bohr, R. Chau, T. Ghani, and K. Mistry, IEEE Spectr. 44, 29 (2007).

- <sup>21</sup> R. Waser, *Nanoelectronics and Information Technology* (Wiley-VCH, 2005), pp. 359–400.

- <sup>22</sup> B. Streetman and S. Banerjee, *Solid State Electronic Devices*, 6th ed. (Prentice Hall, 2005), pp. 96–97.

- <sup>23</sup> S.J. Pearton, F. Ren, A.P. Zhang, and K.P. Lee, Mater. Sci. Eng. R Reports **30**, 55 (2000).

- <sup>24</sup> O. Ambacher, J. Phys. D Appl. Phys. **31**, 2653 (1998).

- <sup>25</sup> S. Rajan, A. Chini, M.H. Wong, J.S. Speck, and U.K. Mishra, J. Appl. Phys. **102**, 044501 (2007).

- <sup>26</sup> P.M. Asbeck, E.T. Yu, S.S. Lau, G.J. Sullivan, J. Van Hove, and J. Redwing, Electron. Lett. **33**, 1230 (1997).

- <sup>27</sup> P.S. Park, D.N. Nath, and S. Rajan, IEEE Electron Device Lett. **33**, 991 (2012).

- <sup>28</sup> U. Singisetti, M.H. Wong, J.S. Speck, and U.K. Mishra, IEEE Electron Device Lett. **33**, 33 (2012).

- <sup>29</sup> U. Singisetti, M.H. Wong, and U.K. Mishra, Semicond. Sci. Technol. **28**, 074006 (2013).

- <sup>30</sup> W.J. Dally and J.W. Poulton, *Digital Systems Engineering* (Cambridge University Press, 1998), p. 663.

- <sup>31</sup> Y. Niiyama, T. Shinagawa, S. Ootomo, H. Kambayashi, T. Nomura, and S. Kato, Furukawa Rev. 1 (2009).

- <sup>32</sup> Y. Cai, Y. Zhou, K.J. Chen, and K.M. Lau, IEEE Electron Device Lett. 26, 435 (2005).

- <sup>33</sup> L. Pang and K. (Kevin) Kim, 2013 IEEE Power Energy Conf. Illinois 8 (2013).

- <sup>34</sup> Y.Q. Wu, P.D. Ye, G.D. Wilk, and B. Yang, Mater. Sci. Eng. B **135**, 282 (2006).

- <sup>35</sup> T. Oka, S. Member, and T. Nozawa, **29**, 668 (2008).

- <sup>36</sup> M. Kanamura, T. Ohki, T. Kikkawa, K. Imanishi, T. Imada, A. Yamada, and N. Hara, IEEE Electron Device Lett. **31**, 189 (2010).

## **Chapter 2 - Review of High-k Dielectrics on GaN**

### Introduction of high-k oxides

Using high-k materials as the gate stack traces back to the fabrication of integrated circuit (IC) using silicon based MOSFETs where the SiO<sub>2</sub>/Si was the most common insulator/semiconductor system until 21<sup>st</sup> century since the development of the first MOSFET.<sup>1</sup> To keep up with Moore's Law, the physical size of the transistor needs to be reduced by half every two years.<sup>2</sup> This leads to the shrinking of the gate dielectric thickness; the SiO<sub>2</sub> decreased from a few hundred nanometers to a few atomic layers (~1-2nm).<sup>3</sup> As the thickness approaching 1 nm, SiO<sub>2</sub> loses its insulating properties, as significant numbers of electrons tunnel through the energy barrier,<sup>4</sup> turning into unwanted heat and draining out of battery quickly.

To solve this problem, new materials are required to replace SiO<sub>2</sub>. They should be able to form an insulating film that is thick enough to prevent electrons tunneling while at the same time being permeable enough to allow the gate electric field into the channel to accumulate enough electrons so that the transistor could be turned on.<sup>1</sup> The technical name for this material is high-k dielectric, which refers the dielectric constant of the material should be larger than that of SiO<sub>2</sub> (3.9).

Similar concepts are also applied to GaN-based transistors. A good compatible dielectric to GaN semiconductor requires a high dielectric constant, large conduction band offset, thermodynamic stable, low oxygen diffusivity, low leakage current and high interface quality with low interface state density.<sup>5–8</sup> However, the much inferior structural quality of the GaN/oxide interfaces in comparison to the Si/SiO<sub>2</sub> interface of Si-based MOS devices has remained a major obstacle <sup>9</sup>. In this chapter, previous studies of high-k dielectrics on GaN are reviewed, among which more attention was cast on Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub> and Ga<sub>2</sub>O<sub>3</sub> due to their outstanding properties. Other oxides are also briefly reviewed and compared. A summary of the best candidate high dielectric for GaN is made.

### Al<sub>2</sub>O<sub>3</sub> as gate dielectric on GaN based transistor

$Al_2O_3$  has been widely studied as a gate oxide due to its suitable physical properties and many methods by which its thin layers can be deposited. The dielectric constant of  $Al_2O_3$  ranges from 8 to 10,  $^{10,11}$  which yields an effective oxide thickness  $\sim 0.4$  times of the  $SiO_2$  thickness. The

band gap of  $Al_2O_3$  ranges from 6.8 to 9.4 eV.<sup>11–14</sup> This gives a high conduction band offset with GaN of  $\Delta E_c$ =2.1 eV.<sup>15,16</sup> A large breakdown field of  $Al_2O_3$  of 10MV/cm, <sup>13</sup> and good thermal stability (amorphous up to at least  $1000^{\circ}C$ ) make it suitable for scaling devices and in high power applications. Many methods have been reported for depositing  $Al_2O_3$  including sputtering, <sup>10</sup> metal-organic chemical vapor deposition (MOCVD), <sup>17,18</sup> oxidation of molecular beam epitaxial (MBE) of aluminum layer, <sup>16</sup> and atomic layer deposition (ALD). <sup>19–22</sup>

In all cases, adding an Al<sub>2</sub>O<sub>3</sub> insulator improved the transistor performance, enabling a great increase in the drain current density and a two to three orders of magnitude of lower leakage current compared to the GaN HFET counterpart. However, the interface quality was not reported by MBE method, <sup>16</sup> and an additional Si<sub>3</sub>N<sub>4</sub> layer was required before sputtering Al<sub>2</sub>O<sub>3</sub> on GaN based transistor to achieve a good quality interface. <sup>10</sup> MOCVD reduces the current collapse by decreasing the interface trap density, and has the advantage of forming crystalline and amorphous Al<sub>2</sub>O<sub>3</sub> by adjusting the reaction temperature, <sup>17</sup> but hysteresis on the capacitance-voltage measurement were not resolved, and quantitative studies of Al<sub>2</sub>O<sub>3</sub> /GaN interface state were not presented. ALD of Al<sub>2</sub>O<sub>3</sub> films were the most studied and offer better control over the oxide thickness. For Al<sub>2</sub>O<sub>3</sub> deposited by ALD on GaN, the as-deposited interface trap density was between 10<sup>12</sup> and 10<sup>13</sup> cm<sup>-2</sup>. This could be reduced by an order of magnitude by postmetallization annealing (PMA) in forming gas (5% H<sub>2</sub>, 95% N<sub>2</sub>) for 5 min at 500°C. <sup>20</sup> Consequently, ALD has become the most widely accepted Al<sub>2</sub>O<sub>3</sub> deposition method.

# HfO2 as gate dielectric on GaN transistor

HfO<sub>2</sub> has also been widely used in GaN based transistors due to its large dielectric constant ( $\epsilon$ =25), <sup>13</sup> large band gap (5.6~5.8 eV)<sup>3</sup> and low state density at the oxide semiconductor interface. Most studies of HfO<sub>2</sub>/AlGaN/GaN focus on the device performance rather than the physical and electrical properties of the oxide-nitride interface. <sup>23–29</sup> The main finding from HfO<sub>2</sub> studies is that the density of surface states could be passivated by all the following reviewed deposition methods which relief the depletion in the 2DEG channel leading to an increasing of sheet carrier density (n<sub>s</sub>). <sup>30,31</sup> Consequently, the drain current was increased and current collapse was reduced.

Deposition studies of HfO<sub>2</sub> for gate dielectrics includes ALD, reactive sputtering and pulsed laser deposition (PLD), among which ALD has better uniformity, better nano-scale

thickness control and low defect densities.  $^{24,25}$  Shi *et al.*  $^{25}$  grew a 15 nm HfO<sub>2</sub> film on AlGaN/GaN HEMT by ALD. The device demonstrated an off-state breakdown voltage  $V_{DS}$  of 1035 V with on resistance of 0.9m $\Omega$  cm<sup>2</sup>, a maximum drain current ( $J_{DS, max}$ ) of 575 mA/mm at the gate voltage of +1 V and a peak transconductance ( $g_{m,max}$ ) of 160mS/mm, which has the best performance of HfO<sub>2</sub>/AlGaN/GaN HEMT ever reported. A 20 nm HfO<sub>2</sub> reported by Liu *et al.*  $^{24}$  showed an increase of the sheet carrier density from  $8.53x10^{12}$  cm<sup>-2</sup> to  $1.12x10^{13}$  cm<sup>-2</sup> as expected, but the mobility ( $\mu_n$ ) was decreased from 1140 cm<sup>2</sup>(Vs)<sup>-1</sup> to 1015 cm<sup>2</sup>(Vs)<sup>-1</sup>. This reduced Hall mobility associated with the increased carrier concentration was proposed to be caused by an increased interface-roughness scattering as a result of 2DEG shifting towards the AlGaN/GaN interface at higher carrier concentration.<sup>32</sup> This is not observed with HfO<sub>2</sub> on GaN deposited by the ALD method. Thicker HfO<sub>2</sub> of 100 nm could be grown by pulsed laser deposition on a normally off device  $^{29}$  with a  $I_{DS,max}$  of 730 mA/mm at  $V_G$  of +10 V and gm max of 185 mS/mm which is very promising for simplicity of circuit design and fail safe power switching system.

Compared to Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub> has a larger dielectric constant, which helps further scaling of the EOT. But Al<sub>2</sub>O<sub>3</sub> has a larger band gap than HfO<sub>2</sub>, and its conduction band offset with GaN was 1 eV higher than that of HfO<sub>2</sub>, <sup>33</sup> which provides a sufficient barrier for carriers in the GaN. Furthermore, Al<sub>2</sub>O<sub>3</sub> has stronger adhesion to many surface and better chemical and thermal stabilities than HfO<sub>2</sub>. <sup>34,35</sup> So a gate stack of HfO<sub>2</sub> on a Al<sub>2</sub>O<sub>3</sub> passivation layer would be beneficial.

More thorough studies of the device physics are still needed. As shown in the papers summarized above, the dielectric constant of  $HfO_2$  varies from 16.5 to 24,  $^{24,28,36}$  and no explanation was provided for the change. Quantitative  $D_{it}$  analysis is also needed to correlate the deposition condition to better control the performance of the device.

## Ga<sub>2</sub>O<sub>3</sub> as gate dielectric on GaN transistor

Ga<sub>2</sub>O<sub>3</sub> is a native oxide of GaN with the dielectric constant of 10.2-14.2 and band gap of 4.8eV.<sup>37</sup> Although the conduction band offset with GaN is 0.46 eV which is smaller than most of the other high k oxides,<sup>15</sup> Ga<sub>2</sub>O<sub>3</sub> can be formed thermally and it is a chemically stable oxide on GaN. It also prevents the introduction of contamination from foreign oxide deposition and is expected to form high quality interface with GaN.<sup>38-41</sup>

The commonly used methods to grow  $Ga_2O_3$  are photoelectrochemical oxidation,  $^{40,41}$  pulsed laser deposition,  $^{39}$  oxygen plasma oxidation,  $^{42}$  saturated water vapor oxidation  $^{43}$  and thermal oxidation.  $^{44-47}$  Among all the above techniques, the lowest interface trap density of  $10^{10}$  cm<sup>-2</sup> eV<sup>-1</sup> was achieved by dry thermal oxidation.  $^{44,45}$  This is also one order of magnitude lower than the lowest achieved  $D_{it}$  with deposited insulator/GaN interface. It is worthwhile exploring a bit more about thermal oxidation of GaN due to this record low  $D_{it}$  and simple experimental setup.

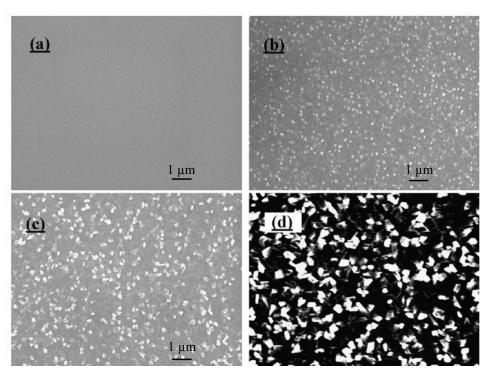

The thermal oxidation of GaN usually yields β-Ga<sub>2</sub>O<sub>3</sub> which is the most thermodynamically stable phase of all possible allotropes of gallium oxide. The oxidation rate of GaN is extremely slow when the temperature is lower than 750°C. The oxidation is a first order reaction for temperatures above 900°C. However, the surface roughness increased with increasing temperature. The following figures showed morphology of oxide surface (Fig. 2.1) and oxide/GaN interface (Fig. 2.2) at different temperatures. As shown in Fig 2.2, there are bubble shaped areas presented for samples oxidized at 950°C and 1000°C which suggests that GaN simultaneously thermally decomposed and was oxidized at these high temperatures. This increasing roughness could deteriorate the interface quality and consequently increase the D<sub>it</sub>. The lowest D<sub>it</sub> of Ga<sub>2</sub>O<sub>3</sub>/GaN ever achieved (1x10<sup>10</sup> cm<sup>-2</sup>eV<sup>-1</sup>) was conduct at an oxidation temperature of 880°C, <sup>44</sup> followed by one order of magnitude higher D<sub>it</sub> of produced at 850°C <sup>47</sup> and 900°C <sup>46</sup> respectively. So the optimal oxidation temperature range is between 850 and 900°C in which the oxidation rate is significant and the interface quality is high.

Figure 2.1 SEM images of Ga<sub>2</sub>O<sub>3</sub> surfaces form at different temperatures (a) 850°C, (b) 900°C, (c) 950°C, (d) 1000°C.<sup>46</sup>

Figure 2.2 SEM images of the underlying GaN surface after the  $Ga_2O_3$  layer was removed. The original oxidation temperatures were: (a)  $850^{\circ}C$ , (b)  $900^{\circ}C$ , (c)  $950^{\circ}C$  (d)  $1000^{\circ}C$  all for 6 hr.  $^{46}$

### Other oxides as Gate dielectric

Chang *et al.*<sup>50,51</sup> deposited 10nm Gd<sub>2</sub>O<sub>3</sub> with a moderate high dielectric constant of 17 on GaN by electron beam evaporation. With a relative small band gap (5.8 eV) of Gd<sub>2</sub>O<sub>3</sub>, 1100°C annealing for 5 min was conducted to refine the crystallinity of monoclinic Gd<sub>2</sub>O<sub>3</sub>, which reduce the leakage current from 7.9x10<sup>-6</sup> to 4.6x10<sup>-9</sup> A/cm<sup>2</sup> at 1 MV/cm. Capacitance-voltage measurements (C-V) showed a small frequency dispersion between 500 and 10 kHz indicating a low interface trap density, but no quantitative interface calculation was performed. Gd<sub>2</sub>O<sub>3</sub> might be suitable gate oxide for high temperature processing of GaN.

Chui *et al.*<sup>52</sup> reported on the properties of 10 nm La<sub>2</sub>O<sub>3</sub> deposited by electron beam evaporation on GaN. The dielectric constant was 13.1 which is much smaller than its static bulk dielectric constant of 30. The leakage current was suppressed by only 1 order of magnitude. A similar current suppression was also observed by Jur *et al.*<sup>53</sup> A 5 nm La<sub>2</sub>O<sub>3</sub> was put down by evaporation of La and subsequently oxidized, the leakage current was 10<sup>-2</sup> A/cm<sup>2</sup> at positive bias, which proves La<sub>2</sub>O<sub>3</sub> does not efficiently of reduce the leakage current for GaN transistor. LaAlO<sub>3</sub> was promising for Si based transistor, <sup>54–57</sup> and a large band offset has been proposed on GaN (shown in Table 2.1), but more research is needed to verify this proposal.

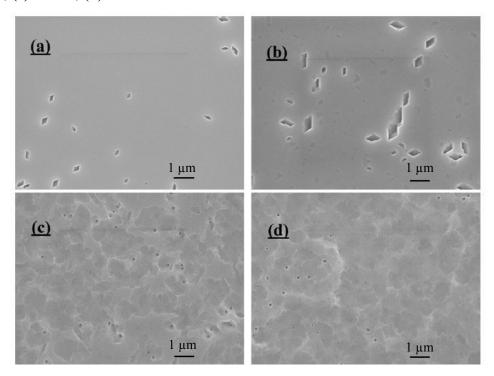

Perovskite oxides such as SrTiO<sub>3</sub>, TiO<sub>2</sub>, PbTiO<sub>3</sub> usually have very large dielectric constant (up to 2000 for SrTiO<sub>3</sub>),<sup>11</sup> and are excellent high k dielectric candidates for the application of dynamic random access memory (DRAM) <sup>58</sup>. Such high dielectric constants are achieved because of these oxides' crystal structures, usually cubic or tetragonal. Take BaTiO<sub>3</sub> as an example (fig 2.3), the Ti ions reside about the center of the Ti–O octahedral. A displacement of Ti ions causes great polarization, which can give rise to very large dielectric constants of 2000–3000. Since ions respond more slowly than electrons to an applied field, the ionic contribution begins to decrease at high frequencies.<sup>13</sup> Also, since the crystal structure of GaN is hexagonal, buffer layers such as MgO and TiO<sub>2</sub> might be needed to maintain the crystallinity of the Perovskite oxides.<sup>59</sup> Furthermore, Perovskite oxides usually have small band offsets with GaN. Improving the electrical breakdown strength and suppressing the leakage current on wide band gap GaN based transistor are still challenging. So more research on the application of perovskite oxide to GaN transistor for high frequency application is greatly needed.

Figure 2.3 The unit cell of BaTiO<sub>4</sub>. The displacement of the cation lattice with respect to the anion lattice induces a static dipole moment and thus, a spontaneous polarization in the perovskite crystal.

$Ta_2O_5$  has been deposited on GaN by ALD and EBE respectively. <sup>60,61</sup> EBE deposited 30 nm  $Ta_2O_5$  film reduced the leakage current by 3 order of magnitude, but the interface traps was not measured. A 6nm thick  $Ta_2O_5$  on AlN/GaN grown by ALD increased the drain current and transconductance. However, the interface trap density of above  $10^{13}$  cm<sup>-2</sup>eV<sup>-1</sup> was quite high.

$SiN_x$  has the potential of achieving good SiN/GaN interface quality, but the device having PECVD SiN gate dielectric showed high leakage current. So SiN coupling with other high band offset oxide such as  $Al_2O_3$  should be more promising.

$Sc_2O_3$  has been deposited on GaN both as passivation layers and gate dielectrics by RF plasma assisted MBE and pulsed laser deposition. <sup>65–67</sup> Drain current slightly increased about 6% by MBE method. <sup>66</sup> A high interface quality with  $D_{it}$ =4x10<sup>11</sup> cm<sup>-2</sup>eV<sup>-1</sup> was achieved by pulsed laser deposition, and a low current density of 1x10<sup>-6</sup> A/cm<sup>2</sup> at 30V gate bias. <sup>67</sup>

$ZrO_2$  has similar physical properties as  $HfO_2$  such as a high dielectric constant of 23 and band gap of 5.8 eV.<sup>11</sup> Electron beam evaporation was applied as the deposition method to grow  $ZrO_2$  on  $GaN.^{63,68}$  There was a ~50% increase of the drain current and four-order of magnitude decrease of the leakage current. But, the intermixing with GaN was unexpected and further studies are needed to overcome this problem.

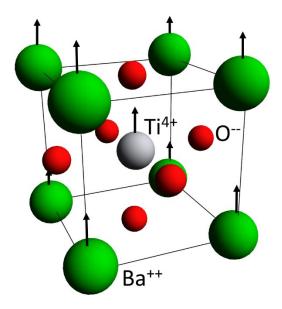

### **Summary**

In general dielectrics with large k-value such as SrTiO<sub>3</sub> have small E<sub>g</sub> (Fig. 2.4) leading to a small breakdown strength and less efficient of suppressing the gate leakage current. On the other hand, Al<sub>2</sub>O<sub>3</sub> has the largest band gap of all the reviewed high-k oxides, and it has a moderate dielectric constant limiting the further scaling of the device. HfO<sub>2</sub> with a complimentary properties of slightly bigger band gap comparing to SrTiO<sub>3</sub> and a larger dielectric constant comparing to Al<sub>2</sub>O<sub>3</sub> makes it a promising high k dielectric. Ga<sub>2</sub>O<sub>3</sub> forms the best interface quality with GaN which could be realized by a simple deposition method. So combining the advantages of different high-k oxides would have great research potential to accelerating the development of GaN based power electronics.

Figure 2.4 Distribution of the high-k dielectrics and their band gap.

Table 2.1 Summary of the reviewed oxides and their properties including band gap, dielectric constant and band offset with GaN.

| Material                       | Band Gap<br>E <sub>g</sub> (eV) | Dielectric<br>Constant<br>ε | Conductance Band offset $\Delta E_c$ (eV) | Valence<br>Band offset<br>ΔE <sub>v</sub> (eV) |

|--------------------------------|---------------------------------|-----------------------------|-------------------------------------------|------------------------------------------------|

| Al <sub>2</sub> O <sub>3</sub> | 8.8-9.4                         | 9.0-11                      | 2.1                                       | 3.4                                            |

| HfO <sub>2</sub>               | 5.6-5.8                         | 21-25                       | 1.09                                      | 1.6                                            |

| HfSiO <sub>4</sub>             | 6.5                             | 11                          | 1.57                                      |                                                |

| LaAlO <sub>3</sub>             | 5.6-6.2                         | 30                          | 1.13                                      | 1.3                                            |

| La <sub>2</sub> O <sub>3</sub> | 6                               | 30                          | 1.97                                      | 0.8                                            |

| Ga <sub>2</sub> O <sub>3</sub> | 4.8                             | 10.2-14.2                   | 0.46                                      | 1.1                                            |

| Gd <sub>2</sub> O <sub>3</sub> | 5.8                             | 17                          | 1.9                                       | 0.7                                            |

| PbTiO₃                         | 3.4                             | 78-104 (91)                 | 0.4                                       |                                                |

| SrTiO <sub>3</sub>             | 3.3                             | 2000                        | -0.1                                      | 0.2                                            |

| Ta <sub>2</sub> O <sub>5</sub> | 4.4                             | 22                          | 0.1                                       | 0.9                                            |

| TiO <sub>2</sub>               | 3.5                             | 80                          |                                           |                                                |

| SiO <sub>2</sub>               | 9                               | 3.9                         | 2.56                                      | 3.2                                            |

| Si <sub>3</sub> N <sub>4</sub> | 5.3                             | 7                           | 1.3                                       | 0.6                                            |

| Sc <sub>2</sub> O <sub>3</sub> | 6.3                             | 14.5                        | 1.97                                      | 0.8                                            |

| ZrO <sub>2</sub>               | 5.8                             | 25                          | 1.1                                       | 1.6                                            |

### Reference

- <sup>1</sup> M. Bohr, R. Chau, T. Ghani, and K. Mistry, IEEE Spectr. 44, 29 (2007).

- <sup>2</sup> G.E. Moore, Electronics **38**, (1965).

- <sup>3</sup> E.P. Gusev, V. Narayanan, and M.M. Frank, IBM J. Res. Dev. **50**, (2006).

- <sup>4</sup> A.T. Fromhold, *Quantum Mechanics for Applied Physics and Engineering* (Courier Dover Publications, 1981).

- <sup>5</sup> D.G. Schlom and J.H. Haeni, MRS Bull. **27**, 198 (2011).

- <sup>6</sup> J. Robertson, MRS Bull. **27**, 217 (2011).

- <sup>7</sup> V. Misra, G. Lucovsky, and G. Parsons, MRS Bull. **27**, 212 (2011).

- <sup>8</sup> S. Guha, E. Gusev, M. Copel, L.-Å. Ragnarsson, and D.A. Buchanan, MRS Bull. **27**, 226 (2011).

- <sup>9</sup> S. Oktyabrsky and P.D. Ye, *Fundamentals of III-V Semiconductor MOSFETs* (Springer New York Dordrecht Heidelberg London, 2010).

- <sup>10</sup> N. Maeda, C. Wang, T. Enoki, T. Makimoto, and T. Tawara, Appl. Phys. Lett. **87**, 073504 (2005).

- <sup>11</sup> J. Robertson, Eur. Phys. J. Appl. Phys. **28**, 265 (2004).

- <sup>12</sup> N. Nepal, N.Y. Garces, D.J. Meyer, J.K. Hite, M. a. Mastro, and J.. C.R. Eddy, Appl. Phys. Express **4**, 055802 (2011).

- <sup>13</sup> G.D. Wilk, R.M. Wallace, and J.M. Anthony, J. Appl. Phys. **89**, 5243 (2001).

- <sup>14</sup> R.H. French, J. Am. Ceram. Soc. **73**, 477 (1990).

- <sup>15</sup> J. Robertson and B. Falabretti, J. Appl. Phys. **100**, 014111 (2006).

- <sup>16</sup> T. Hashizume, S. Ootomo, and H. Hasegawa, Appl. Phys. Lett. **83**, 2952 (2003).

- <sup>17</sup> D. Gregušová, R. Stoklas, K. Čičo, T. Lalinský, and P. Kordoš, Semicond. Sci. Technol. **22**, 947 (2007).

- <sup>18</sup> P. Kordoš, D. Gregušová, R. Stoklas, Š. Gaži, and J. Novák, Solid. State. Electron. **52**, 973 (2008).

- <sup>19</sup> M. Esposto, S. Krishnamoorthy, D.N. Nath, S. Bajaj, T.-H. Hung, and S. Rajan, Appl. Phys. Lett. **99**, 133503 (2011).

- <sup>20</sup> T.-H. Hung, S. Krishnamoorthy, M. Esposto, D. Neelim Nath, P. Sung Park, and S. Rajan, Appl. Phys. Lett. **102**, 072105 (2013).

- <sup>21</sup> Z.H. Liu, G.I. Ng, S. Arulkumaran, Y.K.T. Maung, K.L. Teo, S.C. Foo, and V. Sahmuganathan, Appl. Phys. Lett. **95**, 223501 (2009).

- <sup>22</sup> Y.Q. Wu, P.D. Ye, G.D. Wilk, and B. Yang, Mater. Sci. Eng. B 135, 282 (2006).

- <sup>23</sup> D.A. Deen, S.C. Binari, D.F. Storm, D.S. Katzer, J.A. Roussos, J.C. Hackley, and T. Gougousi, Electron. Lett. **45**, 423 (2009).

- <sup>24</sup> C. Liu, E.F. Chor, and L.S. Tan, Semicond. Sci. Technol. **22**, 522 (2007).

- <sup>25</sup> J. Shi, L.F. Eastman, X. Xin, and M. Pophristic, Appl. Phys. Lett. **95**, 042103 (2009).

- <sup>26</sup> J. Shi and L.F. Eastman, IEEE Electron Device Lett. **32**, 312 (2011).

- <sup>27</sup> X. Xin, J. Shi, L. Liu, J. Edwards, K. Swaminathan, M. Pabisz, M. Murphy, L.F. Eastman, and M. Pophristic, IEEE Electron Device Lett. **30**, 1027 (2009).

- <sup>28</sup> Y. Yue, Y. Hao, J. Zhang, J. Ni, W. Mao, Q. Feng, and L. Liu, IEEE Electron Device Lett. **29**, 838 (2008).

- <sup>29</sup> S. Sugiura, S. Kishimoto, T. Mizutani, M. Kuroda, T. Ueda, and T. Tanaka, Phys. Status Solidi **5**, 1923 (2008).

- <sup>30</sup> M. Marso, G. Heidelberger, K.M. Indlekofer, J. Bernat, A. Fox, P. Kordos, and H. Luth, IEEE Trans. Electron Devices **53**, 1517 (2006).

- <sup>31</sup> R. Vetury, N.Q. Zhang, S. Keller, and U.K. Mishra, IEEE Trans. Electron Devices **48**, 560 (2001).

- <sup>32</sup> J. Antoszewski, M. Gracey, J.M. Dell, L. Faraone, T.A. Fisher, G. Parish, Y.-F. Wu, and U.K. Mishra, J. Appl. Phys. **87**, 3900 (2000).

- <sup>33</sup> J. Yang, B.S. Eller, C. Zhu, C. England, and R.J. Nemanich, J. Appl. Phys. **112**, 053710 (2012).

- <sup>34</sup> I. Kim, J. Koo, J. Lee, and H. Jeon, Jpn. J. Appl. Phys. **45**, 919 (2006).

- <sup>35</sup> Y.Q. Wu, T. Shen, P.D. Ye, and G.D. Wilk, Appl. Phys. Lett. **90**, 143504 (2007).

- <sup>36</sup> V. Tokranov, S.L. Rumyantsev, M.S. Shur, R. Gaska, S. Oktyabrsky, R. Jain, and N. Pala, Phys. Status Solidi Rapid Res. Lett. **1**, 199 (2007).

- <sup>37</sup> H.S. Oon and K.Y. Cheong, Mater. Sci. Semicond. Process. **16**, 1217 (2013).

- <sup>38</sup> Y.-L. Chiou, L.-H. Huang, and C.-T. Lee, Semicond. Sci. Technol. **25**, 045020 (2010).

- <sup>39</sup> S.-A. Lee, J.-Y. Hwang, J.-P. Kim, S.-Y. Jeong, and C.-R. Cho, Appl. Phys. Lett. **89**, 182906 (2006).

- <sup>40</sup> C.T. Lee, H.Y. Lee, and H.W. Chen, IEEE Electron Device Lett. **24**, 54 (2003).

- <sup>41</sup> C.-T. Lee, H.-W. Chen, and H.-Y. Lee, Appl. Phys. Lett. **82**, 4304 (2003).

- <sup>42</sup> H.J. Lee, S.M. Kang, T.I. Shin, J.W. Shur, and D.H. Yoon, J. Ceram. Process. Res. **9**, 180 (2008).

- <sup>43</sup> T. Futatsuki, T. Oe, H. Aoki, N. Komatsu, C. Kimura, and T. Sugino, Jpn. J. Appl. Phys. **48**, 04C006 (2009).

- <sup>44</sup> Y. Nakano and T. Jimbo, Appl. Phys. Lett. **82**, 218 (2003).

- <sup>45</sup> Y. Nakano, T. Kachi, and T. Jimbo, Appl. Phys. Lett. **82**, 2443 (2003).

- <sup>46</sup> Y. Zhou, C. Ahyi, T. Isaacs-Smith, M. Bozack, C.-C. Tin, J. Williams, M. Park, A. Cheng, J.-H. Park, D.-J. Kim, D. Wang, E. a. Preble, A. Hanser, and K. Evans, Solid. State. Electron. **52**, 756 (2008).

- <sup>47</sup> H. Kim, S.-J. Park, and H. Hwang, J. Vac. Sci. Technol. B Microelectron. Nanom. Struct. **19**, 579 (2001).

- <sup>48</sup> R. Roy, V.G. Hill, and E.F. Osborn, J. Am. Chem. Soc. **74**, 719 (1952).

- <sup>49</sup> S.D. Wolter, B.P. Luther, D.L. Waltemyer, C. Onneby, S.E. Mohney, and R.J. Molnar, Appl. Phys. Lett. **70**, 2156 (1997).

- <sup>50</sup> W.H. Chang, C.H. Lee, P. Chang, Y.C. Chang, Y.J. Lee, J. Kwo, C.C. Tsai, J.M. Hong, C.-H. Hsu, and M. Hong, J. Cryst. Growth **311**, 2183 (2009).

- <sup>51</sup> W.H. Chang, P. Chang, T.Y. Lai, Y.J. Lee, J. Kwo, C.-H. Hsu, and M. Hong, Cryst. Growth Des. **10**, 5117 (2010).

- <sup>52</sup> H.-C. Chiu, C.-W. Lin, C.-H. Chen, C.-W. Yang, C.-K. Lin, J.S. Fu, L.-B. Chang, R.-M. Lin, and K.-P. Hsueh, J. Electrochem. Soc. **157**, H160 (2010).

- <sup>53</sup> J.S. Jur, V.D. Wheeler, M.T. Veety, D.J. Lichtenwalner, D.W. Barlage, and M.A.L. Johnson, in *CS MANTECH Conf. 2008, Chicago*, (2008), pp. 17–20.

- <sup>54</sup> E. Cicerrella, J.L. Freeouf, L.F. Edge, D.G. Schlom, T. Heeg, J. Schubert, and S.A. Chambers, J. Vac. Sci. Technol. A Vacuum, Surfaces, Film. 23, 1676 (2005).