#### TRANSISTOR CIRCUIT DESIGN

by

### DUANE SCHULTZE LUNDY

B. S., Kansas State University, 1959

A MASTER'S REPORT

submitted in partial fulfillment of the

requirements for the degree

MASTER OF SCIENCE

Department of Electrical Engineering

KANSAS STATE UNIVERSITY Manhattan, Kansas

1963

Approved by:

Major Professor

LD 2668 K4 1913

Doctu

# TABLE OF CONTENTS

| ments                                  |

|----------------------------------------|

| INTRODUCTION                           |

| EQUIVALENT CIRCUIT                     |

| Equivalent Circuit Analysis            |

| Common Emitter Configuration           |

| Common Collector Configuration         |

| Common Base Configuration              |

| Definitions of Transistor Parameters   |

| Determination of B                     |

| Determination of Re                    |

| Determination of R <sub>b</sub>        |

| Determination of Ce                    |

| Determination of $C_{f c}$             |

| Determination of $R_c$                 |

| Determination of h <sub>fe</sub>       |

| Table of Equivalent Circuit Parameters |

| NEGATIVE FEEDBACK                      |

| Voltage Feedback                       |

| Current Feedback                       |

| HIGH-FREQUENCY AMPLIFICATION           |

| Derivation of Figure of Merit 4        |

| Alternate Equivalent Circuits 5        |

| NEUTRALIZATION                         |

| Isolation by Neutralization 5          |

| Isolation by Mismatch 6                |

| BIAS  | CONSIDE | RATION | IS Al | VD  | TEMP | ERAT          | URE | 1 | FFF | EC | TS | 5 | ٠ | • | • | • | • | • | • | 73 |

|-------|---------|--------|-------|-----|------|---------------|-----|---|-----|----|----|---|---|---|---|---|---|---|---|----|

|       | Leakage | Curre  | ent E | Eve | luat | ion           | •   | • | •   | •  | •  | • |   |   | • | • | • | • | • | 73 |

|       | Bias St | abili: | zatio | on  | Tech | ni <b>q</b> u | 9 3 | • | ٠   | •  |    | • | • |   | ٠ | • |   | • | • | 79 |

| BIBLI | OGRAPHY |        |       |     |      |               | •   |   | ٠   |    |    |   |   | • |   | • | ٠ | ø |   | 88 |

#### INTRODUCTION

One problem that is prevalent in the design of any circuit that contains an active element is the proper representation of the active element by an equivalent circuit. The equivalent circuit for the electronic vacuum tube is well established and is the foundation for most beginning electronic textbooks. The parameters that make up the equivalent circuit can, in most cases, be taken directly from the manufacturer's data sheet, and the operation of the tube can be predicted quite accurately from the equivalent circuit.

There are special cases where the basic equivalent circuit is no longer an accurate representation of the tube. One such case is in the upper useful frequency range of the tube where phenomena such as transit time effects take place. In this frequency range the basic equivalent circuit is no longer accurate and must be revised to include the special effects.

In this report a basic equivalent circuit for the junction transistor is presented. The equivalent circuit is analogous to that of the vacuum tube in that it is relatively simple and the parameters can be taken directly from the manufacturer's data sheet or calculated using some simple relationships.

The transistor parameters specified by the manufacturer usually have a wide range in value, and in many cases the parameters are not adequately specified. It is up to the design engineer to approximate the parameter not adequately specified and to design the circuit to the specification at least to the first

approximation. It is in making these calculations that the equivalent circuit presented performs its most useful function. The equivalent circuit is useful as a first approximation to determine if the circuit meets the design specifications whether an upper or lower limit transistor is used.

This report does not discuss the physical action that takes place in the transistor that determines the parameter. There are many sources available where the subject is developed thoroughly. 2,3,4

This report deals only with small signal (linear) applications of the transistor. The equivalent circuit, and the equations derived from the circuit, are utilized to analyze certain specific transistor applications. The applications analyzed include: (a) negative feedback, (b) high-frequency considerations, including neutralization of the transistor, and (c) bias consideration.

The transistor parameters are usually specified by giving a maximum, minimum, and typical value. Upper and lower limits mean the maximum and minimum values of the parameter specified.

<sup>&</sup>lt;sup>2</sup>W. Shockley, "The Theory of P-N Junctions in Semiconductors and P-N Junction Transistors," Bell System Technical Journal, vol. 28, pp. 435-489, July, 1949.

<sup>&</sup>lt;sup>3</sup>A. Lo, R. Endres, J. Zawels, F. Waldhauer, C. Cheng, Transistor <u>Electronics</u>, Prentice-Hall, Inc., Englewood Cliffs, N. J., pp. 272-309.

<sup>&</sup>lt;sup>4</sup>L. Giacoletto, "Study of P-N-P Alloy Junction Transistor through Medium Frequencies," RCA Review, vol. 14, pp. 506-562, December, 1954.

#### EQUIVALENT CIRCUIT

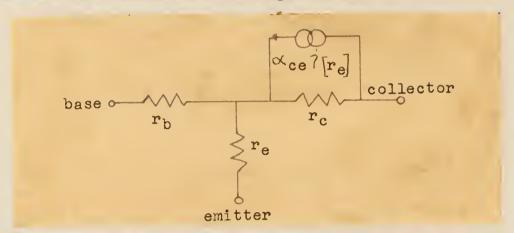

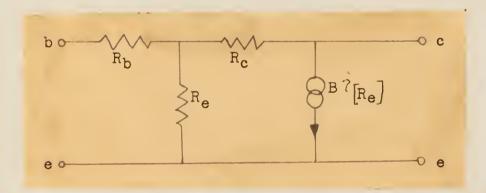

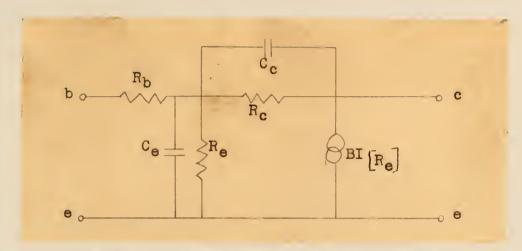

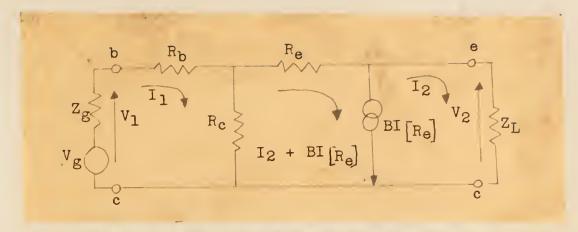

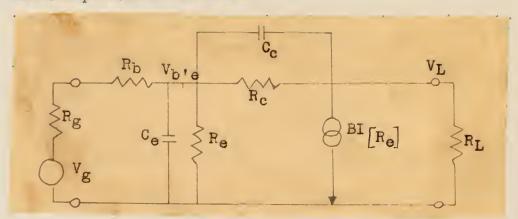

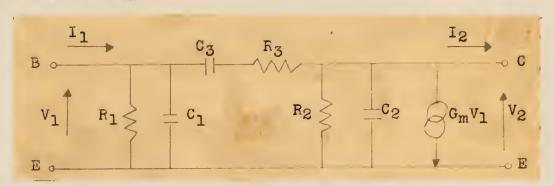

There are two forms of the basic equivalent circuit discussed, the bridged-T and the hybrid-w. The low-frequency forms of the two are illustrated in Figs. 1 and 2.

Fig. 1. Low-frequency bridged-T equivalent circuit.

Fig. 2. Low-frequency hybrid-π equivalent circuit.

The T-equivalent circuit is the basic equivalent circuit used extensively in the literature (for example, see Lo, et al.). The notation,  $7[r_{\Theta}]$ , used in the equivalent circuit indicates the

<sup>&</sup>lt;sup>1</sup>A. Lo, R. Endres, J. Zawels, F. Waldhauer, C. Cheng, Transistor Electronics, Prentice-Hall, Inc., Englewood Cliffs, N. J., p. 43.

current flowing through the resistor in the brackets. To further clarify  $B7R_e$  means B times the current flowing through  $R_e$ .

The definition of the parameter and their dependency (if any) on other parameters for the -T equivalent are as follows.

rh - Base Spreading Resistance

This resistance represents the resistance of the material from which the base is made.  $r_b$  is sometimes referred to as the base connection resistance or the extrinsic base resistance. Typical values of  $r_b$  are from five ohms for a power transistor to several hundred ohms for small power units. This parameter is essentially independent of voltage and current but has a positive temperature coefficient of approximately 0.7 per cent per degree C.

re - Intrinsic Emitter Resistance

There is a direct relationship between the emitter resistance  $r_e$  and emitter current  $I_e$ . The relationship is given by  $r_e = K/(I_e$  in  $M_a$ ), where K is a constant with the dimension of millivolts, and ( $I_e$  in  $M_a$ ) is the emitter d-c bias current in milliamperes. For most transistors K=26 is a good approximation. 1,2 Temperature, collector voltage, and collector current have little effect on this parameter.

lIbid., p. 288.

2P. Jochems, O. Memelink, L. Tummers, "Construction and Electrical Properties of a Germanium Alloy-diffused Transistor," Proceedings of the IRE, vol. 46, no. 6, p. 1162, June, 1958.

### rc - Collector Resistance

The value of  $r_c$  is primarily determined by the surface resistance across the base to collector junction.  $r_c$  can also be defined as the inverse slope of  $I'_{co}$  (leakage current) with collector voltage. Typical values of  $r_c$  are from a few thousand ohms to hundreds of megohms for low-power silicon devices.

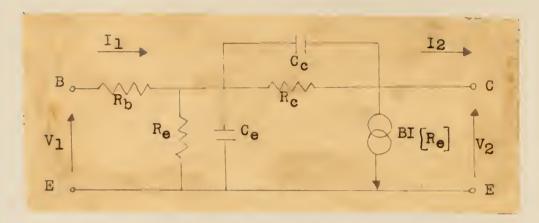

The hybrid- $\pi$  equivalent circuit can be derived from the T-equivalent circuit by writing equations for both and relating equivalent terms.

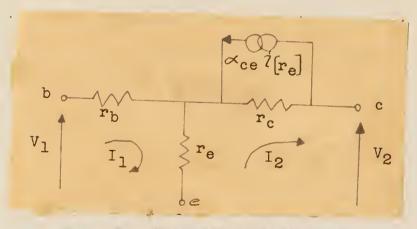

Fig. 3. T-equivalent circuit.

Using loop current analysis and writing equations for the input and output voltage for the T-equivalent circuit yields:

$$V_1 = I_1(r_b + r_e) - I_2r_e$$

(1)

$$-V_2 = -I_1 r_e + I_2 (r_e + r_c) + \propto_{ce} ? |r_e| r_c$$

(2)

The current through re is

$$?[\mathbf{r}_{e}] = \mathbf{I}_{1} - \mathbf{I}_{2} \tag{3}$$

Substituting Eq. (3) into Eq. (2) yields

$$-V_2 = -I_1(r_e - \propto_{ce} r_c) + I_2(r_e + r_c [1 - \propto_{ce}])$$

(4)

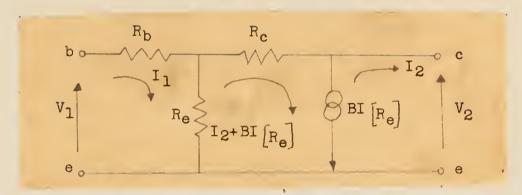

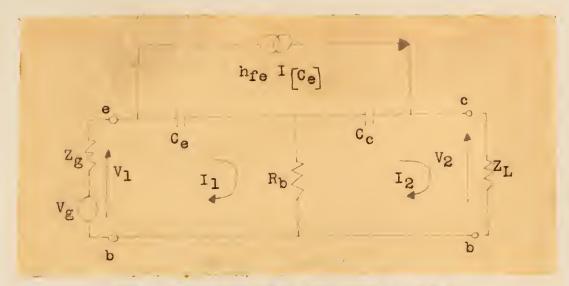

Fig. 4. w-equivalent circuit.

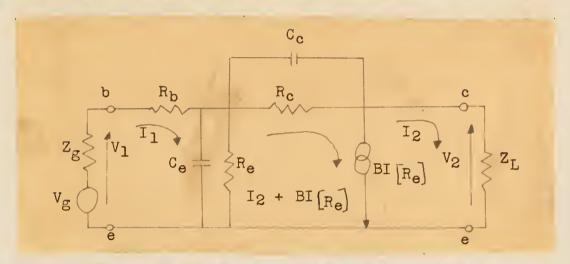

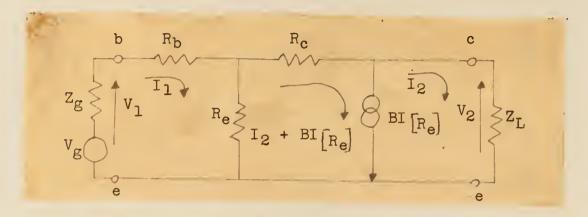

The expressions for the input and output voltages for the hybrid π-equivalent circuit are:

$$V_1 = I_1(R_b + R_e) - (I_2 + BI[R_e])R_e$$

(5)

$$-V_2 = -I_1(R_e) + (I_2 + BI[R_e])(R_e + R_c)$$

(6)

The current through Re is

$$I\left[R_{\Theta}\right] = \frac{I_1}{1+B} - \frac{I_2}{1+B} \tag{7}$$

Substituting Eq. (7) into Eqs. (5) and (6) yields

$$V_1 = I_1(R_b + \frac{R_e}{1+B}) - I_2 \frac{R_e}{1+B}$$

(8)

$$-V_2 = -I_1(\frac{R_e}{1+B} - \frac{BR_e}{1+B}) + I_2(\frac{R_e}{1+B} + \frac{R_e}{1+B})$$

(9)

By comparing Eqs. (1) and (4) with Eqs. (8) and (9), the following relations are obtained.

$$\mathbf{r}_{b} = R_{b} \tag{10}$$

$$r_{e} = \frac{R_{e}}{1 + B} \tag{11}$$

$$\propto_{ce} = \frac{B}{1 + B}$$

(12)

From Eq. (12), B can be determined as

$$B = \frac{\propto_{ce}}{1 - \propto_{ce}}$$

(13)

and since  $1>\infty_{\rm ce}>\cdot$  9, B>>1.

B is defined as the low-frequency, or d-c, short-circuit current gain between base and collector. The relationship between the low-frequency and d-c short-circuit current gain is discussed further in a later section.

From Eq. (10), Re can be determined.

$$R_e = r_e(1 + B) , B >> 1$$

(14)

$$R_{e} = Br_{e} \tag{15}$$

The definitions given previously for the T-equivalent circuit apply to the parameter for the  $\pi$ -equivalent circuit if the correct conversion factors stated above are used.

The hybrid m-equivalent circuit is the most useful of the two equivalent circuits presented, and will be used as the basis equivalent circuit for the remainder of this report.

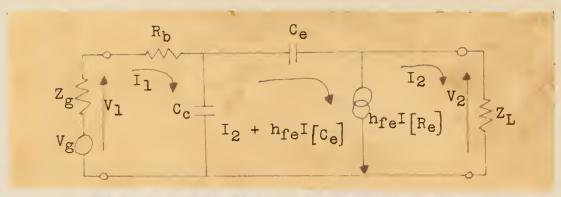

The equivalent circuit thus far developed is useful only for low-frequency application. To extend the usefulness of the equivalent circuit to higher frequencies, reactive elements must be included to represent the variations of the transistor parameters with frequency. Figure 5 is the final equivalent circuit

Fig. 5. Hybrid w-equivalent circuit.

which is useful to the first approximation over the major portion of the transistor frequency range. The equivalent circuit is similar to those developed in the literature 1,2,3, but with approximation made to eliminate the parameters which have little effect on the overall characteristics of the transistor. As is the case of the resistive components, the values of capacitances can be taken directly from the manufacturer's data sheet or calculated, as shown later under definitions of transistor parameters.

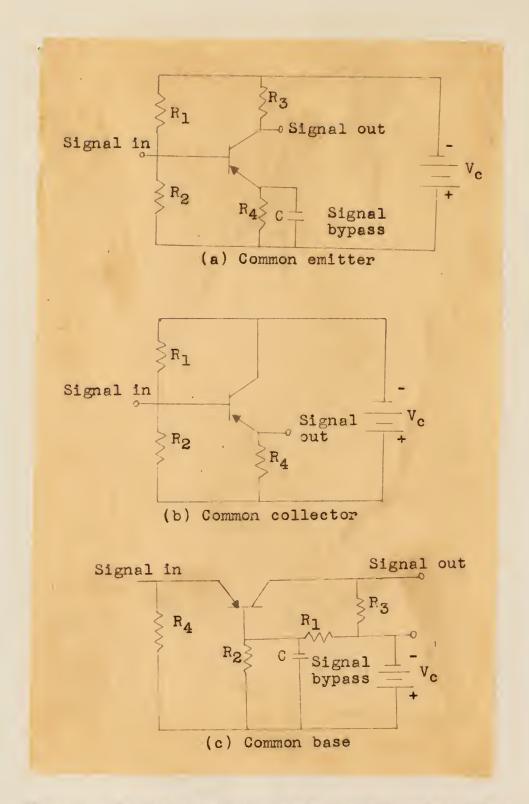

Before elaborating on the frequency dependent parameters, the transfer matrix shall be determined from the equivalent circuit for the three basic configurations: common emitter, common collector, and common base. Approximations will also be made to

lE. Wolfendule, The Junction Transistor and Its Application, The Macmillan Company, New York, 1958, pp. 103-111.

2P. Jochems, O. Memelink, L. Tummers, "Construction and Electrical Properties of a Germanium Alloy-diffused Transistor," Proceedings of the IRE, vol. 46, no. 6, p. 1162, June, 1958.

3L. Giacoletto, "Study of P-N-P Alloy Junction Transistor from D-c Through Medium Prequencies," RCA Review, vol. 14, p. 561, December, 1954.

simplify the matrices for low and high frequencies. From the transfer matrix the voltage gain, current gain, input impedance, and output impedance will be determined.

### Equivalent Circuit Analysis

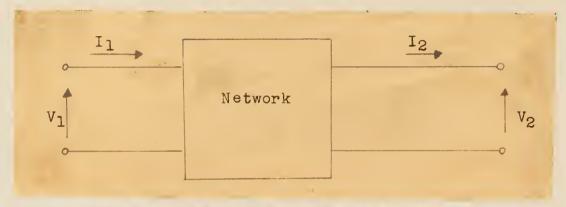

To illustrate the method of analysis using the transfer matrix, a general case is given below.

Fig. 6. General four-terminal network.

For any four-terminal network the following equations can be derived:

$$V_1 = AV_2 + BI_2 \tag{16}$$

$$I_1 = CV_2 + DI_2 \tag{17}$$

The transfer matrix can be written directly from Eqs. (16) and (17).

$$\begin{vmatrix} \mathbf{v_1} \\ \mathbf{I_1} \end{vmatrix} = \begin{vmatrix} \mathbf{A} & \mathbf{B} \\ \mathbf{C} & \mathbf{D} \end{vmatrix} \begin{vmatrix} \mathbf{v_2} \\ \mathbf{I_2} \end{vmatrix} \tag{18}$$

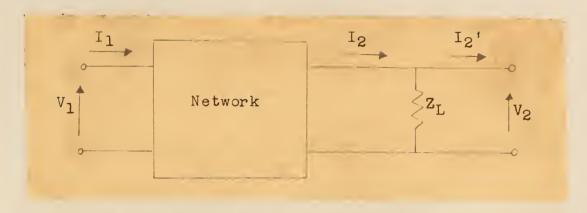

For the purpose of deriving the voltage gain, current gain, input impedance, and output impedance, the general network shown in Fig. 6 is modified as shown in Fig. 7.

Fig. 7. General four-terminal network terminated by a load impedance.

Writing the transfer matrix for the two cascaded networks shown in Fig. 7 yields

$$\begin{vmatrix} \mathbf{v_1} \\ \mathbf{I_1} \end{vmatrix} = \begin{vmatrix} \mathbf{A} & \mathbf{B} \\ \mathbf{C} & \mathbf{D} \end{vmatrix} \begin{vmatrix} \mathbf{1} & \mathbf{0} \\ \mathbf{1/Z_L} & \mathbf{1} \end{vmatrix} \begin{vmatrix} \mathbf{v_2} \\ \mathbf{I'_2} \end{vmatrix}$$

(19)

Carrying out the matrix multiplication and setting  $I'_2 = 0$ , since there is no load on terminal 3, yields

$$\begin{vmatrix} v_1 \\ I_1 \end{vmatrix} = \begin{vmatrix} A + B/Z_L & B \\ C + D/Z_L & D \end{vmatrix} = \begin{vmatrix} A + B/Z_L & B \\ 0 \end{vmatrix}$$

(20)

Solving Eq. (20) for the voltage gain gives

$$K_{V} = \frac{V_{2}}{V_{1}} = \frac{1}{A + B/Z_{L}}$$

(21)

Letting  $V_2 = I_2 Z_L$  in Eq. (20) and solving for the current gain gives

$$K_{1} = \frac{I_{2}}{I_{1}} = \frac{1}{CZ_{L} + D}$$

(22)

Again using the relationship that  $V_2 = I_2 Z_L$  and using Eqs. (21) and (22), the input impedance can be determined.

$$Z_{in} = \frac{K_1 Z_L}{K_V} = \frac{AZ_L + B}{CZ_L + D}$$

(23)

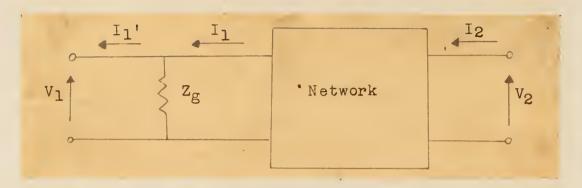

To determine the output impedance when the input is terminated by an impedance, the network shown in Fig. 8 is used.

Fig. 8. General four-terminal network with the input terminated by an impedance.

The output impedance can be found by taking the inverse of the transfer matrix for the four-terminal network and applying the same rules that were applied for finding the input impedance. The output impedance is given by

$$Z_{o} = \frac{DZ_{g} + B}{CZ_{g} + A}$$

(24)

These relationships will be used to derive the pertinent design equations using the basic equivalent circuit (Fig. 5), arranged in the desired configuration. The equations describing the common emitter configuration are derived in detail to illustrate the method. The equations describing the common collector and common base configurations are stated without proof since the method of deriving them is identical to that of the common emitter case.

### Common Emitter Configuration

The transfer matrices will be determined using the loop current method, starting with the common emitter configuration.

Fig. 9. Hybrid π-equivalent circuit for common emitter configuration.

Referring to Fig. 9 the equation for input voltage  $V_1$  and output voltage  $V_2$  can be written as:

$$V_1 = I_1(R_b + Z_e) - (I_2 + BI_{R_e})Z_e$$

(25)

$$-V_2 = -I_1(Z_e) + (I_2 + BI_{R_e})(Z_e + Z_c)$$

(26)

where

$$Z_{e} = \frac{R_{e} \frac{1}{PC_{e}}}{R_{e} + \frac{1}{PC_{e}}}, \quad Z_{c} = \frac{R_{c} \frac{1}{PC_{c}}}{R_{c} + \frac{1}{PC_{c}}}$$

(27)

and P = jw.

The current through the resistance Re is:

$$I[R_{\Theta}] = (I_1 - [I_2 + BI[R_{\Theta}]]) \frac{Z_{\Theta}}{R_{\Theta}}$$

Solving for I Re | yields

$$I[R_e] = \frac{Z_e}{R_e + BZ_e} I_1 - \frac{Z_e}{R_e + BZ_e} I_2$$

(28)

Substituting Eq. (28) into Eqs. (25) and (26) gives new expressions for  $V_1$  and  $V_2$ .

$$V_1 = I_1 \left( \frac{R_e R_b + R_e Z_e + B Z_e R_b}{R_e + B Z_e} \right) - I_2 \frac{R_e Z_e}{R_e + B Z_e}$$

(29)

$$-V_{2} = I_{1} \left( \frac{BZ_{e}Z_{c} - Z_{e}R_{e}}{R_{e} + BZ_{e}} \right) + I_{2} \left( \frac{Z_{e}R_{e} + Z_{c}R_{e}}{BZ_{e}Z_{c} - Z_{e}R_{e}} \right)$$

(30)

Solving for I1 in Eq. (30) yields

$$I_1 = -V_2 \left( \frac{R_e + BZ_e}{BZ_eZ_c - Z_eR_e} \right) - I_2 \left( \frac{Z_eR_e + Z_cR_e}{BZ_eZ_c - Z_eR_e} \right)$$

(31)

Substituting Eq. (31) in Eq. (29) and solving for V1 yields,

$$V_{1} = -V_{2}(\frac{R_{e}R_{b} + R_{e}Z_{e} + BZ_{e}R_{b}}{BZ_{e}Z_{c} - Z_{e}R_{e}}) - I_{2}(\frac{R_{e}Z_{e}Z_{c} + R_{e}Z_{e}R_{b} - R_{b}R_{e}Z_{c}}{BZ_{e}Z_{c} - Z_{e}R_{e}})$$

(32)

The transfer matrix can be written directly from Eqs. (31) and (32).

$$\begin{vmatrix} v_1 \\ = & -\frac{R_e R_b + R_e Z_e + B Z_e R_b}{B Z_e Z_e} - \frac{R_e Z_e Z_e + Z_e R_e R_b + Z_e R_b R_e}{B Z_e Z_e - Z_e R_e} \end{vmatrix} v_2$$

$$= \begin{vmatrix} R_e + B Z_e \\ -\frac{R_e + B Z_e}{B Z_e Z_e - R_e Z_e} - \frac{Z_e R_e + Z_e R_e}{B Z_e Z_e - Z_e R_e} \end{vmatrix} v_2$$

(33)

By comparing the transfer matrix of Eq. (24) with that of the general case given in Eq. (18), the following relationships are evident.

$$A = -\frac{R_e R_b + R_e Z_e + B Z_e R_b}{B Z_e Z_c - R_e Z_e}$$

(34)

$$B = -\frac{R_{e}Z_{e}Z_{c} + Z_{e}R_{e}R_{b} + Z_{c}R_{b}R_{e}}{BZ_{e}Z_{c} - R_{e}Z_{e}}$$

(35)

$$C = -\frac{R_e + BZ_e}{BZ_eZ_c - R_eZ_e}$$

(36)

$$D = -\frac{Z_e R_e + Z_c R_e}{BZ_e Z_c - Z_e R_e}$$

(37)

The voltage gain for the common emitter configuration is determined by using the relationship given in Eq. (21).

$$K_{ve} = -\frac{Z_{L}Z_{e}(B Z_{c} - R_{e})}{R_{e}Z_{e}Z_{c} + R_{e}Z_{e}Z_{L} + BR_{b}Z_{L}Z_{e} + R_{e}Z_{e}R_{b}}$$

$$+R_{e}R_{b}Z_{c} + R_{b}R_{e}Z_{L}$$

(38)

The current gain for the common emitter configuration is determined by using Eq. (22).

$$K_{ie} = -\frac{Z_{e}(BZ_{c} - R_{e})}{R_{e}(Z_{c} + Z_{L} + Z_{e}) + BZ_{L}Z_{e}}$$

(39)

The input impedance for the common emitter configuration is determined by using Eq. (23).

$$Z_{in_e} = R_b + \frac{(Z_c + Z_L)Z_eR_e}{R_eZ_e + BZ_LZ_e + R_eZ_c + R_eZ_L}$$

(40)

The output impedance for the common emitter configuration is determined by using Eq. (24).

$$Z_{oe} = \frac{(Z_{e}R_{e} + Z_{e}R_{e})Z_{g} + Z_{e}R_{e}Z_{e} + Z_{e}R_{b}R_{e} + Z_{e}R_{b}R_{e}}{Z_{g}(R_{e} + BZ_{e}) + R_{e}R_{b} + R_{e}Z_{e} + BZ_{e}R_{b}}$$

(41)

The low-frequency transfer matrix can be determined in a manner equivalent to that of the general case.

The low-frequency common emitter transfer matrix can be determined to be:

Fig. 10. Hybrid-π low-frequency common emitter equivalent circuit.

$$\begin{vmatrix} V_{1} \\ -\frac{(1+B)R_{b}+R_{e}}{BR_{c}-R_{e}} - \frac{R_{e}R_{b}+R_{c}R_{b}+R_{c}R_{e}}{BR_{c}-R_{e}} \end{vmatrix} V_{2}$$

$$= \frac{1+B}{BR_{c}-R_{e}} - \frac{R_{e}+R_{c}}{BR_{c}-R_{e}} \qquad I_{2}$$

The voltage gain  $K_{\rm v}$  can be calculated using the relationship given in Eq. (21).

$$K_{Ve} = -\frac{R_{L}(BR_{c} - R_{e})}{R_{L}([1 + B]R_{b} + R_{e}) + R_{e}R_{b} + R_{c}R_{e}}$$

(43)

In the general case  $R_c >> R_e$ , B >> 1.

$$K_{ve} \simeq -\frac{BR_L R_c}{R_L(BR_b + R_e) + R_c(R_e + R_b)}$$

In most practical cases R<sub>c</sub> >> R<sub>L</sub>.

$$K_{\text{ve}} \simeq -\frac{BR_{\text{L}}}{R_{\text{e}} + R_{\text{b}}} \tag{44}$$

The current gain  $K_i$  can be calculated using the relationship given in Eq. (22).

$$K_{ie} = -\frac{BR_c - R_e}{(1 + B)R_L + R_e + R_c}$$

(45)

In all cases  $R_c >> R_e$ , B >> 1. Therefore  $K_7$  reduces to

$$K_{\gamma e} \simeq -\frac{BR_{c}}{BR_{L} + R_{c}} \tag{46}$$

The current gain with the output short circuited will be of interest later. Therefore setting  $R_{\rm L}$  equal to zero, the short-circuit current gain can be found to be

$$K_{je} \simeq -B$$

short-circuit current gain (47)

The low-frequency common emitter input impedance for the equivalent circuit is

$$R_{in_e} = R_b \frac{(R_c + R_L)R_e}{R_e + BR_L + R_c + R_L}$$

(48)

As before,  $R_c >> R_L$ ,  $R_c >> R_e$ .

$$R_{\text{ine}} \simeq R_{\text{b}} + \frac{R_{\text{c}}R_{\text{e}}}{R_{\text{c}} + BR_{\text{L}}} \tag{49}$$

The input impedance with the output short circuited will be of interest later, so setting  $R_{\rm L}$  equal to zero the short-circuit input impedance can be found to be

$$R_{\rm in_e} \simeq R_b + R_e$$

short-circuit input impedance (50)

The low-frequency common emitter output impedance for the equivalent circuit is

$$R_{\text{out e}} = \frac{(R_e + R_c)R_g + R_e R_c + R_e R_b + R_b R_e}{R_g (1 + B) + R_b (1 + B) + R_e}$$

(51)

The output impedance with the input open circuited is

$$R_{\text{out e}} \simeq \frac{R_{\text{e}} + R_{\text{c}}}{B}$$

open-circuit output impedance (52)

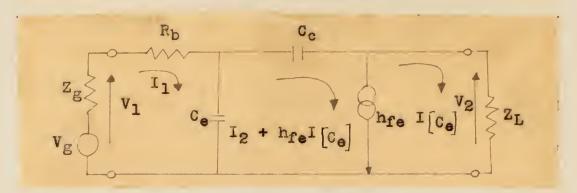

The transfer matrix for the high-frequency common emitter equivalent circuit can be determined using the same method as that used in the general case.

Fig. 11. Hybrid-w high-frequency common emitter equivalent circuit.

This equivalent circuit is useful in the frequency range where  $\left|\frac{1}{PC_e}\right|<< R_e$  and  $\left|\frac{1}{PC_c}\right|<< R_c$ . Also the parameter,  $h_{fe}$ , introduced in Fig. 11 will be defined as  $B = \frac{Z_e}{R_c}$ .

$$h_{fe} = B \frac{Z_e}{R_e} \quad \text{or} \quad B \frac{1}{1 + PC_e R_e}$$

(53)

The transfer matrix for the high-frequency equivalent circuit is

$$\begin{vmatrix} v_1 \\ -\frac{(1+h_{fe})R_b+X_e}{h_{fe}X_c-X_e} - \frac{X_eR_b+X_cR_b+X_cX_e}{h_{fe}X_c-X_e} \end{vmatrix} v_2$$

$$= \frac{1_1}{h_{fe}X_c-X_e} - \frac{X_e+Y_c}{h_{fe}X_c-X_e} \qquad I_2$$

In practically all cases of interest  $X_c > X_e$ , where  $X_c = \frac{1}{PC_c}$  and  $X_e = \frac{1}{PC_e}$ . Using this approximation the voltage gain,  $X_c = \frac{1}{PC_e}$ . Where  $X_c = \frac{1}{PC_e}$  and  $X_c = \frac{1}{PC_e}$  and  $X_c = \frac{1}{PC_e}$ .

Zout are as follows:

$$K_{ve} = -\frac{h_{fe} X_c Z_L}{([1 + h_{fe}]R_b + X_e)Z_L + (R_b + X_e)X_c}$$

(55)

$$K_{ie} = -\frac{h_{fe} X_{c}}{(1 + h_{fe})Z_{L} + X_{c}}$$

(56)

$$Z_{ine} = R_b + \frac{(X_c + Z_L)X_e}{X_c + Z_L(1 + h_{fe})}$$

(57)

$$Z_{\text{out e}} = \frac{X_c Z_g + X_c (X_e + R_b)}{(1 + h_{fe}) Z_g + (1 + h_{fe}) R_b + X_e}$$

(58)

The output impedance with the input open circuited will be of interest later.

$$Z_{\text{out e}} \simeq \frac{X_{\text{c}}}{1 + h_{\text{fe}}}$$

output impedance with input open circuited (59)

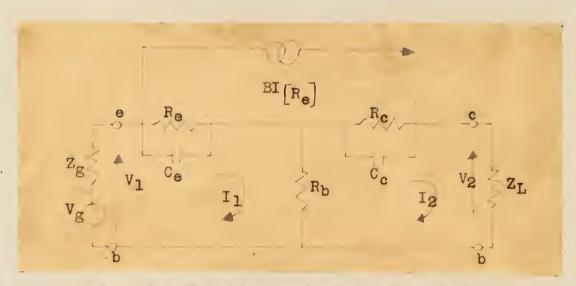

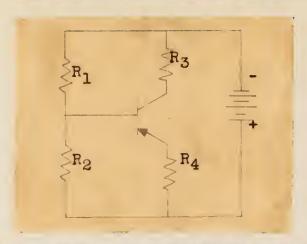

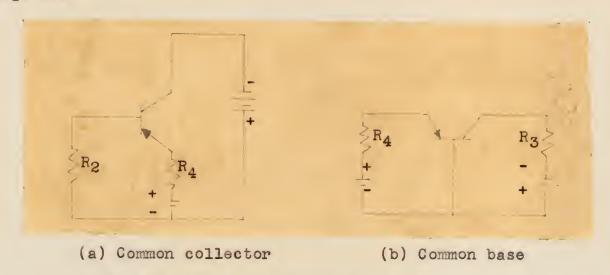

## Common Collector Configuration

Figure 12 is the equivalent circuit in the common collector configuration. The transfer matrix and the equations of interest will be stated without proof since the method of determining these is identical with that used for the common emitter case.

Common collector transfer matrix:

Common collector voltage gain:

$$K_{vc} = \frac{Z_{L}Z_{c}(R_{e} + BZ_{e})}{(R_{b}+Z_{c})(R_{e}+BZ_{e})Z_{L} + R_{e}(Z_{c}R_{b}+ Z_{e}R_{b}+ Z_{c}Z_{e})}$$

(61)

Fig. 12. Hybrid-w equivalent circuit for the common collector configuration.

Common collector current gain:

$$K_{fe} = \frac{Z_{c}(BZ_{e} + R_{e})}{BZ_{e}Z_{L} + R_{e}(Z_{c} + Z_{e} + Z_{L})}$$

(62)

Common collector input impedance:

$$Z_{in_c} = R_b + \frac{Z_L Z_c (R_e + BZ_e) + Z_c Z_e R_e}{Z_c R_e + Z_e R_e + Z_L (R_e + BZ_e)}$$

(63)

Common collector output impedance:

$$Z_{\text{out}_{\mathbf{c}}} = \frac{(Z_{\mathbf{c}}[Z_{\mathbf{g}} + R_{\mathbf{b}}] + Z_{\mathbf{e}}[Z_{\mathbf{g}} + Z_{\mathbf{e}} + Z_{\mathbf{c}}])R_{\mathbf{e}}}{(Z_{\mathbf{g}} + R_{\mathbf{b}} + Z_{\mathbf{e}})(R_{\mathbf{e}} + BZ_{\mathbf{e}})}$$

(64)

Low-frequency common collector transfer matrix:

Fig. 13. Hybrid-π low-frequency common collector equivalent circuit.

Low-frequency common collector voltage gain:

$$K_{ve} = \frac{R_{L}R_{e}(1+B)}{(R_{b}+R_{c})(1+B)R_{L}+R_{c}R_{b}+R_{e}R_{b}+R_{c}R_{e}}$$

(66)

Using the valid approximations that  $R_c >> R_e$ ,  $R_L >> R_e$  and B >> 1.

$$K_{ve} \simeq 1$$

(67)

Low-frequency common collector current gain:

$$K_{ic} = \frac{R_{c}(1+B)}{BR_{L} + R_{c} + R_{e} + R_{L}}$$

(68)

Using the approximations that  $R_c >> R_e$  and B >> 1:

$$K_{ie} \simeq \frac{BR_{c}}{BR_{L} + R_{c}} \tag{69}$$

Low-frequency common collector input impedance:

$$R_{in_e} = R_b + \frac{R_L R_e (1 + B) + R_e R_e}{R_c + R_e + (1 + B) R_L}$$

(70)

Using the approximations that B>>1,  $R_L>>R_e$ , and  $R_c>>R_e$ :

$$R_{inc} \simeq R_b + \frac{(R_e + BR_L)R_c}{R_c + BR_L}$$

(71)

Low-frequency common collector output impedance:

$$R_{out_c} = \frac{R_c(R_g + R_b) + R_e(R_g + R_e + R_c)}{(R_g + R_b + R_c)(1 + B)}$$

(72)

Using the approximations that  $R_c >> R_e$ ,  $R_c >> R_b$ ,  $R_c >> R_g$ ,  $R_g >> R_b$ , and B >> 1:

$$R_{\text{out}_{\mathbf{c}}} \simeq \frac{R_{\text{g}} + R_{2}}{R} \tag{73}$$

Fig. 14. Hybrid-π high-frequency common collector equivalent circuit.

High-frequency common collector transfer matrix:

$$\begin{vmatrix} v_1 \\ = \\ \frac{R_b + X_c}{X_c} & \frac{X_e(R_b + X_c) + X_cR_b}{X_c(1 + h_{fe})} \\ = \\ \frac{1}{X_c} & \frac{X_c + X_e}{X_c(1 + h_{fe})} \end{vmatrix} \qquad v_2$$

(74)

High-frequency common collector voltage gain:

$$K_{vc} = \frac{Z_{L}X_{c}(1 + h_{fe})}{(R_{b} + X_{c})(1 + h_{fe})Z_{L} + X_{c}R_{b} + X_{c}X_{e}}$$

(75)

using the approximations that  $X_c>>R_b,~X_c>>X_e,~$  and (1 +  $h_{fe})Z_L>>(R_b+X_e).$

$$K_{\rm VC} \simeq 1$$

(76)

.

High-frequency common collector current gain:

$$K_{ie} = \frac{X_{c}(1 + h_{fe})}{h_{fe}Z_{L} + X_{c} + X_{e} + Z_{L}}$$

(77)

Using the approximation that  $X_c > X_e$ :

$$K_{ie} \simeq \frac{X_c(1 + h_{fe})}{X_c + Z_L(1 + h_{fe})}$$

(78)

High-frequency common collector input impedance:

$$Z_{in_{\mathbf{c}}} = R_{b} + \frac{Z_{L}X_{c}(1 + h_{fe}) + X_{c}X_{e}}{X_{\mathbf{c}} + X_{e} + Z_{L}(1 + h_{fe})}$$

(79)

Using the approximations that  $X_c >> X_e$ ,  $Z_L >> X_e$ :

$$Z_{in_c} \simeq R_b + \frac{Z_L X_c (1 + h_{fe})}{X_c + Z_L (1 + h_{fe})}$$

(80)

High-frequency common collector output impedance:

$$Z_{\text{oute}} = \frac{X_{c}(Z_{g} + R_{b}) + X_{e}(Z_{g} + X_{e} + X_{c})}{(Z_{g} + R_{b} + X_{c})(1 + h_{fe})}$$

(81)

Using the approximations that  $X_c >> X_e$ ,  $Z_g >> R_b$ , and  $X_c >> Z_g$ .

$$Z_{\text{out}_{\mathbf{c}}} \simeq \frac{Z_{\mathbf{g}} + X_{\mathbf{e}}}{1 + h_{\mathbf{fe}}} \tag{82}$$

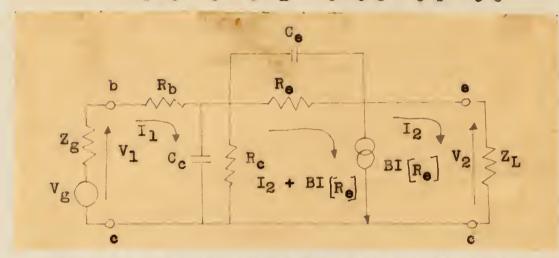

#### Common Base Configuration

Fig. 15. Hybrid-π equivalent circuit for the common base configuration.

Transfer matrix for the common base configuration:

$$V_{1} = \frac{R_{e}(Z_{e}+R_{b})+BZ_{e}R_{b}}{BZ_{e}Z_{c}+R_{b}(R_{e}+BZ_{e})} = \frac{R_{b}R_{e}Z_{e}+Z_{c}Z_{e}R_{e}+Z_{c}R_{b}R_{e}}{BZ_{e}Z_{c}+R_{b}(R_{e}+BZ_{e})} = V_{2}$$

$$= \frac{R_{e} + BZ_{e}}{BZ_{e}Z_{c}+R_{b}(R_{e}+BZ_{e})} = \frac{(R_{b}+Z_{c})(R_{e}+BZ_{e})}{BZ_{e}Z_{c}+R_{b}(R_{e}+BZ_{e})} = I_{2}$$

$$= \frac{R_{e} + BZ_{e}}{BZ_{e}Z_{c}+R_{b}(R_{e}+BZ_{e})} = \frac{(R_{b}+Z_{c})(R_{e}+BZ_{e})}{BZ_{e}Z_{c}+R_{b}(R_{e}+BZ_{e})} = I_{2}$$

Common base voltage gain:

$$K_{vb} = \frac{Z_{L}(BZ_{e}Z_{c} + R_{b}[R_{e} + BZ_{e}])}{Z_{L}(R_{e}[Z_{e}+R_{b}]+BZ_{e}R_{b})+R_{b}R_{e}Z_{e}+Z_{c}Z_{e}R_{e}+Z_{c}R_{b}R_{e}}$$

(84)

Common base current gain:

$$K_{\dot{\gamma}b} = \frac{B(Z_{e}Z_{c} + Z_{e}R_{b}) + R_{b}R_{e}}{(Z_{L} + Z_{c} + R_{b})(BZ_{e} + R_{e})}$$

(85)

Common base input impedance:

$$Z_{in_b} = \frac{R_b(Z_L R_e + Z_e R_e + BZ_e Z_L) + Z_e R_e (Z_L + Z_e + R_b)}{(Z_L + Z_e + R_b)(R_e + BZ_e)}$$

(86)

Common base output impedance:

$$Z_{\text{outb}} = \frac{Z_{\mathbf{c}}(BZ_{\mathbf{e}}Z_{\mathbf{g}} + Z_{\mathbf{g}}R_{\mathbf{e}} + Z_{\mathbf{e}}R_{\mathbf{e}} + R_{\mathbf{b}}R_{\mathbf{e}}) + BZ_{\mathbf{e}}Z_{\mathbf{g}}R_{\mathbf{b}} + Z_{\mathbf{g}}R_{\mathbf{b}} + Z_{\mathbf{e}}R_{\mathbf{b}}R_{\mathbf{e}} + Z_{\mathbf{e}}R_{\mathbf{b}}R_{\mathbf{e}}}{BZ_{\mathbf{e}}R_{\mathbf{b}} + BZ_{\mathbf{e}}Z_{\mathbf{g}} + Z_{\mathbf{g}}R_{\mathbf{e}} + Z_{\mathbf{e}}R_{\mathbf{e}} + R_{\mathbf{e}}R_{\mathbf{b}}}$$

(87)

Fig. 16. Hybrid-π low-frequency common base equivalent circuit.

Low-frequency common base voltage gain:

$$K_{vb} = \frac{R_{L}(BR_{c} + R_{b}[1 + B])}{R_{L}([R_{e} + R_{b}] + BR_{b}) + R_{b}R_{e} + R_{c}R_{e} + R_{c}R_{b}}$$

(88)

Using the approximations that R $_{f c}>>$  R $_{f b}$ , R $_{f c}>>$  R $_{f L}$

$$K_{\rm Vb} \simeq \frac{BR_{\rm L}}{R_{\rm e} + R_{\rm b}} \tag{89}$$

Low-frequency common base current gain:

$$K_{\{b\}} = \frac{B(R_c + R_b) + R_b}{(R_L + R_c + R_b)(1 + B)}$$

(90)

Using the approximations that  $R_c >> R_b$ ,  $R_c >> R_L$ , and B >> 1:

$$K_{b} \simeq 1$$

(91)

The current gain with the output short circuited is:

$$K_{ib} = \frac{B}{1 + B}$$

short-circuit current gain (92)

Low-frequency common base input impedance:

$$R_{in_b} = \frac{R_b(R_L + R_c + BR_L) + R_c(R_L + R_c + R_b)}{(R_L + R_c + R_b)(1 + B)}$$

(93)

Using the approximations that  $R_c >> R_L$ ,  $R_e >> R_b$ ,  $R_L >> R_b$ , and B >> 1:

$$R_{inb} \simeq \frac{R_e + R_b}{B} \tag{94}$$

This is also the approximate input impedance with the output short circuited which will be of use later.

Low-frequency common base output impedance:

$$R_{\text{outb}} = \frac{R_{c}(BR_{g}+R_{g}+R_{e}+R_{b})+BR_{g}R_{b}+R_{g}R_{b}+R_{b}R_{e}}{B(R_{g}+R_{b})+R_{g}+R_{e}+R_{b}}$$

(95)

Using the approximations that  $R_g >> R_b$ ,  $R_c >> R_e$ ,  $R_c >> R_b$ , and B >> 1:

$$R_{\text{outb}} = \frac{R_{\text{c}}(BR_{\text{g}} + R_{\text{e}})}{BR_{\text{g}} + R_{\text{e}}} = R_{\text{c}}$$

(96)

The low-frequency output impedance with the input opencircuited will be of interest later; this is

$$R_{\text{out}_{\text{b}}} = R_{\text{e}}$$

open-circuit current gain (97)

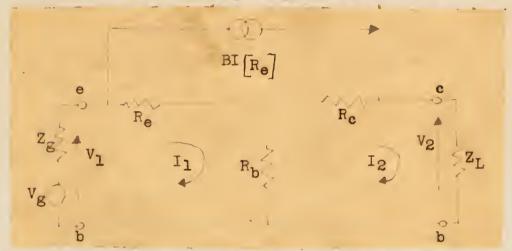

High-frequency common base transfer matrix:

Fig. 17. Hybrid-w common base high-frequency equivalent circuit.

High-frequency common base voltage gain:

$$K_{vb} = \frac{Z_{L}(h_{fe}X_{e} + R_{b}[1 + h_{fe}])}{Z_{L}(X_{e} + R_{b} + h_{fe}R_{b}) + R_{b}X_{e} + X_{c}X_{e} + X_{c}R_{b}}$$

(99)

Using the approximations that  $X_c >> R_b$  and  $X_c >> X_e$ :

$$K_{vb} \simeq \frac{h_{fe} X_{e} Z_{L}}{Z_{L} (X_{e} + R_{b} [h_{fe} + 1]) + X_{e} (R_{b} + X_{e})}$$

(100)

High-frequency common base current gain:

$$K_{ib} = \frac{h_{fe}(X_c + R_b) + R_b}{(Z_L + X_c + R_b)(1 + h_{fe})}$$

(101)

Using the approximation that  $X_c >> R_b$ :

$$K_{ib} \simeq \frac{h_{fe}X_{c}}{(Z_{L} + X_{c})(1 + h_{fe})}$$

(102)

High-frequency common base input impedance:

$$Z_{in_b} = \frac{R_b(Z_L + X_c + h_{fe}Z_L) + X_e(Z_L + X_c + R_b)}{(Z_L + X_c)(1 + h_{fe})}$$

(103)

Using the approximation that  $X_c >> R_b$ :

$$Z_{\text{inb}} \simeq \frac{R_{\text{b}}(Z_{\text{L}}[1 + h_{\text{fe}}] + X_{\text{c}}) + X_{\text{e}}(Z_{\text{L}} + X_{\text{c}})}{(Z_{\text{L}} + X_{\text{c}})(1 + h_{\text{fe}})}$$

(104)

The input impedance at very high frequencies with the output short-circuited will be of interest later; this is

$$Z_{inb} \simeq R_b$$

short-circuit input impedance (105)

High-frequency common base output impedance:

$$Z_{\text{outb}} = \frac{Z_{g}(h_{\text{fe}}X_{c} + X_{c} + h_{\text{fe}}R_{b} + R_{b}) + X_{c}X_{e} + X_{e}R_{b} + X_{c}R_{b}}{Z_{g}(h_{\text{fe}} + 1) + X_{e}R_{b}(1 + h_{\text{fe}})}$$

(106)

The output impedance with the input open-circuited will be of interest later; this is

$$Z_{out_b} \simeq X_c + R_b$$

open-circuit output impedance (107)

#### Definitions of Transistor Parameters

The equivalent circuits having been established, it is now necessary to determine the parameters from the manufacturer's data sheet. Listed below are the parameters usually given on a typical data sheet. In many cases some of the important parameters are missing but usually they can be estimated by utilizing some of the relationships thus far developed.

The configuration of the transistor that the parameter represents is denoted by subscripts. For example,  $h_{fe}$  is the common emitter forward current transfer ratio with the output ac short-circuited, while  $h_{fb}$  is the identical parameter for the common base configuration.

## Small Signal and High-frequency Parameters

- hob -- Common base output admittance, input ac open-circuited.

- hoe -- Common emitter output admittance, input ac open-circuited.

- h<sub>ib</sub> -- Common base input impedance, output ac short-circuited.

- h<sub>ie</sub> -- Common emitter input impedance, output ac short-circuited.

- h<sub>rb</sub> -- Common base reverse voltage transfer ratio, input ac open-circuited.

- hfb -- Common base -forward current transfer ratio, output ac short-circuited.

- hfe -- Common emitter forward current transfer ratio, output ac short-circuited.

- hfc -- Common collector forward current transfer ratio, output ac short-circuited.

- f<sub>xb</sub> Common base the frequency at which the magnitude of the small signal short-circuit forward current transfer ratio is 0.707 of its low-frequency value.

- f<sub>∞e</sub> Common emitter the frequency at which the magnitude of the small signal short-circuit forward current transfer ratio is 0.707 of its low-frequency value.

- fmax Maximum frequency of oscillation.

- Cob -- Collector to base capacitance measured across

the output terminals with the input ac open-circuited.

Coe -- Collector to emitter - capacitance measured across the output terminals with the input ac open-circuited.

r'b -- Base spreading resistance.

NF -- Noise figure.

Z<sub>1</sub> -- Input impedance.

Zo -- Output impedance.

Tq -- Operation temperature.

T; -- Junction temperature.

Tstg - Storage temperature.

# Direct-current Measurements

I<sub>C</sub>, I<sub>E</sub>, I<sub>B</sub> - Direct currents into collector, emitter, or base terminal.

$v_{CB}$ ,  $v_{EB}$  - Voltage collector to base, or emitter to base.

V<sub>CE</sub> -- Voltage collector to emitter.

${

m V}_{

m BE}$  -- Voltage base to emitter.

BV<sub>CBO</sub> - Breakdown voltage, collector to base junction reverse biased, emitter open-circuited (value of I<sub>c</sub> should be specified).

$V_{\rm CEO}$  - Voltage collector to emitter, at zero base current, with the collector junction reverse biased. Specify  $I_{\rm c}$ .

BV<sub>CEO</sub> - Breakdown voltage, collector to emitter, with base open-circuited. This may be a

- function of both 'm'' (the charge carrier multiplication factor) and the  $h_{\mbox{fb}}$  of the transistor. Specify  $I_{\mbox{c}}$ .

- $I_{E0}$ ,  $I_{EB0}$  Emitter current when emitter junction is reverse biased and collector is dc open-circuited.

- I<sub>CEO</sub> Collector current with collector junction reverse biased and base open-circuited.

- ICES Collector current with collector junction reverse biased and base shorted to emitter.

- I<sub>ECS</sub> Emitter current with emitter junction reverse biased and base shorted to collector.

- R<sub>SC</sub> -- Collector saturation resistance.

- Ico, IcBo Collector current when collector junction is reverse biased and emitter is dc open-circuited.

- hFE -- Common emitter direct-current transfer ratio, output short-circuited.

- hFB -- Common base direct-current transfer ratio, output short-circuited.

The methods of determining the equivalent circuit parameters from the data given on the manufacturer's data sheets are listed below.

#### Determination of B

Case 1. hfe given. hfe was defined as the forward current transfer ratio with the output ac short-circuited. This parameter

is usually specified by the manufacturer at a frequency well below the common emitter cut-off frequency. Referring to Eq. (47), it follows that B  $\simeq$  h<sub>fe</sub> if h<sub>fe</sub> is specified as being measured below the common emitter cut-off frequency  $f_{\infty}$ . In terms of the static characteristics h<sub>fe</sub> is defined as

$$h_{fe} = \frac{\partial I_C}{\partial I_B} \Big|_{V_C = C} = \frac{\text{limit}}{\triangle \to 0} \frac{\triangle I_C}{\triangle I_B}$$

where  $I_C$ ,  $I_B$ , and  $V_c$  are the direct-current values of the collector current, base current, and collector voltage respectively.

<u>Case 2.</u>  $h_{FE}$  given.  $h_{FE}$  was defined as the direct-current transfer ratio with the output short-circuited. There is little difference between  $h_{fe}$  and  $h_{FE}$  if  $h_{fe}$  is specified at a frequency well below its cut-off frequency  $f_{\infty,e}$ . This can be substantiated by comparing the values of  $h_{fe}$  and  $h_{FE}$  on data sheets that give both parameters. For making calculations to the first approximation, the following relationships are valid.

$$B \simeq h_{FE}$$

and  $h_{FE} \simeq h_{fe}$

Case 3.  $\propto_{ce}$  or  $h_{fb}$  given. Referring to Eqs.(12) and (92), B can be calculated using the relationship

$$B = \frac{\sim_{ce}}{1 - \sim_{ce}}$$

where  $\propto_{ce} = h_{fb}$ . The above relationship is true if  $h_{fb}$  or  $\propto_{ce}$  is specified at a frequency well below the common base cut-off frequency  $f_{\propto b}$ .

General Electric Transistor Manual, 3rd ed., General Electric Co., Semiconductor Products, 1224 W. Genesee St., Syracuse, New York, 1958.

### Determination of Re

$R_{e}$  can be estimated using the relationship  $R_{e}=\frac{B26}{I_{E}}$  in main all practical cases of interest.

### Determination of Rb

$\underline{\text{Case}}$  1.  $R_b$  is approximately equal to  $r_b$  so if  $r_b$  is given,  $R_b$  can be taken directly from the data sheet.

Case 2.  $r_b$  not given, but  $h_{ie}$  given. In practically all cases the frequency at which  $h_{ie}$  is measured is so low that the low-frequency equivalent circuit applies. Referring to Eq. (50), the equation for determining  $R_b$  can be derived.

$$R_b \simeq h_{\text{ie}} - \frac{\text{B26}}{I_{\text{E}} \text{ in ma}}$$

where  $I_{\mathbb{R}}$  in ma indicates the d-c emitter bias current in milli-amperes. The value of the d-c bias conditions for which any parameter is specified is usually given on the manufacturer's data sheet, and is used in the calculation of  $R_{\rm h}$ .

Case 3.  $r_b$  not given, but  $h_{ib}$  given. Referring to Eq. (94), the equation for determining  $R_b$  can be derived.

$$R_b \simeq B (h_{ib} - \frac{26}{I_E \text{ in ma}})$$

# Determination of Ce

This parameter can be determined knowing Re and f  $\propto$  e of f  $\propto$  b.

There is a fundamental relationship existing between  $f_{\ll e}$  and  $f_{\ll b}$ , this being  $f_{\ll e} = \frac{f_{\ll b}}{B+1}$ , or  $f_{\ll e} \simeq \frac{f_{\ll b}}{B}$ . This relationship can be derived from the equations for the common emitter current gain and the common base current gain. Equation (39) gives for the common emitter current gain

$$K_{ie} = -\frac{Z_e(BZ_c - R_e)}{R_e(Z_c + Z_L + Z_e) + BZ_LZ_e}$$

The expression with the output short circuited is of interest, and also at  $f_{\infty\,e}\ Z_c>>Z_e$  and  $Z_c>>R_e;$  therefore  $K_{ie}\simeq -\frac{BZ_e}{R_e}$ . Similarly for the common base case, simplifying Eq. (85) for the output short circuited yields  $K_{ib}\simeq \frac{BZ_e}{BZ_e+R_e}$ . Rewriting these equations in an alternate form and using the equivalent parameters listed under Definitions of Transistor Parameters, it follows that  $h_{fe}=\frac{B}{1+j\omega}\frac{C_eR_e}{C_eR_e}$ . The frequency at which  $h_{fe}$  is 0.707 of its value at low frequencies is defined as  $f_{\infty e};$  therefore  $\left|X_{ce}\right|=R_e$  at  $f_{\infty e}$  or  $f_{\infty e}=\frac{1}{2\pi C_eR_e}$ . The equivalent expressions for the common base case are

$$\begin{array}{l} h_{fb} = \dfrac{1}{1+B~j\omega~C_eR_e} ~~\text{and}~ f_{\infty b} = \dfrac{1}{2\pi~B~C_eR_e}~.~~\text{From this it is} \\ \text{obvious that}~ f_{\infty e} \simeq \dfrac{f_{\infty b}}{B}~\text{for the equivalent circuits developed.} \\ \text{The equations for finding $C_e$ are therefore $C_e$} = \dfrac{1}{2\pi~f_{\infty e}R_e}~\\ \text{or}~ C_e = \dfrac{B}{2\pi~f_{\infty b}R_e}~. \end{array}$$

# Determination of Cc

Cc can be estimated from the value given for Cob. The data

given for  $C_{ob}$  on the manufacturer's data sheet is a direct indication of the value of  $C_c$ , (refer to Eq. (107)).  $C_{ob}$  is a measured parameter and it includes some extrinsic capacitance, so  $C_{ob}$  is always greater than  $C_c$ . As an approximation  $C_c$  can be estimated to be  $14\mu$  F<sub>d</sub> less than the value given for  $C_{ob}$ .

# Determination of Rc

$R_c$  can be approximated when  $h_{oe}$  or  $h_{ob}$  is given on the data sheet.

Case 1.  $h_{0e}$  given. Referring to Eq. (52), the equation for the common emitter output impedance with the input open circuited was found to be  $R_{out}$   $c = \frac{R_e + R_c}{B}$  which is equal to  $\frac{1}{h_{0e}}$  in this case. Using the relationships already developed, the equation for  $R_c$  can be determined to be

$$R_c = \frac{B}{h_{oe}} - \frac{B26}{I_E \text{ in ma}} \text{ or } R_e \simeq \frac{B}{h_{oe}}$$

since

$$\frac{B}{h_{oe}} >> \frac{B26}{I_E \text{ in ma}}$$

in all cases.

Case 2. hob given. Using the same procedure as used above with reference to Eq. (97), Rc can be found to be Rc  $\simeq \frac{1}{h_{\rm ob}}$ .

# Determination of hfe

This parameter is equivalent to the one given on the data sheet. The problem is to determine its value at the frequency of interest. One method is to use the expression  $h_{\mbox{fe}} \simeq B \frac{Z_e}{R_e}$

where  $Z_{\theta}$  can be determined at the frequency of interest. Another method of determining  $h_{f\theta}$  is to use the approximation that  $h_{f\theta}$  decreases at a rate of approximately 6 db per octave from its value at  $f_{\propto \theta}$ .

## Table of Equivalent Circuit Parameters

Table 1 is a tabulation of the parameters that constitute the equivalent circuit and formulas useful in approximating these parameters from the manufacturer's data sheet.

Table 1. Approximate relationships between equivalent circuit parameters and parameters on manufacturer's data sheet.

| Equiva-                           | •                                          | Equations for                    | calculating                      |                          |

|-----------------------------------|--------------------------------------------|----------------------------------|----------------------------------|--------------------------|

| lent<br>circuit<br>param-<br>eter | : Di-<br>: rect :<br>: equiva-<br>: lent : | Common base                      | Common<br>emitter                | : Direct : calculation : |

| В                                 |                                            | ≪/1 -≪                           | h <sub>FE</sub>                  |                          |

| Rb                                | rb                                         | $B(h_{ib} - \frac{26}{I_E(ma)})$ | $h_{10} - \frac{B26}{I_{E}(ma)}$ |                          |

| Re                                |                                            | B                                | TE (IIII)                        | $B26/I_{\rm E}(ma)$      |

| Ce                                |                                            | w∝b Re                           | 1/w ce Re                        |                          |

| C <sub>e</sub>                    | Cob                                        | Cop                              |                                  |                          |

| $R_{\mathbf{c}}$                  |                                            | 1/h <sub>ob</sub>                | B/h <sub>oe</sub>                | Ze                       |

| hfe                               |                                            |                                  |                                  | B R <sub>e</sub>         |

#### NEGATIVE FEEDBACK

Negative feedback is of use in the design of transistor amplifiers to improve the following characteristics:

- 1. Frequency response

- a. In the design of wide-band amplifiers negative feedback is of use in trading gain for bandwidth.

- 2. Variation in gain due to variation in transistor parameters.

- 3. Distortion.

There are two basic forms of feedback which will be discussed here--voltage (shunt) feedback and current (series) feedback.

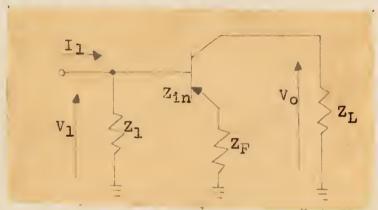

### Voltage Feedback

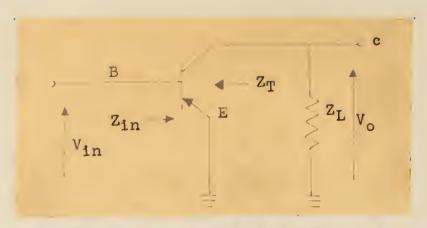

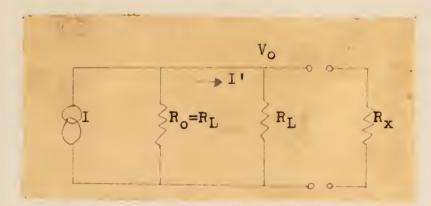

The method of analysis will be to determine a constant voltage form of an equivalent circuit for the amplifier without feedback and then to modify this equivalent circuit by adding the feedback circuit to determine the desired design equations. The common emitter amplifier configuration will be used as the basic circuit for the analysis.

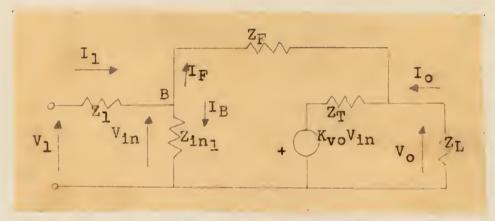

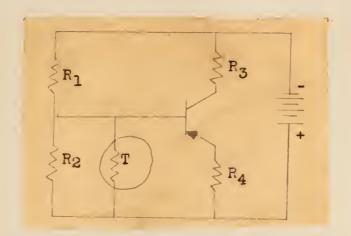

Figure 18 shows the basic common emitter amplifier stage with the biasing network not shown.

Figure 19 shows the constant voltage form of equivalent circuit for the common emitter stage.

Fig. 18. Common emitter amplifier stage.

Fig. 19. Constant voltage form of equivalent circuit for the common emitter amplifier stage.

In Fig. 19:

Kvo = voltage gain with load open circuited

Z<sub>T</sub> = output terminal impedance with input short

circuited

Zin = input impedance

B, C, E = the base, collector, and emitter terminals respectively.

The open-circuit voltage gain can be found for the general case by referring to Fig. 6 and Eq. (16), and letting  $I_2 = 0$ .

$$V_2/V_1 = 1/A$$

(108)

Therefore in Fig. 19

$$K_{VO} = 1/A \tag{109}$$

In terms of the common emitter equivalent circuit previously developed, Eq. (34), A is

$$A = -\frac{R_{e}R_{b} + R_{e}Z_{e} + BZ_{e}R_{b}}{BZ_{e}Z_{c} - R_{e}Z_{e}}$$

(110)

Therefore the open-circuit voltage gain is

$$K_{vo} = -\frac{BZ_eZ_c - R_eZ_e}{R_eR_b + R_eZ_e + BZ_eR_b}$$

(111)

$Z_{\rm T}$  can be found by using Eq. (24), by letting  $Z_{\rm g}=0$  (input short circuited).

$$Z_{T} = \frac{B}{A} = \frac{Z_{e}R_{e}Z_{c} + Z_{e}R_{b}R_{e} + Z_{c}R_{b}R_{e}}{R_{e}R_{b} + R_{e}Z_{e} + BZ_{e}R_{b}}$$

(112)

From Fig. 19 the equation for the voltage gain can be written as

$$K_{\text{ve}} = -\frac{1}{A} \frac{Z_{\text{L}}}{Z_{\text{T}} + Z_{\text{m}}} \tag{113}$$

Substituting Eqs. (110) and (112) into Eq. (113) yields the previously derived Eq. (38) for the common emitter voltage gain.

From Eq. (40), the input impedance without feedback is

$$Z_{\text{in}_{\Theta}} = R_{\text{b}} + \frac{(Z_{\text{c}} + Z_{\text{L}})Z_{\text{e}}R_{\text{e}}}{R_{\text{e}}Z_{\text{e}} + BZ_{\text{L}}Z_{\text{e}} + R_{\text{e}}Z_{\text{c}} + R_{\text{e}}Z_{\text{L}}}$$

(114)

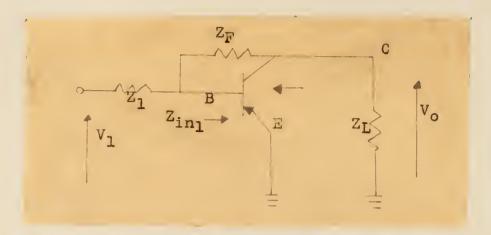

The voltage gain with feedback will now be determined.

Figure 20 is the common emitter amplifier with voltage feedback.

From Fig. 21, using Millman's theorem and solving for  $V_{\mbox{in}}$ , yields

Fig. 20. Common emitter amplifier with voltage feedback.

Fig. 21. Equivalent circuit of amplifier stage with feedback.

$$v_{in} = \frac{\frac{v_1}{z_1} + \frac{v_o}{z_F}}{\frac{1}{z_{in_1}} + \frac{1}{z_1} + \frac{1}{z_F}}$$

(115)

where  $Z_{\text{in}}$  is the modified input impedance as described in Eq. (121).

Using the approximation that  $\rm Z_F >> \rm Z_{in_1}$ , which is true in all practical cases, and solving for  $\rm V_o$  in terms of  $\rm K_{Vo}V_{in}$ , yields

$$V_{o} \simeq -\frac{\frac{Z_{L} Z_{F}}{Z_{L} + Z_{F}}}{\frac{Z_{L} Z_{F}}{Z_{O} + Z_{F}}} \quad K_{vo} V_{in}$$

$$(116)$$

Letting

$$Z_{X} = \frac{Z_{L} Z_{F}}{Z_{L} + Z_{F}} \tag{117}$$

Eq. (116) can be written

$$V_{o} \simeq -\frac{Z_{x}}{Z_{x} + Z_{o}} K_{vo} V_{in}$$

(118)

Solving for  $\frac{V_o}{v_{in}}$ , replacing  $K_{vo}$  with  $\frac{1}{A}$  , yields

$$K_{\text{vel}} \simeq -\frac{V_{\text{o}}}{V_{\text{in}}} = -\frac{Z_{\text{x}}}{Z_{\text{x}} + Z_{\text{o}}} \frac{1}{A}$$

(119)

Equation (119) is approximately equal to Eq. (113) if  $Z_L$  is replaced by  $Z_X$ , so the voltage gain from base to collector with feedback is approximately given by Eq. (38) if  $Z_L$  is replaced by  $Z_X$  and  $Z_F >> Z_{\text{in}_7}$ .

$$K_{\text{ve}_{1}} \simeq -\frac{Z_{\mathbf{x}}Z_{\mathbf{e}}(BZ_{\mathbf{c}} - R_{\mathbf{e}})}{R_{\mathbf{e}}Z_{\mathbf{e}}Z_{\mathbf{c}} + R_{\mathbf{e}}Z_{\mathbf{e}}Z_{\mathbf{x}} + BR_{\mathbf{b}}Z_{\mathbf{x}}Z_{\mathbf{e}} + R_{\mathbf{e}}Z_{\mathbf{e}}R_{\mathbf{b}} + R_{\mathbf{e}}R_{\mathbf{b}}Z_{\mathbf{c}} + R_{\mathbf{b}}R_{\mathbf{e}}Z_{\mathbf{x}}}$$

(120)

Using the same argument stated above,  $Z_{\rm inl}$  in Fig. 21 is approximately equal to  $Z_{\rm inE}$  defined by Eq. (40), if  $Z_{\rm L}$  in Eq. (40) is replaced by  $Z_{\rm X}$  defined in Eq. (117).

$$Z_{\text{inl}} \simeq R_b + \frac{(Z_c + Z_x)Z_eR_e}{R_eZ_e + BZ_xZ_e + R_eZ_c + R_eZ_x}$$

(121)

From Eq. (119)

$$V_{\text{in}} \simeq -\frac{V_o}{K_{\text{ve}_1}}$$

or  $V_o \simeq -V_{\text{in}} K_{\text{ve}_1}$  (122)

Substituting Eq. (120) into Eq. (115) and solving for  $V_0/V_1$ , which is the voltage gain with feedback, yields:

$$K_{vF} = \frac{V_{o}}{V_{1}} \simeq -\frac{Z_{F}}{Z_{g}} \left( \frac{1}{\frac{1}{K_{vel}} (\frac{Z_{F}}{Z_{g}} + \frac{Z_{F}}{Z_{inl}} + 1) + 1} \right)$$

(123)

If Kve; is sufficiently large,

$$K_{\rm VF} \simeq -\frac{Z_{\rm F}}{Z_{\rm I}} \tag{124}$$

Derivation of input impedance with feedback:

$$Z_{in_{\overline{F}}} = Z_1 + \frac{v_{in}}{I_1} \tag{125}$$

$$I_{\gamma} = I_{B} + I_{F} \tag{126}$$

$$I_{\rm B} = \frac{v_{\rm in}}{z_{\rm in}} \tag{127}$$

$$I_{F} = \frac{V_{in} - V_{o}}{Z_{F}} \tag{128}$$

Substituting Eq. (122) into Eq. (128) gives

$$I_{\rm F} \simeq \frac{V_{\rm in} + K_{\rm vel} V_{\rm in}}{Z_{\rm F}} \tag{129}$$

Substituting Eqs. (127) and (128) into Eq. (125) and solving for input impedance with feedback, yields:

$$Z_{inF} \simeq Z_1 + \frac{1}{\frac{1}{Z_{in1}} + \frac{1}{Z_F} (1 + K_{vel})}$$

(130)

Derivation of current gain:

From Eqs. (126), (127), and (128) the input current is

$$I_1 = I_B + I_F \simeq V_{in} \left( \frac{1}{Z_{in1}} + \frac{1}{Z_F} \left[ 1 + K_{vel} \right] \right)$$

(131)

The output current is given by

$$I_o = \frac{V_o}{Z_L} \simeq -\frac{K_{vel} V_{in}}{Z_L}$$

(132)

Solving for the current gain with feedback yields

$$K_{iF} = \frac{I_o}{I_1} \sim -(\frac{K_{vel}}{Z_L}) \frac{1}{\frac{1}{Z_{in_1}} + \frac{1}{Z_F} (1 + K_{vel})}$$

(133)

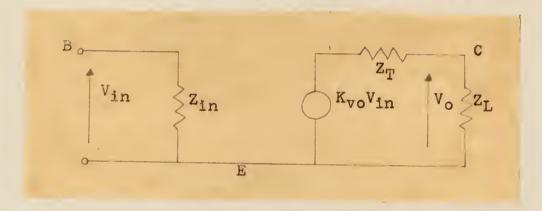

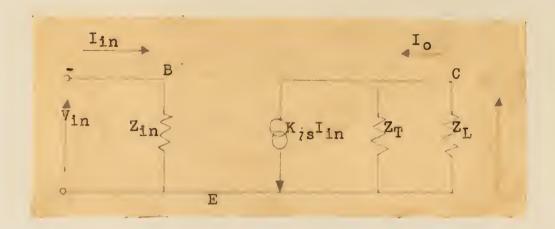

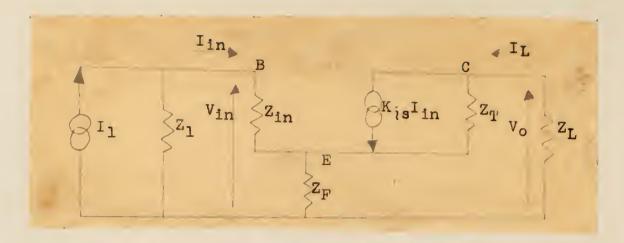

#### Current Feedback

The method of analysis will be to determine a constant-current form of an equivalent circuit for the amplifier without feedback, and then to modify this equivalent circuit by adding the feedback circuit to determine the desired design equations. The common emitter amplifier configuration will be used as the basic circuit for the analysis.

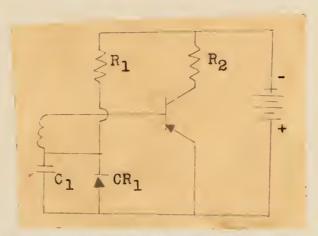

Figure 18 is the common emitter amplifier stage with the biasing network not shown. Figure 22 is the constant-current form of equivalent circuit for the amplifier stage.

In Fig. 22

K<sub>7S</sub> = current gain of the amplifier with the output

short circuited

$\mathbf{Z}_{\mathrm{T}}$  = output terminal impedance with the input open circuited

Fig. 22. Constant-current form of equivalent circuit for the common emitter amplifier stage.

Z<sub>in</sub> = input impedance

B, C, E = the base, collector, and emitter terminals respectively.

The short-circuit current gain can be found for the general case by referring to Fig. 6, Eq. (16), and letting  $V_2=0$ .

$$I_2/I_1 = 1/D$$

(134)

Therefore in Fig. 22

$$K_{is} = 1/D$$

(135)

In terms of the common emitter equivalent circuit previously developed, Eq. (37), D is

$$D = -\frac{Z_e R_e + Z_c R_e}{BZ_e Z_c - Z_e R_e}$$

(136)

Therefore the short-circuit current gain is

$$K_{S} = -\frac{BZ_eZ_c - Z_eR_e}{Z_eR_e + Z_cR_e}$$

(137)

$\rm Z_T$  can be found by using Eq. (24) by letting  $\rm Z_g {\:\longrightarrow\:} \infty$  (input open circuited).

$$Z_{T} = \frac{D}{C} = \frac{Z_{e}R_{e} + Z_{c}R_{e}}{R_{e} + BZ_{e}}$$

(138)

From Fig. 22 the equation for the current gain can be written as

$$K_{j\Theta} = \frac{1}{D} \frac{Z_{T}}{Z_{T} + Z_{L}} \tag{139}$$

Substituting Eqs. (136) and (138) into Eq. (139) yields the previously derived Eq. (39) for the common emitter current gain.

The input impedance is given by Eq. (40).

The equation describing the amplifier stage with feedback will now be determined. Figure 23 is the common emitter amplifier stage with current feedback.

Fig. 23. Common emitter amplifier with current feedback.

Referring to Fig. 24 and writing the equation for E in in terms of I in (assuming  $\rm Z_T>>\rm Z_F$  and  $\rm Z_L>>\rm Z_F)$  , yields

$$V_{in} \simeq I_{in} (Z_{in} + Z_F) + K_{is}I_{in} (\frac{Z_T}{Z_T + Z_L}) Z_F$$

(140)

Solving Eq. (140) for  $V_{in}/I_{in}$  gives the input impedance with feedback when measured at the base terminal.

Fig. 24. Equivalent circuit of common emitter amplifier stage with current feedback.

$$Z_{inFB} = \frac{V_{in}}{I_{in}} \simeq Z_{in} + Z_{F} \left[ 1 + K_{is} \left( \frac{Z_{T}}{Z_{T} + Z_{L}} \right) \right]$$

(141)

The input impedance with feedback taking into account Z1

is

$$Z_{inF} = \frac{V_{in}}{I_{1}} \simeq \frac{1}{\frac{1}{Z_{1}} + \frac{1}{Z_{in} + Z_{F} \left[1 + K_{is} \left(\frac{Z_{T}}{Z_{T} + Z_{L}}\right)\right]}}$$

(142)

Solving for  $V_{\rm O}$  gives (assuming  $Z_{\rm O} >> Z_{\rm F}$  and  $Z_{\rm L} >> Z_{\rm F}$ ),

$$V_{o} \simeq -K_{is} I_{in} Z_{L} \frac{Z_{T}}{Z_{T} + Z_{L}}$$

(143)

The voltage gain with feedback is

$$K_{vF} = V_0/V_{in} \tag{144}$$

Substituting Eqs. (140) and (143) into Eq. (144) yields

$$K_{VF} \simeq -\frac{K_{1s}}{Z_{T} + Z_{L}} \frac{Z_{T}}{Z_{T} + Z_{L}} \frac{Z_{L}}{Z_{T} + Z_{L}}$$

$$(145)$$

Derivation of current gain with feedback.

From Fig. 24

$$I_1 \simeq I_{\text{in}} \frac{Z_1 + Z_{\text{in}} F_B}{Z_1} \tag{146}$$

$$I_{o} \simeq -K_{7} s I_{1n} \frac{Z_{o}}{Z_{o} + Z_{L}}$$

(147)

Solving for current gain yields

$$I_{iF} \simeq \frac{I_o}{I_1} = -Z_1 \frac{K_s I_{in} \frac{Z_T}{Z_T + Z_L}}{I_{in}(Z_1 + Z_{inF_B})}$$

(148)

Substituting Eq. (141) into Eq. (148) and simplifying, yields

$$K_{iF} \simeq -\frac{Z_1}{Z_F}$$

$$\frac{1}{1 + \frac{1}{X_{iS}} \frac{Z_T}{Z_T + Z_L}} \frac{(Z_1 + Z_{in} + 1)}{Z_F}$$

(149)

If

$$K_{is} = \frac{Z_T}{Z_T + Z_T}$$

$Z_F > > Z_1 + Z_{in} + Z_F$ ,

$$K_{iF} \simeq -\frac{Z_1}{Z_F} \tag{150}$$

#### HIGH-FREQUENCY AMPLIFICATION

Undoubtedly the most important consideration in the design of a high-frequency amplifier is the proper choice of the transistor to be used. If signal power gain is used as a criterion for the usefulness of a given transistor at a given frequency, a figure of merit for the transistor can be developed

which is analogous to the well known gain bandwidth product for the vacuum tube. The figure of merit for the transistor is the frequency at which the signal power gain is unity. The figure of merit is often defined on data sheets as the maximum frequency of oscillation. Once the figure of merit for a transistor has been determined the signal power gain that is possible at frequencies below it can be estimated, using the approximation that signal power gain increases 6 db per octave below the figure of merit.

### Derivation of Figure of Merit

The figure of merit for transistors can be determined from the basic equivalent circuit.

Fig. 25. Equivalent circuit for determining signal power gain.

Since the figure of merit is for optimum conditions, it will be derived assuming the input and output are conjugately

<sup>&</sup>lt;sup>1</sup>L. Giacoletto, "Study of P-N-P Alloy Junction Transistor from D-c through Medium Frequencies," <u>RCA Review</u>, vol. 14, December. 1954.

matched. The condition of unity power gain occurs at the upper useful frequency range of the transistor, so at high frequencies certain simplifying conditions hold. These are:

$$X_e >> X_c$$

$R_e >> X_e$   $R_c >> X_c >> R_L$   $R_b >> X_e$  f  $>> f  $<$  b$

The following equations are taken directly from the equivalent circuit.

Since as stated above  $R_b >> X_e$  and  $X_c >> R_b$ , the input power under matched conditions  $(R_b = R_g)$  is

$$P_{in} \simeq \frac{|v_g|^2}{4R_b} \tag{151}$$

The output power is

$$P_{o} = \frac{|v_{L}|^{2}}{R_{L}} \tag{152}$$

since the output is matched  $R_L = R_0$ , where  $R_0$  is the output resistance of the transistor. The output impedance for the high-frequency case was derived as Eq. (58), and is

$$Z_{\text{out}_{e}} = \frac{X_{c}Z_{g} + X_{c}(X_{e} + R_{b})}{(1 + h_{fe})Z_{g} + (1 + h_{fe})R_{b} + X_{e}}$$

(153)

Using the approximation that  $h_{\text{fe}}>>1$  and the simplifying relationships stated above, the output impedance is

$$Z_{\text{out e}} \simeq \frac{X_{c}}{h_{fe}}$$

(154)

Since  $h_{fe} = \frac{BZ_e}{R_e}$ , the output impedance can be written as

$$Z_{\text{out }e} = R_0 = R_L \simeq \frac{C_e R_e}{C_c B}$$

(155)

Equation (155) indicates that the output impedance of the transistor is resistive at high frequencies.

Solving for the output voltage in terms of the current generator  $\text{BI}\left[\overline{R_{e}}\right]$  yields

$$V_{L} \simeq BI [R_e] R_L = h_{fe} I [C_e] R_L$$

(156)

Since  $\rm X_{e} <<$   $\rm R_{e},$   $\rm X_{c} >>$   $\rm R_{b},$  and  $\rm X_{c} >>$   $\rm R_{L},$  solving for I [Ce] yields

$$I \left[ C_{e} \right] = \frac{V_{g}}{2 R_{b}} - h_{fe} I \left[ C_{e} \right] \frac{R_{L}}{X_{c}}$$

(157)

It has been established that  $R_{\rm L}=R_{\rm O}$  and  $R_{\rm O} \simeq \frac{X_{\rm C}}{h_{\rm fe}}$  . Using

these relationships in Eq. (157), and solving for I ce yields

$$I[C_e] \simeq \frac{V_g}{4 R_b} \tag{158}$$

Combining Eqs. (156) and (158), and solving for  $V_{\rm L}$ , yields

$$V_{L} \simeq h_{fe} \frac{V_{g}}{4 R_{h}} R_{L}$$

(159)

In terms of B

$$V_{L} \simeq \frac{BX_{e}}{R_{e}} \frac{V_{g}}{4 R_{b}} R_{L}$$

(160)

or

$$V_{L} \simeq \frac{B V_{g} R_{L}}{j\omega C_{e}R_{e} 4 R_{b}}$$

(161)

Combining Eqs. (152), (155), and (161) and solving for the output power, yields

$$P_{o} \simeq \frac{B|V_{g}|^{2}}{16 R_{b}^{2} \omega^{2} R_{e} C_{e} C_{c}}$$

(162)

The power gain is

$$P_{G} = \frac{P_{o}}{P_{in}} \sim \frac{B}{(2\pi f)^{2} 4 R_{b} R_{e} C_{e} C_{c}}$$

(163)

Setting the power gain equal to 1 and solving for f yields

$$f = \sqrt{\frac{B}{8 \pi R_b C_c}} \frac{1}{2 \pi R_e C_e}$$

(164)

but  $f_{\infty e} = \frac{1}{2 \pi c_e R_e}$  and  $f_{\infty b} = B f_{\infty e}$ . Therefore

$$f = \sqrt{\frac{f_{\infty b}}{8 \pi R_b C_c}}$$

(165)

Equation (165) is the figure of merit for the transistor, or the frequency at which the power gain is equal to unity under matched conditions.

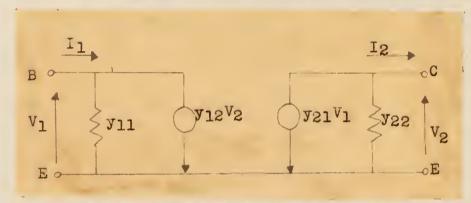

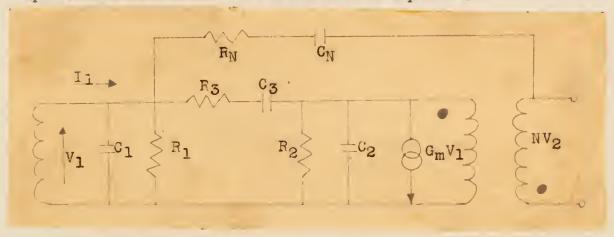

### Alternate Equivalent Circuits

The parameters for the y-equivalent circuit, Fig. 27, and the  $\pi$ -equivalent circuit, Fig. 28, will now be determined in terms of the parameters of the basic equivalent circuit, Fig. 26. The  $\pi$ -equivalent circuit will be useful in determining the design equations for neutralizing a transistor amplifier stage, as will be shown later.

The transfer matrix parameters that describe Fig. 26 have been previously determined in Eqs. (34), (35), (36), and (37). In general the equations describing Fig. 26 in terms of the transfer matrix parameters are:

$$V_1 = A V_2 + B I_2$$

(166)

Fig. 26. Hybrid π-equivalent circuit.

Fig. 27. Y-equivalent circuit.

Fig. 28. π-equivalent circuit.

$$I_1 = C V_2 + D I_2$$

(167)

The equations describing Fig. 27 in terms of the y-parameters are:

$$I_1 = y_{11} V_1 + y_{12} V_2$$

(168)

$$-I_2 = y_{21} V_1 + y_{22} V_2$$

(169)

Solving Eq. (166) for I2 yields

$$I_2 = V_1 \frac{1}{B} - V_2 \frac{A}{B} \tag{170}$$

or

$$-I_2 = -\frac{1}{B}V_1 + \frac{A}{B}V_2 \tag{171}$$

Substituting Eq. (170) into Eq. (167) yields

$$I_1 = \frac{D}{B} V_1 - (\frac{DA - BC}{B}) V_2$$

(172)

Comparing Eqs. (171) and (172) with Eqs. (168) and (169), the following relationships are evident.

$$y_{11} = \frac{D}{B}$$

(173)

$$y_{12} = \frac{BC - DA}{B} \tag{174}$$

$$y_{21} = -\frac{1}{B} \tag{175}$$

$$y_{22} = \frac{A}{B}$$

(176)

From Eqs. (34), (35), (36), and (37), the transfer matrix parameters for the hybrid  $\pi$ -equivalent circuits are:

$$A = -\frac{R_{e}R_{b} + R_{e}Z_{e} + BZ_{e} R_{b}}{BZ_{e}Z_{c} - R_{e}Z_{e}}$$

(177)

$$B = -\frac{R_e Z_e Z_c + Z_e R_e R_b + Z_c R_b R_e}{B Z_e Z_c - Z_e R_e}$$

(178)

$$C = -\frac{R_e + BZ_e}{BZ_eZ_c - Z_eR_e}$$

(179)

$$D = -\frac{Z_e R_e + Z_c R_e}{BZ_e Z_c - Z_e R_e}$$

(180)

Substituting Eqs. (177) through (180) into Eqs. (173) through (176) yields

$$y_{11} = \frac{Z_{e}R_{e} + Z_{c}R_{e}}{R_{e}Z_{e}Z_{c} + Z_{e}R_{e}R_{b} + Z_{c}R_{b}R_{e}}$$

(181)

$$y_{12} = \frac{-Z_e}{Z_e Z_c + Z_e R_b + Z_c R_b}$$

(182)

$$y_{21} = \frac{BZ_eZ_c - Z_eR_e}{R_eZ_eZ_c + Z_eR_bR_e + Z_cR_bR_e}$$

(183)

$$y_{22} = \frac{R_e R_b + R_e Z_e + B Z_e R_b}{R_e Z_e Z_c + Z_e R_b R_e + Z_c R_b R_e}$$

(184)

Equations (181) through (184) above give the y-parameters of Fig. 27 in terms of the hybrid n-parameters of Fig. 26.

The following relationships between the parameters of Figs. 27 and 28 are evident.

$$y_{11} = Y_1 + Y_3 = \frac{I_1}{v_1} \quad (v_2 = 0)$$

(185)

$$y_{22} = Y_2 + Y_3 = \frac{I_2}{V_2} \quad (V_1 = 0)$$

(186)

$$y_{21} = G_m - Y_3 = \frac{I_2}{V_1} \quad (V_2 = 0)$$

(187)

$$y_{12} = -Y_3 = \frac{I_1}{V_2}$$

$(V_1 = 0)$  (188)

Solving for the  $\pi$  equivalent circuit parameters in terms of the hybrid  $\pi$  equivalent circuit parameters yields

$$Y_3 = -y_{12} = \frac{Z_e}{Z_e Z_c + Z_e R_b + Z_c R_b}$$

(189)

$$G_{m} = y_{21} + Y_{3} = \frac{BZ_{e}Z_{c}}{R_{e}Z_{e}Z_{c} + Z_{e}R_{b}R_{e} + Z_{c}R_{b}R_{e}}$$

(190)

$$Y_2 = y_{22} - Y_3 = \frac{R_e R_b + BZ_e R_b}{R_e Z_e Z_c + Z_e R_b R_e + Z_c R_b R_e}$$

(191)

$$Y_1 = y_{11} - Y_3 = \frac{Z_c}{Z_c Z_c + Z_c R_b + Z_c R_b}$$

(192)

Equations (189) through (192) give the m equivalent circuit parameters of Fig. 28 in terms of the hybrid-m parameters of Fig. 26.

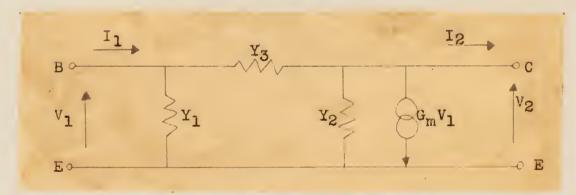

The equivalent circuit of Fig. 28 is more useful if the Y-parameters are divided into their real and imaginary components as shown in Fig. 29.

Fig. 29. π-equivalent circuit showing real and imaginary components.

Comparing Figs. 28 and 29, the following relationships are evident.

$$Y_{1} = \frac{1}{R_{1}} + j\omega c_{1}$$

(193)

$$Y_2 = \frac{1}{R_2} + j\omega c_2$$

(194)

$$Y_3 = \frac{1}{R_3 + \frac{1}{j\omega c_3}}$$

(195)

$$G_{\rm m} = g_{\rm mR} + jg_{\rm mI} \tag{196}$$

The following results are obtained by solving Eqs. (189) through (192) for their real and imaginary components as indicated in Eqs. (193) through (196).

$$R_1 \simeq R_b + P_e \frac{R_e + R_b}{R_e + R_b + \omega^2 C_e^2 R_e^2 R_b}$$

(197)

$$c_1 \simeq c_e \frac{1}{(1 + \frac{R_b}{R_e})^2 + \omega^2 c_e^2 R_b^2}$$

(198)

$$R_{2} = \frac{R_{c}}{1 + BR_{b} \frac{R_{e} + R_{b} + \omega^{2} C_{e} C_{c} R_{e} R_{b} R_{c}}{(R_{b} + R_{e})^{2} + \omega^{2} C_{e}^{2} R_{e}^{2} R_{b}^{2}}}$$

(199)

For low power transistor  $R_e>>R_b$  , since  $R_e \sim \frac{B26}{I_E\,(ma)}$  ,  $B \sim R_b$  , and  $I_E <$  5 ma.

Simplifying Eq. (199) yields

$$R_{2} \simeq \frac{R_{c}}{1 + B \frac{R_{b}}{R_{e}} \frac{1 + \omega^{2} C_{e} C_{c} R_{b} R_{c}}{1 + \omega^{2} C_{e}^{2} R_{b}^{2}}}$$

(200)

At sufficiently high frequencies

$$R_2 \simeq \frac{C_e R_e}{B C_c} \tag{201}$$

and since  $\omega_{\infty b} = B/R_eC_c$

$$R_2 \simeq \frac{1}{\omega_{\infty b} c_e}$$

(202)

$$c_2 \simeq c_e (1 + B \frac{R_b(R_b + R_e)}{(R_b + R_e)^2 + \omega^2 c_e^2 R_b^2 R_e^2})$$

(203)

Solving for the real and imaginary parts of Y3 yields

$$R_{3} = R_{b} \left(\frac{C_{e}}{C_{c}}\right) + \frac{R_{b} + R_{e}}{R_{e}R_{c}\omega^{2}C_{c}^{2}}$$

(204)

$$C_3 = \frac{C_c}{R_e + R_b - C_e R_b}$$

$$R_e - C_c R_c$$

(205)

$$g_{mR} \simeq \frac{B(R_b + R_e)}{(R_b + R_e)^2 + \omega^2 C_e^2 R_b^2 R_e^2}$$

(206)

$$g_{mI} \simeq \frac{\omega c_e R_b R_e B}{(R_b + R_e)^2 + \omega c_e^2 R_b^2 R_e^2}$$

(207)

Equations (201) through (207) give the parameters of the equivalent circuit shown in Fig. 29 in terms of the parameters of the hybrid π-equivalent circuit shown in Fig. 26. Due to the complexity involved in calculating these equations, the following simplifying assumptions were made.

$$R_c >> R_b$$

$R_c >> R_e$   $R_c >> B$   $C_e >> C_c$

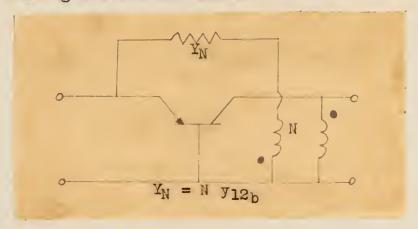

#### NEUTRALIZATION

The basic limitation imposed by the transistor on its application in its upper useful frequency range is its inherent bilateral nature. As the operating frequency of the transistor is increased the internal feedback impedance between its output

and input becomes smaller, and instability due to positive feed-back results. There are two basic methods of reducing the effects of the internal feedback and extending the useful frequency range of the transistor. The two methods discussed are: (1) Isolation by neutralization, and (2) isolation by mismatch.

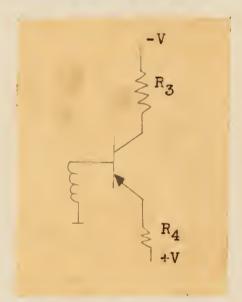

## Isolation by Neutralization

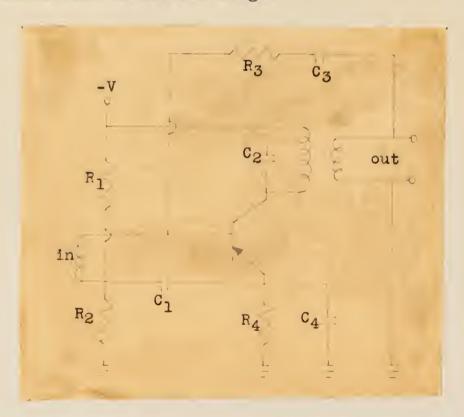

The principle involved in neutralization is simply to sample the output voltage of the stage to be isolated and feed back this voltage to the input with the correct phase and amplitude to cancel the internal feedback voltage. Figure 30 is an example of a neutralized transistor stage.

Fig. 30. Example of neutralized amplifier.

The problem the designer is faced with is to determine the correct value for the components that make up the neutralizing network and develop an equivalent circuit to represent the neutralized stage. The method employed in this report to determine the required design equations is to use the wequivalent circuit previously developed (see Fig. 28). The desired values of the feedback components are determined with only minor calculations from this equivalent circuit. Figure 31 is the a-c equivalent circuit of the neutralized amplifier.

N = transformer turns ratio

N > 1 = for step-up transformer

N < 1 = for step-down transformer

Fig. 31. Equivalent circuit of neutralized amplifier.

From Fig. 31 it is evident that for proper neutralization (assuming an ideal transformer)

$$R_{N} = N R_{3} \tag{208}$$

$$C_{N} = C_{3}/N \tag{209}$$

where R3 and C3 are given by Eqs. (204) and (205). Therefore

$$R_{N} = N \left( \frac{R_{b}C_{e}}{C_{c}} + \frac{R_{b} + R_{e}}{R_{e}R_{c}\omega^{2}C_{c}^{2}} \right)$$

(210)

and

$$C_{N} = \frac{1}{N} \left( \frac{C_{c}}{R_{\Theta} + R_{b} - C_{\Theta} R_{b}} \right)$$

$$(211)$$

Equations (210) and (211) are the desired values of the neutralizing components in terms of the hybrid equivalent circuit parameters.

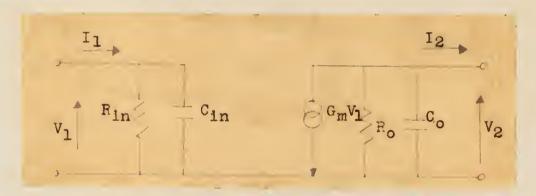

Since neutralizing the amplifier eliminates the internal feedback, the neutralized transistor can be represented by the equivalent circuit of Fig. 32.

Fig. 32. Equivalent circuit of neutralized amplifier stage.

In Fig. 32

$$R_{in} = R_1$$

(see Eq. (197)) (212)

$$C_{in} = C_1$$

(see Eq. (198)) (213)

$$R_0 = R_2$$

(see Eq. (199)) (214)

$$C_0 = C_2$$

(see Eq. (203)) (215)

$$G_{\rm m} = g_{\rm mR} + jg_{\rm ml}$$

(see Eqs. (206) and (207)) (216)

assuming

$$R_N \; + \; j\omega c_N >> \frac{1}{\frac{1}{R_1} \; + \; j\omega \; c_1} \quad \text{and} \; R_N \; + \; j\omega c_N >> \frac{1}{\frac{1}{R_2} \; + \; j\omega c_2} \; .$$

The common emitter configuration was used as the basis of analysis in the previous example. The common base configuration can be neutralized in a similar manner, the requirement being that

$$Y_N = -y_{12}$$

(217)

where YN = the effective neutralizing admittance

y12 = the reverse transfer admittance of the transistor.

In terms of the common base transfer matrix parameters (Eq. 83),

$$y_{12} = \frac{BC - DA}{B} \simeq -\frac{R_b(R_e + BZ_e)}{Z_cR_e(Z_e + R_b)}$$

(218)

assuming  $Z_c >> R_h$ .

Figure 33 shows a typical neutralized common base stage with the biasing network not shown.

Fig. 33. Neutralized common base stage.

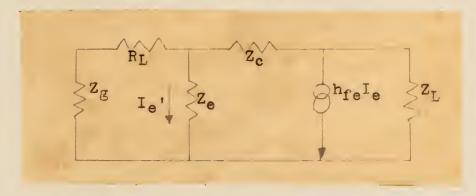

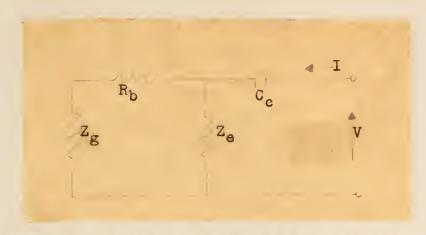

### Isolation by Mismatch

Theoretically, isolation by neutralization is the optimum method of stabilizing a transistor at high frequencies, but it soon becomes apparent to the design engineer that though neutralization is the optimum method it has certain troublesome limitations. Transistor parameters vary from unit to unit and since the neutralizing network must be identical to the internal feedback network, considerable adjustment time is required for each unit under production conditions. Wide-band amplifiers also present problems when neutralization is attempted, since the neutralizing network can be made optimum for only one set of parameters and one frequency. It is possible to reduce the effects of the bilateral nature of the transistor without resorting to the complication of a neutralizing network by sacrificing gain in the interstage network. Isolation by this method will be termed isolation by mismatch since the method requires a deliberate mismatch between transistor output impedance and load impedance.

The problem is to determine the maximum load impedance that will assure stable operation. Or, after the design of the stage has been completed, meeting the design specifications, the stage should be reevaluated to see if it is stable using limit transistors and components.

The equivalent circuit shown in Fig. 34 will be used to derive the equation for the maximum stable load impedance. The

equivalent circuit is identical with the basic equivalent circuit (Fig. 5) with

$$Z_{e} = \frac{R_{e}}{1 + j\omega C_{e}R_{e}}, Z_{e} = \frac{R_{c}}{1 + j\omega C_{c}R_{c}},$$

and

$$h_{fe} = \frac{BZ_e}{R_e} = \frac{B}{1 + j\omega C_e R_e}$$

Fig. 34. Transistor equivalent circuit, terminated by load and generator impedances.

Assuming no externally applied signals, instability occurs when  $I_e^{\ '}=I_e.$

Solving for  $I_{\Theta}$  in terms of the current generator  $h_{\mathbf{f}\mathbf{e}}I_{\Theta}$  yields

$$I_{e'} = -h_{fe}I_{e} \frac{Z_{L}(R_{b} + Z_{g})}{(Z_{e} + \frac{Z_{e}(R_{b} + Z_{g})}{Z_{e} + R_{b} + Z_{g}} + Z_{L})(R_{b} + Z_{g} + Z_{e})}$$

(219)

Since  $Z_c>>Z_e$ , Eq. (219) can be simplified.

$$I_e' = -h_{fe}I_e \frac{Z_L}{Z_c + Z_L} \frac{R_b + Z_g}{R_b + Z_g + Z_e}$$

(220)

Instability occurs when  $I_e' = I_e$ , or when

$$h_{fe} = \frac{Z_L}{Z_c + Z_L} = \frac{R_b + Z_g}{R_b + Z_g + Z_e} + 1 = 0$$

(221)

Rearranging Eq. (220), to separate the terms  $1/Z_{\rm g}$  and  $1/Z_{\rm L}$ , and using the approximation that in the frequency range of interest  $h_{\rm fe}>>1$ , yields

$$(\frac{1}{Z_{e} + R_{b}} + \frac{1}{Z_{g}})(\frac{h_{fe} R_{b} + Z_{e}}{Z_{c}(Z_{e} + R_{b})} + \frac{1}{Z_{L}}) + \frac{h_{fe} Z_{e}}{Z_{c}(Z_{e} + R_{b})^{2}} \simeq 0$$

(222)

In general, Eq. (222) can be written in terms of real and imaginary components.

$$(re(a) + j im(a))(re(b) + j im(b)) = -re(c) - j im(c)$$

(223)

where re = real term

im = imaginary term

$$a = \frac{1}{Z_e + R_b} + \frac{1}{Z_g}$$

$$b = \frac{h_{fe} R_b + Z_e}{Z_c (Z_e + R_b)} + \frac{1}{Z_L}$$

$$c = \frac{h_{fe} Z_e}{Z_c (Z_e + Z_b)^2}$$

Equation (223) can be written as two real equations. 1

$$re(a) re(b) - im(a) im(b) = -re(c)$$

(224)

$$im(b) re(a) + im(a) re(b) = -im(c)$$

(225)

Solving Eq. (224) for im(a) and im(b) yields

$$im(a) = \frac{re(a) re(b) + re(c)}{im(b)}$$

(226)

$$im(b) = \frac{re(a) re(b) + re(c)}{im(a)}$$

(227)

lw. Gartner, Transistors Principles, Design, and Applications, D. Van Nostrand Company, Inc., Princeton, New Jersey, p. 370.

Substituting Eqs. (226) and (227) into Eq. (225) and solving for im(a) and im(b), yields

$$\lim(a) = \frac{-im(c) \pm \sqrt{(im(c))^2 - 4 \operatorname{re}(b) \operatorname{re}(c) \operatorname{re}(a) + \operatorname{re}(a)^2 \operatorname{re}(b)}}{2 \operatorname{re}(b)}$$

(228)

$$\lim(b) = \frac{-im(c) \pm \sqrt{im(c)^2 - 4 \operatorname{re}(b) \operatorname{re}(c) \operatorname{re}(a) + \operatorname{re}(a)^2 \operatorname{re}(b)}}{2 \operatorname{re}(a)}$$

(229)

For possible instability, Eqs. (228) and (229) must be real to satisfy Eqs. (224) and (225). If

$$0 < re(a)^2 re(b)^2 + re(a) re(b) re(c) - \frac{im(c)^2}{4}$$

Eqs. (224) and (225) will be imaginary and stability will be assured independent of load and generator susceptances. In a tuned amplifier it is necessary to determine the maximum values of the real parts of the terminating impedances independent of the imaginary parts, since in the "tuning up" process the imaginary parts may assume a wide range of values. If the real part of Eq. (222) is satisfied, then it is possible that during "tune up" the imaginary part will be satisfied and instability will result.

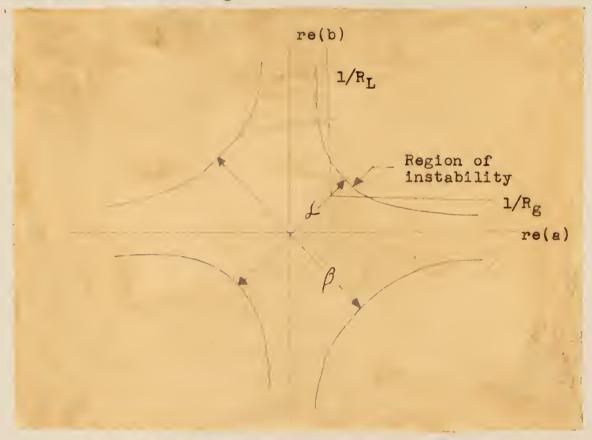

Setting Eq. (230) equal to zero (limit of assured stability) and solving for re(a) re(b), yields

$$2 \operatorname{re}(a) \operatorname{re}(b) = -\operatorname{re}(c) + |c|$$

(231)

$$2 \operatorname{re}(a) \operatorname{re}(b) = -\operatorname{re}(c) - |c|$$

(232)

where | c | indicates the magnitude of c.

Equations (231) and (232) describe two equilateral hyperbolas illustrated in Fig. 35.

Fig. 35. Graphical presentation of Eqs. (231) and (232).

In Fig. 35

$$\propto = 2 \left[ -\text{re} \left( \frac{h_{\text{fe}} Z_{\text{e}}}{Z_{\text{c}} (Z_{\text{e}} + R_{\text{b}})^2} \right) + \left| \frac{h_{\text{fe}} Z_{\text{e}}}{Z_{\text{c}} (Z_{\text{e}} + R_{\text{b}})^2} \right| \right]$$

(233)

$$\beta = 2 \left[ -\text{re} \left( \frac{h_{\text{fe}} Z_{\text{e}}}{Z_{\text{c}} (Z_{\text{e}} + R_{\text{b}})^2} \right) - \left| \frac{h_{\text{fe}} Z_{\text{e}}}{Z_{\text{c}} (Z_{\text{e}} + R_{\text{b}})^2} \right| \right]$$

(234)

where

libid., page 371.

$$\operatorname{re} \left(\frac{1}{Z_{e} + R_{b}}\right) \simeq \frac{R_{e} + \frac{\omega^{2}}{\omega_{\infty}e^{2}} R_{b}}{R_{e}^{2} + \frac{\omega^{2}}{\omega_{\infty}e^{2}} R_{b}^{2}}$$

(235)

$$re \left(\frac{h_{fe} R_{b} + Z_{e}}{Z_{c}(Z_{e} + R_{b})}\right) \simeq \frac{\frac{\omega^{2}}{\omega_{\infty e}} C_{c}R_{b}(BR_{b} + R_{e})}{R_{e}^{2} + \frac{\omega^{2}}{\omega_{\infty e}} R_{b}^{2}}$$

(236)

re

$$\left(\frac{h_{fe} Z_{e}}{Z_{c}(Z_{e} + R_{b})^{2}}\right) \simeq \frac{2 \frac{\omega}{\omega_{\infty} e} C_{c}BR_{e}^{2}R_{b}}{(R_{e}^{2} + \frac{\omega^{2}}{\omega_{\infty} e} R_{b}^{2})^{2}}$$

(237)

$$\left| \frac{h_{fe} Z_{e}}{Z_{c} (Z_{e} + R_{b})^{2}} \right| \simeq \frac{\omega C_{c} BR_{e}}{R_{e}^{2} + \frac{\omega^{2}}{\omega \propto e^{2}} R_{b}^{2}}$$

(238)

Equations (235) through (238) were derived assuming  $Z_c \simeq \frac{1}{j\omega C_c}$ ,  $R_e >> R_b$ ,  $h_{fe} >> 1$ , and  $\omega_{\infty e} \simeq \frac{1}{R_e C_e}$ .  $\omega_{\infty e}$  is the common emitter angular cut-off frequency described previously.

Assuming  $1/R_g$  and  $1/R_L$  are positive values, Eq. (231) is the one of interest. Substituting Eqs. (235) through (238) into Eq. (231), and simplifying, yields the equation for absolute stability.

$$\frac{\left(\frac{R_{e} + \frac{\omega^{2}}{\omega_{\infty}e^{2}}R_{b}}{\omega_{\infty}e^{2}} + \frac{1}{R_{g}}\right) \left(\frac{\omega^{2}}{\omega_{\infty}e^{2}}C_{c}R_{b}(BR_{b} + R_{e})}{R_{e}^{2} + \frac{\omega^{2}}{\omega_{\infty}e^{2}}R_{b}^{2}} + \frac{1}{R_{L}}\right) >$$

$$\frac{B \omega C_{c}R_{e} \left(\frac{\omega}{\omega_{\infty}e} + \frac{\omega^{2}}{\omega_{\infty}e}R_{b} - R_{e}\right)^{2}}{(R_{e}^{2} + \frac{\omega^{2}}{\omega_{\infty}e^{2}}R_{b}^{2})^{2}}$$

$$(239)$$

Solving Eq. (239) for 1/R<sub>I</sub>, yields

$$\frac{1}{R_{L}} > \frac{\omega C_{c}BR_{e}(R_{e} - \frac{\omega}{\omega \propto e} R_{b})^{2} R_{g}}{2(R_{e}^{2} + \frac{\omega^{2}}{\omega \propto e^{2}} R_{b}^{2})(\left[R_{e} + \frac{\omega^{2}}{\omega \propto e^{2}} R_{b}\right] R_{g} + R_{e}^{2} + \frac{\omega^{2}}{\omega \propto e^{2}} R_{b}^{2})}$$

$$- \frac{\omega^{2} C_{c}R_{b}(BR_{b} + R_{e})}{\omega \propto e^{(R_{e}^{2} + \frac{\omega}{\omega \propto e^{2}} R_{b}^{2})}} \tag{240}$$

When  $\omega$  is of the same order of magnitude of  $\omega_{\infty e}$  (mid-frequency range), Eq. (240) can be further simplified to yield

$$R_{\rm L} < \frac{2 \left| X_{\rm c} \right|}{B} \frac{R_{\rm g} + R_{\rm e}}{R_{\rm g}} \text{ where } \left| X_{\rm c} \right| = \frac{1}{\omega C_{\rm c}}$$

(241)

If Eq. (240) or (241) is satisfied (depending on the frequency range of interest), the transistor will be unconditionally stable.

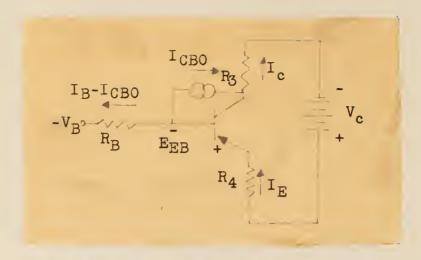

Conversely, the maximum stable value of  $R_{\rm g}$  could have been determined for a given  $R_{\rm L}$ .