# REDUCING SIGNAL COUPLING AND CROSSTALK IN MONOLITHIC, MIXED-SIGNAL INTEGRATED CIRCUITS

by

#### MATTHEW JOHN CLEWELL

B.S., Kansas State University, 2011

#### A THESIS

submitted in partial fulfillment of the requirements for the degree

#### MASTER OF SCIENCE

Department of Electrical Engineering College of Engineering

KANSAS STATE UNIVERSITY Manhattan, Kansas

2013

Approved by:

Major Professor Dr. William B. Kuhn

# Copyright

MATTHEW JOHN CLEWELL

2013

## **Abstract**

Designers of mixed-signal systems must understand coupling mechanisms at the system, PC board, package and integrated circuit levels to control crosstalk, and thereby minimize degradation of system performance. This research examines coupling mechanisms in a RF-targeted high-resistivity partially-depleted Silicon-on-Insulator (SOI) IC process and applying similar coupling mitigation strategies from higher levels of design, proposes techniques to reduce coupling between sub-circuits on-chip.

A series of test structures was fabricated with the goal of understanding and reducing the electric and magnetic field coupling at frequencies up to C-Band. Electric field coupling through the active-layer and substrate of the SOI wafer is compared for a variety of isolation methods including use of deep-trench surrounds, blocking channel-stopper implant, blocking metal-fill layers and using substrate contact guard-rings. Magnetic coupling is examined for on-chip inductors utilizing counter-winding techniques, using metal shields above noisy circuits, and through the relationship between separation and the coupling coefficient. Finally, coupling between bond pads employing the most effective electric field isolation strategies is examined.

Lumped element circuit models are developed to show how different coupling mitigation strategies perform. Major conclusions relative to substrate coupling are 1) substrates with resistivity  $1 k\Omega \cdot cm$  or greater act largely as a high-K insulators at sufficiently high frequency, 2) compared to capacitive coupling paths through the substrate, coupling through metal-fill has little effect and 3) the use of substrate contact guard-rings in multi-ground domain designs can result in significant coupling between domains if proper isolation strategies such as the use of deep-trench surrounds are not employed. The electric field coupling, in general, is strongly dependent on the impedance of the active-layer and frequency, with isolation exceeding 80 dB below 100 MHz and relatively high coupling values of 40 dB or more at upper S-band frequencies, depending on the geometries and mitigation strategy used. Magnetic coupling was found to be a strong function of circuit separation and the height of metal shields above the circuits. Finally, bond pads utilizing substrate contact guard-rings resulted in the highest degree of isolation and the lowest pad load capacitance of the methods tested.

## **Table of Contents**

| Tal | ole of Figure | <sup>2</sup> S                                   | vii |

|-----|---------------|--------------------------------------------------|-----|

| Tal | ble of Tables | 3                                                | xi  |

| Ac  | knowledgem    | nents                                            | xii |

| 1.  | Introduction  | on – Sources of Coupling in Real-World Systems   | 1   |

|     | 1.1 Sys       | stem-Level Coupling                              | 2   |

|     | 1.2 Bo        | ard-Level Coupling                               | 3   |

|     | 1.2.1         | Multi-Layer PC Boards                            | 3   |

|     | 1.2.2         | Separating Ground Domains                        | 5   |

|     | 1.2.3         | Bypass Capacitors                                | 6   |

|     | 1.2.4         | Vias and Other Interconnects                     | 6   |

|     | 1.3 Pag       | ckage-Level Coupling                             | 7   |

|     | 1.3.1         | Bond Wire Inductances                            | 8   |

|     | 1.3.2         | Through-Silicon Vias                             | 8   |

|     | 1.4 Ch        | ip-Level Coupling                                | 9   |

|     | 1.4.1         | Top-Level Coupling                               | 9   |

|     | 1.4.2         | Coupling through the Silicon                     | 10  |

| 2.  | Coupling N    | Mechanisms and Mitigation Techniques On-Chip     | 11  |

|     | 2.1 Bu        | lk-CMOS                                          | 11  |

|     | 2.2 Sil       | icon-on-Insulator                                | 12  |

|     | 2.2.1         | Thin-Film SOI                                    | 13  |

|     | 2.2.2         | Thick-Film SOI                                   | 14  |

|     | 2.3 Pro       | ocess Features in Thick-Film SOI                 | 16  |

|     | 2.3.1         | Substrate/Well Contacts                          | 18  |

|     | 2.3.2         | Channel-Stopper Implant                          | 18  |

|     | 2.3.3         | Deep-Trench Isolation                            | 19  |

|     | 2.3.4         | Metal-Fill Layers                                | 19  |

|     | 2.4 Mo        | otivation                                        | 21  |

| 3.  | Electric Fie  | eld Coupling                                     | 23  |

|     | 3.1 Ele       | ectric Field Coupling Analysis in Thick-Film SOI | 24  |

|    | 3.1.1             | Coupling through the Substrate                             | 24 |

|----|-------------------|------------------------------------------------------------|----|

|    | 3.1               | 1.1 Coplanar Strips                                        | 27 |

|    | 3.1.2             | 2D Surface Coupling through the Silicon Active-Layer       | 31 |

|    | 3.1.3             | Lumped Element Coupling Models                             | 32 |

|    | 3.1               | .3.1 Methods to Reduce Coupling                            | 33 |

|    | 3.2 Ex            | xperimental Array and Measurements                         | 33 |

|    | 3.2.1             | Blank Test Cell                                            | 34 |

|    | 3.2.2             | Active-Layer Resistance Coupling                           | 35 |

|    | 3.2.3             | Active-Layer Coupling with Channel-Stopper Implant Blocked | 36 |

|    | 3.2.4             | Coupling with Deep-Trench Isolation Surrounds              | 37 |

|    | 3.2.5             | Deep-Trenches with Channel-Stopper Implant Present         | 38 |

|    | 3.2.6             | Fill-Metal Coupling                                        | 39 |

|    | 3.2               | .6.1 Active-Layer Coupling with Fill-Metals Blocked        | 39 |

|    | 3.2               | .6.2 Effects of Fill-Metal on Inter-Metal Coupling         | 41 |

|    | 3.2.7             | Active-Layer Coupling with Metal-1 Guard-Rings             | 43 |

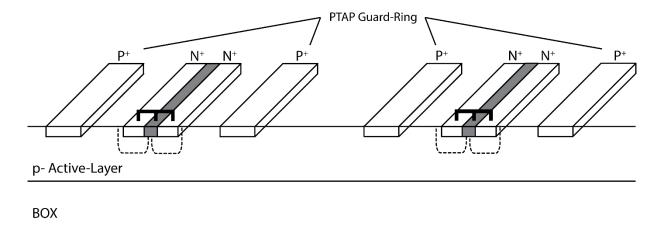

|    | 3.2.8             | N+ Diffusion Structures                                    | 44 |

|    | 3.2.9             | Use of PTAP Guard-Rings with N+ Diffusions                 | 46 |

|    | 3.3 Fu            | iture Work                                                 | 47 |

| 4. | Magnetic Coupling |                                                            | 49 |

|    | 4.1 M             | agnetic Coupling Analysis                                  | 49 |

|    | 4.2 Ex            | sperimental Structure and Measurements                     | 53 |

|    | 4.3 Fu            | iture Work                                                 | 58 |

| 5. | Bond Pad          | Coupling                                                   | 61 |

|    | 5.1 Ex            | sperimental Array and Measurements                         | 62 |

|    | 5.1.1             | Deep-Trench Grid                                           | 65 |

|    | 5.1.2             | Inserting Ground Pad                                       | 65 |

|    | 5.1.3             | PTAP Guard-Ring and Metal-1 Shield                         | 65 |

|    | 5.2 Ef            | fect of Coupling Mitigation on Pad Load Capacitance        | 66 |

|    | 5.3 Fu            | ıture Work                                                 | 66 |

| 6. | Conclusio         | n                                                          | 69 |

|    | 6.1 El            | ectric Field Coupling                                      | 69 |

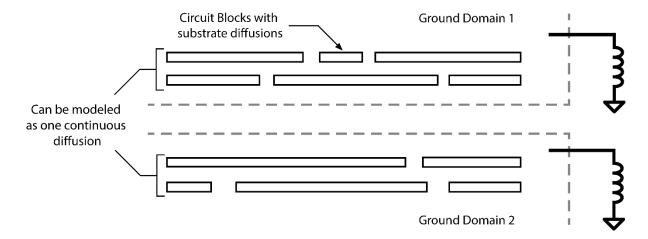

| 6.1.1 Designs with Multiple Ground Domains                   | 69 |

|--------------------------------------------------------------|----|

| 6.2 Magnetic Coupling                                        | 70 |

| 6.3 Bond Pads                                                | 71 |

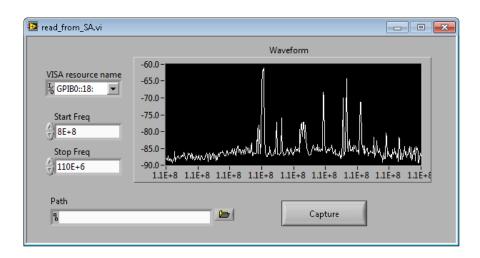

| Appendix A - Spectrum Analyzer Data Acquisition with LabVIEW | 73 |

| Appendix B - Documentation of Coupling ICs                   | 75 |

| References                                                   | 81 |

# **Table of Figures**

| Figure 1.1 – Photograph of the Kansas State University Body Area Network Board [3]              | 1    |

|-------------------------------------------------------------------------------------------------|------|

| Figure 1.2 – Example of multi-layer PC board with (a) analog circuits on the top side and (b)   |      |

| digital on the back side.                                                                       | 4    |

| Figure 1.3 – Example of (a) bus-topology and (b) star-topology.                                 | 4    |

| Figure 1.4 – Feedback path through the power supply causing oscillation in high-gain amplifi    | iers |

| [2]                                                                                             | 5    |

| Figure 1.5 – (a) Power supply filter decoupling techniques and (b) circuit model of a via       | 6    |

| Figure 1.6 – Diagram of a coplanar waveguide structure.                                         | 7    |

| Figure 1.7 – (a) Photograph of the KSU Micro-Transceiver Radio showing the bond wires in        | a    |

| QFN style package. (b) Photograph of the bottom of the QFN package.                             | 8    |

| Figure 1.8 – Currents in counter-wound inductors.                                               | 9    |

| Figure 2.1 – Typical bulk-CMOS cross-section showing coupling paths.                            | 11   |

| Figure 2.2 – Diagram of the standard cell frame.                                                | 12   |

| Figure 2.3 – Thin-film SOI technologies, (a) silicon-on-sapphire and (b) buried-oxide           | 13   |

| Figure 2.4 – Typical thick-film SOI cross-section.                                              | 14   |

| Figure 2.5 – Typical features found in thick-film SOI processes.                                | 17   |

| Figure 2.6 – Diagram of a PTAP and NTAP in thick-film SOI.                                      | 18   |

| Figure 2.7 – (a) Photograph and (b) diagram of a deep-trench grid structure.                    | 19   |

| Figure 2.8 – Photograph showing two different metal-fill patterns.                              | 20   |

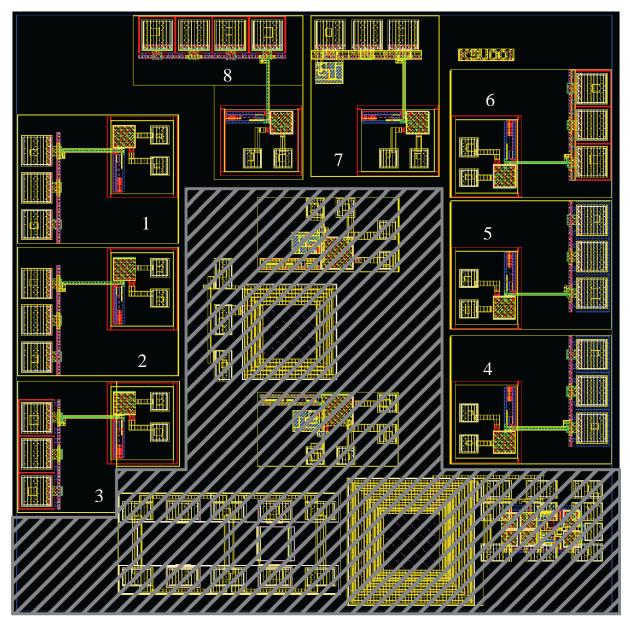

| Figure 2.9 – KSU Mars Micro-Transceiver Radio top-level layout.                                 | 21   |

| Figure 2.10 - Enlarged layout view of analog and digital sections of the KSU Micro-Transcei     | iver |

| Radio.                                                                                          | 22   |

| Figure 3.1 – Transmitter/receiver coupling structures.                                          | 23   |

| Figure $3.2 - (a)$ Capacitance due to the BOX. (b) Small region of the substrate with potential | V    |

| between the faces and (c) its circuit model.                                                    | 24   |

| Figure 3.3 – Computed frequncies above which substrates behave more as a dielectric than a      |      |

| conductor                                                                                       | 27   |

| Figure 3.4 – Cross-section of coplanar strips                                                   | 27   |

| Figure 3.5 – (a) Capacitance per unit length for CPS versus spacing and (b) equivalent spacing of                            |

|------------------------------------------------------------------------------------------------------------------------------|

| a parallel plate capacitor for the same capacitance as CPS                                                                   |

| Figure 3.6 – (a) ADS simulation schematic for the coupling between CPS for 10 $\mu m$ spacing and                            |

| (b) simulated $S_{21}$ for 5 $\mu m$ wide, 100 $\mu m$ long bars with 10 $\mu m$ spacing (red) and 100 $\mu m$               |

| spacing (blue)                                                                                                               |

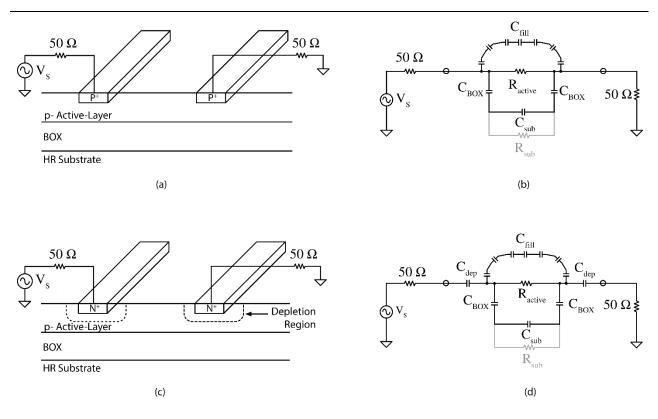

| Figure $3.7 - (a)$ Diffusion generator and receiver P+ bars in p- active-layer and (b) the simplified                        |

| lumped element circuit coupling model. (c) N+ diffusion generator and receiver bars in p-                                    |

| active-layer and (d) the simplified lumped element circuit coupling model                                                    |

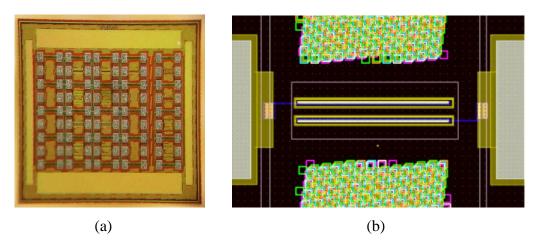

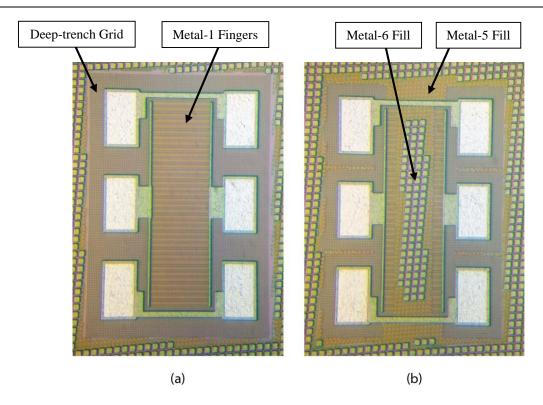

| Figure 3.8 – (a) Die photo of fabricated electric field coupling test-structure array. (b) Example                           |

| generator/receiver structure with deep-trench isolation surrounds and metal-fill layers                                      |

| blocked                                                                                                                      |

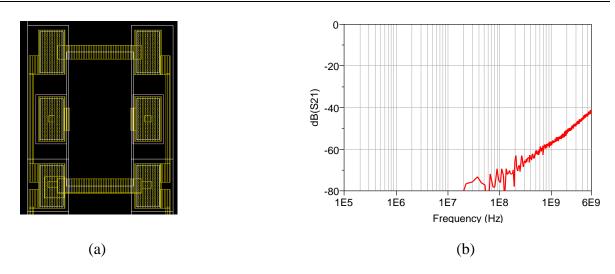

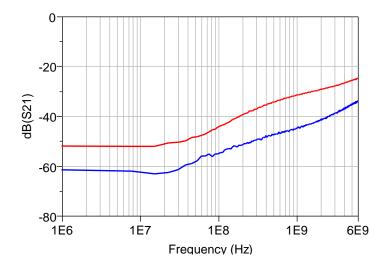

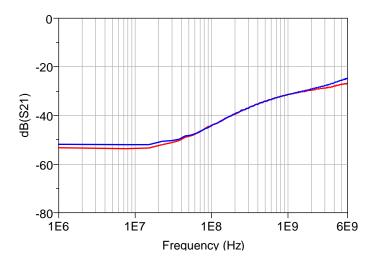

| Figure $3.9 - (a)$ Layout of blank test cell and (b) measured $S_{21}$ of the blank test cell                                |

| Figure $3.10$ – Measured $S_{21}$ for P+ diffusions in p- active-layer with 10 $\mu m$ (red) and 100 $\mu m$                 |

| (blue) separations                                                                                                           |

| Figure $3.11$ – Measured $S_{21}$ for P+ diffusions in p- active-layer with channel-stopper implant                          |

| blocked with 10 μm (red) and 100 μm (blue) separations                                                                       |

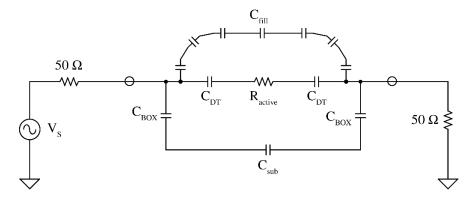

| $Figure \ 3.12-Simplified \ circuit \ model \ for \ P+ \ bars \ in \ p- \ active-layer \ with \ addition \ of \ deep-trench$ |

| series capacitance                                                                                                           |

| Figure $3.13$ – Measured $S_{21}$ for P+ diffusions in p- active-layer with deep trench surrounds and                        |

| channel-stopper implant blocked with 10 $\mu m$ (red) and 100 $\mu m$ (blue) separations 38                                  |

| Figure $3.14 - Measured S_{21}$ for P+ diffusions in p- active-layer with deep trench surrounds with                         |

| $10~\mu m$ (red) and $100~\mu m$ (blue) separations and channel-stopper present between the bars. $39$                       |

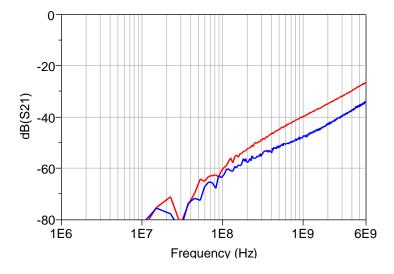

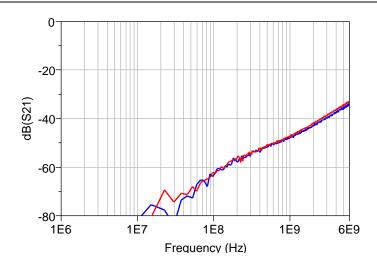

| Figure $3.15 - (a)$ Diagram showing coupling path formed from metal-fill. (b) Measured $S_{21}$ for                          |

| P+ diffusions in p- active-layer with (red) and without (blue) metal-fill layers blocked with                                |

| 100 μm separation                                                                                                            |

| Figure $3.16$ – Measured $S_{21}$ for P+ diffusions in p- active-layer with deep-trench surrounds and                        |

| channel-stopper blocked, with (red) and without (blue) the metal fill layers blocked, using                                  |

| 100 μm bar separation                                                                                                        |

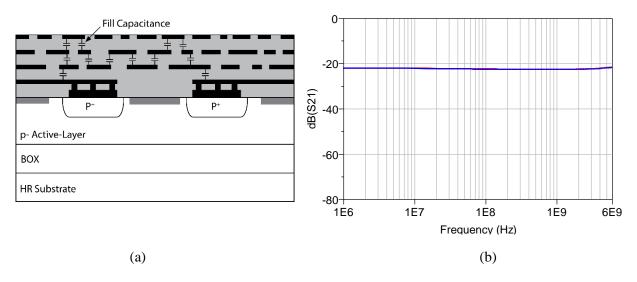

| Figure 3.17 – (a) Simplified diagram of the Metal-1 interdigitated planar capacitor and (b)                                  |

| lumped element circuit coupling model                                                                                        |

| Figure 3.18 – Photograph of the interdigitated Metal-1 structures, (a) with metal-fill and (b)       |

|------------------------------------------------------------------------------------------------------|

| without42                                                                                            |

| Figure $3.19 - Measured S_{21}$ of the interdigitated test structures in Figure 3.18 with (red) and  |

| without (blue) metal-fill above the fingers                                                          |

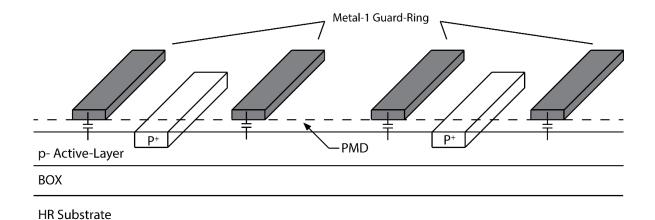

| Figure 3.20 – Diagram of P+ diffusions in p- active-layer with Metal-1 guard-ring                    |

| Figure $3.21$ – Measured $S_{21}$ for P+ diffusions in p- active-layer with a metal-1 electrostatic  |

| guard-ring (red) and without guard-ring (blue), with 10 µm separation (metal-fill and                |

| channel-stopper implant are blocked)                                                                 |

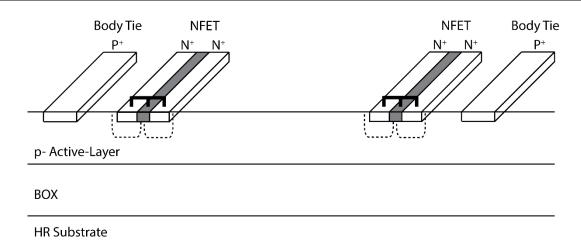

| Figure 3.22 – Diagram of the NFET test structure showing grounded body-ties on either side of        |

| the FETs                                                                                             |

| Figure $3.23 - (a)$ Measured $S_{21}$ for zero-biased NFETs with no coupling mitigation (red) and P+ |

| diffusions in p- active-layer with deep trench surrounds (blue), using two $100/0.18~\mu m$          |

| NFETs with 10 μm separation. (b) Simulated S <sub>21</sub> for the former case                       |

| Figure 3.24 – Lumped element model for Figure 3.22, with body-ties represented as resistors to       |

| ground                                                                                               |

| Figure $3.25$ – Measured $S_{21}$ for biased NFETs with PTAP guard-ring surround (red) and P+        |

| diffusion in p- active-layer with deep trench surround (blue), using 100/0.18 µm NFETs               |

| with 10 μm separation46                                                                              |

| Figure 3.26 – Diagram of N+ diffusions in p- active-layer with PTAP guard-ring surrounds 47          |

| Figure 3.27 – Layout of new blank test cell with deep-trench grid under the signal pads (left) and   |

| 100/0.18 μm NFETs separated by 100 μm with PTAP guard-ring and deep-trench surrounds                 |

| (right)                                                                                              |

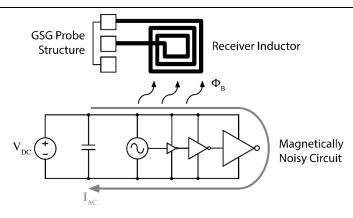

| Figure 4.1 – Model of the basic magnetic test structure consisting of a noise generator and an on-   |

| chip planar spiral inductor                                                                          |

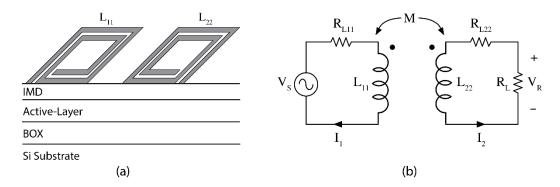

| Figure 4.2 – (a) Mutually coupled generator and receiver inductors and (b) simplified circuit        |

| model50                                                                                              |

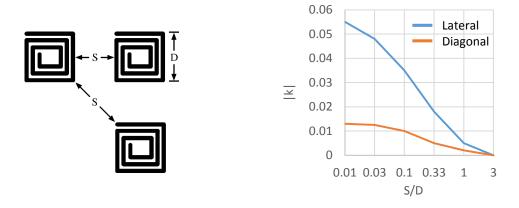

| Figure 4.3 – Coupling coefficient versus inductor spacing (used with permission from [52]) 51        |

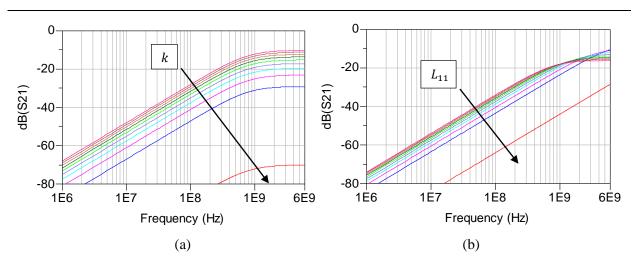

| Figure $4.4$ – Simulated $S_{21}$ for two mutually coupled inductors while k is varied and (b)       |

| simulated S <sub>21</sub> with a fixed k and varying generator inductance                            |

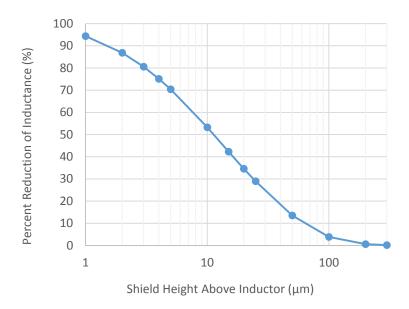

| Figure 4.5 – Plot of the reduction of inductance in a single loop inductor due to metal shield       |

| height53                                                                                             |

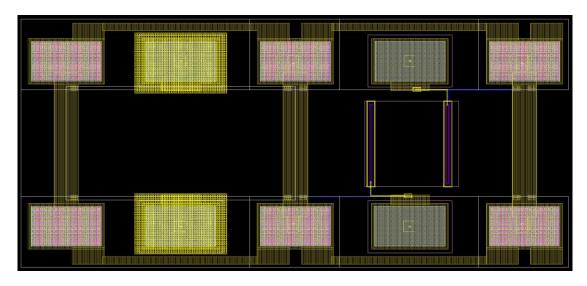

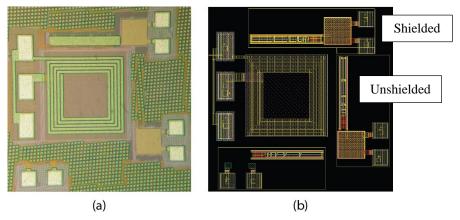

| Figure $4.6 - (a)$ Photograph of fabricated magnetic test structure and (b) layout view of the        |          |

|-------------------------------------------------------------------------------------------------------|----------|

| structure                                                                                             | 54       |

| Figure 4.7 – Layout of a generator structure from Figure 4.6.                                         | 54       |

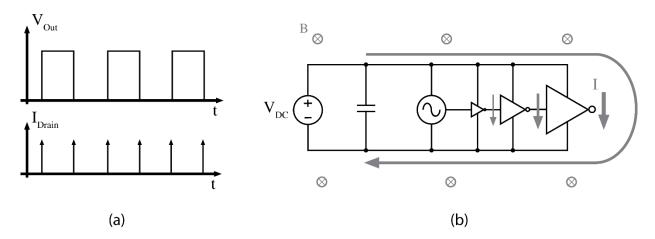

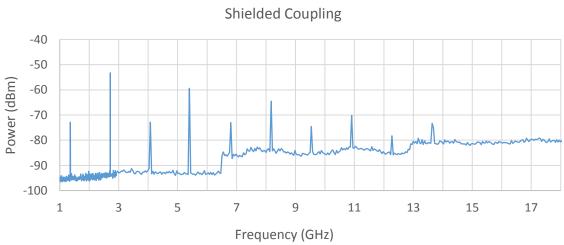

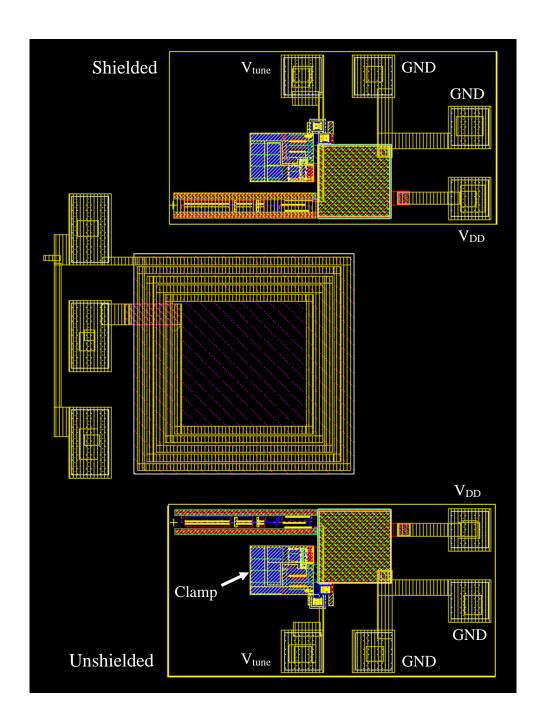

| Figure 4.8 – (a) CMOS inverter switching characteristics and (b) schematic of the basic               |          |

| generator structure showing currents and magnetic field lines.                                        | 55       |

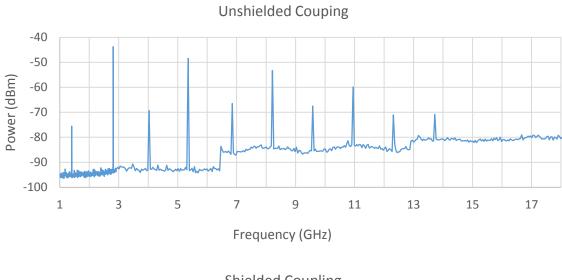

| Figure $4.9 - \text{Magnetic}$ coupling without metal shield (top) and with metal shield (bottom)     | 57       |

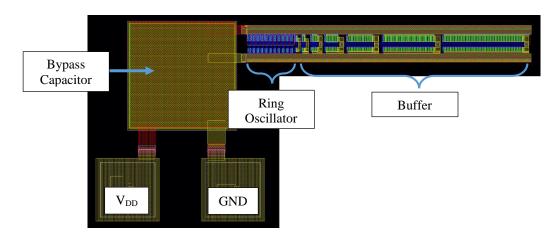

| Figure 4.10 – Magnetic test structure with variable frequency noise generators                        | 59       |

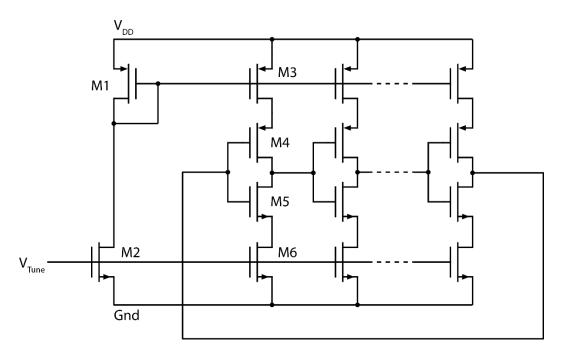

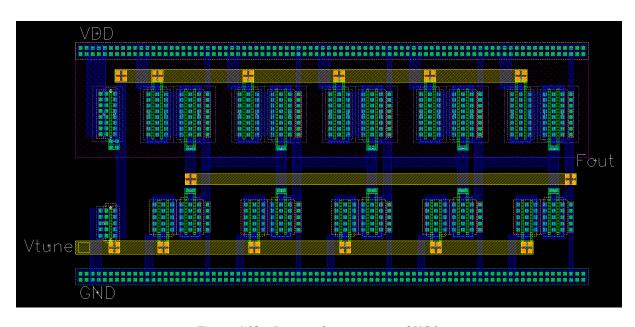

| Figure 4.11 – Current-starved VCO schematic                                                           | 60       |

| Figure 4.12 – Layout of current-starved VCO.                                                          | 60       |

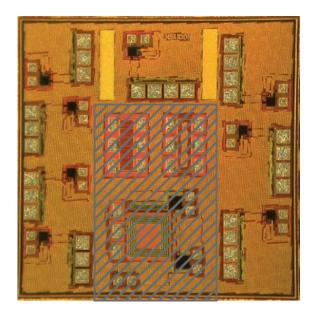

| Figure 5.1 – Photograph of the pad coupling test structure chip                                       | 62       |

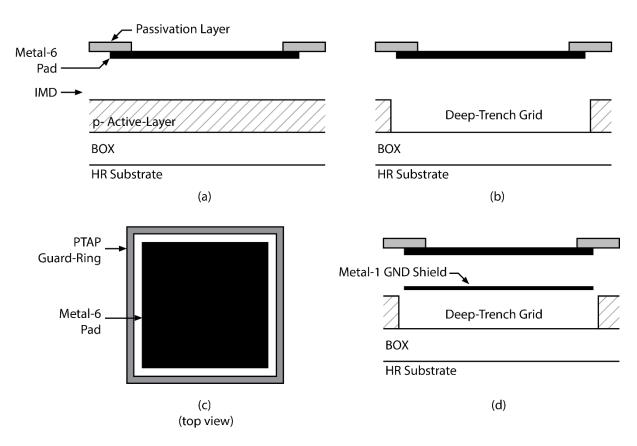

| Figure 5.2 –Diagram of the different bond pad coupling mitigation techniques                          | 63       |

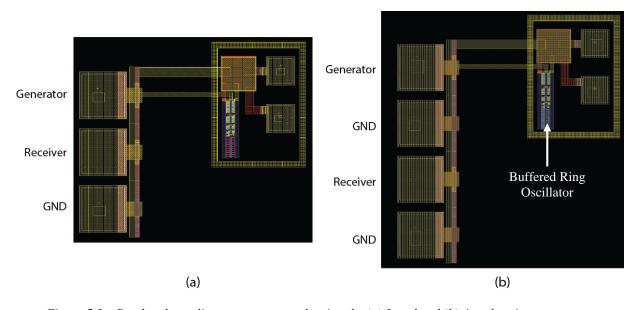

| Figure 5.3 – Bond pad coupling test structures showing the (a) 3-pad and (b) 4-pad variant            |          |

| structures.                                                                                           | 63       |

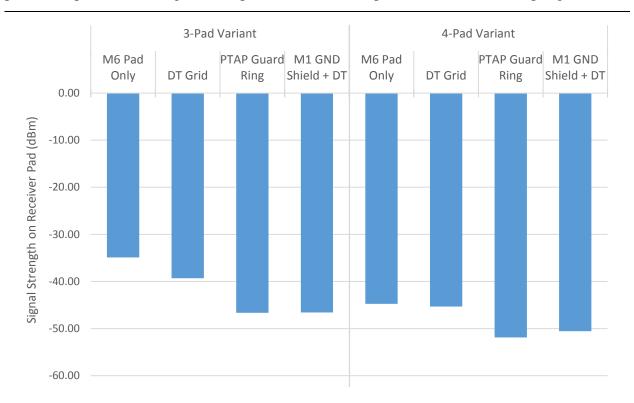

| Figure 5.4 – Measured strength of the fundamental of the signal (1.5 GHz) coupled from the            | <b>;</b> |

| generator pad to the receiver pad for both the 3-pad (left) and 4-pad test structures (righ           | ıt). 64  |

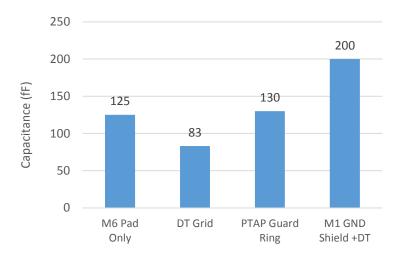

| Figure 5.5 – Measured pad load capacitance with the coupling mitigation techniques applied            | l 66     |

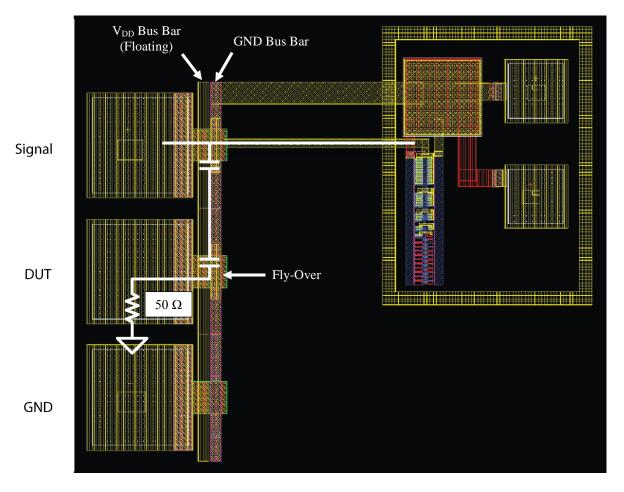

| Figure $5.6$ – Diagram showing coupling path between bond pads through a floating $V_{\text{DD}}$ bus | bar.     |

|                                                                                                       | 67       |

| Figure 5.7 – Layout of the new chip with updated pad coupling test structures                         | 68       |

| Figure 6.1 – Coupling between ground domains when using substrate contact guard-rings (la             | ayout    |

| top-view)                                                                                             | 70       |

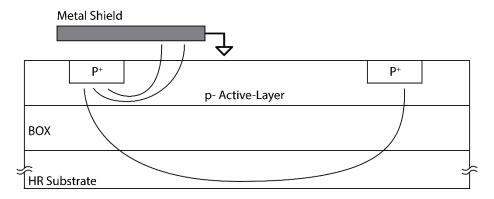

| Figure 6.2 – Metal shield reducing electric field coupling.                                           | 71       |

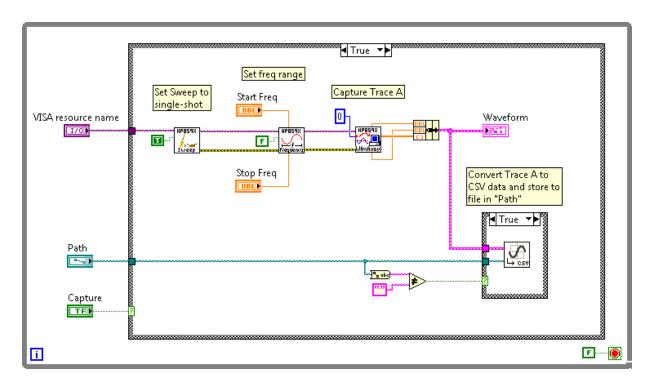

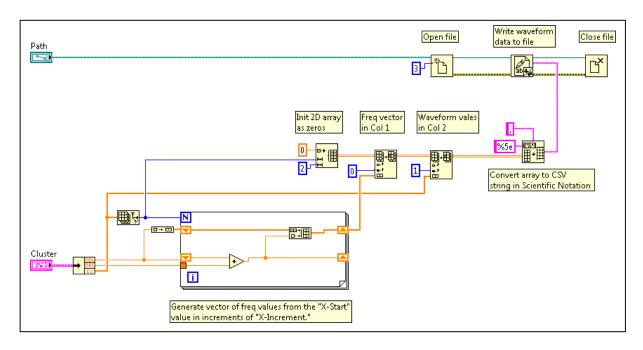

| Figure A.1 – Front panel view of the Spectrum Analyzer Data Acquisition LabVIEW Tool .                | 73       |

| Figure A.2 – LabVIEW VI of the Spectrum Analyzer Data Acquisition LabVIEW Tool                        | 74       |

| Figure A.3 – LabVIEW VI to save a waveform as a text file in the CSV format                           | 74       |

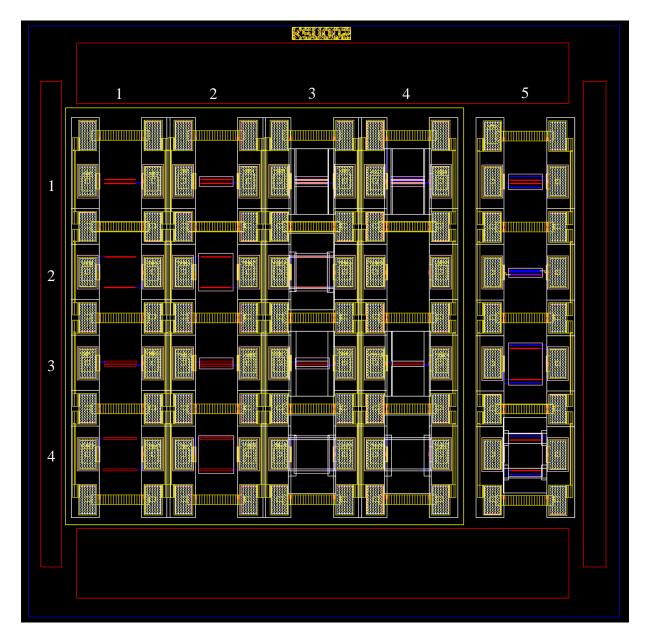

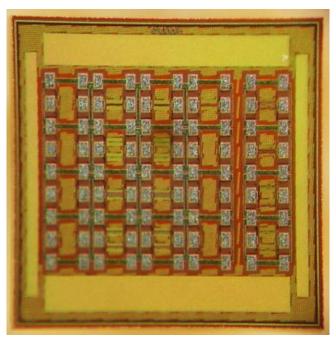

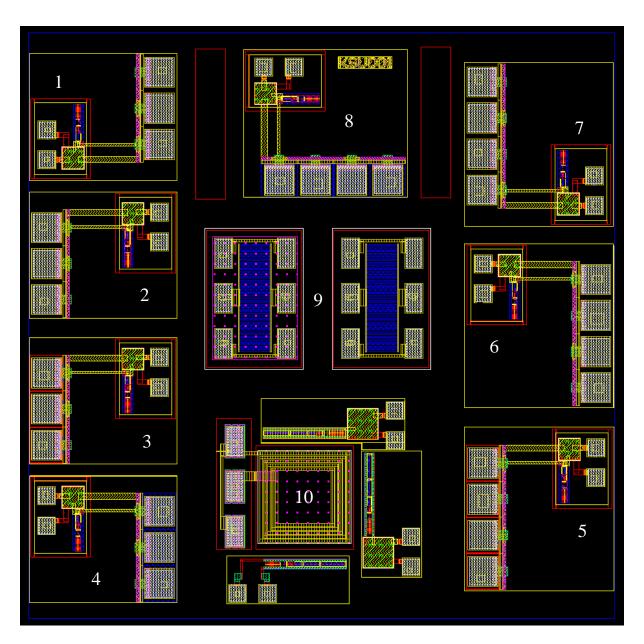

| Figure B.1 – Electric field coupling test chip layout.                                                | 75       |

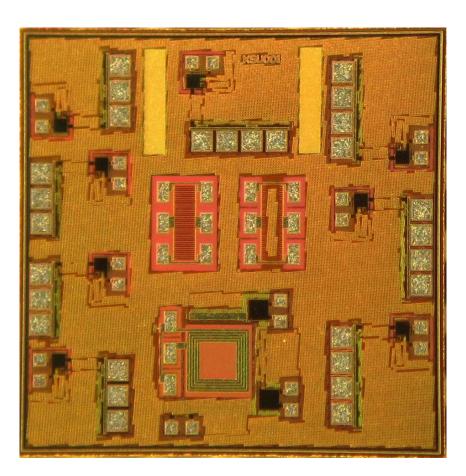

| Figure B.2 – Photograph of the electric field test array IC.                                          | 76       |

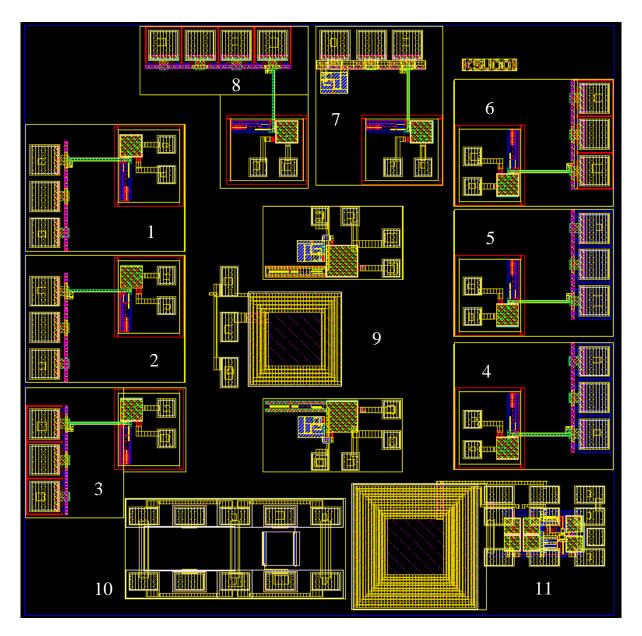

| Figure B.3 – Magnetic and pad coupling test chip (Version 1).                                         | 77       |

| Figure B.4 – Photograph of the magnetic/pad coupling test IC (Version 1)                              |          |

| Figure B.5 – Magnetic and pad coupling test chip (Version 2).                                         | 79       |

## **Table of Tables**

| Table 2.1 – Representative parameter values for a thick-film SOI process                          | 17     |

|---------------------------------------------------------------------------------------------------|--------|

| Table 3.1 – Measured Ractive parameters for P+ diffusions in Figure 3.10.                         | 35     |

| Table $3.2-Measured\ R_{active}$ and $X_c$ parameters for the P+ diffusions with the channel-stop | per    |

| implant blocked                                                                                   | 36     |

| Table $3.3$ – Measured $X_c$ values for the P+ diffusions with deep-trench surrounds extracted    | l from |

| Figure 3.13                                                                                       | 38     |

| Table 5.1 – Description of new pad coupling structures from Figure 5.7                            | 68     |

| Table B.1 – Cell descriptions of the electric field coupling test chip array                      | 76     |

## Acknowledgements

This work was supported in part by a research contract with Sandia National Laboratories. Sandia National Laboratories is a multi-program laboratory managed and operated by Sandia Corporation, a wholly owned subsidiary of Lockheed Martin Corporation, for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-AC04-94AL85000. Research was also supported under NASA EPSCoR Project NNX11AM05A.

## 1. Introduction – Sources of Coupling in Real-World Systems

Designers of mixed-signal integrated circuits need to understand coupling mechanisms to control cross-talk between circuit blocks and thereby minimize the degradation of system performance. The objective of this thesis is to provide IC designers with a guide to reduce undesired coupling on-chip. Although this research primarily focuses on analog RF systems designed in Silicon-on-Insulator (SOI) substrates, this work can be of use to any IC designer no matter the frequency or substrate.

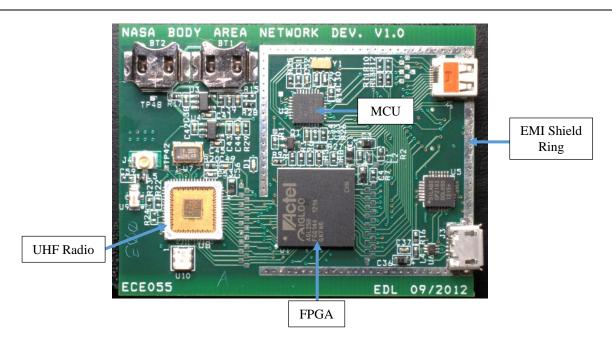

To illustrate some of the issues in a complex, mixed-signal system, the Kansas State University Body Area Network (BAN) board will be used as an example [1]. A photograph of this board is shown in Figure 1.1. The BAN board is designed to harvest energy from the environment and using that energy, report biometric sensor data wirelessly to another radio. This system contains a UHF radio, microcontroller (MCU), FPGA, and analog sensors on a companion daughter board (not pictured). The UHF radio communication link is provided by the KSU Micro-Transceiver [2]. This radio integrates a complete RF frontend including a transmitter, receiver, M-PSK modulator, baseband IF and synthesizer on a single 9 mm<sup>2</sup> chip.

Figure 1.1 – Photograph of the Kansas State University Body Area Network Board [3].

## 1.1 System-Level Coupling

Before the in-depth analysis of coupling issues on-chip, circuit designers should note that many of the same coupling issues that plaque the integrated circuit world are present in higher levels of product design. Therefore it is beneficial to address some of the more common coupling issues that are present at the various levels of product design and their mitigation strategies.

The first area to address coupling issues is at the system-level in the early design phases of a product. Major architectural design decisions at this level can have a significant impact on coupling, system performance and complexity. In the KSU radio, for instance, the choice of whether to operate in full-duplex or half-duplex mode was a significant driver for the coupling mitigation strategies employed later in the circuit design. If operating in full-duplex, the strong signal from the transmitter could couple into the sensitive receiver and degrade performance, whereas only operating in half-duplex mode, the transmitter is off during receive. The latter mode was chosen to decrease system complexity and development time.

The type of power supplies and regulators employed is another important system-level consideration. Switch-Mode Power Supplies (SMPS) are used for battery powered applications due to their high efficiency. However to obtain high efficiency and small size, high-amplitude energy must be switched at high frequencies. The electromagnetic interference (EMI) from the switching frequency and its harmonics can couple into other circuit blocks in the same system or even disrupt outside systems – in particular a nearby antenna. Due to the small form-factor of the BAN board and the sensitive UHF radio, less efficient linear regulators were used.

One common technique to gain some immunity from noise sources such as SMPS is to use differential signaling. In most situations, electric field induced EMI will couple onto both signaling lines of the differential circuit equally. Due to the high common-mode rejection characteristics of differential circuits, their noise immunity is much higher than single-ended circuits. However, differential circuits may increase the complexity of designs and the static power dissipation due to their Class-A nature. Differential signaling is not just limited to the system-level – most of the sensitive RF sections on the KSU radio are differential.

Formulating a frequency plan to identify critical system frequencies and bandwidths is another important technique in high performance mixed-signal systems. Clocks from devices such as MCUs and FGPAs can generate numerous harmonics over a wide range of frequencies that can couple into sensitive subs-systems. Identifying critical bandwidths and choosing clock

frequencies to avoid in-band interference can decrease complexity and increase performance by not requiring sub-systems to filter intra-system interferers. For example, if a SMPS is used in conjunction with an audio sub-system, selecting the switching frequency outside the range of human hearing can minimize undesired signals from falling in the audio band. On the BAN board, the clocks for the MCU, FPGA and synthesizer reference were chosen to prevent their harmonics from falling close to a desired receive channel or image frequency of the receiver. Other important considerations the frequency plan should include are loop bandwidths of synthesizers and IF bandwidths in receivers. If the system is to operate in an environment with strong external interferes, such as those from the cellular and ISM bands, these frequencies must also be addressed.

## 1.2 Board-Level Coupling

The next level where coupling issues should be addressed is the PC board-level. Perhaps the most well studied level, designers recognize early on the potential for coupling problems, especially in mixed-signed environments. Digital logic families such as TTL and CMOS have large switching currents that can produce significant amounts of EMI. Other digital circuitry on the PC board may be immune due to their high noise margins; however analog circuitry does not usually have this luxury.

## 1.2.1 Multi-Layer PC Boards

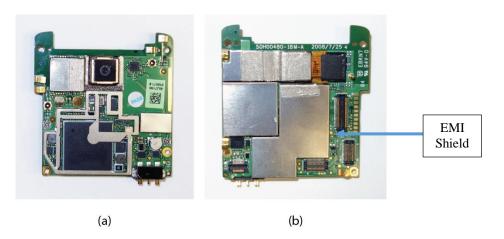

One effective way to isolate digital and analog circuit blocks is to use a multi-layer PC board. With a four-layer board, for instance, digital circuits can be routed on the top layer and analog circuits on the bottom, such as shown in the commercially designed cell-phone PC board in Figure 1.2. Within the board itself, the two inner layers then can be used for power and ground. The power and ground planes act similar to an EMI shield, reducing the coupling between the top and bottom signal layers. In an ideal situation, each signal layer would be buried between two ground planes to form a coaxial cable like structure called stripline [4]. However, this increases the cost and complexity of the PC board and is usually unnecessary. For example, the BAN board shown previously in Figure 1.1 contains a high gate-count FPGA together with a UHF receiver operating to levels as low as -120 dBm (0.22  $\mu$ V into 50  $\Omega$ ) with a four layer board on which both analog/RF and digital circuits co-located on the top layer, with a solid

Figure 1.2 – Example of multi-layer PC board with (a) analog circuits on the top side and (b) digital on the back side.

ground plane 12 mil below. Successful operation is achieved thanks to careful routing at the PC board-level and frequency planning at the system-level.

If further EMI mitigation is needed, grounded metal shielding structures can be soldered directly to the board (also present on the PC board in Figure 1.2). On the BAN board in Figure 1.1, a ring of copper was left exposed to attach an optional EMI shield. Stitching vias can be seen along the ring to create a low impedance path to ground. This optional shield may be used when this board is combined with a daughter board which forms a capacitively loaded top hat antenna [5], since the antenna represents a much more vulnerable component in the system if it is to be operated in receive-mode.

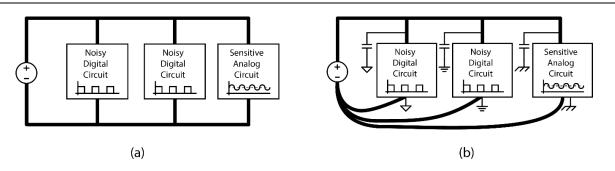

With a more limited number of layers in the PC board, an effective way to isolate circuit blocks is to keep the analog and digital supply and ground currents separate. In Figure 1.3a, the sensitive analog circuit can be seen connected to noisy digital circuit blocks using a bus topology. The strong switching currents the digital blocks draw from the power supply can

Figure 1.3 – Example of (a) bus-topology and (b) star-topology.

induce ripple on the supply voltage due to the non-ideal nature of the power supply and the non-zero impedances in the power supply trace on the PC board.

### 1.2.2 Separating Ground Domains

A good approach for connecting the grounds of circuit blocks in a limited two layer PC board environment may be to use the star-topology shown in Figure 1.3b. An even more ideal approach is to use the star-topology for *both* the power and ground rails [6], [7]. However, in complex designs this may be unfeasible. As shown in Figure 1.3b, each of the three circuit blocks has an individual connection to the return on the power supply. This could also be realized on a 4-layer circuit board by providing individual subdivided ground planes for each of the digital and analog circuit blocks (denoted with the different ground symbols in Figure 1.3b). Each of the grounds domains will then need to connect to the return of the power supply at some point on the PC board. Care must be taken to ensure that this point does not cause the ground domains to interact. For this reason, a single, unbroken ground plane is more typically used [8].

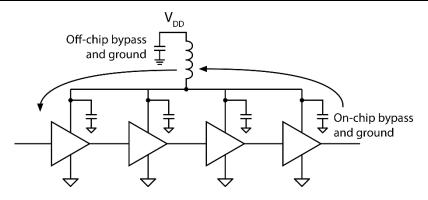

Coupling between circuit blocks in the same ground domain can also occur due to feedback in the power-supply rails. Take for example the case of a series of cascaded amplifiers shown in Figure 1.4. The last amplifier will pull strong currents from the power supply and can cause voltage ripples to appear on the power supply rail. The now modulating power supply rail can produce a signal at the amplifier input. This ripple will then be amplified by the first amplifier. The amplified ripple is then amplified by the next stage which is also amplifying the ripple seen on the power supply. This then continues through the chain of amplifiers, eventually causing it to oscillate if the loop-gain is sufficiently high. The solution to this problem is to employ bypass capacitors as shown.

Figure 1.4 – Feedback path through the power supply causing oscillation in high-gain amplifiers [2].

### 1.2.3 Bypass Capacitors

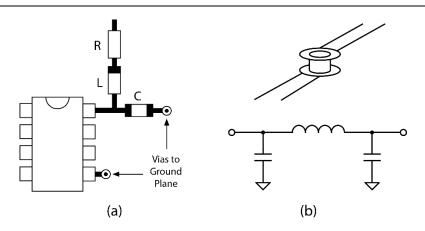

Adding bypass (decoupling) capacitors is one common – and necessary – method to reduce the feedback issues caused by signals injected onto the power supply rail. The signal injection is reduced by providing the signals with a low impedance path to ground through the bypass cap. As the clock frequencies of designs increases, the parasitic properties of the bypass capacitors must also be taken into account. As the frequency increases above the self-resonant frequency (SRF), the capacitor will begin to act more and more like an inductor [9], limiting its ability to create the desired AC path to ground. Care must to taken to ensure proper capacitors with sufficiently high SRFs and sufficiently short interconnects are used in high frequency designs.

In conjunction with bypass capacitors, further power supply isolation can be achieved by placing an inductor in series with the power supply (Figure 1.5a). If a SMD inductor is used, the response of the LC filter combined with the supply source impedance can result in resonances and very poor bypassing at select frequencies. A resistor can be placed in series to lower the quality-factor of the LC resonator ("de-Q it"), however the resistance must be kept small to minimize IR drops. Alternatively, a ferrite bead could be used. At low frequencies (<100 KHz) they act as inductors. However, at high frequencies ferrites beads are very resistive [10]. Hence they pass the DC supply current while blocking signal currents, as desired.

#### 1.2.4 Vias and Other Interconnects

One final issue board-level designers must consider is the parasitic nature of vias and other interconnects on PC boards. An equivalent lumped element circuit model of a via is shown in Figure 1.5b [11]. The non-ideal nature of vias can create discontinuities in microwave structures

Figure 1.5 – (a) Power supply filter decoupling techniques and (b) circuit model of a via.

Figure 1.6 – Diagram of a coplanar waveguide structure.

such as microstrip and stripline which can degrade RF performance. Moreover, the inductance inherent in vias create non-negligible impedances at RF frequencies between the ground pins of IC packages or bypass capacitors and the ground node on a PC board. Currents flowing through these impedances create "ground-bounce" voltages. Just as before, the ground-bounce can cause feedback and oscillation. One way to reduce this effect is to reduce the inductance in the via. This can be done by physical shrinking the length of the via by using thinner PC boards. Another simple way to reduce the inductance is to use multiple vias for ground. This effectively makes the via inductances appear in parallel, reducing the overall inductance seen by a circuit node. This technique necessarily causes the associated ground conductors on the surface of the board to become larger and the ground is effectively moved to the surface. The resulting surface artwork then takes on a form of a coplanar waveguide (CPW) structure (Figure 1.6), which can allow operation well into the microwave and millimeter wave bands [12].

## 1.3 Package-Level Coupling

Another source of ground-bounce is the package used to mount the integrated circuit to the PC board. The pins from the package to the PC board and associated bond wires within the package also contribute to total parasitic inductance seen by the integrated circuit and must be taken into account when considering high-frequency analog or high-speed digital designs. Bulky DIP (dual-inline package) style packages with long pins have been replaced with slimmer gull-wing type surface-mount packages such as QFP (quad-flat package). For even higher speed designs, lead-less QFN (quad-flat, no-leads) style packages are becoming the norm. BGA (ball-grid array) style packages are often used for very high pin count ICs such as processors and memory. For high performance RF designs, the IC can be flipped over and soldered directly to the PCB in a processed called flip-chip [13]. All of these different packaging technologies strive to reduce the length of the leads and thus the parasitic inductance.

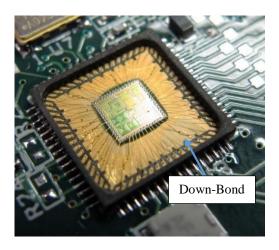

Figure 1.7 – (a) Photograph of the KSU Micro-Transceiver Radio showing the bond wires in a QFN style package. (b) Photograph of the bottom of the QFN package.

#### 1.3.1 Bond Wire Inductances

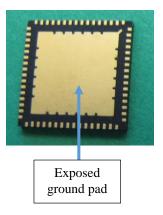

If using a package technology that requires wire bonding, the inductance of the bond wires must be considered. Typical bond wire inductances are on the order of 1 nH/mm and just like vias on a PC board, present non-negligible impedances at RF frequencies. The KSU radio shown in Figure 1.7a is mounted inside a QFN package with an exposed ground pad (Figure 1.7b). A series of vias connect the exposed ground pad to the ground plane below the IC on the BAN board of Figure 1.1 to create a low impedance ground. The chip is bonded to the package paddle (gold surface in Figure 1.7a) which is directly connected to the exposed ground pad on the bottom of the package. To reduce the length of the bond wires connecting the grounds of the IC, they can be "down-bonded" directly to the paddle instead of to the lead frame of the QFN package. By using down-bonds, the bond wire length and therefore its inductance can be cut in half. As with vias, if even lower inductance is needed, multiple pins in parallel may be used as ground returns.

## 1.3.2 Through-Silicon Vias

If the integrated circuit process supports back-of-the-wafer metallization, through-silicon vias (TSV) can be used to connect the on-chip grounds directly to the paddle [14]. Similar to vias on a PCB board, TSVs allow a connection from the metal layers on the top of the IC to the backside of the wafer. Depending on the thickness of the wafer, TSVs have the potential to reduce the ground inductance even further than using down-bonds. The drawback is that they consume large

areas on chip, require extra processing and increase the cost of the wafer. Common processes that support TSVs are GaAs and SiGe where microwave and millimeter wave operation is targeted.

## 1.4 Chip-Level Coupling

The final level at which coupling analysis should be performed and the focus of this thesis is the chip-level. Many of the same coupling mitigation techniques used in the previous levels of design are useful when attempting to address the issues of on-chip coupling. Similar to PC boards, both internal and external signals can couple into sensitive sub-circuits and degrade performance. As with the previous discussion, coupling mitigation on-chip can be broken into top-level and silicon-level strategies.

## 1.4.1 Top-Level Coupling

The use of differential circuits is critical for noise immunity from both internal and external signal sources. The KSU radio makes extensive use of differential circuit topologies in subcircuits such as the LNA, mixer, IF amplifiers, VCO and modulator [2]. EMI shields can be realized on-chip by placing metal floods over noisy circuit blocks. In [15] a thin magnetic film of CoZrNb applied to magnetically noisy circuits showed improvements in reducing coupling. However, this technique is outside the features offered by typical commercial processes. In [16] magnetic shields to reduce coupling between adjacent traces are proposed. In the KSU radio, a grounded metal flood was placed over the noisy digital synthesizer to reduce the amount of

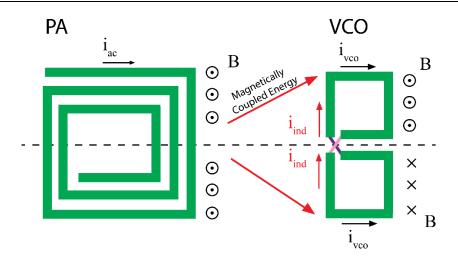

*Figure 1.8 – Currents in counter-wound inductors.*

magnetic coupling into the sensitive receiver.

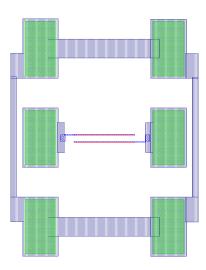

Further EMI suppression can be obtained by counter-winding on-chip spiral inductors in differential circuits such as LNAs and VCOs [2]. Figure 1.8 shows the relationship of the windings of the inductors in the PA and VCO of the KSU radio. The strong currents in the PA inductor can couple magnetically (and to a lesser extent through electric field lines) into the VCO. These currents could potentially pull the phase of the VCO and corrupt the transmitted M-PSK signal constellation or even prevent the synthesizer from locking the VCO. The current labeled  $i_{vco}$  in Figure 1.8 represents the nominal oscillation current of the VCO. The magnetic field from the PA inductor will induce a voltage and hence a current  $i_{ind}$  in the inductors of the VCO. Since the VCO inductors are positioned on the center-line of the PA inductor, the induced currents should couple equally onto each of the VCO inductors. The induced currents will flow through the inductors in opposite directions and cancel. Furthermore, the current  $i_{vco}$  in the counter-wound VCO inductors produces a zero net magnetic field outside the two inductors, at least along the dotted centerline shown. This has the added benefit of reducing the amount of coupling from the VCO to other parts of the radio, such as the LNA in the receiver.

Chip designers must also be aware of ground-bounce issues at the chip-level. The high sheet-resistances of the metals due to small geometries in semiconductors can result in significant IR-drops. Wide metals therefore should be used to ensure low impedance power and ground paths. Due to the inductance of bond wires, further on-chip decoupling should be provided to form solid AC grounds where possible. Another way to combat supply noise is to use active RC filters on the supply lines such as those used on KSU radio in [2]. These supply filters in conjunction with the off-chip bypass capacitors on the supply attenuate signals on the power supply rails in the high-gain IF amplifier subsection of the radio to prevent oscillation.

#### 1.4.2 Coupling through the Silicon

Unlike the thick, insulative materials typically used in PC boards, the semiconducting substrate used in most ICs has the potential for many non-ideal coupling situations. This causes the coupling analysis in processes such as bulk-CMOS and SOI to be much more complicated than PC board level coupling issues. In the following chapters, the various coupling mechanisms on-chip will be explored along with their different coupling mitigation strategies.

## 2. Coupling Mechanisms and Mitigation Techniques On-Chip

Over the history of integrated circuits, many different wafer technologies have been developed for various applications. However, the primary driving force behind these new technologies has been integration. To achieve this goal, mixed-signal sub-systems that were once separate, such as receivers, transmitters and synthesizers, are being incorporated on the same physical die. To allow IC designers to build more highly integrated chips, the coupling mechanisms and mitigation strategies must be well understood. This research focuses on characterizing the coupling mechanisms and formulating mitigation strategies to reduce coupling in a relatively new IC design process type: partially-depleted silicon-on-insulator (SOI).

## 2.1 Bulk-CMOS

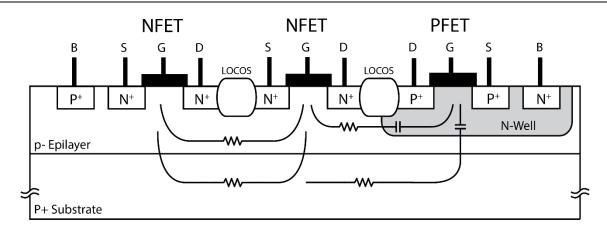

Before SOI is examined, it is beneficial to briefly look at coupling issues present in bulk-CMOS. Bulk processes are appealing to designers due to their simplicity and low cost. A typical wafer consists of a highly doped substrate of single crystalline electronics-grade silicon on the order of 800 µm thick with a lightly doped epitaxial layer (epilayer) on the order of a few microns developed to combat issues of latchup [17]. Figure 2.1 shows the cross-section of a typical bulk-CMOS wafer. In this technology, NFETs are developed in the p- epilayer, while PFETs developed in separately doped N-wells.

Bulk processes create many non-ideal situations when attempting to address issues of crosstalk. Devices have a direct DC coupling path to other circuit blocks through the epilayer. The issue of coupling reduction has been previously addressed in bulk-CMOS technologies

Figure 2.1 – Typical bulk-CMOS cross-section showing coupling paths.

Figure 2.2 – Diagram of the standard cell frame.

through the use of LOCOS (local oxidation of silicon [18]), STI (shallow-trench isolation [19]), guard-rings, buried layers and differential circuits [20]–[23]. LOCOS, STI, and guard-rings can be effective at reducing the coupling through the lightly doped epilayer. However, they are ineffective at reducing coupling for signals injected into the highly doped P+ substrate which creates a low impedance coupling path between active devices [20]. Due the effectiveness of this coupling path once signals are injected into the substrate they can couple into circuitry a great distance from the source. Buried layers and triple-well processes [24] can be used to reduce deep-substrate coupling, however they increase the wafer cost.

The junction capacitance between N-wells and the p- epilayer can also be used to reduce surface coupling. Lower frequency signals can be contained in their respective wells by keeping P devices in a continuous n-well and N devices in a continuous p-well, as shown in Figure 2.2. Power and ground rails can be routed on the top and bottom and substrate contact guard-rings can be added for isolation. This method of routing is called the standard cell-frame [25] and is widely used in bulk-CMOS and other wafer technologies to improve auto-routing in VLSI algorithms and to reduce the effects of latchup. This technique is also referred to as the *line-of-diffusion*, recognizing the long, continuous strips of n-well and p-well.

#### 2.2 Silicon-on-Insulator

Silicon-on-Insulator (SOI) technologies attempt to address some of the major challenges of bulk-CMOS – namely increasing device speed and reducing power consumption [26]. In these technologies, a thin layer of silicon is grown on an insulating material, such as sapphire or SiO<sub>2</sub>, backed with a silicon "handle" wafer. In fact, the first patented transistor was fabricated using

SOI by J. E. Lilienfield in 1926 [27]. Though the technology in Lilienfield's time was not developed enough to successfully create his transistor, today there are many different foundries manufacturing many different types of SOI. These wafers can be broken into two main categories based on the thickness of the top layer of silicon: thin-film and thick-film.

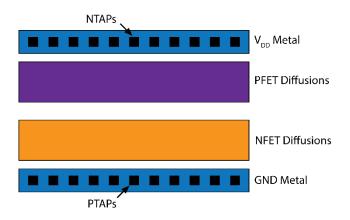

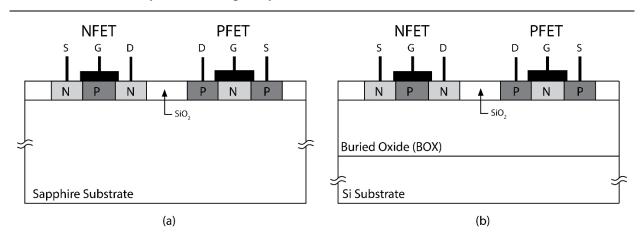

#### 2.2.1 Thin-Film SOI

In thin-film SOI technology, a thin layer (≤ 100 nm) of epitaxial silicon is grown on an insulating substrate, such as sapphire [28]. This type of process is called Silicon-on-Sapphire (SOS) and is shown in Figure 2.3a. As an alternative to the use of sapphire, the thin layer of silicon can be separated from a silicon substrate by a layer of buried oxide (BOX) on the order of 0.5 − 1 µm thick [26], as shown in Figure 2.3b. Thin-film SOI processes are sometimes referred to as fully-depleted (FD-SOI) recognizing that the channel region of MOSFETs extends from the gate oxide to the insulating layer (the BOX, or sapphire substrate in the case of SOS). This leaves no neutral piece of silicon in the MOSFET and thus no body contacts are needed unlike bulk-CMOS [29]. However this can lead to the degradation of the I-V characteristic of MOSFETs due to the floating-body effect [30].

The main advantage of thin-film SOI comes from the ultra-thin silicon layer. Since this layer is so thin, it can be etched away or oxidized in the regions outside of active-devices, dielectrically isolating adjacent devices and eliminating the DC coupled surface path. The primary coupling path is then through the insulating substrate, but only at high frequencies. As shown in [31], the degree to which thin-film SOI can reduce coupling is a strong function of both the substrate resistivity and the frequency.

Figure 2.3 – Thin-film SOI technologies, (a) silicon-on-sapphire and (b) buried-oxide.

#### 2.2.2 Thick-Film SOI

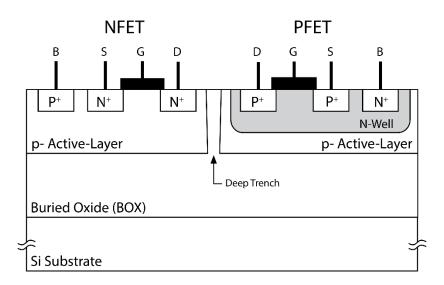

In thick-film SOI processes, a much thicker layer of silicon on the order of 1 µm sits above an insulating layer such as SiO<sub>2</sub> (Figure 2.4). Unlike thin-film technologies, the channels of thick-film MOSFETs *do not* extend to the BOX layer and thus are alternatively referred to as partially-depleted SOI (PD-SOI). Since there is neutral silicon under the channels regions of MOSFETs, body contacts are required and when used, the floating-body effect is not present.

Due to the lack of surface isolation, the coupling mechanisms are much more complicated to analyze and more resemble those of bulk-CMOS technologies. However, if the process supports deep-trenches [26], surface coupling can be reduced and the coupling properties can become closer to that of the more ideal thin-film case. As shown in Figure 2.4, a deep-trench of SiO<sub>2</sub> can extend from the surface of the top silicon active-layer down to the BOX. Surrounding an entire transistor with a deep-trench will result in complete surface dielectric isolation. However like guard-rings in bulk-CMOS, deep-trenches are ineffective against signals coupled into the substrate. Furthermore, surrounding active-devices with deep-trenches consumes large areas on-chip and may not be practical for high density designs.

Other coupling mitigation techniques in thick-film SOI have also been explored such as burying a conductive ground plane under the BOX, called ground-plane SOI (GPSOI) [32]. Although GPSOI can provide high isolation, the added step in manufacturing increases the cost of the wafer. It is also well known that placing a ground plane under spiral planar inductors will

Figure 2.4 – Typical thick-film SOI cross-section.

severely degrade their performance, which is counter-productive to RF applications where high quality-factor (high-Q) inductors are greatly desired.

Since SOI technologies are still evolving, fewer studies about coupling reduction have been performed. Early investigations in [31] and [33] showed that SOI can have advantages over bulk-CMOS from a coupling perspective, at least at lower frequencies. It has also been shown, however, that a bulk-CMOS process with well-developed coupling mitigation strategies can sometimes outperform SOI [34]. Studies in SOI such as [35] and [36] approached the issue of coupling by modifying process specific parameters such as the thickness and depth of the BOX and the resistivity of the handle substrate. In contrast, for the current thesis, only parameters that are available to the designer will be modified such as increasing the spacing of circuits or adding deep-trench. Following the techniques used in [37], the issue of coupling reduction in this research will be focused on a typical high-resistivity SOI process that is commercially available to the public.

Designs utilizing on-chip inductors, can experience not only coupling through the wafer but also magnetic coupling through the metal layers. Magnetic coupling could occur between inductors and/or circuits with ground loops. Though not necessarily specific to thick-film SOI, magnetic coupling is also addressed in this thesis. Following the example in [16], a magnetic isolation technique is examined over a wide range of frequencies.

### 2.3 Process Features in Thick-Film SOI

The primary focus of this research are thick-film SOI processes with a high-resistivity substrate on the order of  $1 k\Omega \cdot \text{cm}$ . To characterize the coupling, various test structures were designed and measured in a commercial SOI process with high-resistivity substrate targeted at RF and mixed-signal designs. To protect the intellectual property rights of the fabrication vendor, actual process specific parameters cannot be published. However, the values in Table 2.1 can be considered a good representation of a typical high-resistivity thick-film SOI process such as that used in this research. A detailed cross-section showing different coupling paths in the thick-film SOI is shown in Figure 2.5. This figure also illustrates some of the different features that can be used to address the issue of cross-talk reduction in thick-film SOI. Layout issues using this SOI process that were investigated are:

- signal coupling through the high-resistivity substrate,

- increasing the separation between circuits,

- adding deep-trenches,

- blocking the implant of channel-stopper,

- blocking the dummy metal fill,

- PTAP guard rings surrounds,

- grounded Metal-1 guard-ring surrounds and

- placing a Metal-1 shield over magnetically noisy circuits.

Table 2.1 – Representative parameter values for a thick-film SOI process.

| Parameter                                            | Value | Units                |

|------------------------------------------------------|-------|----------------------|

| Active-layer thickness                               | 1     | μm                   |

| Active-layer resistance with channel-stopper implant | 1     | $k\Omega/sq$         |

| Active-layer resistance w/o channel-stopper implant  | 100   | $k\Omega/sq$         |

| N+ or P+ diffusion depth                             | < 0.1 | μm                   |

| N+ or P+ diffusion resistance                        | 10    | $\Omega/sq$          |

| BOX thickness                                        | 1     | μm                   |

| Deep trench wall thickness                           | 1     | μm                   |

| High Resistivity substrate resistivity               | > 1   | $k\Omega\!\cdot\!cm$ |

| Substrate thickness                                  | > 200 | μm                   |

Figure 2.5 – Typical features found in thick-film SOI processes.

<sup>&</sup>lt;sup>1</sup> Inter-Metal Dielectric

<sup>&</sup>lt;sup>2</sup> Pre-Metal Dielectric

Figure 2.6 – Diagram of a PTAP and NTAP in thick-film SOI.

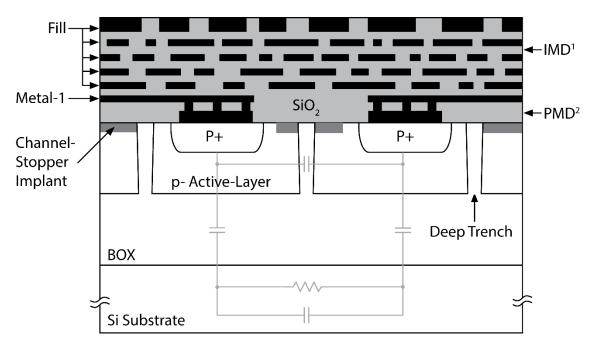

#### 2.3.1 Substrate/Well Contacts

Substrate contacts are highly doped diffusions of P+ into the p- active-layer (PTAP) or N+ into an N-doped well (NTAP). Figure 2.6 shows an example of a PTAP and an NTAP in thick-film SOI. Unlike the rectifying contacts of the source and drain diffusions in MOSFETs, these contacts are ohmic and do not form a depletion region. In processes such as bulk-CMOS and thick-film SOI they are used to make the body connection to bias the active-layer. Rings of substrate contacts, called guard-rings, can be placed around NMOS and PMOS devices to help reduce the effects of latchup in a bulk-CMOS environment by collecting minority carriers in the active-layer before they can reach the underlying substrate and propagate [38]. In a similar fashion, substrate contact guard-rings can also be placed around sensitive circuitry to shunt currents in the active-layer to ground and minimize coupling between circuits. This is possible in both bulk-CMOS and in SOI. Due to the resistance and thickness of the active-layer, such substrate contacts must be kept within a few microns of devices to be effective.

## 2.3.2 Channel-Stopper Implant

The channel-stopper implant is a shallow, high density P+ implant into the surface of the p-active-layer, placed outside the active regions of devices such as MOSFETs and diodes. The channel-stopper implant is also referred to as the *field-implant*, recognizing the area outside the active regions on-chip is called the "field." Its primary purpose is to prevent surface inversion due to high voltage signal runs on metal layers above the active-layer. Voltages as high as 15V can still be found in modern "low-voltage" processes in circuits such as high performance power amplifiers. High voltages can cause the surface to invert from P to N creating a channel of low

Figure 2.7 – (a) Photograph and (b) diagram of a deep-trench grid structure.

resistance N type material under the high-voltage run, similar to the gate of a MOSFET. Signals finding their way into this channel can couple into circuitry a great distance from the source. Unfortunately, the P+ channel-stopper implant itself decreases the resistance of the active-layer, forming a potentially strong surface coupling path for any signals that make their way into the field areas – possibly through capacitive mechanisms.

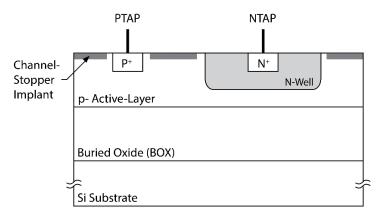

## 2.3.3 Deep-Trench Isolation

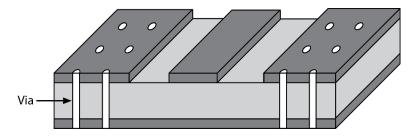

As discussed previously, completely surrounding an active device with deep-trench dielectrically isolates it from the rest of the active-layer. This results in no DC coupling path in the active-layer and coupling properties can approach the case of thin-film SOI. Grid patterns of deep-trench can also be used to effectively remove large areas of the active-layer. This is especially useful for improving the Q of planar spiral inductors [39]. The bond pad in Figure 2.7a employs a deep-trench grid underneath to reduce signals in the active-layer/substrate coupling into the pad. As shown in the diagram in Figure 2.7b, islands of silicon from the active-layer will still remain. As demonstrated in [39], if the grid geometries are similar in dimension to the DT wall thickness, then these silicon islands will not have a large effect and the gridded area can be considered largely insulating.

## 2.3.4 Metal-Fill Layers

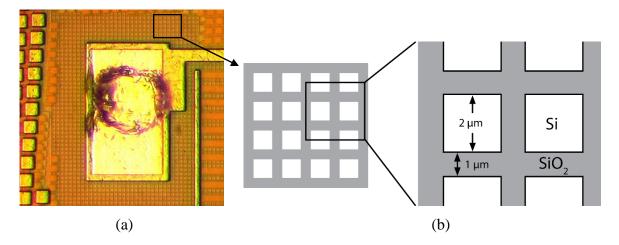

In processes with multiple layers of routing metals, dummy metal may be added in the field of the chip to increase the metal density in those areas. Metal-fill is added to minimize large variations in the wafer surface topology [40], [41], which could result in undesired partial

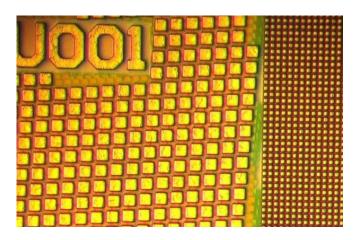

Figure 2.8 – Photograph showing two different metal-fill patterns.

removal of portions of metal layers during chemical-mechanical polishing (CMP), leading to open circuits. The metal-fill pattern varies by process, but in general consists of an array of metal shapes, such as shown in Figure 2.8. On the left, automatically generated Metal-6 fill shapes can be seen (metal-fill is present on the lower metal layers, but is obfuscated by the Metal-6 fill). On the right, a custom high-density metal-fill was used to further increase the metal density in that area. Fill patterning may also be done on the poly-silicon layers used for the gates of MOSFETs. The field of the chip may also be doped with "active fill" shapes to control the variance of breakdown voltages of active devices [42].

### 2.4 Motivation

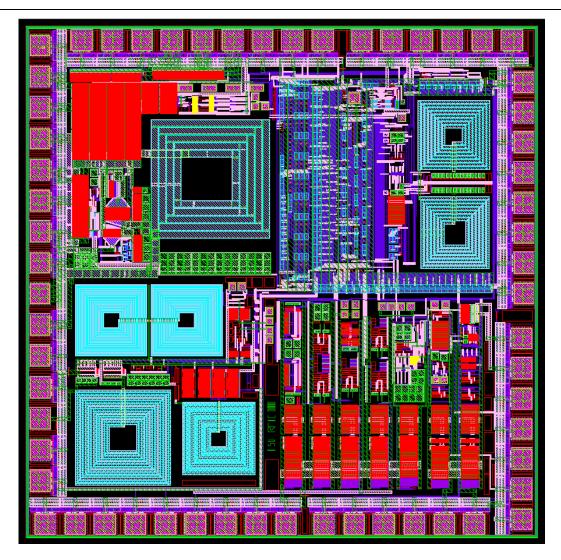

Unlike thin-film SOI processes, the presence of the conductive active-layer and substrate in thick-film SOI creates a potentially strong coupling situation. Signals in these conductive layers can couple into circuits in other parts of the chip, degrading system performance. Take for example the KSU Micro-Transceiver Radio which was designed and fabricated using a thin-film SOS process. The top-level layout is shown in Figure 2.9. The chip contains a transmitter consisting of a 100 mW PA, digital synthesizer and analog VCO in the upper half of the chip. The lower half contains a receiver which consists of an LNA and intermediate-frequency (IF) section operating to signal levels as low as -120 dBm. Although the radio only operates in half-duplex mode (i.e. the PA is off while receiving), strong digital signals from the synthesizer could

Figure 2.9 – KSU Mars Micro-Transceiver Radio top-level layout.

couple into the sensitive analog LNA and IF sections. Successful operation was achieved in thinfilm SOS due to careful layout, the use of differential circuitry and frequency planning. Additionally, a grounded metal-shield was placed over the digital synthesizer to reduce coupling to other parts of the radio.

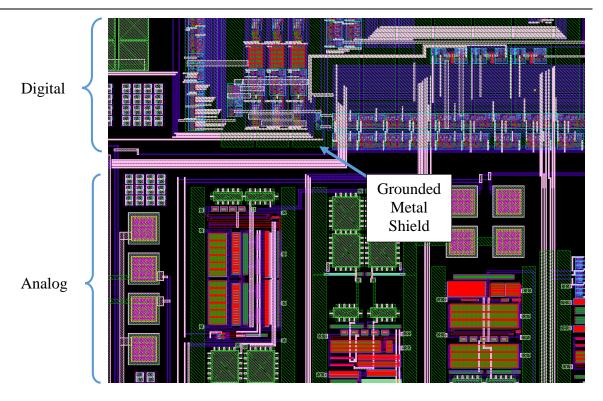

However, if the thin-film SOS radio design were ported to a thick-film SOI process without addressing thick-film specific coupling issues, the performance of the radio could be substantially degraded. One of the many locations where coupling issues could arise is through the physical proximity between the analog IF section and digital circuitry in the synthesizer. An enlarged view of this region is shown in Figure 2.10, showing the digital synthesizer circuitry in the top and the analog IF circuitry in the bottom. The active-layer and high-resistivity substrate could allow strong digital signals from the synthesizer to couple into the sensitive analog IF section.

In the chapter to follow, electric field coupling mechanisms in thick-film SOI will be analyzed. In later chapters, magnetic coupling and bond pad coupling will also be investigated. Methods to reduce coupling will be presented employing techniques applicable to most commercial thick-film SOI processes.

Figure 2.10 - Enlarged layout view of analog and digital sections of the KSU Micro-Transceiver Radio.

## 3. Electric Field Coupling

Following from the previous discussion, designers of mixed-signal integrated circuits must understanding coupling mechanisms and reduction techniques to be able to build highly-integrated, high performance chips. In this chapter, electric field coupling mechanisms and mitigation techniques will be analyzed. In later chapters, magnetic field coupling along with electric field coupling between bond pads will be investigated. In total, three test chips were fabricated. The first contains test structures to characterize electric field coupling. The second and third chips contain structures to characterize magnetic coupling between noisy digital circuits and RF inductors, and electric field coupling between bond pads. Appendix B contains an overview of the structures on each chip. The details of each structure will be discussed in their respective chapters to follow.

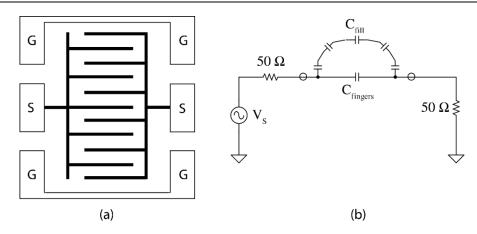

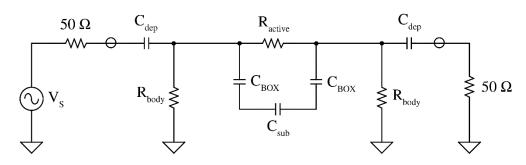

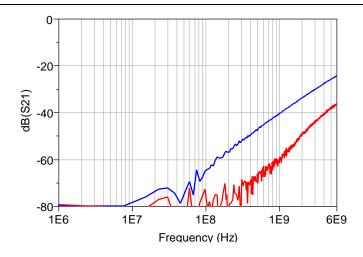

To analyze and measure electric field coupling in high-resistivity thick-film SOI wafers, an array of transmitter/receiver structures were fabricated similar to the one shown Figure 3.1. The structures consist of 100 µm long, bar shaped P+ diffusion in the p- active-layer. Note that the 100 µm long bars are *not* MOSFETs; they are ohmic contacts allowing signals to be injected directly into the active-layer of the SOI to assess the active-layer's transport of signals and the effect of using features like deep-trench to block those signals. Later in this chapter, coupling effects between MOSFETs will be discussed.

Contacting the diffusion bars are a set of coplanar, ground-signal-ground (GSG) probing

Figure 3.1 – Transmitter/receiver coupling structures.

structures suitable for making high-frequency RF measurements.  $S_{21}$  measurements were made using an Agilent 8753E vector network analyzer (VNA) from 1 MHz to 6 GHz. The elongated bar structures were chosen over the square structures in [37] to ensure there was sufficient coupling between the two bars, thus increasing the signal-to-noise (SNR) of the test.

In the sections to follow, circuit models will be constructed to illustrate how each of the features discussed previously affect the overall coupling between the bar structures. Rather than the highly descriptive models developed in [43], the models developed in this thesis aim to be more analytical, with the goal of assisting circuit designers in quantitatively predicting the attenuations achievable with various coupling mitigation strategies.

## 3.1 Electric Field Coupling Analysis in Thick-Film SOI

To simplify the analysis, coupling through the high-resistivity substrate and surface coupling through the active-layer will be discussed separately. The two analyses will then be combined to create an overall model of the electric field induced coupling mechanisms in the thick-film SOI wafer.

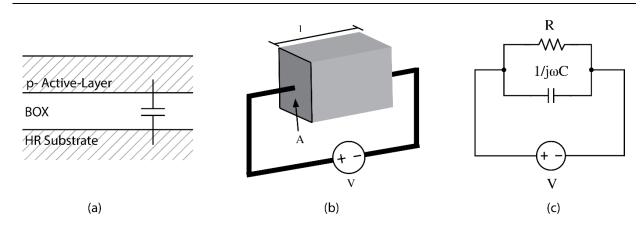

## 3.1.1 Coupling through the Substrate

The active-layer and substrate can act as the plates of a capacitor with the BOX acting as the dielectric (Figure 3.2a). If the resistance of the substrate is low  $(0.1 - 10 \,\Omega \cdot \text{cm})$ , significant displacement currents can flow into the substrate. Once these currents are in the substrate, they can propagate to other parts of the chip. Even when the resistivity is high, significant currents

Figure 3.2 – (a) Capacitance due to the BOX. (b) Small region of the substrate with potential V between the faces and (c) its circuit model.

can flow into the substrate as the following analysis demonstrates.

Capacitive coupling through the BOX can be used to advantage in SOI processes with low-resistivity substrates to shunt displacement currents to ground [44]. However, if high-resistivity silicon (e.g. > 1  $k\Omega \cdot cm$ ) is used for the substrate, the resistance may be sufficiently large that it can be ignored. Thus, the coupling path through the substrate can be modeled as purely capacitive at high-frequencies. Like silicon-on-sapphire (SOS) processes which have purely insulative substrates, the unavoidable capacitive coupling path through the high-resistivity substrate still exists<sup>1</sup>.

To determine at what frequency the coupling through the high-resistivity substrate can be modeled as purely capacitive, consider a section of the substrate material as shown in Figure 3.2b. Assuming the left and right faces are equipotential surfaces, such a section can be thought of as a capacitor in parallel with a resistor (Figure 3.2c). If a voltage V is applied between the two faces, the current flowing through the substrate material is then,

$$V = IZ \to I = V/Z \tag{3.1}$$

Modeling the substrate as an RC network, its impedance is,

$$Z = R \mid\mid \frac{1}{j\omega C}.$$

(3.2)

Where, || denotes the parallel combing operator. The capacitance of the section of substrate material is given by,

$$C = \varepsilon \frac{A}{l} . {(3.3)}$$

and the resistance can be found as,

$$R = \rho \frac{l}{4} \ . \tag{3.4}$$

where the  $\rho$  is the volume resistivity. Combining (3.2) through (3.4) gives,

$$Z = \rho \frac{l}{A} \mid \mid \frac{1}{j\omega\varepsilon\frac{A}{l}}.$$

(3.5)

To avoid the parallel combining operator, (3.5) can be expressed in terms of admittance:

<sup>&</sup>lt;sup>1</sup> As discussed in [31], this mechanism will limit the degree to which high-resistivity substrates can improve coupling mitigation in thick-film SOI and is the reason a well-designed coupling strategy in bulk-CMOS using guard-rings and highly-doped buried layers can sometimes outperform thick-film SOI [34].

$$Y = \frac{1}{Z} = \sigma \frac{A}{l} + j\omega \varepsilon \frac{A}{l}, \qquad (3.6)$$

where  $\sigma$  is the conductivity of the semiconductor. For the general case of complex permittivity,  $\varepsilon$  is given by,

$$\epsilon = \epsilon_0 \epsilon_r (1 - j \tan(\delta_d)), \qquad (3.7)$$

where  $tan(\delta_d)$  is the loss tangent. Combining (3.6) and (3.7), the admittance is then,

$$Y = \frac{A}{I} \left[ \sigma + \omega \epsilon_o \epsilon_r tan(\delta_d) + j \omega \epsilon_o \epsilon_r \right] . \tag{3.8}$$

The loss tangent describes the inherent losses of a dielectric due to atomic heating. For example, in a capacitor a sinusoidal electric field moves charge back and forth between the plates through the dielectric material (displacement current). When the electric field changes polarity, the ions carrying the charge in the dielectric must also change their dipole moment. Thus the dipole moments of the ions are oscillating with the electric field. If the dipole moments were perfectly in-phase with the electric field, there would be no energy loss. However, this is never the case and the ions dissipate energy through finite phase-shifts in relation to the driving electric field. This effect is called dielectric damping [45]. As the frequency increases, the phase-shift increases as the rotating dipole moments attempt to keep up with the oscillating electric field. The tangent of the angle between the phases of the electric field and the dipole moment is called the loss tangent. Similarly, the sine of the angle between the electric field and the dipole moment is called the power-factor.

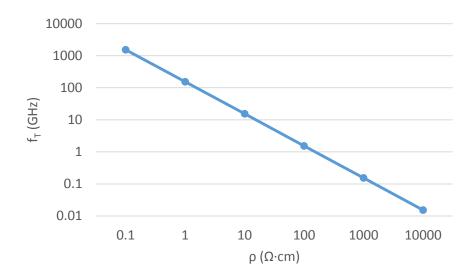

For the case of a high-resistivity silicon substrate the loss tangent is approximately 0.005 [46]. Since the loss tangent is quite small,  $\sigma$  dominates over the second term in (3.8). From this, we can identify a transition frequency ( $f_T$ ) where the capacitive coupling will dominate over the resistive coupling. At this transition frequency the first and third terms in the brackets of (3.8) are equal yielding,

$$f_T = \frac{1}{2\pi\epsilon_0 \epsilon_r \rho} \ . \tag{3.9}$$

Figure 3.3 shows the computed transition frequencies for substrates doped from  $0.1 \Omega \cdot \text{cm}$  to  $10 \ k\Omega \cdot \text{cm}$ . For high-resistivity substrates where  $\rho$  is typically  $1 - 10 \ k\Omega \cdot \text{cm}$ , the transition frequency is between 16 MHz and 160 MHz. Above these frequencies the substrate can be approximated as acting purely capacitive and the resistive coupling path can be largely ignored. With this approximation, the substrate coupling is essentially equivalent to that of an SOS or

Figure 3.3 – Computed frequncies above which substrates behave more as a dielectric than a conductor.

GaAs process [36]. Note that because the second term in (3.8) increases with frequency, at sufficiently high frequencies, it can no longer be ignored. However, this should not occur until around 30 GHz for a 1  $k\Omega$  · cm substrate with  $tan(\delta_d) = 0.005$ . Hence, we can treat the high-resistivity substrate as purely capacitive over a broad range of frequencies from approximately 100 MHz to 10 GHz.

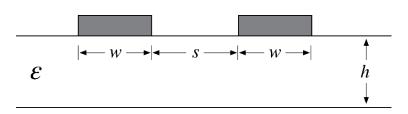

### 3.1.1.1 Coplanar Strips

With the above conclusion that at sufficiently high frequencies the high-resistivity substrate acts as an insulator, the high-frequency coupling behavior expected for the 100 µm long bars from Figure 3.1 (and hence, for layouts of comparable structures on-chip) can be estimated using capacitor formulas. If signals are coupled through the substrate only, the two bars can be modeled as two coplanar strips (CPS) with a supporting dielectric below, as shown in Figure 3.4. The capacitance per unit length between the CPS is given by (3.10) [47].

*Figure 3.4 – Cross-section of coplanar strips.*

$$c = \varepsilon_0 \varepsilon_{eff} \frac{K(k_0')}{K(k_0)} \tag{3.10}$$

where,

$$k_0 = \frac{\frac{s}{2}}{w + \frac{s}{2}}, \qquad k = \frac{\sinh\left(\frac{\pi s}{4h}\right)}{\sinh\left(\frac{\pi (w + g)}{2h}\right)}, \quad k'_0 = \sqrt{1 - k_0^2}, \quad k' = \sqrt{1 - k^2}$$

$$\varepsilon_{eff} = 1 + (\varepsilon - 1)q$$

,  $q = \frac{1}{2} \frac{K(k')}{K(k)} \frac{K(k_0)}{K(k'_0)}$

The function K() is the Complete Elliptic Integral of the First Kind given by,

$$K(k) = \int_0^{\frac{\pi}{2}} \frac{d\theta}{\sqrt{1 - k^2 \sin^2 \theta}} \ . \tag{3.11}$$

If the substrate thickness h is much larger than the spacing or width geometries of the CPS, then as  $h \to \infty$ ,  $k \to k_0$ . Using this simplification in (3.10) yields,

$$c = \varepsilon_0 \left( 1 + \frac{\varepsilon - 1}{2} \right) \frac{K(k_0')}{K(k_0)}. \tag{3.12}$$

To eliminate the need to compute Elliptic Integrals, the following approximation can be made [12]:

$$\frac{K(k_0')}{K(k_0)} \approx \begin{cases}

\left[\frac{1}{\pi} ln\left(2\frac{1+\sqrt{k_0'}}{1-\sqrt{k_0'}}\right)\right] & \text{for } 0 \le k \le \frac{1}{\sqrt{2}} \\

\left[\frac{1}{\pi} ln\left(2\frac{1+\sqrt{k_0}}{1-\sqrt{k_0}}\right)\right]^{-1} & \text{for } \frac{1}{\sqrt{2}} \le k \le 1

\end{cases}$$

(3.13)

Equation (3.12) is defined for the case of a single layer of thick dielectric, which can be assumed for signals injected into the high-resistivity thick-film SOI substrate (this situation will be shown later if specific coupling mitigation strategies are used). For the cases of SOI where the substrate resistance cannot be ignored, a more generalized formula for the capacitance of CPS taking into account multiple layers of dielectrics is given in [48].

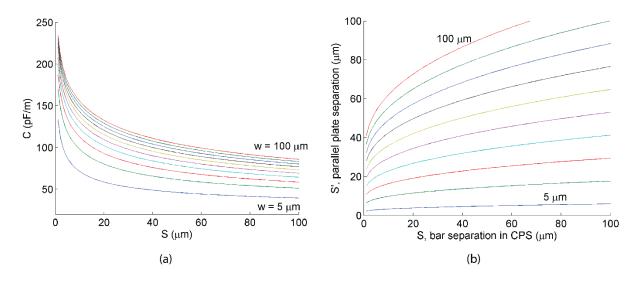

Figure 3.5 – (a) Capacitance per unit length for CPS versus spacing and (b) equivalent spacing of a parallel plate capacitor for the same capacitance as CPS.

A family of capacitance per unit length plots for various spacing and width of CPS is shown in Figure 3.5a. As expected, the capacitance falls off as the spacing between the bars increases. This plot also shows a diminishing return on capacitance for increasing widths of the bars around  $100 \mu m$ .

To help the reader understand the relationship between spacing and capacitance in CPS, these parameters are compared to the familiar case of a parallel plate capacitor. The capacitance per unit length of an equivalent parallel plate capacitor is given by,

$$c = \varepsilon_0 \varepsilon_r \frac{w}{s'} \tag{3.14}$$

where s' denotes the required separation of the plates to achieve the same capacitance from CPS using (3.12) for a given space and width. The relationship between the separation of parallel plates and CPS is shown in Figure 3.5b for different widths of CPS. Note that two 100  $\mu$ m strips separated by 20  $\mu$ m have the same capacitance as two parallel plates which are 100  $\mu$ m wide, but separated by 70  $\mu$ m. This is reasonable since the field lines for the CPS case are arcing from the bottom of one strip to the bottom of the other and follow longer paths. Interestingly, for the other extreme, where two 5  $\mu$ m wide strips are separated by 100  $\mu$ m, the capacitance is the same as a parallel-plate configuration of two 5  $\mu$ m wide strips separated by only about 7  $\mu$ m. This is consistent with the path widening up due to the divergence of the fields terminating on the strips.

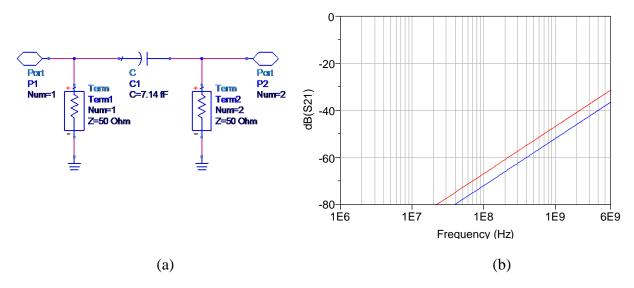

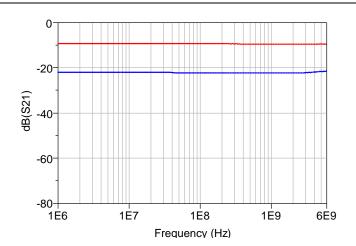

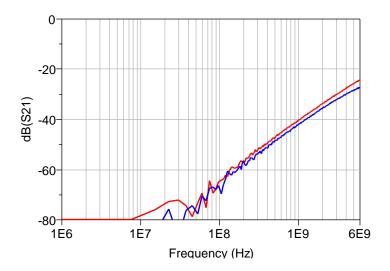

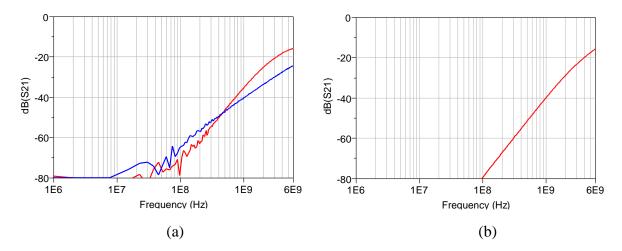

Figure 3.6 – (a) ADS simulation schematic for the coupling between CPS for 10  $\mu$ m spacing and (b) simulated  $S_{21}$  for 5  $\mu$ m wide, 100  $\mu$ m long bars with 10  $\mu$ m spacing (red) and 100  $\mu$ m spacing (blue).

The implications of this are significant in the area of coupling, as it shows that large separations do not provide as much isolation as one might first believe.

It should be noted that (3.12) was derived in [47] for the case of infinitely long strips and does not include fringing field capacitance from the ends of finite length strips. In the same manner, (3.14) also does not include fringing field capacitances in either the width or the length dimension of the plates. Thus these equations somewhat under-estimate the capacitance. It is beyond the scope of this research to provide an in-depth analysis of fringing field capacitances, however (3.12) is still useful for estimating the capacitance of the P+/N+ bars and the above implications for coupling still apply.

To get a feel for the signal isolation (dB of attenuation) that one may see in practice as a function of frequency, we examine the case of Figure 3.1. If the primarily coupling path between the 100  $\mu$ m long bars in Figure 3.1 is through the high-resistivity substrate only, the thick-film SOI wafer can be approximated as a single layer of dielectric with  $\varepsilon_r = 11.6$ , and the capacitance between the bars can be approximated using (3.12). Using this capacitance in the 2-port circuit in Figure 3.6a, the coupling (S<sub>21</sub>) can be plotted over a range of frequencies as shown in Figure 3.6b. As expected, there is no coupling at DC and the coupling increases linearly at 20 dB/decade, and reaches significant values of -50 dB and above past 1 GHz. While concerning, the actual situation may be worse than this figure implies. Coupling within the thick-film top layer is also significant and must still be addressed.

## 3.1.2 2D Surface Coupling through the Silicon Active-Layer