# Q-ENHANCED TUNABLE FILTER DESIGN WITH APPLICATIONS IN RECEIVER ARCHITECTURES

by

#### CHELSI KOVALA

B.S., Kansas State University, 2009 B.S., Kansas State University, 2009

#### **A THESIS**

submitted in partial fulfillment of the requirements for the degree

#### MASTER OF SCIENCE

Department of Electrical Engineering College of Engineering

KANSAS STATE UNIVERSITY Manhattan, Kansas

2012

Approved by: Major Professor William Kuhn

# Copyright CHELSI ANN KOVALA

2012

### **Abstract**

Q-enhanced Filters have been researched extensively, but have not been often implemented into receiver architectures due to inherent challenges in the design and stability of these filters. However, recent works have successfully addressed Q-enhanced filter designs which are viable for receiver implementation with tuning algorithms to achieve temperature stability. This work continues these efforts with the redesign of a Two-Pole Q-Enhanced Band-Pass filter tested at narrower fractional bandwidths than previous work of less than one percent and considers potential significant improvements in receiver performance using this filer.

The Q-enhanced filter redesign ports the existing filter to a new integrated circuit technology which performs better at higher frequencies. The redesign in particular addresses problems in the previous design. The frequency divider design is modified, resistance tuning is added, and additional modifications to the overall filter functionality are implemented. General problems in obtaining an ideal passband shape by eliminating unwanted coupling are addressed. The supporting software for the tuning algorithm is modified to use analog controls and shown to achieve further narrowed bandwidths of 5 MHz and 2.5 MHz at center frequencies of 500 MHz, which are demonstrated to be temperature stable. Future software modifications are described to prepare the existing code base for the new filter design.

Potential applications for a Q-enhanced filter include improving the performance of receiver designs. One of the most important performance parameters of a receiver is its spurious response rejection. To explore this behavior, an automated test system is developed to characterize receivers, and four receivers are tested. The test results are presented in a novel graphical display, which is used to evaluate receiver performance and compare receivers. These results motivated the development of a potential modified superheterodyne receiver architecture using the Q-enhanced filter as an image filter and an IF filter. The viability of this receiver design is tested and shown to provide significant improvements to receiver's spurious rejection response.

# **Table of Contents**

| List of Figures                                               | viii |

|---------------------------------------------------------------|------|

| List of Tables                                                | xi   |

| Acknowledgements                                              | xii  |

| Dedication                                                    | xiii |

| Chapter 1 - Introduction                                      | 1    |

| 1.1 Objective                                                 | 1    |

| 1.2 Q-Enhanced Filter Development Primer                      | 1    |

| 1.2.1 Integrated Filter Design                                | 1    |

| 1.2.1.1 Previous Work                                         | 1    |

| 1.2.1.2 Q-Enhancement                                         | 1    |

| 1.2.1.3 Revised Integrated Circuit Block Diagram              | 2    |

| 1.2.2 Supporting Hardware and Software                        | 4    |

| 1.2.2.1 Previous Work                                         | 4    |

| 1.2.2.2 Software Additions                                    | 5    |

| 1.3 Receiver Architectures and Filter Applications            | 5    |

| 1.3.1 Motivation                                              | 5    |

| 1.3.2 Prior Art                                               | 6    |

| 1.3.3 Research Accomplished                                   | 7    |

| 1.3.3.1 Spurious Rejection Response Testing System            | 7    |

| 1.3.3.2 Spurious Rejection Response Results                   | 7    |

| 1.3.3.3 Filter Application                                    | 7    |

| Chapter 2 - Q-Enhanced Filter Redesign                        | 7    |

| 2.1 Design Overview                                           | 7    |

| 2.2 Porting Design to Different Integrated Circuit Technology | 8    |

| 2.3 Asymmetry in the Passband                                 | 10   |

| 2.3.1 Sources of Asymmetry                                    | 10   |

| 2.3.1.1 Admittance Review                                     | 11   |

| 2.3.1.2 The First Source of Asymmetry                         | 12   |

| 2.3.1.2.1 Origin of Asymmetry: Inductive Coupling                     | 12 |

|-----------------------------------------------------------------------|----|

| 2.3.1.2.2 Circuit Design Solution: Resistance Tuning                  | 15 |

| 2.3.1.3 The Second Source of Asymmetry                                | 20 |

| 2.3.1.3.1 Origin of Asymmetry: Incorrectly Driven Coupling Capacitors | 20 |

| 2.3.1.3.2 Circuit Design Solution: Corrected Loading                  | 21 |

| 2.4 Additional Circuit Redesigns                                      | 23 |

| 2.4.1 Frequency Divider                                               | 23 |

| 2.4.2 Amplitude Detector                                              | 28 |

| Chapter 3 - Supporting Hardware and Software                          | 31 |

| 3.1 Previous Work                                                     | 31 |

| 3.2 Top-level Code Implementation                                     | 31 |

| 3.3 Software Additions                                                | 32 |

| 3.3.1 Fine Tuning                                                     | 33 |

| 3.3.1.1 Implementation                                                | 33 |

| 3.3.1.2 Results                                                       | 38 |

| 3.3.2 Resistance Tuning                                               | 39 |

| 3.3.2.1 Implementation                                                | 39 |

| 3.3.2.2 Control Word and Passband Controls                            | 40 |

| Chapter 4 - Spurious Responses in Receivers                           | 41 |

| 4.1 Introduction to Receiver Architectures                            | 41 |

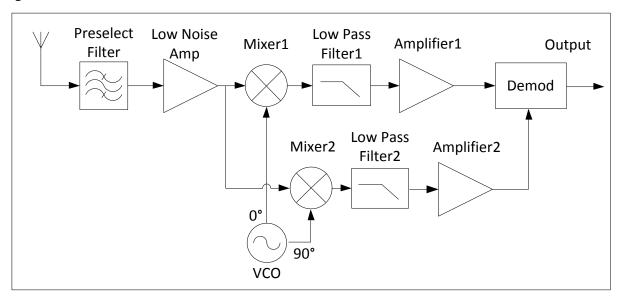

| 4.1.1 Direct Conversion                                               | 42 |

| 4.1.2 Superheterodyne                                                 | 43 |

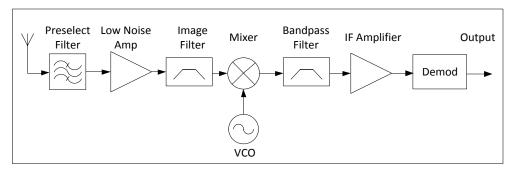

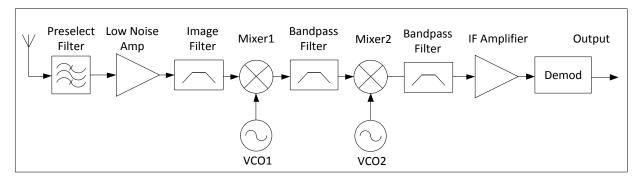

| 4.1.3 Multiple Conversion Superheterodyne                             | 44 |

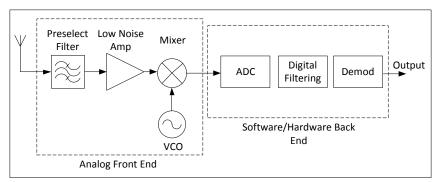

| 4.1.4 Software Defined Radio                                          | 44 |

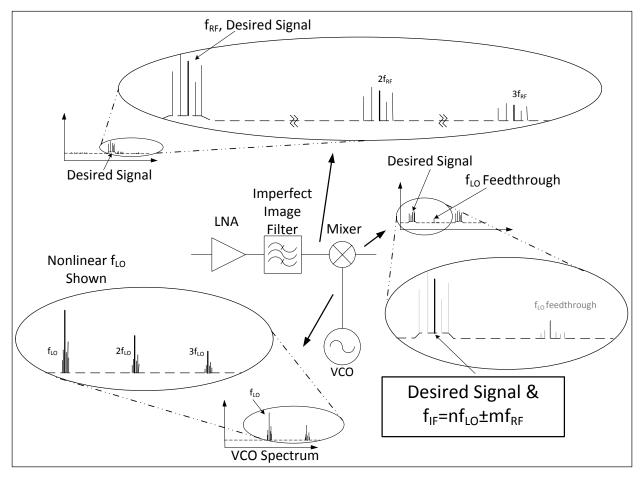

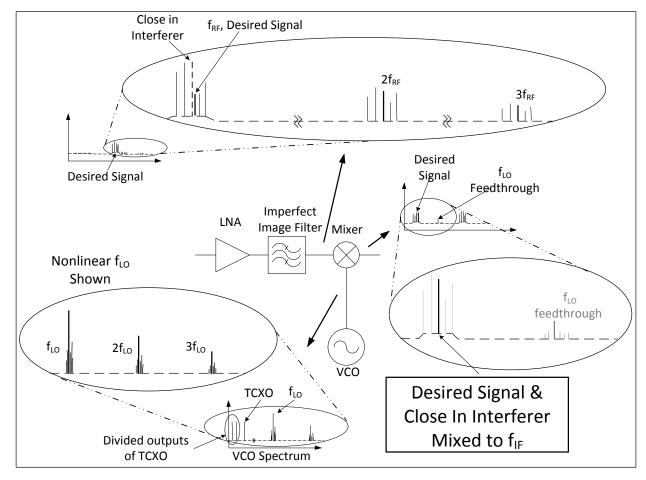

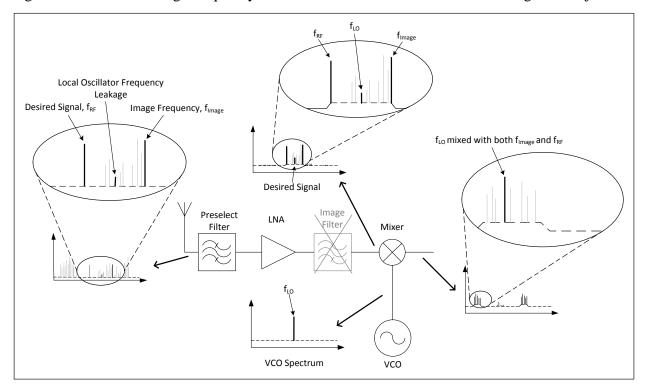

| 4.2 Spurious Responses in Receivers                                   | 45 |

| 4.2.1 Nonlinear Behaviors                                             | 47 |

| 4.2.1.1 Amplification                                                 | 47 |

| 4.2.1.2 Mixer Spurs                                                   | 47 |

| 4.2.1.3 Intermodulation Distortion                                    | 49 |

| 4.2.2 Spurs from Digital Synthesizers                                 | 49 |

| 4.2.3 Image Frequency                                                 | 50 |

| 4.2.4 1/2IF & 1/3IF Spur Frequencies                                  | 51 |

|-----------------------------------------------------------------------|----|

| 4.3 Spurious Response Test System                                     | 52 |

| 4.3.1 Manual Measurement Process                                      | 52 |

| 4.3.2 Automated Measurement Development                               | 53 |

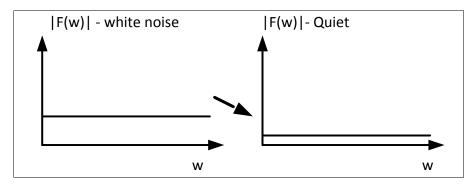

| 4.3.2.1 – Quieting Detection Method                                   | 53 |

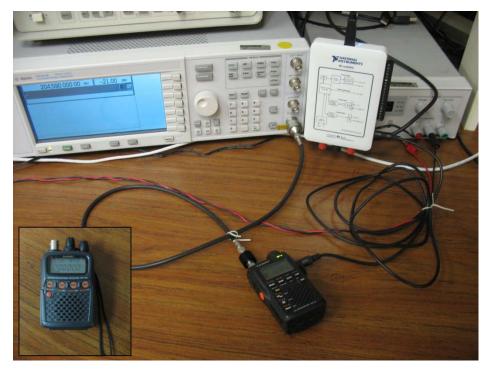

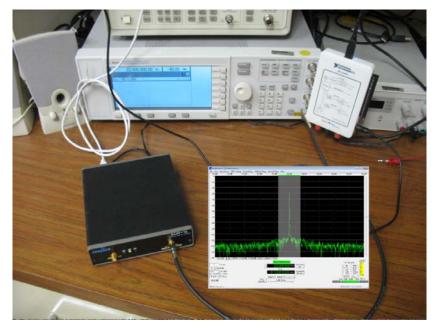

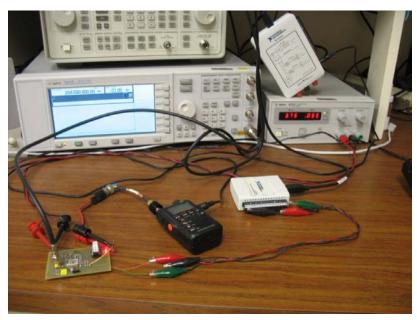

| 4.3.2.2 Physical Test Setup                                           | 54 |

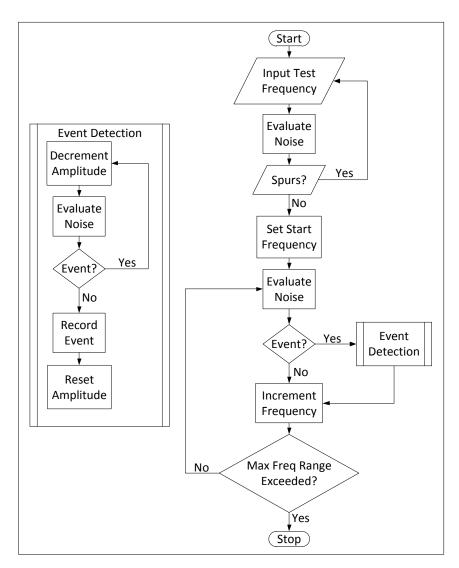

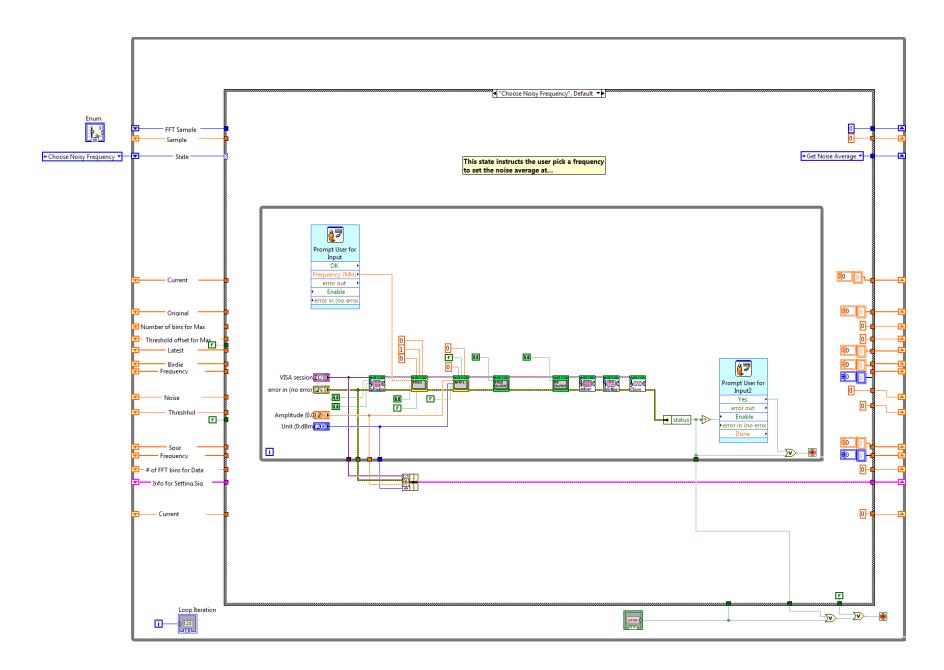

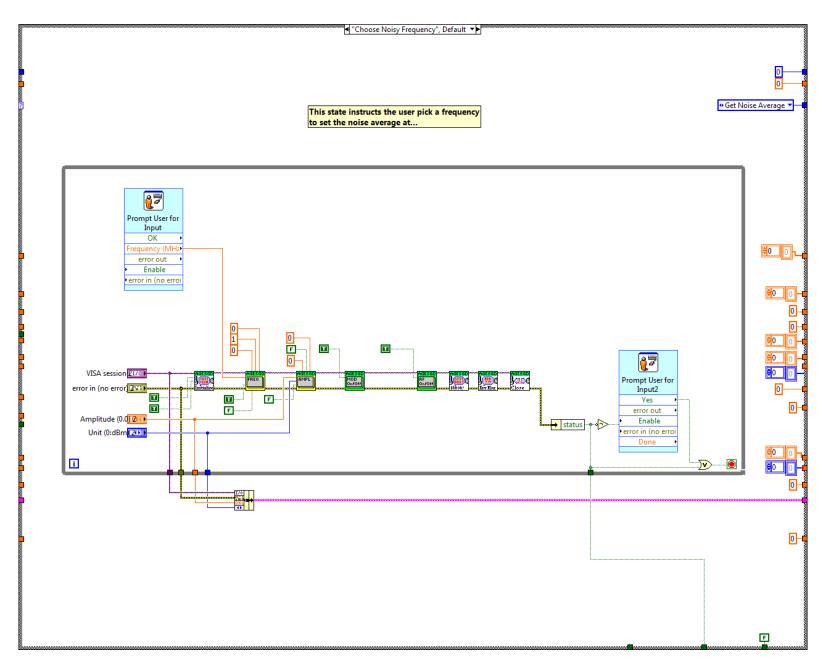

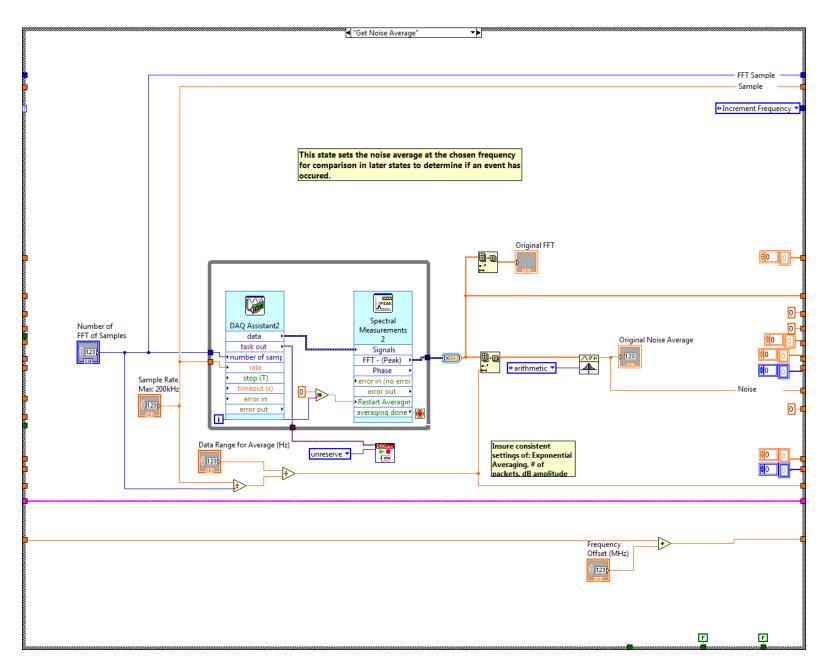

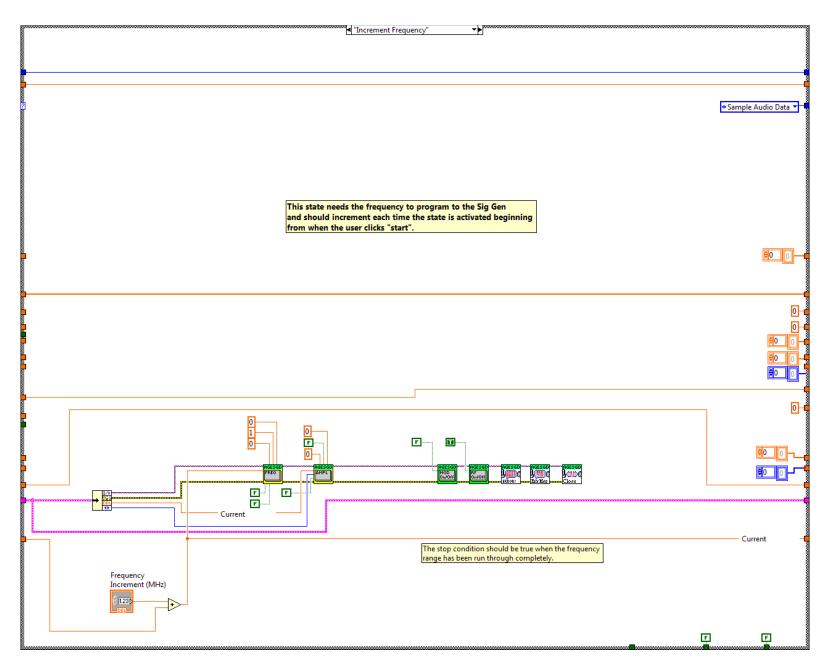

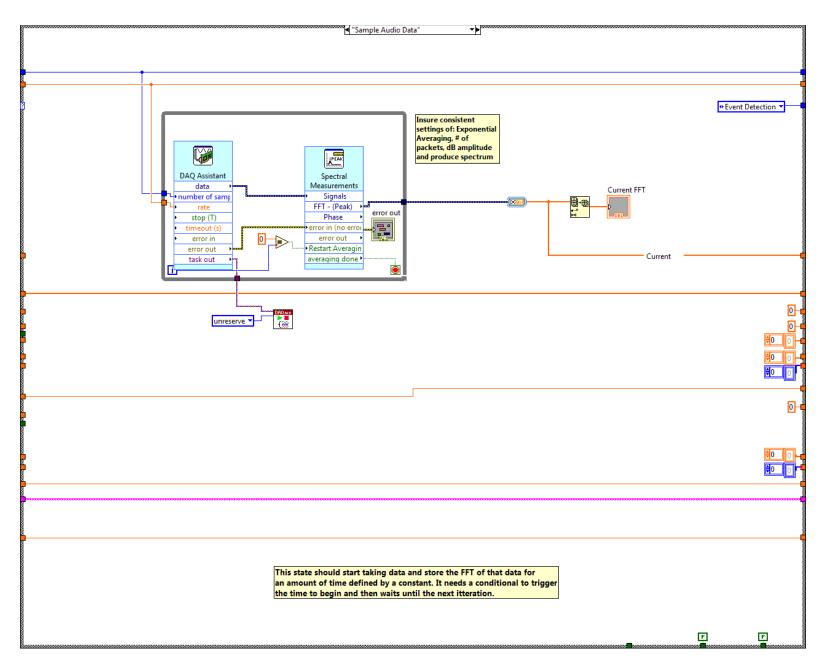

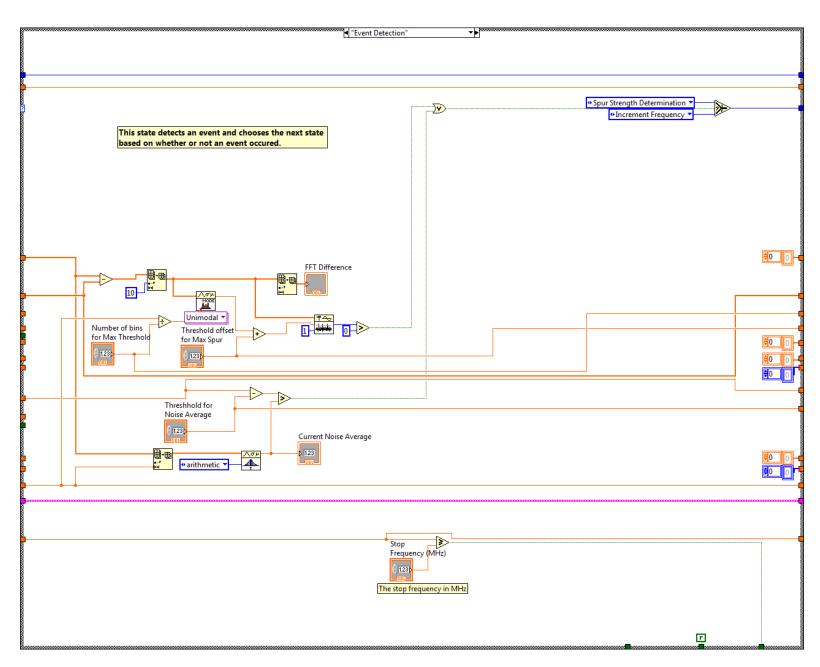

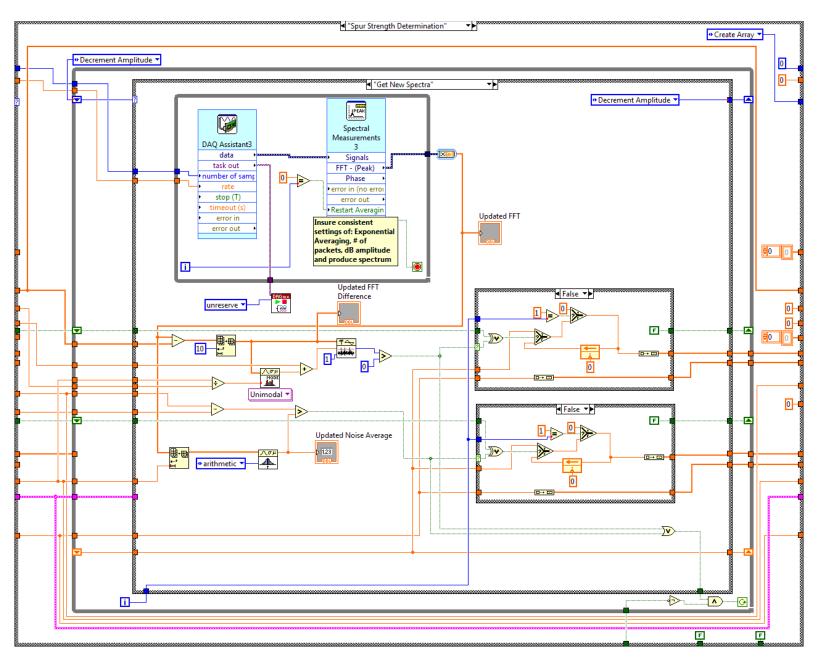

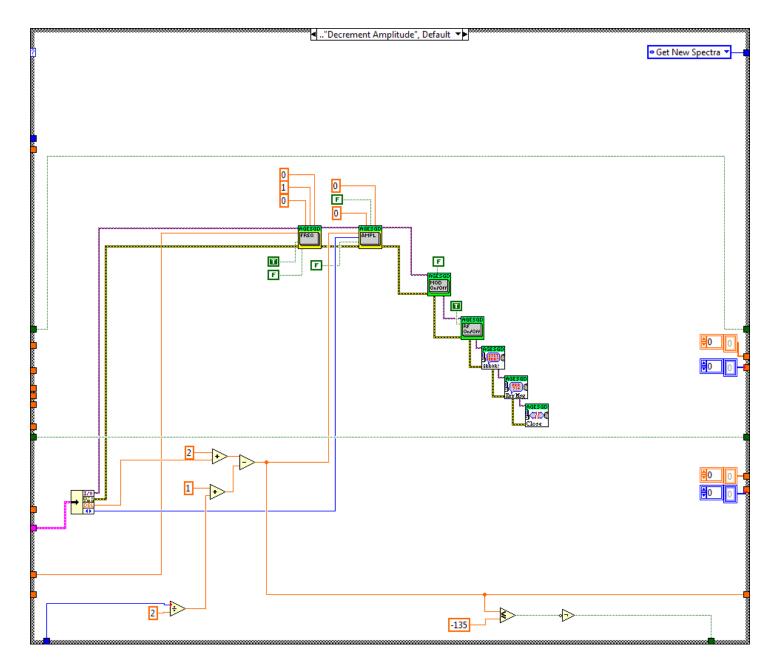

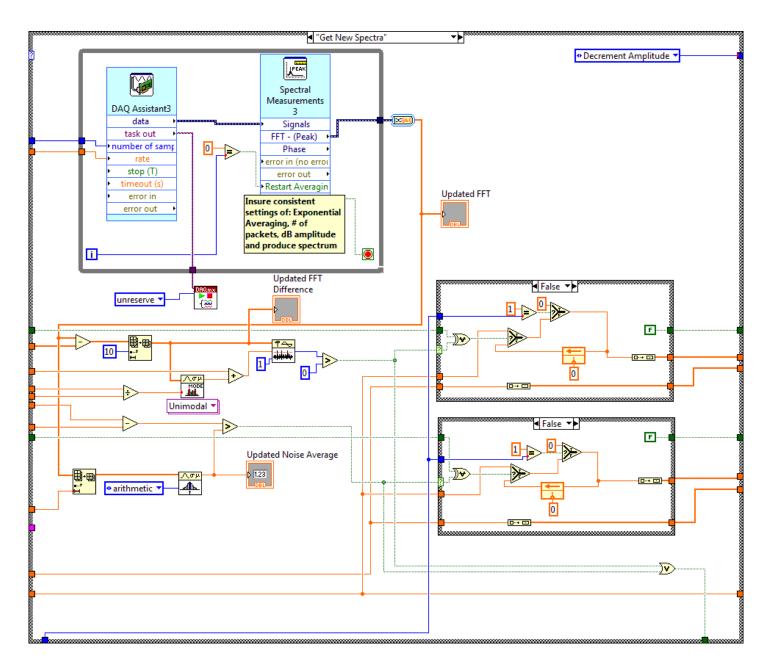

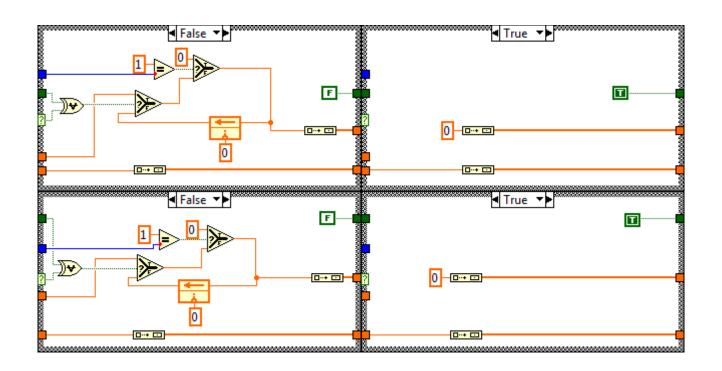

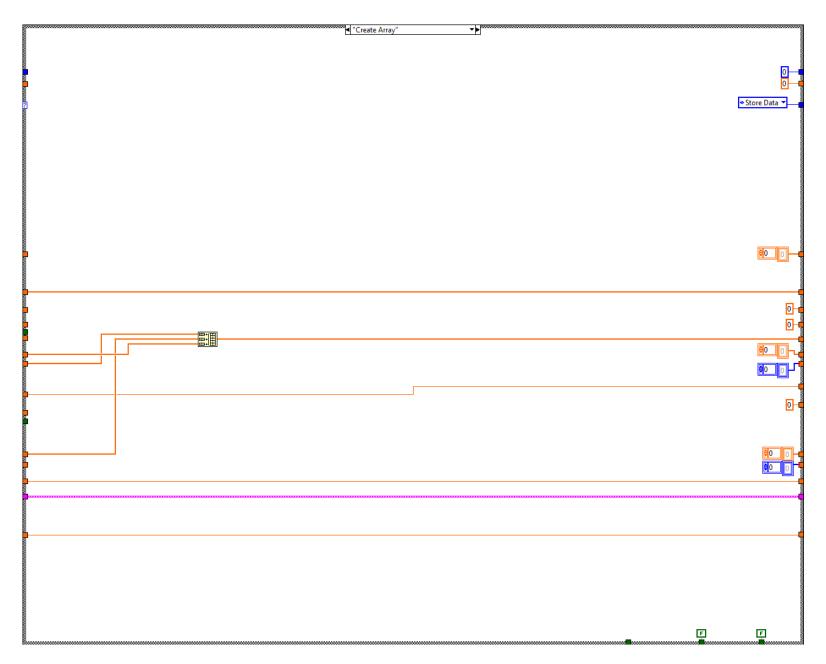

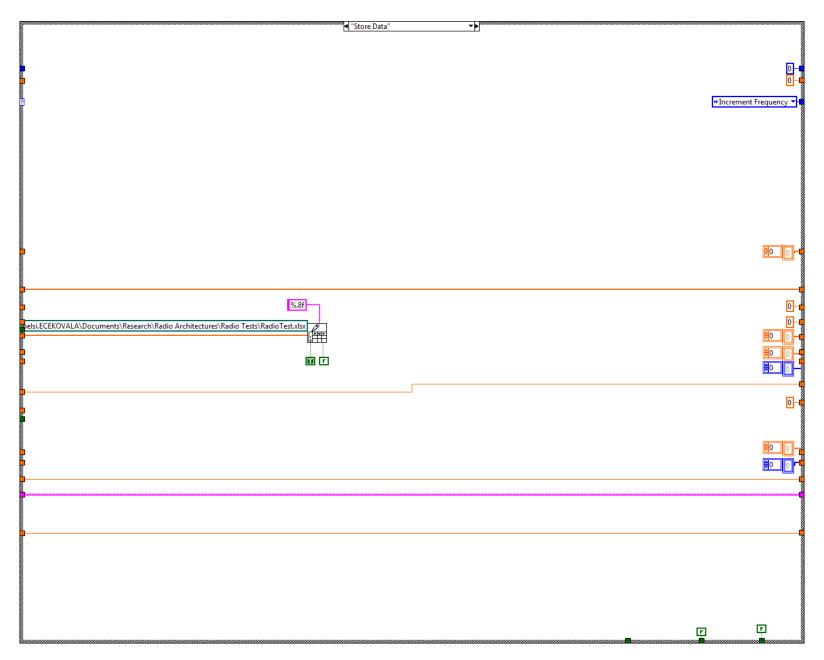

| 4.3.2.2 LabVIEW Code Algorithm                                        | 57 |

| 4.4 Receiver Block Diagrams                                           | 58 |

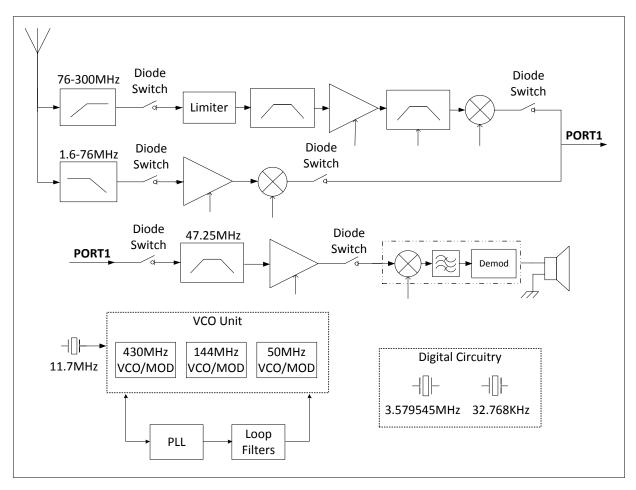

| 4.4.1 VR-120                                                          | 58 |

| 4.4.2 VX-3                                                            | 59 |

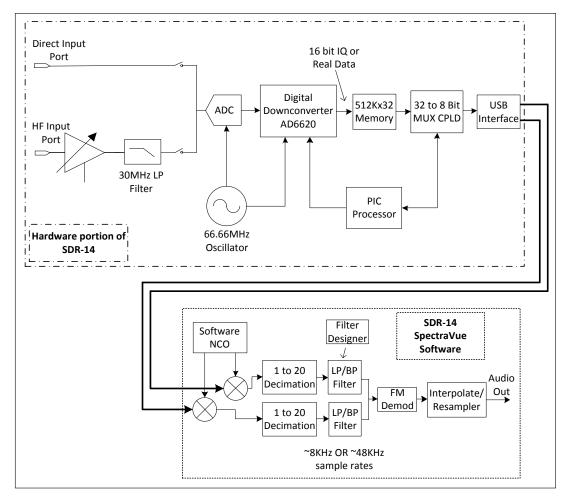

| 4.4.3 Software Defined Radio                                          | 61 |

| 4.4.4 K-State Microtransceiver                                        | 62 |

| 4.5 Receiver Test Results                                             | 62 |

| 4.5.1 Checking for Mixer Spurs                                        | 63 |

| 4.5.2 Three Receivers Tuned to an HF Frequency                        | 63 |

| 4.5.3 Three Receivers Tuned to Two Different Frequencies in HF Band   | 71 |

| 4.5.4 Two Receivers Compared at VHF Bands                             | 76 |

| 4.5.5 The K-State Microtransceiver Spurious Rejection Response at UHF | 79 |

| Chapter 5 - The Q-Enhanced Filter as a Solution to SDR Architectures  | 81 |

| 5.1 – Spur Reduction Achieved by Changing the IF                      | 81 |

| 5.2 – A New Architecture Using the Q-Enhanced Filter                  | 86 |

| Chapter 6 - Conclusion                                                | 87 |

| 6.1 System Status Summary                                             | 87 |

| 6.1.1 Integrated Circuit Redesign                                     | 87 |

| 6.1.2 Software Development                                            | 87 |

| 6.2 Receiver Spurious Response Conclusions                            | 88 |

| 6.3 Future Work                                                       | 88 |

| 6.3.1 Filter Layout                                                   | 88 |

| 6.3.2 Filter Testing                                                  | 88 |

| 6.3.3 Software                                                        | 88 |

| 6 3 3 1 Fine Tuning Code Future Work                                  | 89 |

| Chapter 7 - Bibliography                                | 90  |

|---------------------------------------------------------|-----|

| Appendix A - IC Redesign                                | 92  |

| Appendix B - C Code                                     | 106 |

| Appendix C - National Instruments LabVIEW Code          | 122 |

| Appendix D - Octave Code for Spurious Response Analysis | 135 |

# **List of Figures**

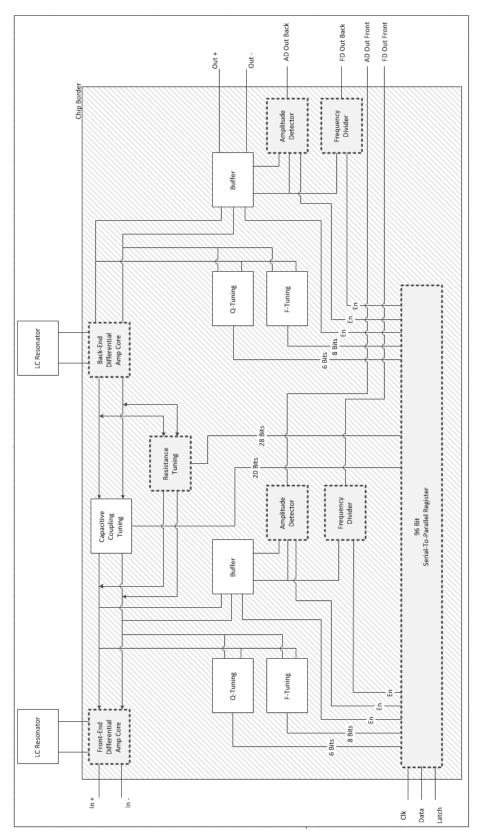

| Figure 1.1 – Q-Enhanced Filter Block Diagram                                                   | 3  |

|------------------------------------------------------------------------------------------------|----|

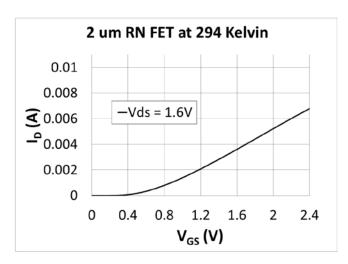

| Figure 2.1 – I <sub>D</sub> versus V <sub>GS</sub> Curve Showing Quadratic and Linear Behavior | 9  |

| Figure 2.2 – Filter Response Showing Asymmetric Passband (Used with Permission [2])            | 10 |

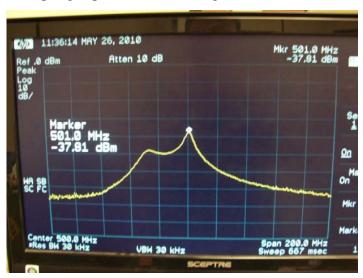

| Figure 2.3 – Two Port Network (Used with Permission [2])                                       | 11 |

| Figure 2.4 – Topological Transformation of LC Tank Circuit                                     | 12 |

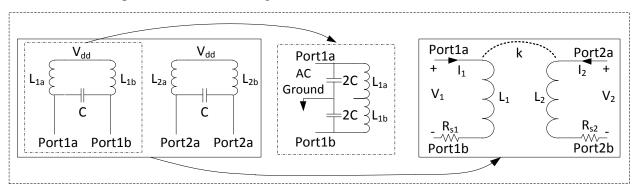

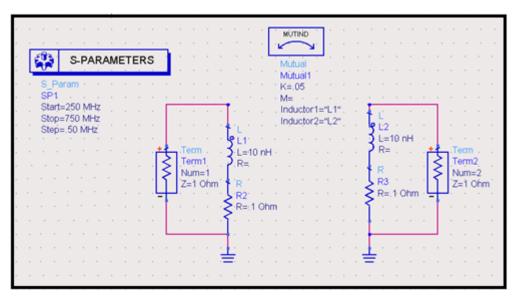

| Figure 2.5 – ADS Circuit Simulating Admittance Parameters                                      | 14 |

| Figure 2.6 – ADS Simulation Output of Admittance Parameters                                    | 14 |

| Figure 2.7 – Range of Resistance Values                                                        | 16 |

| Figure 2.8 – Resistance Tuning Circuitry Topology                                              | 17 |

| Figure 2.9 – Top View Resistance Tuning Circuitry                                              | 18 |

| Figure 2.10 – Narrowed View Resistance Tuning Circuitry                                        | 19 |

| Figure 2.11 – Resistance Tuning Circuitry Models                                               | 20 |

| Figure 2.12 – Resistance Tuning Circuitry Models                                               | 21 |

| Figure 2.13 – Top View Capacitive Coupling Circuit                                             | 22 |

| Figure 2.14 – Narrowed View Ctuneblock from Fig. 2.13                                          | 22 |

| Figure 2.15 – Cell View Capacitive Coupling Circuit                                            | 23 |

| Figure 2.16 – Top View Frequency Divider                                                       | 23 |

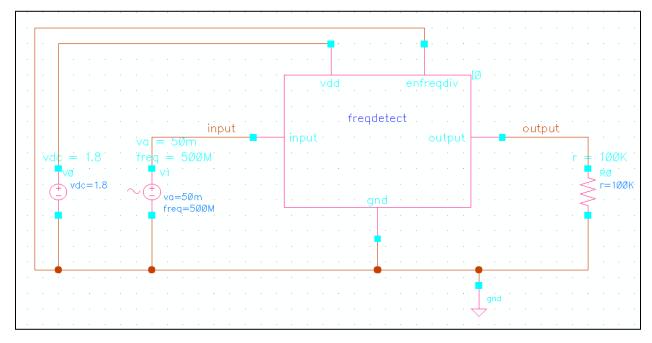

| Figure 2.17 –Frequency Divider Testbench                                                       | 24 |

| Figure 2.18 –Frequency Divider Simulation Output                                               | 25 |

| Figure 2.19 –Frequency Divider Testbench to Test Bypass Capacitor                              | 26 |

| Figure 2.20 –Frequency Divider Circuit Narrowed View                                           | 26 |

| Figure 2.21 –Frequency Divider Circuit to Test Bypass Capacitor Simulation Output with         |    |

| Insufficiently Large Bypass Capacitor                                                          | 27 |

| Figure 2.22 – Frequency Divider Circuit to Test Bypass Capacitor Simulation Output with        |    |

| Correctly Sized Bypass Capacitor                                                               | 28 |

| Figure 2.23 –Amplitude Detector Circuit                                                        | 29 |

| Figure 2.24 – Amplitude Detector Circuit Testbench                                             | 30 |

| Figure 2.25 – Amplitude Detector Simulation Output                                             | 30 |

| Figure 3.1 – Top Level Flowchart of Tuning Algorithm                                           | 32 |

| Figure 3.2 – Frequency Tuning Algorithm Flowchart: Revision 2                | 34 |

|------------------------------------------------------------------------------|----|

| Figure 3.3 – Get Frequency Algorithm Flowchart (Used with Permission [2])    | 35 |

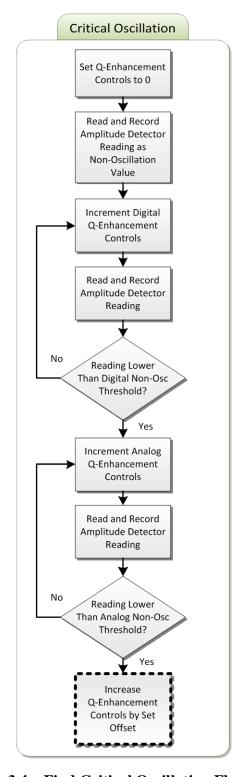

| Figure 3.4 – Find Critical Oscillation Flowchart                             | 36 |

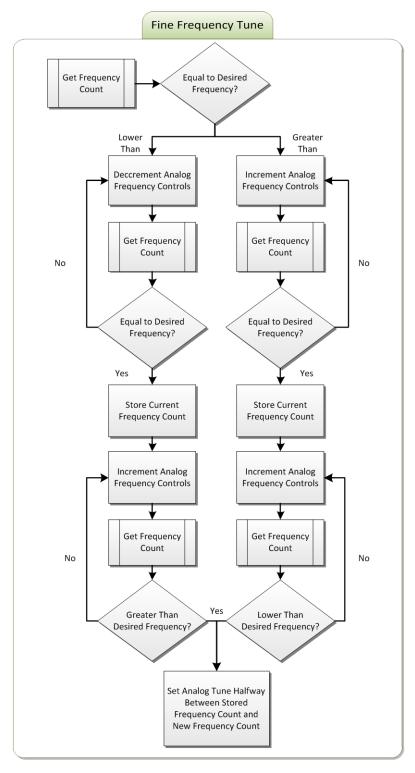

| Figure 3.5 – Fine Tune Flowchart                                             | 37 |

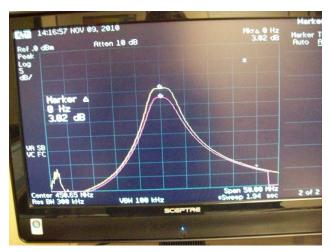

| Figure 3.6 - Passband Variation without                                      | 38 |

| Fine Tuning                                                                  | 38 |

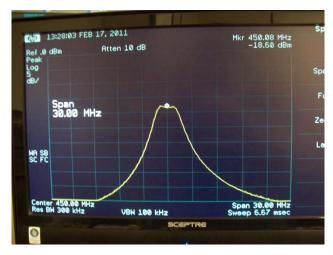

| Figure 3.7 – 2.5 MHz Bandwidth Passband with Fine Tuning                     | 39 |

| Figure 4.1 – Direct Conversion Receiver Block Diagram                        | 42 |

| Figure 4.2 – Superheterodyne Receiver Block Diagram                          | 43 |

| Figure 4.3 – Multiple Conversion Superheterodyne Receiver Block Diagram      | 44 |

| Figure 4.4 – Superheterodyne Receiver Block Diagram                          | 44 |

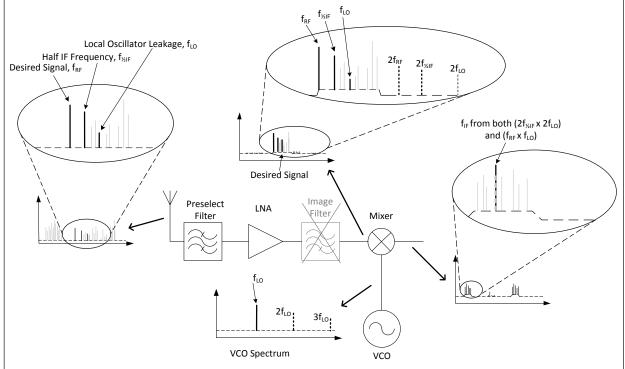

| Figure 4.5 – Superheterodyne Receiver with Spectra                           | 46 |

| Figure 4.6 – Nonlinear Spurs                                                 | 48 |

| Figure 4.7 – Digital Spurs                                                   | 50 |

| Figure 4.8 – Image Frequency                                                 | 51 |

| Figure 4.9 – 1/2IF & 1/3IF Spur Frequencies                                  | 52 |

| Figure 4.10 Fourier Spectrum Response to Quieting                            | 54 |

| Figure 4.11 – Test Setup for VR-120 & VX-3                                   | 55 |

| Figure 4.12 – Test Setup for SDR                                             | 56 |

| Figure 4.13 – Test Setup for K-State Microtransceiver                        | 56 |

| Figure 4.14 – Spurious Rejection Response Test System LabVIEW Code Flowchart | 57 |

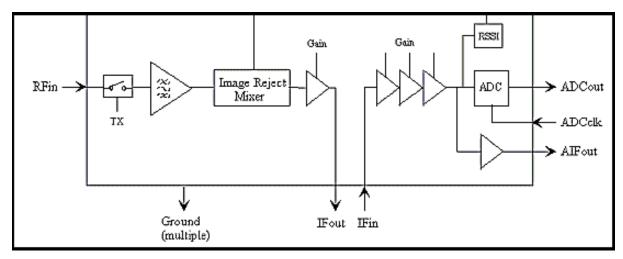

| Figure 4.15 – VR-120 Block Diagram - after [18]                              | 59 |

| Figure 4.16 – VX-3 Block Diagram - after [19]                                | 60 |

| Figure 4.17 – SDR Block Diagram - after [20]                                 | 61 |

| Figure 4.18 – K-State Microtranciever - after [21]                           | 62 |

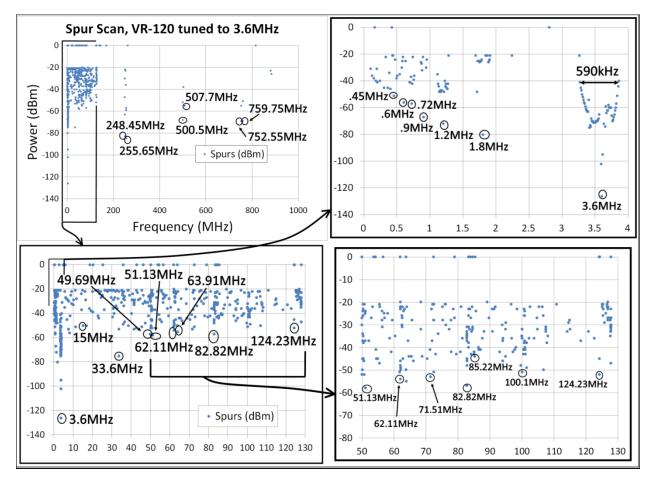

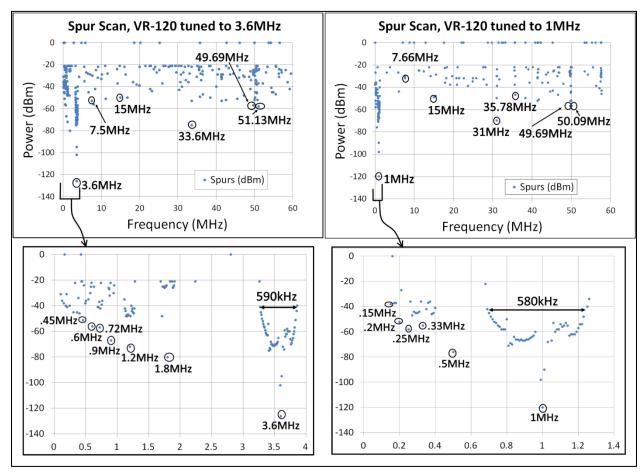

| Figure 4.19 – VR-120 3.6 MHz Tune Test Results                               | 64 |

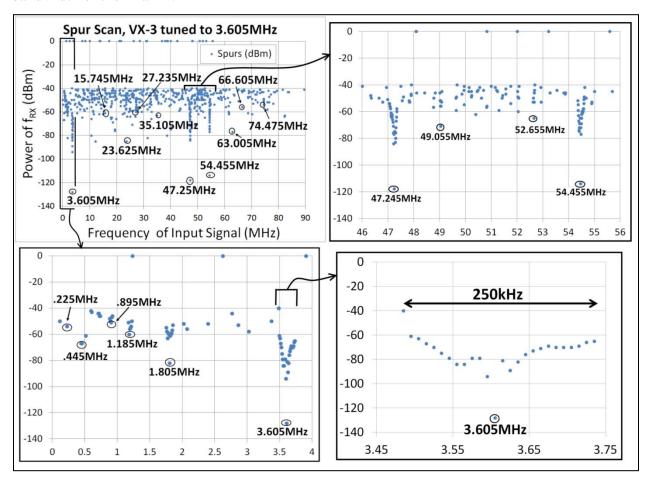

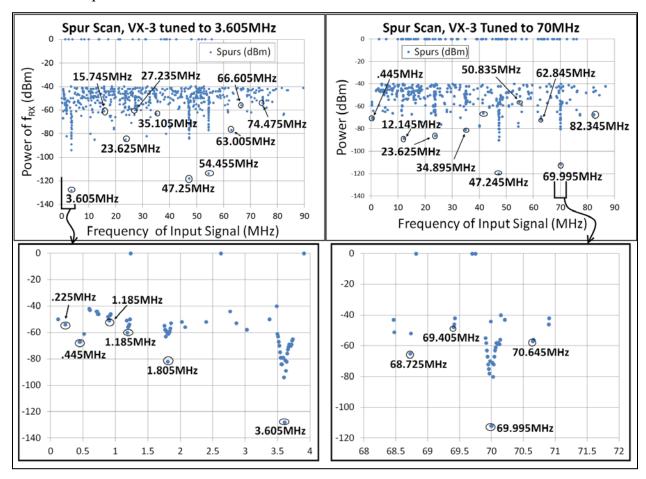

| Figure 4.20 – VX-3 3.6 MHz Tune Test Results                                 | 66 |

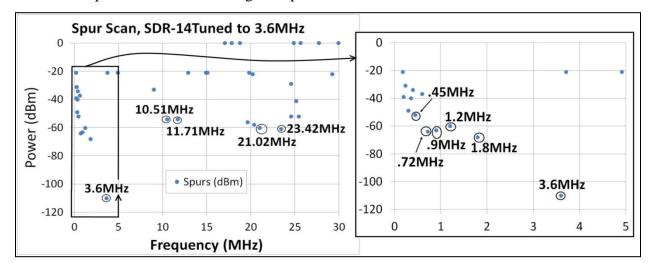

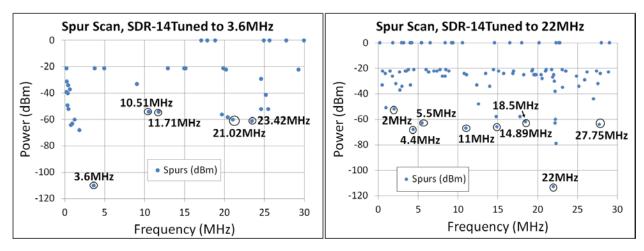

| Figure 4.21 – SDR 3.6 MHz Tune Test Results                                  | 69 |

| Figure 4.22 – VR-120 3.6 MHz to 1 MHz Tune Comparison Test Results           | 71 |

| Figure 4.23 – VX-3 3.6 MHz to 70 MHz Tune Comparison Test Results            | 73 |

| Figure 4.24 – SDR-3.3.6 MHz to 22 MHz Tune Comparison Test Results           | 75 |

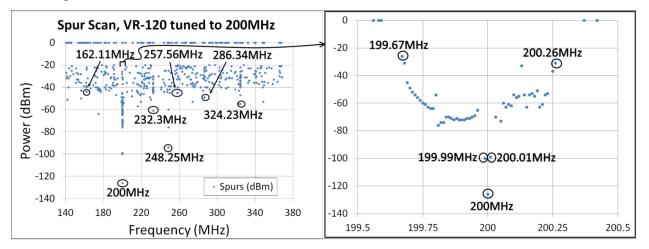

| Figure 4.25 – VR-120 120 MHz Tune Comparison Test Results                                | 76   |

|------------------------------------------------------------------------------------------|------|

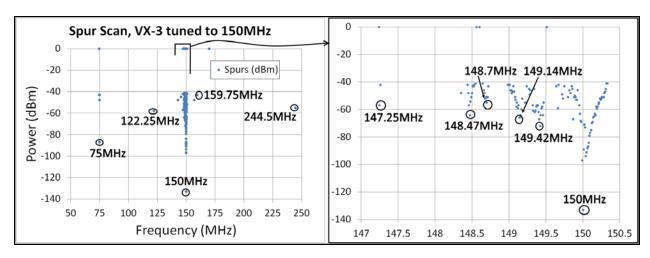

| Figure 4.26 – VX-3 150 MHz Tune Comparison Test Results                                  | 78   |

| Figure 4.27 – K-State Microtransceiver Without & With the Fractional N-Synthesizer Test  |      |

| Results                                                                                  | 80   |

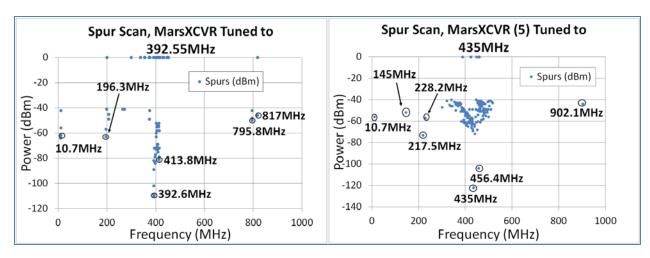

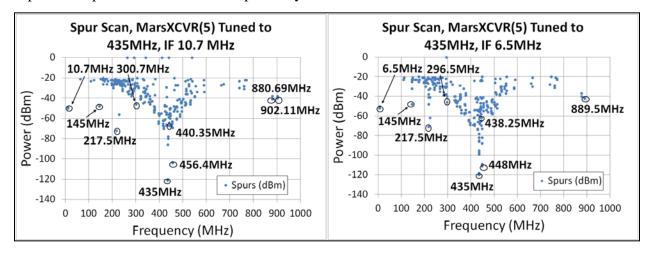

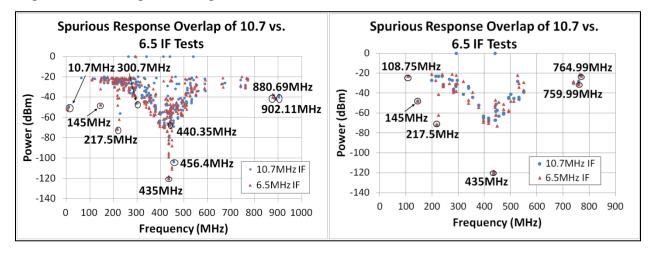

| Figure 5.1 – K-State Microtransceiver 435MHz Tune Different IF Comparison Test Results   | 81   |

| Figure 5.2- K-State Microtransceiver Varied IF Comparison Spur Residual                  | 84   |

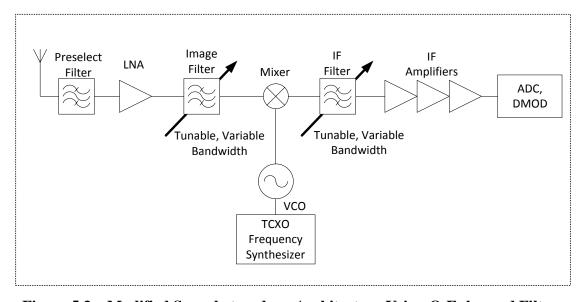

| Figure 5.3 – Modified Superheterodyne Architecture Using Q-Enhanced Filters              | 86   |

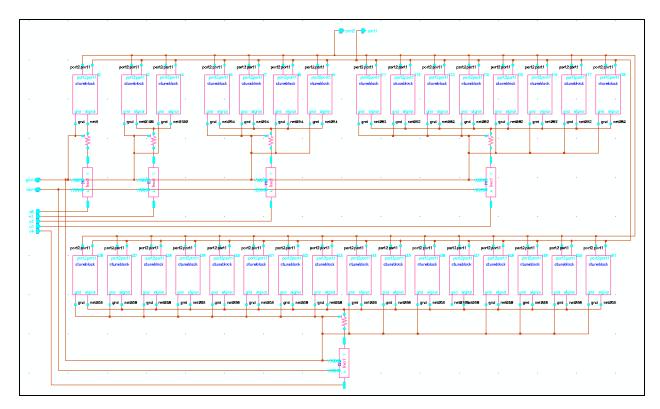

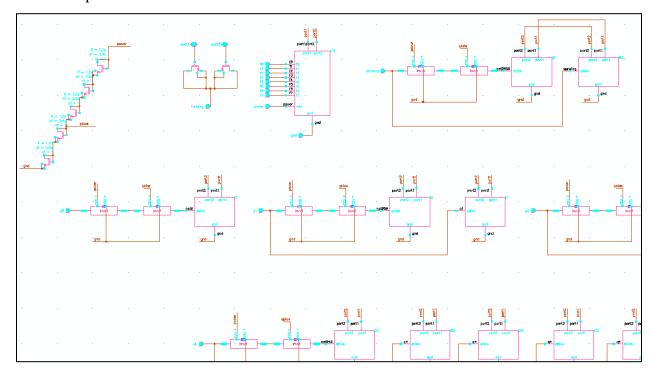

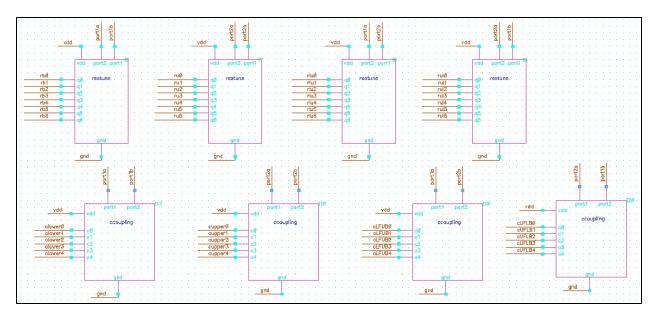

| Figure A.1 – Top Level View of Q-Enhanced Filter Schematic                               | 92   |

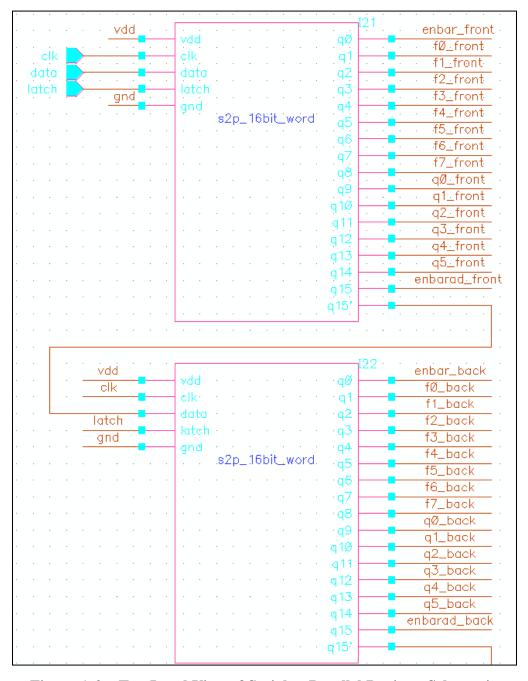

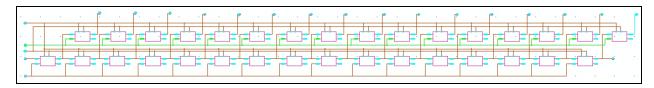

| Figure A.2 – Top Level View of Serial to Parallel Register Schematic                     | 93   |

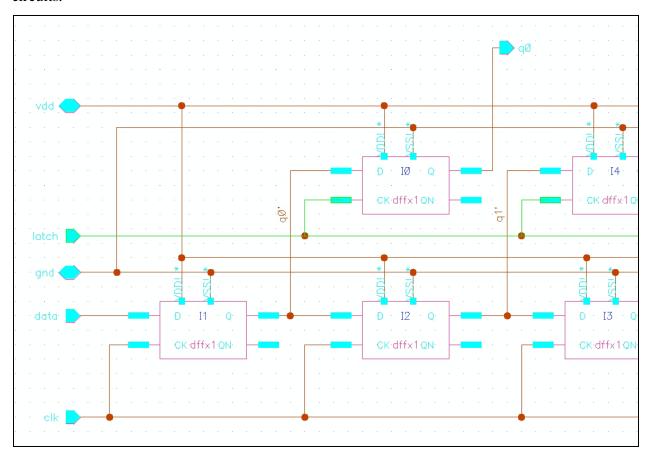

| Figure A.3 – Single Cell View of Serial to Parallel Register Schematic                   | 94   |

| Figure A.4 – Narrowed View of Serial to Parallel Register Single Cell                    | 94   |

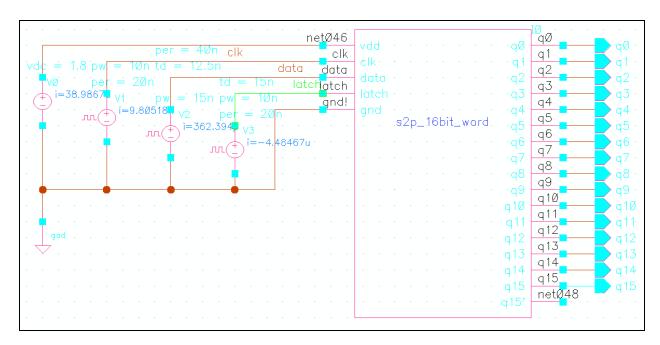

| Figure A.5 – Test Bench for Serial to Parallel Register                                  | 95   |

| Figure A.6 – Simulation Output for Serial to Parallel Register                           | 95   |

| Figure A.7 – Simulation Output for Serial to Parallel Register                           | 96   |

| Figure A.8 – Top View of Differential Cores, Frequency Detectors, and Amplitude Detector | rs97 |

| Figure A.9 –Differential Core, Tuning Block, and Buffer                                  | 97   |

| Figure A.9 –Differential Core Schematic                                                  | 98   |

| Figure A.10 –Differential Core Test Bench                                                | 99   |

| Figure A.11 – Simulation Output of Differential Core                                     | 99   |

| Figure A.12 – Buffer Circuit                                                             | 100  |

| Figure A.13 – Buffer Circuit Testbench                                                   | 101  |

| Figure A.14 – Simulation Output of Buffer Circuit                                        | 101  |

| Figure A.15 – Top View of Frequency and Q-Enhancement Tuning Blocks                      | 102  |

| Figure A.16 - Narrowed View of Frequency and Q-Enhancement Tuning Block                  | 102  |

| Figure A.17 – Top View of Frequency Tuning Block                                         | 103  |

| Figure A.18 – Narrowed View of Frequency Tuning Block                                    | 103  |

| Figure A.19 – Cell View of Q-Enhancement Tuning Block                                    | 104  |

| Figure A.20 – Top View of Capacitive Coupling and Resistance Tuning Blocks               | 105  |

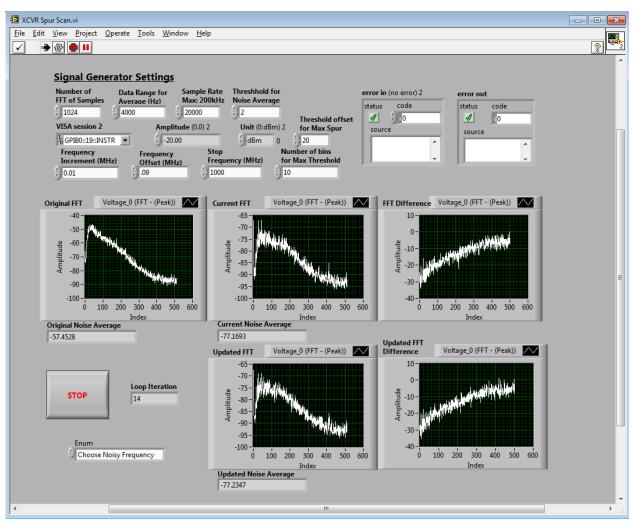

| Figure C.1 – Screen Shot of NI Code 'XCVR_Spur_Scan' Running                             | 122  |

# **List of Tables**

| Table 3.1 – Fine Tune Settings for 2.5 MHz Bandwidth                                   | 39 |

|----------------------------------------------------------------------------------------|----|

| Table 3.2 – Word Sent from Microcontroller to Filter                                   | 40 |

| Table 4.1 – VR-120 3.6 MHz Tune Test Results                                           | 65 |

| Table 4.2 – VX-3 3.6 MHz Tune Test Results                                             | 68 |

| Table 4.3 – SDR 3.6 MHz Tune Test Results                                              | 69 |

| Table 4.5 – VR-120 3.6 MHz to 1 MHz Tune Comparison Test Results                       | 72 |

| Table 4.6 – VX-3 3.6 MHz to 70 MHz Tune Comparison Test Results                        | 74 |

| Table 4.7 – SDR 3.6 MHz to 22 MHz Tune Comparison Test Results                         | 75 |

| Table 4.8 – VR-120 120 MHz Tune Comparison Test Results                                | 77 |

| Table 4.9 – VX-3 150 MHz Tune Comparison Test Results                                  | 78 |

| Table 4.10 – K-State Microtransceiver Without & With the Fractional N-Synthesizer Test |    |

| Results                                                                                | 80 |

| Table 5.1 – K-State Microtransceiver Spurious Response, IF= 10.7 MHz                   | 82 |

| Table 5.2 – K-State Microtransceiver Spurious Response, IF= 6.5 MHz                    | 83 |

| Table 5.3 – K-State Microtransceiver 435MHz Tune Different IF Spur Residual            | 86 |

# Acknowledgements

My first thanks must go to Dr. Kuhn. I've enjoyed many of his classes and benefited greatly from his teaching over several years. Dr. Kuhn truly enjoys his work and cares about teaching that knowledge. I am so grateful to have honor of working under his tutelage.

Thank you also to the rest of my committee, Dr. Rys and Dr. DeVault. I appreciate your time and feedback.

I must also thank Renee Strouts and Joel Schonberger. Their work has been essential to my research. Joel in particular left a beautifully documented project for me and tirelessly answered questions as I began to learn the existing system. I hope to find myself working with engineers of his caliber, and superlative documentation skills, in the future.

A thanks also goes to Steven Melton and to Mathew Clewell. They have both been excellent office mates this past year, providing many fun distractions, much good conversation, intelligent technical advice and many sanity checks.

Thank you also to Joel Carroll for the use of a 'MyDAQ' and a willingness to answer a string of questions about LabVIEW.

I am particularly grateful to my close friends Aimee Smith and Josh Zavala for their encouragement and support this past semester. Their help, while dramatically different from each other, has been much appreciated and I am grateful to them both.

I am grateful to so many people not mentioned here. I'm honored to have received the time and effort so of many professors who were doubtlessly quite busy and still found away to answer yet another question. I have studied with many students and learned a great deal from them. I've known and learned with many people here at K-State and benefited from their insight. Thank you.

# **Dedication**

This thesis is dedicated to my parents, because they taught me to dream about learning.

This thesis is dedicated to my Grandma Verna, because she taught me how to have faith in my dreams and work to achieve my dreams one pragmatic step at a time.

This thesis is dedicated to the souls that I have known along the path to this dream, because they have taught me how to live and how to love. I hope in the end I have made their lives better as they have made mine. Most of all, I wish them the courage to dream and the faith and passion to achieve their dreams.

# **Chapter 1 - Introduction**

## 1.1 Objective

This thesis is divided into two parts. First, this thesis documents the redesign of the Two-Pole Q-Enhanced Band-Pass Filter into a new integrated circuit (IC) technology. Problems in the previous filter design are explained and solutions are explored. Additionally, the supporting software is refined with additions and improvements to the pre-existing tuning algorithm and changes to the supporting software and hardware needed for the redesigned IC portion of the filter are explained. Second, this thesis considers the currently used methods for, and historical emphasis placed on, characterizing a receivers spurious rejection responses. The development of an automated test system to explore this behavior is described and the test results are presented in a novel graphical format. Based on the demonstrated capability of the Q-enhanced filter and insight from the spurious rejection response data, this thesis proposes a new receiver architecture. Finally, this architecture is tested to determine if it could significantly improve a receiver's spurious rejection capability.

# 1.2 Q-Enhanced Filter Development Primer

## 1.2.1 Integrated Filter Design

#### 1.2.1.1 Previous Work

The existing Q-enhanced filter used as a starting point for this thesis was designed by Renee Strouts based on circuit concepts developed in a class project. The original design is documented in [1]. This active filter uses Q-enhancement to create a tunable variable bandwidth bandpass filter. Q-Enhancement is explained thoroughly in both [1] and [2] and will only be defined here briefly to lend context to this thesis's discussion of the filter.

#### 1.2.1.2 Q-Enhancement

'Q-enhancement' refers to the technique of increasing the quality factor of an inductor, capacitor, or tuned circuit [3]. The 'quality factor' is defined by the ratio of the energy stored to

the energy dissipated in these components. In general, Q is defined mathematically by equation (1.1).

$$Q = 2\pi \times \frac{Energy Stored}{Energy Dissapated Per Cycle}$$

(1.1)

A more detailed explanation of Q and the associated RF models of inductors and capacitors can be found in [2]. The important idea to understand here is that every inductor and capacitor includes a non-ideal resistance which limits the components performance at sufficiently high frequencies. This behavior is crucial to filter design because the Q of a filter fundamentally limits its achievable bandwidth according to (1.2).

$$Bandwidth = \frac{f_0}{Q}$$

(1.2)

where  $f_0$  is the center frequency of the filter passband and Q is the composite filter quality factor. Typically, the overall Q of a filter has been limited by the inductors used. In particular, high Q inductors are very difficult to manufacture in integrated circuits [4]. In this work off chip inductors are used, but the previous theses and associated research include efforts to achieve high Q on chip inductors [5]. Q-Enhancement is achieved in the filter in this thesis using cross coupled field effect transistors.

### 1.2.1.3 Revised Integrated Circuit Block Diagram

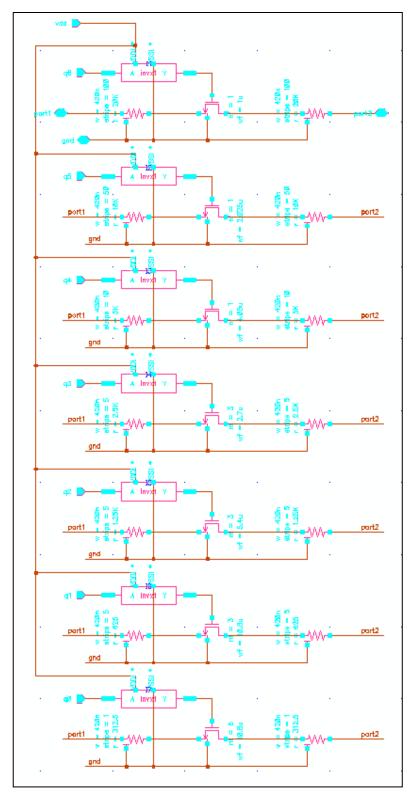

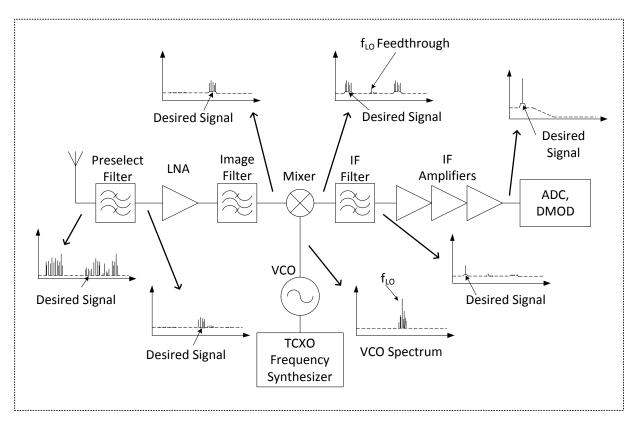

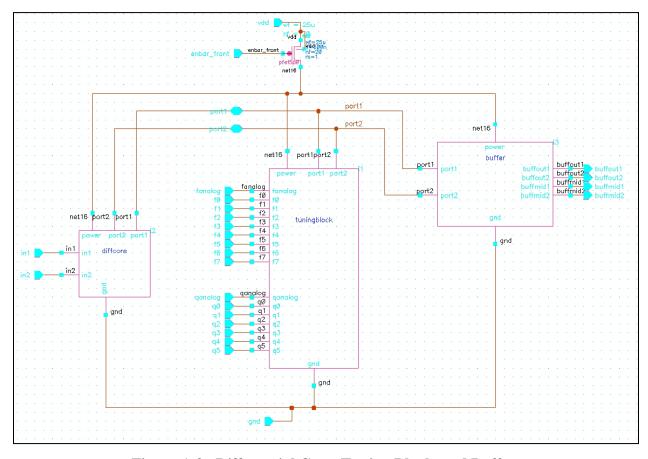

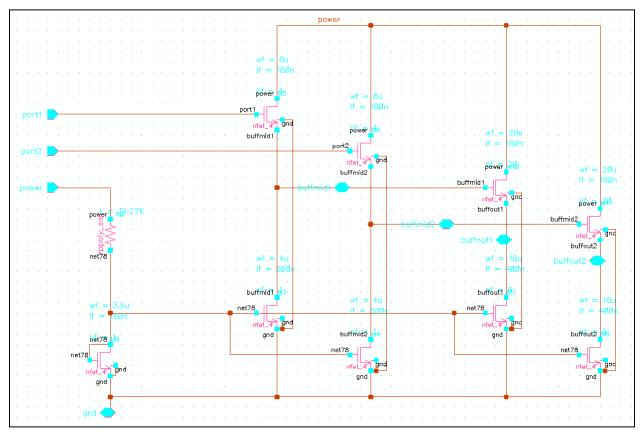

The top level block diagram for the revised Two-Pole Q-Enhanced Band-Pass Filter is shown in Figure 1.1.

Figure 1.1 – Q-Enhanced Filter Block Diagram

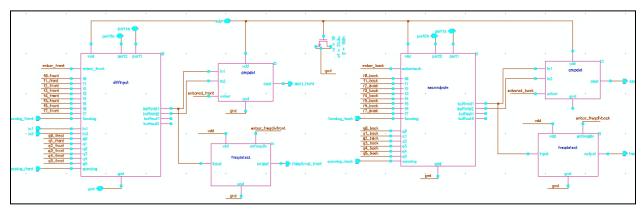

Similar to previous designs, the filter's input signal is driven into a differential cascoded amplifier core, labeled 'Front-End'. The second core, the 'Back-End' is an identical copy of the Front-End with grounded inputs. The amplitude detection and frequency division circuits for the Front-End and Back-end are driven by the cores via identical buffers to protect the filter from too much loading. The filter is programmed via the serial to parallel register from a microcontroller which runs the supporting software introduced in section 1.2.2. This communication is a bit stream which controls the enabling of the buffers, amplitude detectors, and frequency dividers. The rest of these bits control binary weighted cells of Q-enhancement, frequency tuning, capacitive coupling and resistance tuning used to tune the filter center frequency, bandwidth and shape of the passband. The LC tank circuits are off-chip resonators driven by the Front-end and Back-end. The final output of the filter is driven differentially from the Back-End buffer.

The entire IC was ported to a .18µm SOI process technology which is lower power and better performance at higher frequencies than the .5µm and .25µm SOI processes used previously. Portions of the circuit were redesigned to add functionality, improve performance or to fix problems in the existing filter. These modified circuit designs are shown shaded slightly darker with a dashed outline in Figure 1.1. The serial to parallel register was increased from 64 bits to 96 bits to control additional circuitry. The intrinsic gain of the cascoded amplifier cores was lowered to 1 to improve the dynamic range. Resistance tuning circuitry was added to cancel unwanted coupling affects. The frequency dividers were redesigned entirely to eliminate internal oscillation problems in the current design. Also, a pre-existing design flaw was discovered in the amplitude detector circuit. The design changes to the frequency divider and the addition of the resistance tuning are explained in section Chapter 2. The design flaw in the amplitude detector is also explained in Chapter 2. The rest of the circuit design as ported to the new process is documented in appendix A.

#### 1.2.2 Supporting Hardware and Software

#### 1.2.2.1 Previous Work

The filter is implemented on a circuit board using a microcontroller to program and tune the filter for testing and implementation. In the previous thesis work by Joel Schonberger, a test application was written in C# to create a graphical user interface (GUI) which allowed the user to control the filter manually or provide settings to an automated tuning algorithm. The circuit board, the supporting software written for the microcontroller, and GUI are documented thoroughly in [2]. The review here is therefore brief and provided only as a basis for understanding the additions to this supporting software described in this thesis.

#### 1.2.2.2 Software Additions

It has been a long time goal of the work this thesis continues to achieve fractional bandwidths of one percent or less relative to the center frequency. Achieving this narrow bandwidth required the addition of fine tuning in the existing automated tuning algorithm. Those additions are implemented and tested and documented in Chapter 3 and Appendix B. The changes to the filter design also create a need to modify the supporting code for the microcontroller and the GUI. The changes to the code for the microcontroller are explained in Chapter 3. Changes to the GUI are also suggested, but not yet implemented.

# 1.3 Receiver Architectures and Filter Applications

#### 1.3.1 Motivation

A crucial issue in today's wireless communication technologies is maximizing throughput in the allocated spectrum. As a result increasing demands are being placed on communication technology. According to Michael Marcus, retired associate chief for Technology with the FCC, "Transmitters don't use spectrum, receivers do." [6] Therefore, if receiver performance is improved, the spectrum can be used more efficiently. Given the rapidly increasing popularity of devices using wireless technologies, the demand on the RF spectra is growing. Improving receiver's performance to meet this demand is an important goal.

Receiver performance is a complex topic with a long history. To improve upon current designs it is necessary to quantify current receiver performance to accurately assess the current state of the technology and gain insight into how it could be improved. The task of a receiver is to detect and translate the signal it's tuned to receive without being affected by any other signal. One way to measure how well a receiver does this is to measure the receiver's spurious rejection response. This work attempts to address the need to measure receiver performance by developing a spurious response rejection test system and developing a novel graphical format to display the results.

The limiting factor in improving receiver performance is largely governed by the ability to filter and completely isolate only the desired signal. As a result, much research has been done to design optimal filters. Q-Enhancement has been considered as an option for use integrated receivers in previous work [7] and [8]. However, it's been assumed that the limited dynamic range and high noise figure associated with Q-enhancement would compromise receiver performance [9]. This research in this thesis characterizing receiver's spurious rejection response indicates this conclusion is not fully correct.

#### 1.3.2 Prior Art

There are many criteria used to evaluate various aspects of receiver performance including but not limited to, sensitivity, noise figure, dynamic range, third order intercept, IF rejection, and adjacent channel rejection. This criterion is used both by amateurs [10] and in industry and academia [11]. Another technique often used to look mixing schemes is the so-called 'spur chart' in which a diagram is developed to illustrate potential combinations of incoming signal frequencies and their harmonics and  $f_{LO}$  and its harmonics that a receiver may respond to [12]. Despite the useful information this diagram contains, it is difficult to understand quickly. Moreover, no information about the severity of the spurious response is identified.

Literature generally emphasizes the important causes of spurious responses in receivers to be mixing, IF separation, harmonics and coupling with existing signals in the receiver [13]. Other work has explored automated testing spurious rejection responses to apprehend the full complexity of receiver's performance [14], [15].

Unfortunately, spur charts and the many various standards of receiver performances mentioned above fail to yield an intuitive assessment of the receiver's spurious response rejection performance. Even the works on automated spurious response testing, while quite thorough, didn't offer a simple way to view and intuitively evaluate the receiver performance. Chapter 4 in this work addresses a new automated spurious rejection response test system and develops and demonstrates a useful, intuitive graphical display of the test results.

## 1.3.3 Research Accomplished

#### 1.3.3.1 Spurious Rejection Response Testing System

To understand and characterize receiver spurious rejection response an automated test system was developed. This system allowed four receivers to be tested thoroughly over different amplitude ranges and different frequencies. The system uses a 'MyDAQ' and a LabVIEW based test GUI. This system is explained at length in section 4.3.

#### 1.3.3.2 Spurious Rejection Response Results

The data obtained from the Spurious Rejection Test System proved extensive. A graphical display of the results was developed providing insights into the four receivers tested. Explanations for the spurious responses observed were analyzed and evaluated in section 4.5.

#### 1.3.3.3 Filter Application

Finally, a modified superheterodyne receiver using the Q-enhanced filter is proposed in Chapter 5. The potential improvements in spurious rejection are partially tested using the Spurious Rejection Test System. The results strongly indicate this solution might provide an excellent alternative to current receiver architectures.

# **Chapter 2 - Q-Enhanced Filter Redesign**

# 2.1 Design Overview

This Chapter documents the redesign of a two-pole Q-enhanced band-pass filter IC originally designed by Renee Strouts [1]. The first section will explain briefly the process of porting this design to a new technology. The next section will focus on the problems with an asymmetrical passband in the previous filter design. The origin of this asymmetry is explained theoretically and the solution in the hardware design is documented. Last, this section looks at the circuits which were changed significantly from the original design or had intrinsic issues in the original design.

# 2.2 Porting Design to Different Integrated Circuit Technology

This section describes porting the previous IC design in a silicon-on-sapphire (SOS) process to a bulk SOI process. The bulk SOI process runs on a lower power voltage and has a smaller minimum length of .18 $\mu$ m than the SOS process. The new process also includes body contacts and a different  $k'_n$  value. As a result, porting the circuit design required re-biasing the circuits and choosing new W/L ratios which matched the circuits design specifications.

In general, analog design using metal on oxide semiconductor field effect transistors (MOSFETs or 'FET's) at an IC level is ruled by well-known equation (2.1)

$$I_D = \frac{k_n'}{2} \frac{W}{L} (V_{GS} - v_t)^2$$

(2.1)

for FETs in the active region neglecting Early effect. Long channel FETs in the triode region are described by (2.2).

$$I_D = k_n' \frac{W}{L} \left( (V_{GS} - v_t) v_{DS} - \frac{v_{DS}^2}{2} \right)$$

(2.2)

Also,

$$k_n' = \mu C_{ox} \tag{2.3}$$

and

$$V_{OV} = (V_{GS} - v_t) (2.4)$$

The above equations are well known, but the quadratic term is only correct for FETs that are 'long channel' with a sufficiently small overvoltage. If the FET is 'short channel' or the overvoltage is large enough, the equation for  $I_D$  versus  $V_{GS}$  the active region reduces to (2.5).

$$I_D = \frac{k_n'}{2} \frac{W}{L} (V_{GS} - v_t')$$

(2.5)

Where the new threshold voltage,  $v'_t$ , is the interpolated  $V_{GS}$ -axis intercept of the linear portion of the  $I_D$  versus  $V_{GS}$  relationship. A particular case of this behavior in a FET is shown in Figure 2.1. This behavior is not typically explained in textbooks, but is consistently exhibited in experimental data [16].

Figure 2.1 – I<sub>D</sub> versus V<sub>GS</sub> Curve Showing Quadratic and Linear Behavior

It's easy to see in the  $I_D$  versus  $V_{GS}$  above that the quadratic behavior only lasts from about  $V_{GS}$  = .35 V to VGS = .8 V. After  $V_{GS}$  increases past about .8 V, the current increases linearly. This behavior, as stated above, may start nearly as soon as the FET is in saturation if the length is small enough. The new process lengths used in the Q-enhanced filter redesign were so small that most design work assumes that the FETs are short channel.

Two other equations are important during this design when a FET is used as a switch. First, when the FET is 'on' so that it's conducting current and in the triode region, the resistance that signals see from drain to source,  $r_{ON}$ , is given in (2.6).

$$r_{ON} = \frac{1}{\frac{k_N''W}{2L}(v_{gs} - v_t)}$$

(2.6)

Simultaneously, the capacitance of the FET can be calculated using (2.7).

$$C = nWLC_{ox} (2.7)$$

which can then be used to find the impedance of a FET using (2.8)

$$X_C = \frac{1}{2\pi f C} \tag{2.8}$$

The 'n' in (2.7) is a fractional value between zero and one determined by the signal path through the FET and whether the FET is off, in triode or in saturation.

Finally, since the overall design of the previous IC was robust and working well, most circuits could be redesigned by simply assuming the same biasing scheme and altering the W/L ratio to compensate for the change in  $k'_n$ . However, this assumed the body effect would be negligible. While this would simplify porting the design, some circuits needed to be addressed in more detail. In general good design practice dictated that all circuits needed to be simulated and

evaluated individually to ensure a robust design that matched, or ideally exceeded, its predecessor's performance.

# 2.3 Asymmetry in the Passband

This section deals with pronounced asymmetry in the passband shape, a major problem in the previous design. This problem is documented extensively in [2] and illustrated in Figure 2.2. The theoretical origin of this asymmetry is investigated and determined to be a result of two issues in the previous design: the non-idealities of inductive coupling with finite Q inductors and an error in the original coupling capacitor circuit design.

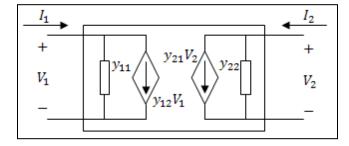

Figure 2.2 – Filter Response Showing Asymmetric Passband (Used with Permission [2])

#### 2.3.1 Sources of Asymmetry

Both sources of asymmetry are explored and characterized mathematically using admittances in [2]. However, there is an algebraic error in the solution describing the inductive coupling, so the corrected solution is explained in section 2.3.1.2 followed by the circuit level solution. To prepare a basis for explaining the hardware design solution to these asymmetries, admittances are reviewed in section 2.3.1.1. Finally, the solution for the coupling capacitors derived in [2] is presented in section 2.3.1.3 along with the circuit level solution.

#### 2.3.1.1 Admittance Review

The basic ideas of admittance are presented here to provide a context for the discussion of characterizing the asymmetries in the passband. The definitions of y-parameters are shown in Figure 2.3 and equations (2.9) - (2.13). Y parameters for inductors, capacitors and resistors are derived in (2.14) - (2.16).

Admittance is defined as the inverse of impedance and can described with the two port network shown in Figure 2.3.

Figure 2.3 – Two Port Network (Used with Permission [2])

This network allows the following definitions to be developed.

$$\begin{bmatrix} i_1 \\ i_2 \end{bmatrix} = \begin{bmatrix} y_{11} & y_{12} \\ y_{21} & y_{22} \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \end{bmatrix}$$

(2.9)

Input port admittance

$$y_{11} = \frac{i_1}{V_1} \Big|_{V_2 = 0} \tag{2.10}$$

Reverse Transfer Admittance

$$y_{12} = \frac{i_1}{V_2} \Big|_{V_1 = 0} \tag{2.12}$$

Forward Transfer Admittance

$$y_{21} = \frac{i_2}{V_1} \Big|_{V_2 = 0} \tag{2.11}$$

Output Port Admittance

$$y_{22} = \frac{i_2}{V_2} \Big|_{V_1 = 0} \tag{2.13}$$

Using the definitions in (2.10) - (2.13) a resistor, capacitor and inductor, connected between ports one and two, are characterized in the next three equations.

Resistor:

$$y_{21} = \frac{i_2}{V_1}\Big|_{V_2 = 0} = \frac{i_2}{Ri_1} = \frac{-i_1}{Ri_1} = -\frac{1}{R}$$

(2.14)

Capacitor:

$$y_{21} = \frac{i_2}{V_1}\Big|_{V_2=0} = \frac{i_2}{(-jX_c)i_1} = \frac{-i_1}{(-jX_c)i_1} = \frac{-j}{X_c}$$

(2.15)

Inductor:

$$y_{21} = \frac{i_2}{V_1}\Big|_{V_2 = 0} = \frac{i_2}{(jX_L)i_1} = \frac{-i_1}{(jX_L)i_1} = \frac{j}{X_L}$$

(2.16)

By symmetry for these elements,  $y_{12}$  will equal  $y_{21}$ . A similar process could be used to find  $y_{11}$  and  $y_{22}$ , which should also be equal to each other by symmetry.

### 2.3.1.2 The First Source of Asymmetry

As explained above, all inductors are limited by their Q value and have a small amount of resistance. The previous work determined that the coupling between the inductors in the LC tank circuits was not purely inductive due to the limited Q of the inductors [2]. As a result the inductors introduced an unwanted coupling term 90° out of phase with the desired LC coupling used in realizing the basic 2-pole response. To quantify and understand this unwanted coupling, the impedance of the LC tank circuits are modeled mathematically in section 2.3.1.2.1.

#### 2.3.1.2.1 Origin of Asymmetry: Inductive Coupling

The LC tank circuits for the Q-enhanced filter are off chip and laid out using two discrete inductors and a capacitor as shown in Figure 2.4.

Figure 2.4 – Topological Transformation of LC Tank Circuit

This topology shown on the left of Figure 2.4 was used to allow the desired biasing. It is not immediately obvious how to translate these two circuits into two port network. The topological transformation required is shown in Figure 2.4, beginning with the topology of the tank circuits and ending with the circuit rearranged into a two port network topology for admittance analysis of the inductor coupling issue.

From Figure 2.4 it's defined that  $2L_{1a}=2$   $L_{1b}=$   $L_1$ . The capacitors are omitted since we only need to consider the inductive coupling, shown as k in the last box to the right. Using these definitions the forward transfer admittance can be derived as follows

$$L_1 = L_2$$

,  $R_{s1} = R_{s2} = R_s$ ,  $M = k\sqrt{L_1L_2}$  (2.17, 2.18, 2.19)

$$V_1 = j\omega L I_1 + j\omega L I_2 k + I_1 R_s$$

(2.20)

$$0 = j\omega L I_2 + j\omega L I_1 k + I_2 R_s \tag{2.21}$$

Solving (2.21) for  $I_1$  and letting  $X_L = \omega L$

$$I_1 = -\frac{I_2(jX_L + R_S)}{jX_L k} (2.22)$$

Substitute (2.22) into (2.20) where  $X_L = \omega L$

$$V_1 = -\frac{I_2(jX_L + R_S)}{k} + jX_L I_2 k - \frac{I_2(jX_L + R_S)R_S}{jX_L k}$$

(2.23)

$$y_{21} = \frac{I_2}{V_1} \Big|_{V_2 = 0} = \frac{1}{\frac{-(jX_L + R_S)}{k} + jX_L k - \frac{(jX_L + R_S)R_S}{iX_L k}}}$$

(2.24)

Combining fractions, inverting and multiplying out yields

$$y_{21} = \frac{jX_L k}{-(jX_L + R_S)jX_L - (jX_L + R_S)R_S}$$

(2.25)

$$y_{21} = \frac{jX_L k}{-(-1)X_L^2 - jR_S X_L - jX_L R_S + R_S^2}$$

(2.26)

$$y_{21} = \frac{jX_L k}{R^2 + X_L^2 - j2X_L R_S} \tag{2.27}$$

$$y_{21} = \frac{jX_L k}{(R_S^2 + X_L^2) - j2X_L R_S} \left( \frac{(R_S^2 + X_L^2) + j2X_L R_S}{(R_S^2 + X_L^2) + j2X_L R_S} \right)$$

(2.28)

$$y_{21} = \frac{-2X_L^2 R_s k}{\left(R_s^2 + X_L^2\right)^2 + 4X_L^2 R_s^2} + \frac{jX_L k \left(R_s^2 + X_L^2\right)}{\left(R_s^2 + X_L^2\right)^2 + 4X_L^2 R_s^2}$$

(2.29)

Now letting  $Q \gg 1$ , so  $R_s \ll X_L$  due to  $R_s = \frac{X_L}{Q}$ , all  $R_s^2$  go to zero.

$$y_{21} = \frac{-2R_s k}{X_L^2} + \frac{jk}{X_L} = \frac{k}{X_L} \left( -\frac{2}{Q} + j \right)$$

(2.30)

Last, we cancel the unwanted real component of  $y_{21}$  using the admittance of a resistor derived in (2.10). The necessary resistance to eliminate the unwanted  $y_{21}$  admittance can be found by summing that admittance with the admittance of a resistor and solving for the resistor. The resulting resistance value is shown calculated in (2.27).

$$\frac{\left(R_S^2 + X_L^2\right)^2 + 4X_L^2 R_S^2}{2X_L^2 R_S k} \approx \frac{X_L^2}{2R_S k} \approx \frac{QX_L}{2k} = R$$

(2.31)

where the real parts in (2.29) and (2.30) are shown having solved for the wanted resistance value. From (2.31) we observe that in the ideal case  $y_{21}$  is equal to  $\frac{jk}{x_L}$  due to the quadrature relationship between V and I in an inductor. This is the term needed in a coupled resonator filter to from the desired passband response [17]. However, (2.31) shows an additional undesired "in-phase" term

as well. This term gives rise to the asymmetric shape seen in Figure 2.2 previously. This result in (2.29) was confirmed using ADS. That simulation and its output are shown in Figure (2.5) – (2.6).

Figure 2.5 – ADS Circuit Simulating Admittance Parameters

Figure 2.6 – ADS Simulation Output of Admittance Parameters

The simulation results in Figure 2.6 show agreement with the full form of the solution. The next section describes the circuit level solution to the unwanted portion of the inductive coupling in the next Q-enhanced filter design.

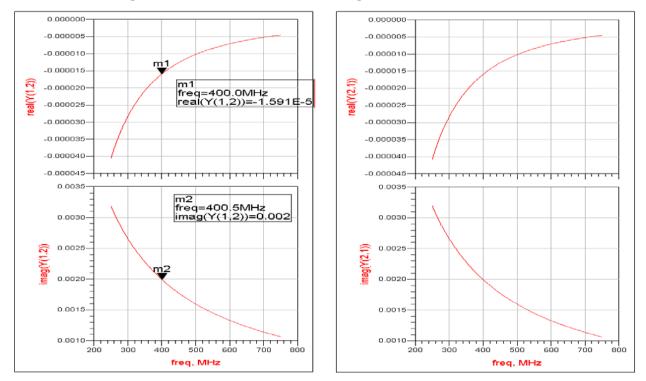

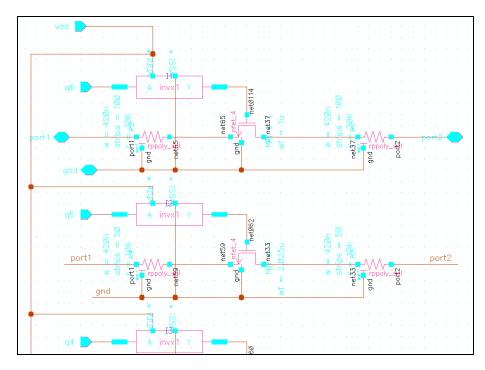

#### 2.3.1.2.2 Circuit Design Solution: Resistance Tuning

The work above shows that resistors interconnecting the LC tank circuits can be used to cancel the asymmetry in the passband. According to the result in the previous section the resistance value required will depend on frequency of operation, the strength of the coupling between the inductors and the Q of the inductors. The k value, or the amount of coupling between inductors, is documented in [2]. The range of frequencies considered is 400 MHz - 500 MHz. A typical range of Q values for on board inductors range from 5-20. Using this equation and these ranges, a potential range of resistance values was calculated using the full form of the solution and varying these parameters from the expected minimum to the expected maximum. A table summarizing these results is shown in Figure 2.7.

| Constants          |              |             |                   |      | Constants          |              |                          |                   |      |

|--------------------|--------------|-------------|-------------------|------|--------------------|--------------|--------------------------|-------------------|------|

| Centered at 500MHz | .040003      | 3.90E-09    | from Q            | 5-20 | Centered at 500MHz | .040003      | 3.90E-09                 | from Q            | 5-20 |

| f                  | ,04-,0003    | 5.50E-05    | Rs                | Q    | f                  | k            | L.                       | Rs                | Q    |

| 5.00E+08           | 0.04         | 3.90E-09    | 0.612610567       | 20   | 5.00E+08           | 0.04         | 3.90E-09                 | 2.45044227        | 5    |

| Basic Calcs        | 0.04         | 5.502 05    | 0.012010507       |      | Basic Calcs        | 0.04         | 3,302 03                 | ZI-TOO-T-TZE/     |      |

| XL                 |              |             |                   |      | XL                 |              |                          |                   |      |

| 12,25221135        | -            |             |                   |      | 12.25221135        | -            |                          |                   |      |

| Finally            |              |             |                   |      | Finally            |              |                          |                   |      |

| ,                  | Real(y21)    | Imag(y21)   | Yields a needed R | ₹    | •                  | Real(y21)    | Imag(y21)                | Yields a needed R |      |

|                    |              | 0.003172412 | 3109.01777        | 4    |                    |              | 0.003062939              | 950.7716007       | ,    |

| Constants          |              |             |                   |      | Constants          |              |                          |                   |      |

| Centered at 500MHz | .040003      | 3.90E-09    | from Q            | 5-20 | Centered at 500MHz | .040003      | 3.90E-09                 | from Q            | 5-20 |

| f                  | k            | L           | Rs                | Q    | f                  | k            | L                        | Rs                | Q    |

| 5.00E+08           | 0.0003       | 3.90E-09    | 0.612610567       | 20   | 5.00E+08           | 0.0003       | 3.90E-09                 | 2.45044227        | 5    |

| Basic Calcs        |              |             |                   |      | Basic Calcs        |              |                          |                   |      |

| XL                 |              |             |                   |      | XL                 |              |                          |                   |      |

| 12.25221135        |              |             |                   |      | 12.25221135        |              |                          |                   |      |

| Finally            |              |             |                   |      | Finally            |              |                          |                   |      |

|                    | Real(y21)    | Imag(y21)   | Yields a needed R | ł    |                    | Real(y21)    | Imag(y21)                | Yields a needed R |      |

|                    | -2.41234E-06 | 2.37931E-05 | 414535.703        | 2    |                    | -7.88833E-06 | 2.2972E-05               | 126769.5468       |      |

| Constants          |              |             |                   |      | Constants          |              |                          |                   |      |

| Centered at 500MHz | .040003      | 3.90E-09    | from Q            | 5-20 | Centered at 500MHz | .040003      | 3.90E-09                 | from Q            | 5-20 |

| f                  | k            | L           | Rs                | Q    | f                  | k            | L                        | Rs                | Q    |

| 4.00E+08           | 0.04         | 3.90E-09    | 0.490088454       | 20   | 4.00E+08           | 0.04         | 3.90E-09                 | 1.960353816       | 5    |

| Basic Calcs        |              |             |                   |      | Basic Calcs        |              |                          |                   |      |

| XL                 |              |             |                   |      | XL                 |              |                          |                   |      |

| 9.801769079        |              |             |                   |      | 9.801769079        |              |                          |                   |      |

| Finally            |              |             |                   |      | Finally            |              |                          |                   |      |

|                    | Real(y21)    | 01,         | Yields a needed R |      |                    | Real(y21)    | Imag(y21)                | Yields a needed R |      |

|                    | -0.000402056 | 0.003908693 | 2487.21421        | 9    |                    | -0.001314/22 | 0.003777092              | 760.6172805       | •    |

| Constants          |              |             |                   |      | Constants          |              |                          |                   |      |

| Centered at 500MHz | .040003      | 3.90E-09    | from Q            | 5-20 | Centered at 500MHz | .040003      | 3.90E-09                 | from Q            | 5-20 |

| f                  | k            | L           | Rs                | Q    | f                  | k            | L                        | Rs                | Q    |

| 4.00E+08           | 0.0003       | 3.90E-09    | 0.490088454       | 20   | 4.00E+08           | 0.0003       | 3.90E-09                 | 1.960353816       | 5    |

| Basic Calcs        |              |             |                   |      | Basic Calcs        |              |                          |                   |      |

| XL<br>0.801750070  |              |             |                   |      | XL<br>0.801760070  |              |                          |                   |      |

| 9.801769079        |              |             |                   |      | 9.801769079        |              |                          |                   |      |

| Finally            | Poal(v21)    | Imag(y21)   | Yields a needed R | ,    | Finally            | Poal(v21)    | Imag(v21)                | Yields a needed R |      |

|                    | Real(y21)    | 2.93152E-05 | 331628.562        |      |                    | Real(y21)    | Imag(y21)<br>2.83282E-05 | 101415.6374       |      |

|                    | -5.U134ZE-U0 | Z.3313ZE-03 | 331028.302        | ,    |                    | -3.80041E-00 | 2.83282E-U3              | 101415.0374       |      |

Figure 2.7 – Range of Resistance Values

The range of resistance values predicted in Figure 2.7 range from .75 k $\Omega$  to 400 k $\Omega$ . However, the 400 k $\Omega$  case uses a coupling of k=.0003. In [2] this coupling value was shown to be so small that no significant asymmetry was produced in the passband. Therefore here, when choosing the range of values to be implemented, values on the order of 400 $\Omega$  were treated as open circuits . Conversely, the lower range of resistance values result from much higher coupling values which were also shown in [2] to cause significant asymmetry in the passband and were given more emphasis when choosing resistance values for the circuit design.

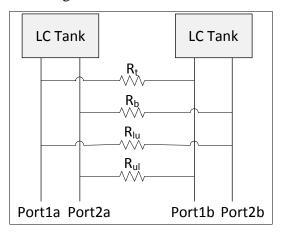

A bank of binary weighted resistors were designed to interconnect the LC tank circuits in the topology shown in Figure 2.8. Values were chosen to meet the range indicated in Figure 2.7, but more importance was given to resistance values resulting from higher coupling coefficients based on the results in [2], the available range of resistance values chosen is  $750\,\Omega$  to  $40\,k\Omega$ . The circuit is shown at the top level in Figure 2.8 and with a closer in view in Figure 2.9.

**Figure 2.8 – Resistance Tuning Circuitry Topology**

Figure 2.9 – Top View Resistance Tuning Circuitry

Figure 2.10 – Narrowed View Resistance Tuning Circuitry

The circuits in Figures 2.9 and 2.10 were implemented for each of the resistors shown in Figure 2.8 so these tuning circuits could cancel all possible geometries of inductive coupling.

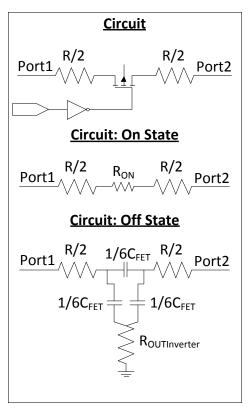

These resistor banks were designed to be controlled by digital signals from the S/P register driven through inverters to the gate of a FET. When the FET's are on, they are driven in the triode region. When the FETs are off they are seen in the circuit as small capacitors. The first design consideration here was keeping the FET large enough that it's on resistance was negligible relative to the resistors it activated when on. The W/L ratio was calculated by targeting a low on resistance relative to the resistors being driven using equation (2.32).

$$\frac{W}{L} = \frac{1}{r_{ON} \frac{k'_n}{2} (v_{gs} - v_t)} \tag{2.32}$$

Calculation shows a W/L ratio of 350 was adequate to produce  $R_{ON}$  value on the order of 2.5% of the total resistance from port1 to port2 for the 750  $\Omega$  resistor when the FET was on.

The second design consideration was to ensure the impedance effects of capacitance due to the FET when it's off are sufficiently small. This restriction dictates that the W/L of the FET be small enough that its impedance was large relative to the resistors it was driving, using equations (2.7) and (2.8). The FETs used to produce the small R<sub>ON</sub> were shown to produce a

complex impedance 14 times larger than the resistors, which should be sufficient to avoid loading ports one and two when the FET is off. Figure 2.11shows the capacitances modeled for the design in the on and off states.

**Figure 2.11 – Resistance Tuning Circuitry Models**

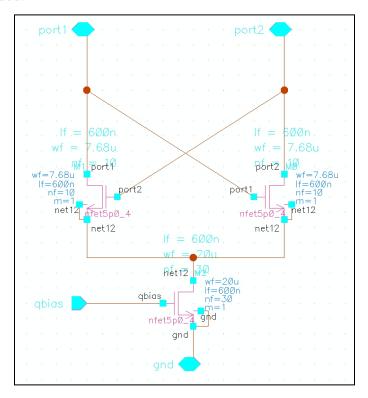

#### 2.3.1.3 The Second Source of Asymmetry

#### 2.3.1.3.1 Origin of Asymmetry: Incorrectly Driven Coupling Capacitors

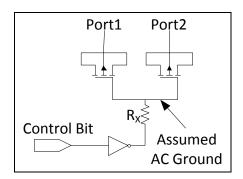

The second source of asymmetry in the passband shape was a result of errors in the driving circuitry of the coupling capacitors used to offset the inductive coupling. The assumption originally was that the capacitors, which were driven through a resistor via an inverter saw an AC ground as shown in Figure 2.12.

Figure 2.12 – Resistance Tuning Circuitry Models

However, these capacitors were connected between the front-end and band-end LC tank circuits in the same topology used for the resistors in Figure 2.8. Unfortunately the two LC tank circuits contain different signals, so the signals at port1 and port2 didn't cancel each other. As a result the gates of the FETs were not an AC ground.

Similar to section 2.3.1.2 the incorrect loading was modeled using Y-parameters and the admittance needed to cancel the unwanted loading was found to be described by (2.33).

$$y_{21} = \frac{R_X}{X_C^2 + 4R_X^2} - \frac{j2R_X^2}{X_C(X_C^2 + 4R_X^2)}$$

(2.33)

(2.33) shows for the unwanted real part of  $y_{21}$  to be negligible,  $X_C$  must be much greater than  $R_X$ . This derivation and confirmation in simulation and tests with the Q-enhanced circuit is documented in [2]. Section 2.3.1.3.2 describes the hardware solution to resolve this loading problem.

#### 2.3.1.3.2 Circuit Design Solution: Corrected Loading

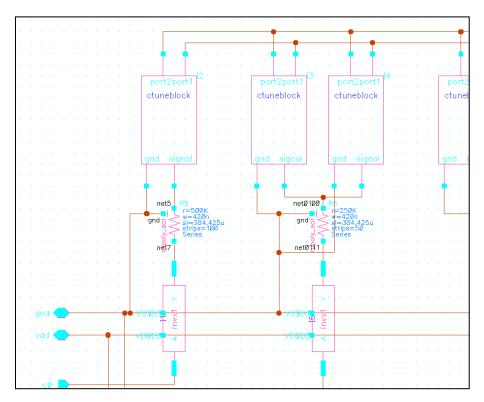

As (2.33) shows, the solution to mitigate the loading is to make the  $R_X$  small relative to the impedance of the capacitive impedance of the FET when it's on. The  $X_C$  of the FET is calculated by equations (2.7) and (2.8) and can be used to estimate the necessary  $R_X$ . The range of coupling capacitor values were achieved as by implementing binary weighted banks of capacitors, similar to the resistor scaling. The  $R_X$  values for each bank of capacitors were scaled down as the coupling capacitor values are increased. The schematic for this circuitry is shown below in three views to explain the overall layout of the whole circuitry and provide views of the lower level topology and smaller elements.

**Figure 2.13 – Top View Capacitive Coupling Circuit**

Figure 2.14 – Narrowed View Ctuneblock from Fig. 2.13

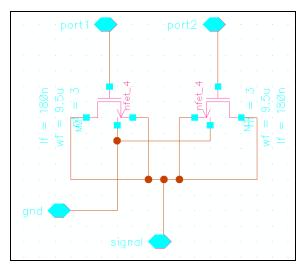

Figure 2.15 – Cell View Ctuneblock

# 2.4 Additional Circuit Redesigns

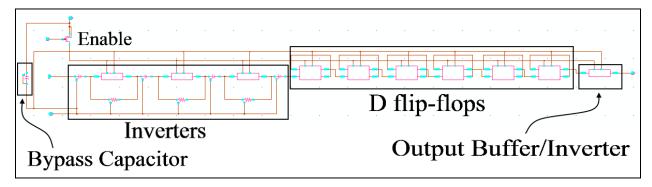

### 2.4.1 Frequency Divider

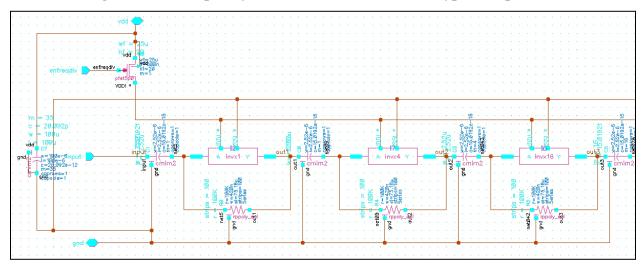

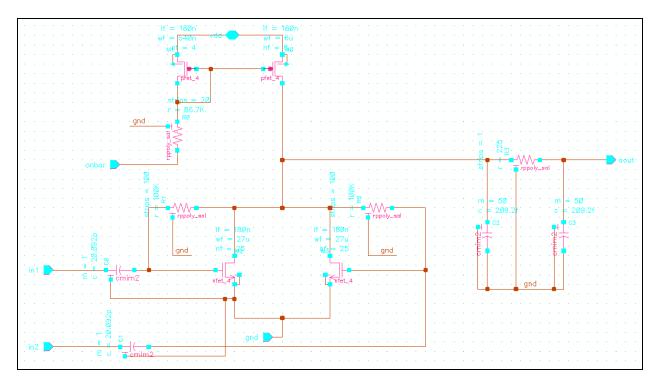

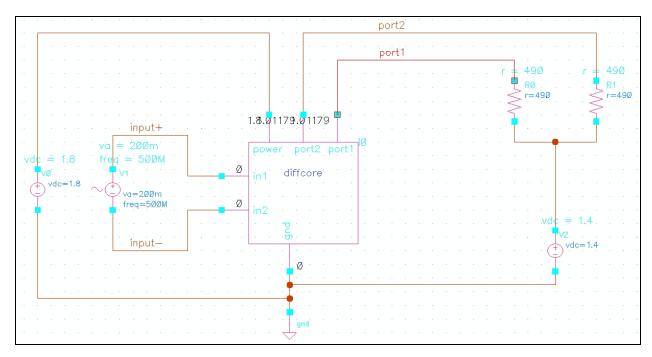

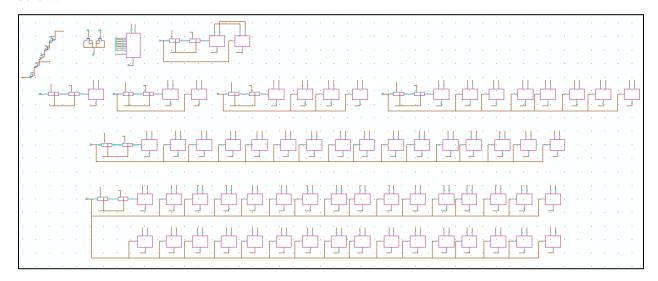

In the previous design the frequency divider circuitry lacked the desired sensitivity due to an internal oscillation frequency documented in [2]. Many designs were considered as potential solutions because the SOI process the filter was designed in didn't have the digital circuitry that could function reliably at the frequency ranges needed to divide down 500 MHz. However, the new process D-Flip-Flop and inverter circuits performed well according to simulation and the new frequency divider was designed as shown below in Figure 2.16.

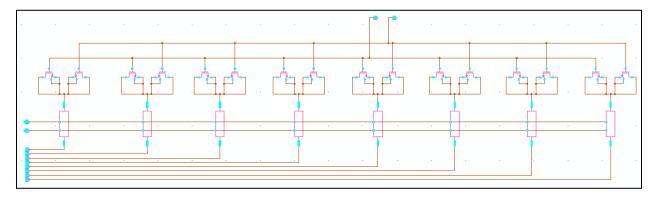

Figure 2.16 – Top View Frequency Divider

This circuit works by using the inverters, self-biased using the resistors shown, and AC coupled to amplify and shift DC offset of the signal to clock the first DFF. The series of 6 DFF provides the desired division of 64 and an inverter is used as a buffer at the output to avoid loading issues.

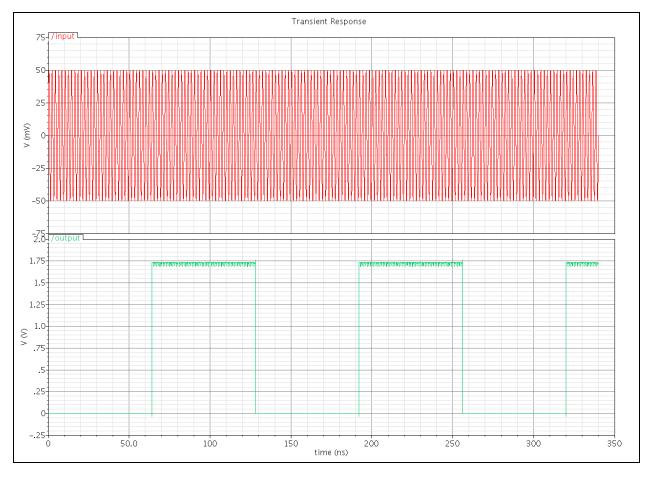

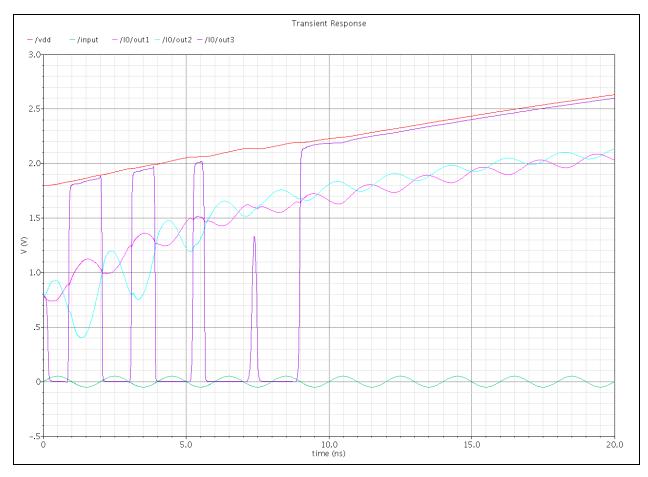

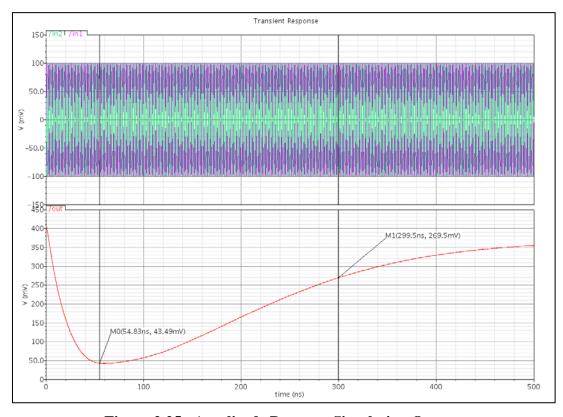

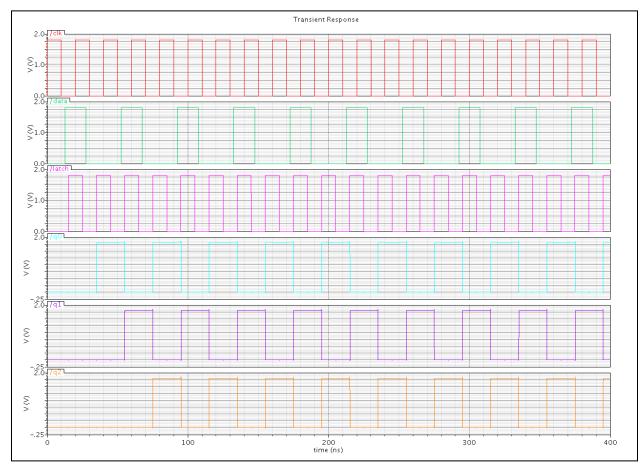

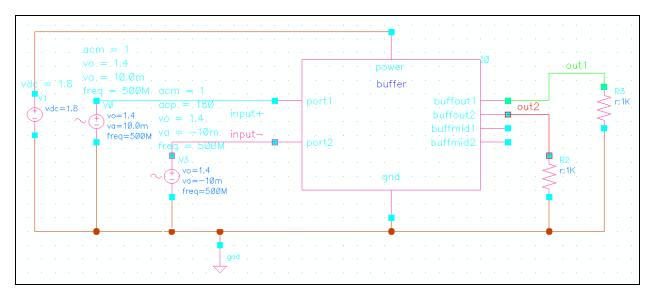

According to simulation, this circuit takes a  $10 \text{ mV}_{PP}$  differential sinewave at 500 MHz and outputs a single ended digital square wave from 0 V to  $V_{dd}$  at 7.8125 MHz, 1/64 the original frequency. The testbench and simulation output are shown in Figures (2.17) and (2.18).

Figure 2.17 – Frequency Divider Testbench

Figure 2.18 – Frequency Divider Simulation Output

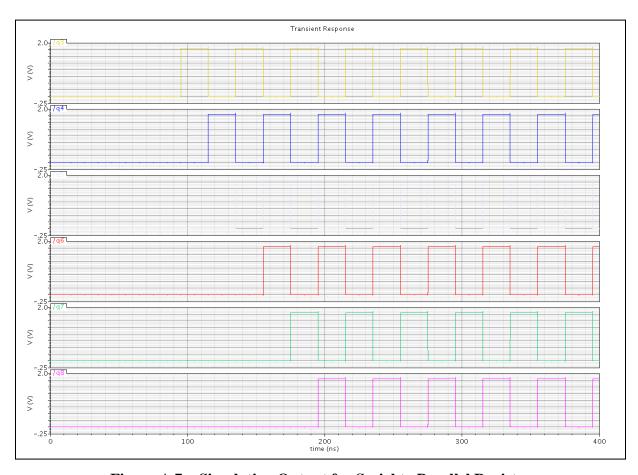

The digital circuitry used in the new frequency divider design has the potential couple into the low-level circuits within the die and needed a bypass capacitor, shown in the above design, to smooth out any spikes in the power line. To ensure the cap was large enough to protect the circuitry and keep the power input constant the circuit test bench was set up with a 1H inductor in the power line to so that the circuit couldn't draw current from the supply immediately. Then the simulation was run to see if the circuit functioned correctly. The size of the bypass cap was increased until the circuit maintained normal operation even with the inductor in the power line. The testbench and the first part of the circuit in Figure 2.16 are shown in Figures 2.19 and 2.20 followed by two output simulations. The first simulation output in Figure 2.21 shows the circuitry performance with the bypass capacitor too small and the second simulation output in Figure 2.22 shows the circuit performance with the bypass capacitor sufficiently large.

Figure 2.19 – Frequency Divider Testbench to Test Bypass Capacitor

Figure 2.20 – Frequency Divider Circuit Narrowed View

Figure 2.21 –Frequency Divider Circuit to Test Bypass Capacitor Simulation Output with Insufficiently Large Bypass Capacitor

Figure 2.22 – Frequency Divider Circuit to Test Bypass Capacitor Simulation Output with Correctly Sized Bypass Capacitor

As shown by the simulation outputs the final bypass cap of about .7nF was large enough to assure smooth and stable operation.

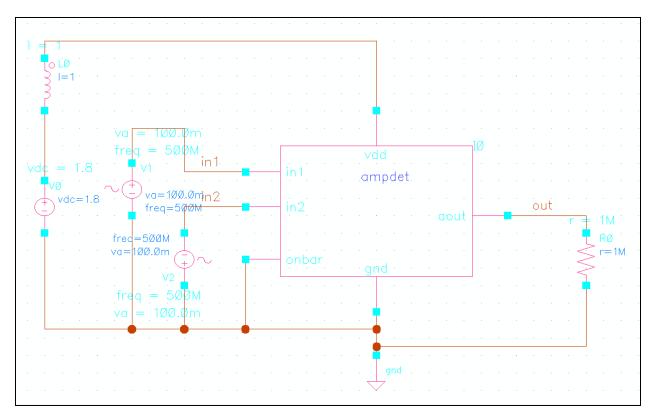

## 2.4.2 Amplitude Detector

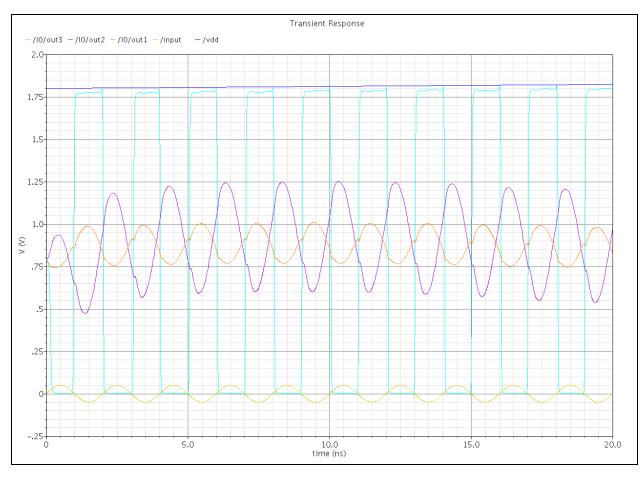

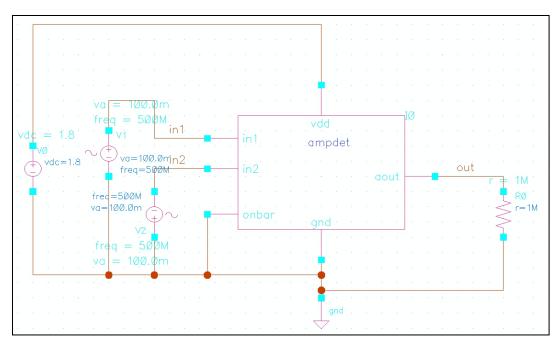

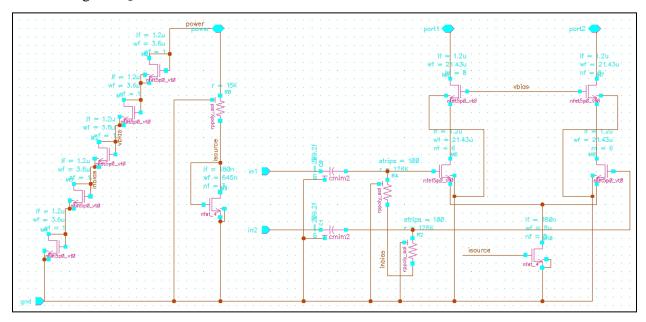

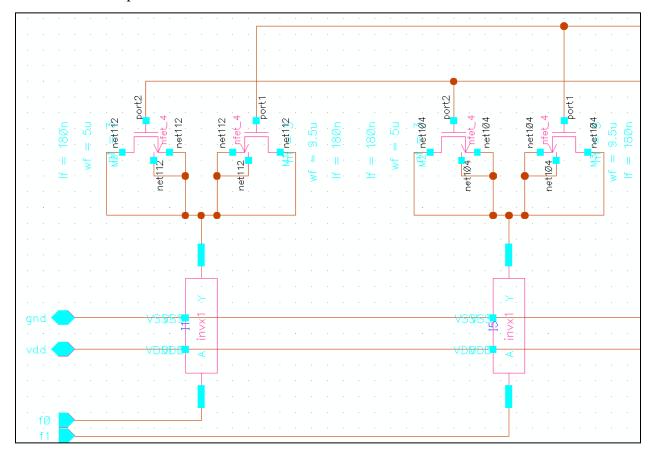

The last circuit discussed in detail is the amplitude detection circuitry. During simulation a problem with the basic design was discovered. In the previous filter small signals were never input to the amplitude detector due to problems with the frequency detector. As a result the problem in the circuit design was never noticed. At this time a full solution to this problem is not known, but the design flaw is detailed briefly here to document the problem to provide future designers a basis to begin designing upon. The amplitude detection circuit as currently designed is shown in Figure 2.23.

Figure 2.23 – Amplitude Detector Circuit

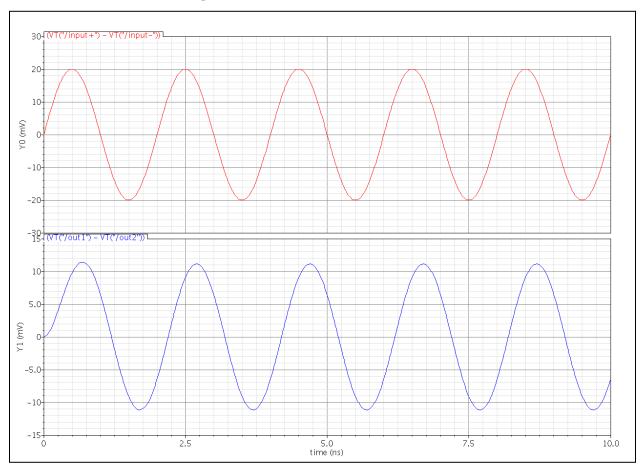

This circuit sets up a bias current using the current mirror with the PFETs at the top of the circuit. The input signal is driven differentially through AC coupling capacitors to the input. These capacitors have a small impedance relative to the FETs and biasing resistors connected to the signal at the input. When there is a sufficiently large AC signal applied at the input, the core FETs turn on shorting the drain voltage to ground and the voltage at the drain of both FETs drops. Good sensistivity is ensured by biasing the core FETs close to their thresholds so that only a small voltage is needed to turn them on. The output stage is a resistor and two capacitors in a low pass configuration to filter the output signal. Ideally, a stable DC voltage is output which drops quickly and significantly with the application of an input signal. During the design and simulaiton of this circuit a problem was discovered with the design as illustrated in Figures 2.24 and 2.25.

Figure 2.24 – Amplitude Detector Circuit Testbench

**Figure 2.25 – Amplitude Detector Simulation Output**

As desired, this circuit produces a sharp decrease in the output voltage level in direct proportion to the amplitude of the input signal. However the output simulation shows that after the voltage drops sharply it slowly increases. This behavior was determined to be caused by the time constant created by the resistors biasing the core FETs and the input capacitors. The problem occurs because when one of the FETs is turned on, the voltage drops as the input signal is still being applied, but the currents charging the input capacitor are not symmetrical. With the FET on, a larger  $C_{GS}$  is created, and then when it is off during the subsequent half of the cycle of the input, the  $C_{GS}$  is no longer the same value. As a result the input coupling capacitor stores up a charge and slowly pushes the output voltage up again. This issue will need to be resolved before the design is fabricated.

The rest of the circuits in the Q-enhanced filter were very similar to the original design and are omitted in the body of this text. However for clarity and documentation, these circuits are included in the appendix A where they are explained briefly and shown with their simulations.

# **Chapter 3 - Supporting Hardware and Software**

#### 3.1 Previous Work

In the thesis preceding this work, C based support code was written to for a dsPIC64FJ802 microcontroller to program and control the Q-enhanced filter. The microcontroller sent a control word, 64 bits in length, to the filter's serial to parallel register. Additionally, C# code was used to create a GUI that allowed the user to interface with the filter. Two versions of the C code on the microcontroller were developed: an automated, temperature stable algorithm that took user settings and could achieve bandwidths of 20MHz-5MHz, and a manual algorithm that allowed the user to manually set all the bits of the control word. As a basis to understand the code modifications implemented and recommended in the future, the next section briefly reviews the automated algorithm with the inclusion of resistance tuning.

## 3.2 Top-level Code Implementation

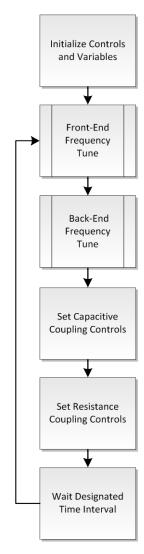

The automated algorithm worked as shown in Figure 3.1. The first step in the algorithm is setting all controls based on user inputs and initializing all additional settings. Next, the

algorithm tunes the front-end frequency, then the back-end frequency, sets the coupling controls, sets the resistance tuning, waits the designated time interval and iterates. The only change at this top level of the algorithm is the addition of the resistance tuning. The information for modifying the code to implement this new hardware is detailed in section 3.3.2. The other additions to the algorithm occur within the front-end tuning and back-end tuning blocks. These changes are explained in section 3.3.1.

**Figure 3.1 – Top Level Flowchart of Tuning Algorithm**

#### 3.3 Software Additions

The first set of changes to the C code are additions implemented to improve the tuning algorithm by using the fine resolution frequency and q-enhancement controls in the current filter design. The second set of additions are needed to prepare the current code for the addition of the

resistance tuning capability. The next section on fine tuning explains the changes to the code and documents the resulting improvements in the automated algorithm. The following section on resistance tuning will describe the suggested implementation and hardware specifics needed to implement passband symmetry control. Additionally, each of these sections enumerates the additions to the C code and C# code that are needed.

#### 3.3.1 Fine Tuning

#### 3.3.1.1 Implementation

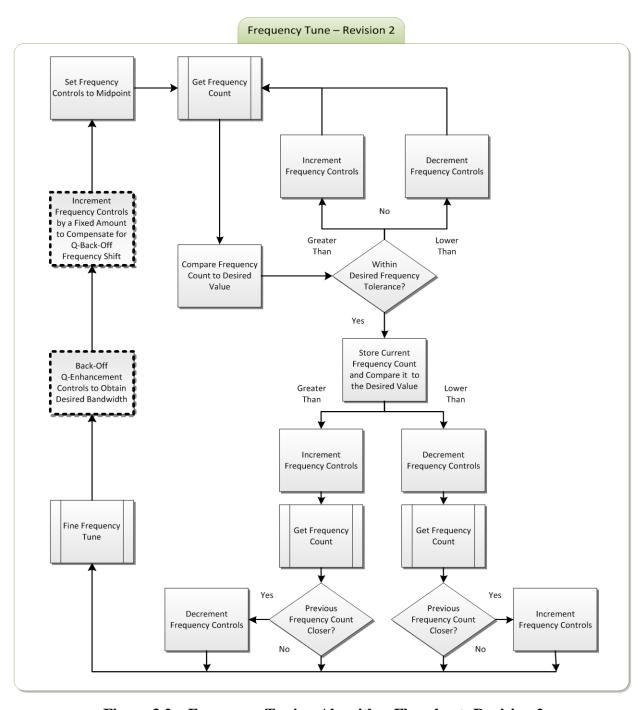

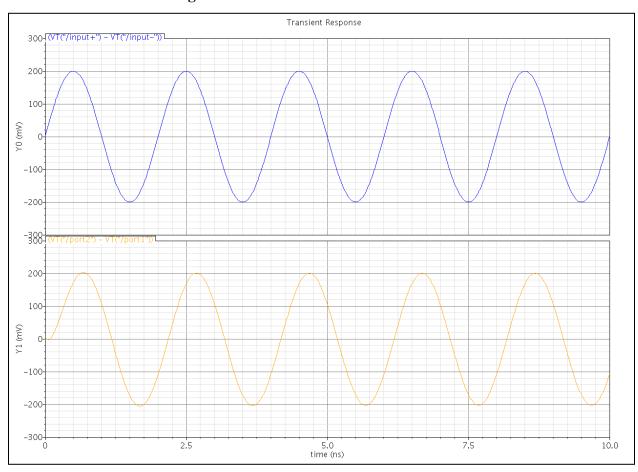

It was a long time goal of this work to achieve finer frequency tuning accuracy and smaller bandwidth capability. In preparation for this goal external DACs were already implemented on the circuit board with the microcontroller. These DACs were intended to generate the necessary analog voltages to the pins on the filter which controlled the analog frequency tuning and Q-enhancement controls, but were not tested and exercised in previous work [2]. The analog circuits the fine-tuning explained in this section uses are essentially identical to those in Figures A.17 and A.19. Figures 3.2 through 3.5 show the flowcharts for the modified automated algorithm and are explained below.

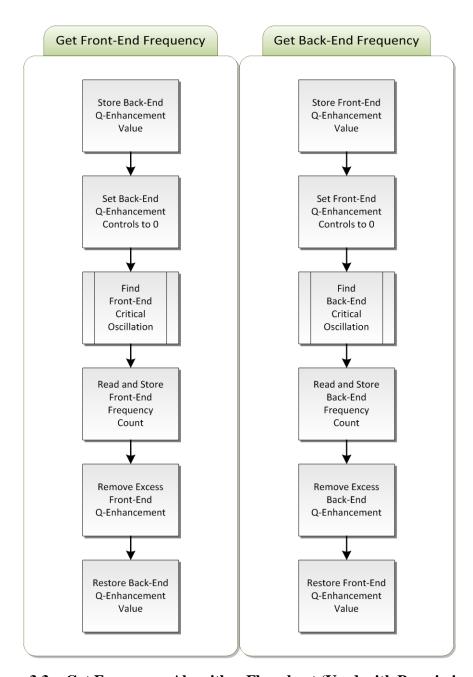

The modified frequency tuning algorithm is shown in Figure 3.2 is identical to the flowchart in [2], except for the addition of fine tuning which uses the analog controls, implemented immediately after the course tuning which uses the digital controls. The 'get-frequency' flowchart in Figure 3.3 for the front and back ends is unchanged. However the 'find-critical-oscillation' flowchart in Figure 3.4 now includes the fine Q-enhancement tuning. The last flowchart in Figure 3.5 is entirely new and documents the logical flow of the fine tuning algorithm.

The fine tuning portion of the algorithm functions very similarly to the course tuning. First, the fine tuning determines whether the current frequency is higher or lower than desired. Second, the algorithm iterates to find the first analog setting to set the current frequency equal to the desired frequency. Those analog settings are stored and then further incremented until the frequency no longer equals the desired frequency. Those analog settings are compared to the stored settings and the analog controls are set centered between them to achieve the closest frequency to the desired frequency as possible.

**Figure 3.2 – Frequency Tuning Algorithm Flowchart: Revision 2**

Figure 3.3 – Get Frequency Algorithm Flowchart (Used with Permission [2])

Figure 3.4 – Find Critical Oscillation Flowchart

**Figure 3.5 – Fine Tune Flowchart**

#### 3.3.1.2 Results

The fine-tuning code addition improved the algorithm's performance. Without fine tuning some settings at bandwidths on the order of 5MHz exhibited variation in gain and bandwidth in the passband from one tuning iteration to the next. When the filter was programmed and the automatic tuning algorithm run, the settings that were chosen by the tuning algorithm were output to the GUI. These outputs showed a change  $\pm 1$  in the digital q-enhancement settings when the gain in the passband varied. This indicated that the tuning algorithm needed additional precision to avoid fluctuation between two values in the algorithm. Bandwidths below 5MHz were not achievable without producing unstable outputs from the filter.

Figure 3.6 shows the passband variation caused by this quantization error in the tuning

Figure 3.6 - Passband Variation without

Fine Tuning

algorithm. This behavior was captured by setting the first trace of the spectrum analyzer to capture the maximum value of the passband and the second trace to capture the minimum value of the passband. This variation between tuning iterations was eliminated when the fine tuning code was implemented.

After the fine tuning was implemented, a temperature stable bandwidth of 2.5MHz with a center frequency of 450 MHz, a fractional bandwidth of about .6%, was achieved. Figure 3.7 shows a screen

capture of the filter tuned to this narrow bandwidth and the settings which achieved this passband shape are shown in Table 3.2. This bandwidth and passband shape was maintained by the algorithm which included the fine tuning when heated from 20°C to 75°C.

Figure 3.7 – 2.5 MHz Bandwidth Passband with Fine Tuning

| Algorithm Settings      |       |         |  |  |  |  |

|-------------------------|-------|---------|--|--|--|--|

| Bandwidth               | 5 MHz | 2.5 MHz |  |  |  |  |

| Center Frequency        | 450 N | MHz     |  |  |  |  |

| Frequency Tolerance     | .3 M  | Hz      |  |  |  |  |

| AD Threshold 1          | 3     | 2       |  |  |  |  |

| AD Threshold 2          | 3     | 3       |  |  |  |  |

| Q-Offset                | 2     | 2       |  |  |  |  |

| Q-Back-Off              | 2     | 1       |  |  |  |  |

| F-Offset                | 2     | 2       |  |  |  |  |

| Capacitive Upper Tuning | 8     | 5       |  |  |  |  |

| Capacitive Lower Tuning | 6     | 6       |  |  |  |  |

| Capacitive UFLB Tuning  | 0     | 0       |  |  |  |  |

| Capacitive LFUB Tuning  | 0     | 0       |  |  |  |  |

**Table 3.1 – Fine Tune Settings for 2.5 MHz Bandwidth**

These settings are dependent on the resistors used to cancel passband asymmetries and the Q of the on chip inductors. These settings may need to be varied  $\pm 1$  if one of these variables has been changed. The addition of the more precise controls suggested in the future work should help to mitigate uncertainty in these settings.

## 3.3.2 Resistance Tuning

### 3.3.2.1 Implementation

The resistance tuning code needs to be developed to utilize resistance tuning controls described in section 2.3.1.2.2. This code can't be fully tested without the new filter design, but

many of the necessary additions to the code-base are clear. Some of the modifications needed are detailed below.

#### 3.3.2.2 Control Word and Passband Controls

The filter is programmed by the microcontroller via SPI communication. The current code sends a 64 bit word to the filter. The new filter will have an additional 28 bits of data to set the resistance tuning circuitry documented in section 2.3.1.2.2. The full 96 bit control word that the serial to parallel register will need from the microcontroller is shown in table 3.3. 'FENDCON' and 'BENDCON' are the control bits for the front-end and back-end frequency tuning, the amplitude detector and frequency divider. 'CAPCON1' and 'CAPCON2' are the control bits for the capacitive coupling circuits. 'RESCON1' and 'RESCON2' are the control bits for the passband asymmetry neutralization. RESCON1 and RESCON2 are unimplemented at the time of this thesis's publication.

| FENDCON | BENDCON | CAPCON1 | CAPCON2 | RESCON1 | RESCON2 |

|---------|---------|---------|---------|---------|---------|

| MSB     |         |         |         |         | LSB     |

Table 3.2 – Word Sent from Microcontroller to Filter

The resistance value needed to cancel asymmetries due to unwanted inductive coupling in the LC tanks, calculated in section 2.3.1.2.1, is shown again in (3.1) and then expressed in terms of coupling, k, and the Q of the filter.

$$\frac{-1}{R} = \frac{-2X_L^2 R_S k}{\left(R_S^2 + X_L^2\right)^2 + 4X_L^2 R_S^2} = \frac{-2Qk}{R_S((1+Q^2)^2 + 4Q^2)} = \frac{-2Q^2 k}{2\pi f((1+Q^2)^2 + 4Q^2)}$$

(3.1)

since  $R_s = \frac{X_L}{Q}$ . Letting  $Q \gg 1$ , then  $R \ll X_L$  and all  $R^2$  go to zero and this equation can be

expressed as (3.2) where we assume the Q of the filter is dominated by the Q of the inductors.

$$\frac{1}{R} = \frac{k}{X_L} \frac{2}{Q} \xrightarrow{\text{yields}} R = \frac{QX_L}{2k}$$

(3.2)

Note this resistance value assumes that the non-symmetry in the capacitive coupling discussed in section 2.3.2 has been successfully mitigated by raising the resistor values between the inverter and the FET's they drive and the *only* resistance being canceled out by this tuning is due to the inductive coupling. However, these resistors can also compensate for a capacitor coupling non-idealities if needed; only the value will need to be modified.

The capacitive coupling is currently implemented as a manual input by the user. It's recommended that the resistance tuning be implemented the same way for testing. Eventually, when the filter is fully tested a bandwidth and center frequency could be chosen and the capacitive coupling and resistance tuning could be chosen based off of a lookup table. This would require knowing the coupling value between the inductors either by user input or hard coding.

## **Chapter 4 - Spurious Responses in Receivers**

This chapter addresses the impact of filtering on receiver performance at an architectural level. As a basis for cogent discussion, receiver architectures are briefly enumerated and a superheterodyne architecture is explained in some detail as a foundation of further analysis. Next, receiver performance is discussed focusing on the intrinsic limitations imposed by a receiver's ability to avoid spurious responses. An overview of spurious responses is presented with a brief explanation of their origins in superheterodyne receivers. To observe these behaviors in receivers a novel method of measurement and receiver characterization is described. Using this evaluation method some commercial handheld radios, a software defined radio (SDR) and an integrated radio are characterized. Finally in Chapter 5, a modified receiver architecture using a tunable variable bandwidth Q-enhanced bandpass filter is presented and our testing procedure is used to verify the validity of this solution.

#### 4.1 Introduction to Receiver Architectures